アプリケーション・ノート (7)

-

Crystal Oscillator Design Guide[AN14518]

-

PN5190 design-in recommendations[AN12551]

-

PN5190 questions and answers[AN13669]

-

PN5190 antenna design guide[AN12549]

-

PN5190 EMV L1 SW porting to IMX1170[AN13425]

カタログ (1)

データ・シート (2)

-

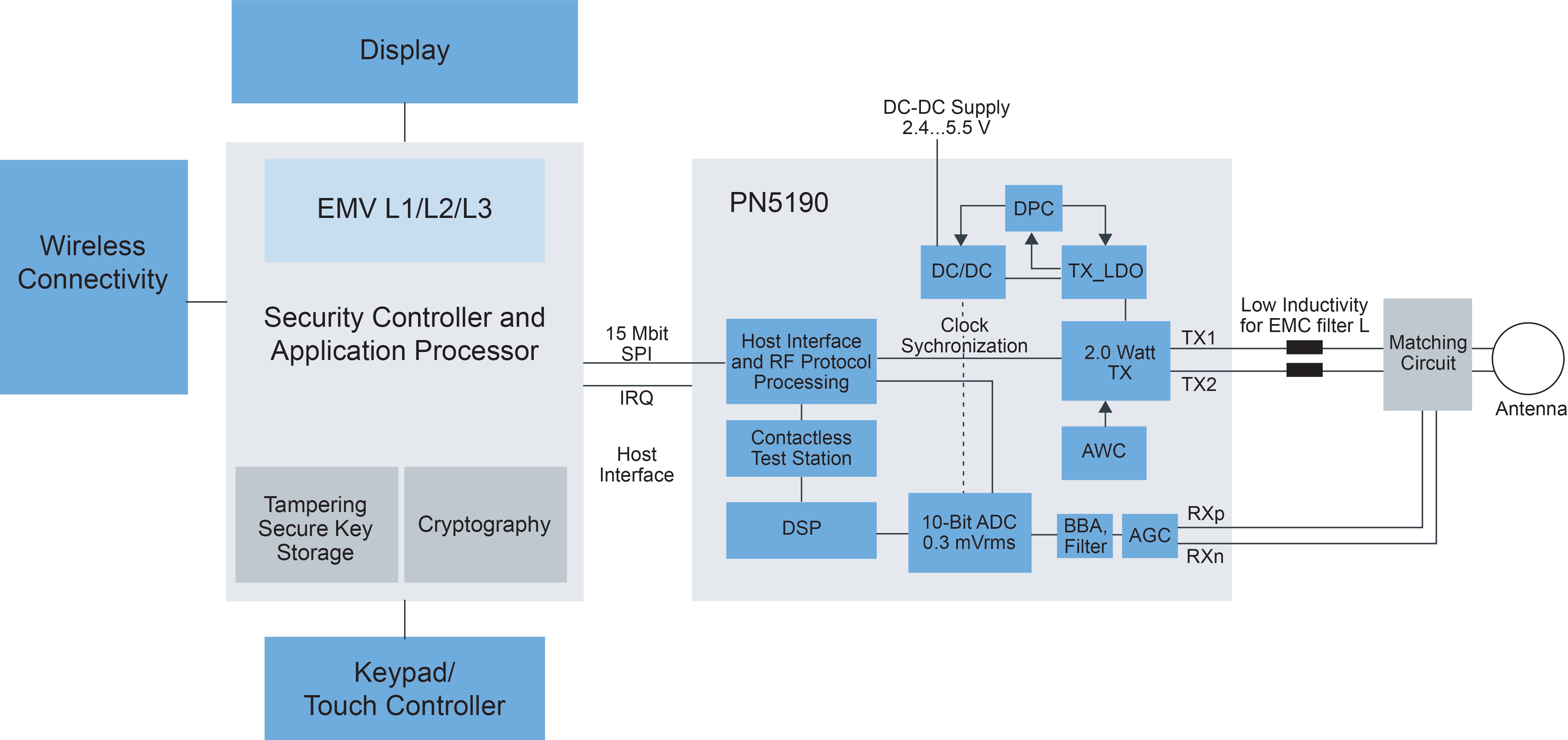

PN5190B2 NFC Frontend[PN5190B2]

-

PN5190B1 NFC Frontend[PN5190B1]

ドキュメント (2)

-

PN5190 instruction layer[UM11942]

ファクト・シート (1)

-

NXP PN5190 NFC Frontend[PN5190-FS]