USB 2.0フルハイスピードソリューション

USBフルスピード・ソリューションのアプリケーションは次のとおりです。

- マウス、キーボード

- 低速プリンタ

- マイク

- ゲームコントローラ

- 産業機器制御

USB高速ソリューションのアプリケーションは次のとおりです。

- 大容量ストレージデバイス(フラッシュドライブを含む)

- プリンタ

- スキャナ

- ビデオアダプタ

- 携帯電話

- タブレット

- ワイヤレスアダプタ

USB 2.0フルスピード専用デバイスコントローラ

USB 2.0フルスピードデバイスコントローラは、NXP Semiconductorsのシリコン実証済みの技術を使用して構築された、高度に構成可能で合成可能なUSBコアです。

このコアは、コスト重視のアプリケーションで効率的なUSB実装を提供する極めて低いゲート数設計です。

USB側の標準USBトランシーバおよびシステム側のAMBA® AHBインタフェースと統合され、主要な組み込み型マイクロプロセッサーコアをすべてサポートします。

特長

- USB 2.0仕様に準拠

- フルスピード(12 Mbps)の動作をサポート

- AHBインターフェイスに接続されたDMAエンジン

- 低いゲート数(7 Kゲート)

- LPMのサポートなど、さまざまな低電力機能

- 最大14の非制御論理エンドポイント

- バルク、割り込み、またはアイソクロナスのエンドポイントタイプ

- 最大パケットサイズ0~1023

- ソフトウェア制御による割り込み構造

- エンドポイントバッファ用のシングルポートRAMをサポート

- USBバッファは、パケットまたは転送レベルでプログラムできます

- サードパーティ製ソフトウェア(ドライバなど)によるサポート

- AMBA® AHB準拠のシステム・インターフェイス

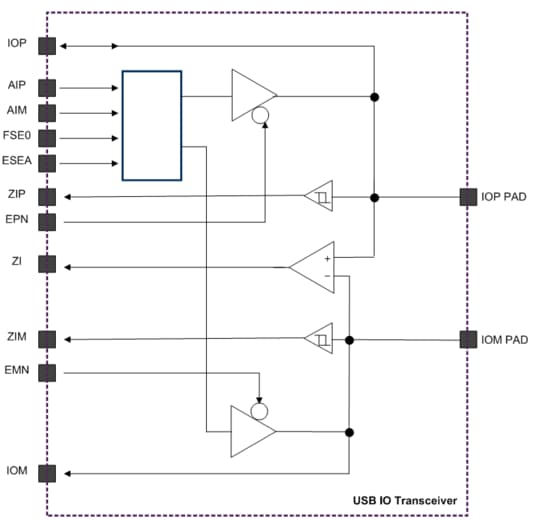

USB 2.0 I/Oトランシーバ

USB IOトランシーバは、TSMC 90LPおよび65LPプロセスで使用可能なCMOS IOセルです。USB規格リビジョン2.0(フルスピードおよびロースピードのみ、2000年4月27日)に準拠しています。

セルトランシーバは、ロジックCMOS信号をUSB対応の出力信号に変換し、その逆も可能です。このトランシーバは、データ転送レートのモードとして、ロースピードモード(1.5 Mbps)とフルスピードモード(12 Mbps)の2つをサポートしています。どちらのモードでも、出力信号レベルの振幅は外部電源電圧と等しくなります。

レシーバは、0.2V (0.8V < CMR < 2.5V)という小さな差動信号を検出することができます。これにより、ノイズのマージンが良くなり、堅牢な通信システムの構築に役立ちます。差動レシーバとは別に、このセルには2つのシングルエンドレシーバも含まれており、各レシーバは2つのデータラインに対応しています

特長

- 12 Mbps (フルスピード)および1.5 Mbps (ロースピード)のシリアルデータ伝送をサポート

- ロジックCMOS信号をUSB対応の出力信号に変換し、その逆も可能

- ホストのダウンストリームポート、ハブのアップストリーム/ダウンストリームポート、デバイスのアップストリームポートに使用可能

- D+およびD – 出力の個別イネーブル信号によって、USBと同じデータレートのUARTモードでこれらの2つのパスを個別に制御できます

- シングルエンドデータインタフェースをサポート

- プログラマブルな差動またはシングルエンドコア入力と強制的なシングルエンドロー

- サスペンドモードでテスト可能なIDDQ

- D+データライン上の内部プログラマブルなプルアップ抵抗

- D+およびD – データラインの両方で内部スイッチ可能なプルダウン抵抗

- 電源シーケンスの要件なし

- D+およびD – は、コアの電源がオフでIOの電源がオンの場合にハイインピーダンスになります

- 小面積(90nmで0.04mm2)

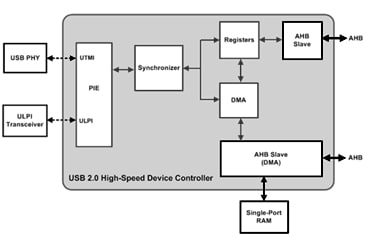

USB 2.0高速デバイスコントローラ

USB 2.0高速デバイスコントローラは、NXP Semiconductorsのシリコン実証済みの技術を使用して構築された、高度に構成可能で合成可能なUSBコアです。

このコアは、コスト重視のアプリケーションで効率的なUSB実装を提供する極めて低いゲート数設計です。

USB側の標準UTMI準拠PHYまたはUSB ULPIトランシーバ、およびシステム側のAMBA® AHBインターフェイスと統合され、主要な組み込み型マイクロプロセッサーコアをすべてサポートします。

特長:

- USB 2.0仕様に準拠

- 高速(480 Mbps)およびフルスピード(12 Mbps)の動作をサポート

- AHBインターフェイスに接続されたDMAエンジン

- ゲート数が少ない(20Kゲート)

- さまざまな低電力機能

- 最大14の非制御論理エンドポイント

- バルク、割り込み、またはアイソクロナスのエンドポイントタイプ

- 最大パケットサイズ0~1023

- ソフトウェア制御による割り込み構造

- エンドポイントバッファ用のシングルポートRAMをサポート

- USBバッファは、パケットまたは転送レベルでプログラムできます

- サードパーティ製ソフトウェア(ドライバなど)によるサポート

- 独立したAMBA® AHB準拠のシステム・インターフェイス

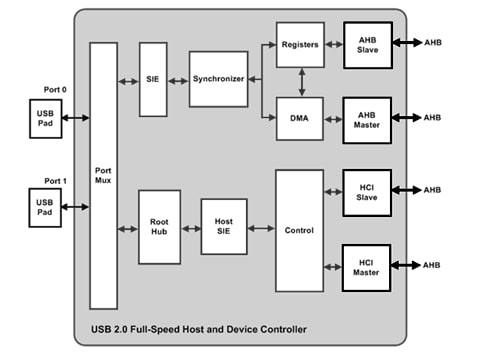

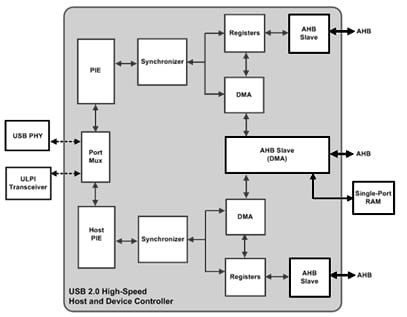

USB 2.0高速ホストおよびデバイスコントローラ

USB 2.0高速ホストおよびデバイスコントローラは、NXP Semiconductorsのシリコン実証済み技術を使用して構築された、高度に構成可能で合成可能なUSBコアです。

このコアは、コスト重視のアプリケーションで効率的なUSB実装を提供する極めて低いゲート数設計です。

USB側の標準UTMI準拠PHYまたはUSB ULPIトランシーバ、およびシステム側のAMBA® AHBインターフェイスと統合され、主要な組み込み型マイクロプロセッサーコアをすべてサポートします。

特長:

- USB 2.0仕様に準拠

- 高速(480 Mbps)、フルスピード(12 Mbps)、および低速(ホストのみ、1.5 Mbps)動作をサポート

- ホストとデバイスの機能はソフトウェアの制御下で切り替え可能

- ホストはOCHI準拠

- ホストとして使用可能な2つのポート

- AHBインターフェイスに接続されたDMAエンジン

- 低いゲート数(43Kゲート)

- さまざまな低電力機能

- 最大14の非制御論理エンドポイント

- バルク、割り込み、またはアイソクロナスのエンドポイントタイプ

- 最大パケットサイズ0~1023

- ソフトウェア制御による割り込み構造

- エンドポイントバッファ用のシングルポートRAMをサポート

- USBバッファは、パケットまたは転送レベルでプログラムできます

- サードパーティ製ソフトウェア(ドライバなど)によるサポート

- 独立したAMBA® AHB準拠のシステム・インターフェイスで、ホストとデバイスの機能に対して個別のインターフェイスを提供

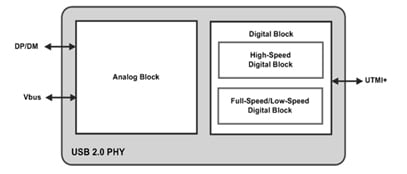

USB 2.0のPHY

特長:

- USB 1.1(FSおよびLS)およびUSB 2.0(HS)に完全準拠

- dpに1.5kΩのプルアップ抵抗、dpとdmに45Ωと15kΩのプルダウン終端抵抗を内蔵(USB 2.0で定義)

- dpに外付け1.5kΩプルアップ抵抗、dpとdmに15kΩプルダウン終端抵抗を使用するオプション

- 8または16ビットパラレルワードUTMI+準拠インタフェース

- UTMI+ v1.0レベル3

- UTMI+のオン・ザ・ゴー機能

- Mini-Aまたはmini-Bの検出

- Vbus比較器

- 60 MHz (8ビットインターフェイス)または30 MHz (16ビットインターフェイス)のクロックアウト

- 480 MHzクロックイン

- 複数のトランシーバの出力クロックを位置合わせするための再配置可能な分周器

- 高速、フル、低速の接続解除検出

- 機能モードでの低消費電流

- サスペンドモードでの低消費電流

- 小面積(90nmで0.9mm2)

パートナーのSilvacoがUSB IPの配布を担当します。Silvacoは、アナログ/ミックスドシグナル、パワーIC、メモリ設計に使用されるソフトウェアツールの大手EDAプロバイダーです。

カリフォルニア州サンタクララに本社を置くSilvacoは、30年以上にわたり北米、ヨーロッパ、日本、アジアにオフィスを構え、TCAD、SPICE Modeling、PDK開発に迅速かつ低コストのサービスを提供しています。2016年6月にSilvacoはSemiconductor IP blocksベンダーのIPextremeを買収し、現在はSilvacoのIP部門(IPextremeブランドの下)となっています

USB IPはNXPが所有していますが、Silvacoを通じてパッケージ、販売、サポートされています

成果物

| 成果物 |

| VHDL RTLソースコード(Verilog on request) |

| テストスイートを備えたテストベンチ |

| ユーザーズガイドと統合ガイドを含むドキュメント |

| テクノロジーに依存しない統合の制約 |

| 該当する場合 |

| 行動モデル |

| フロントエンドおよびバックエンドのビュー |