-

OM13561

-

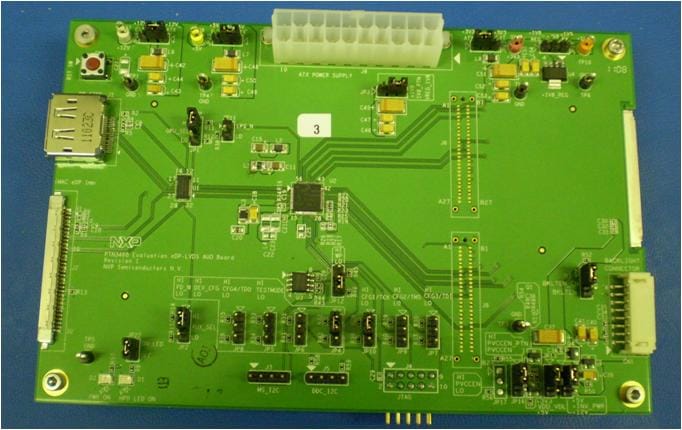

PTN3460I demo board.

Kit Contains:

- Demo Board

- Setup instruction

- Schematic pages

お客様の素早い設計とより早い製品化を実現する、技術情報と専門知識をご紹介します。

OM11064 is "End of Life", please use the replacement part OM13561.

The PTN3460/3460I Demo Board provides an easy interface between a host system (PC/Laptop) with a DisplayPort connector and a LCD panel with LVDS signal inputs. PTN3460/3460I acts as a bridge between the PC's DisplayPort connector and a LCD panel by converting DisplayPort protocol to LVDS format.

PTN3460I demo board.

| 代理店 | 地域 | 在庫 | 在庫日 | 注文 |

|---|

Upon selection of a preferred distributor, you will be directed to their web site to place and service your order. Please be aware that distributors are independent businesses and set their own prices, terms and conditions of sale. NXP makes no representations or warranties, express or implied, about distributors, or the prices, terms and conditions of sale agreed upon by you and any distributor.

PTN3460 demo board.

| 代理店 | 地域 | 在庫 | 在庫日 | 注文 |

|---|

Upon selection of a preferred distributor, you will be directed to their web site to place and service your order. Please be aware that distributors are independent businesses and set their own prices, terms and conditions of sale. NXP makes no representations or warranties, express or implied, about distributors, or the prices, terms and conditions of sale agreed upon by you and any distributor.

クイック・リファレンス ドキュメンテーションの種類.

1-5 の 8 ドキュメント

セキュアファイルの読み込み中、しばらくお待ちください。

2 設計・ファイル

セキュアファイルの読み込み中、しばらくお待ちください。