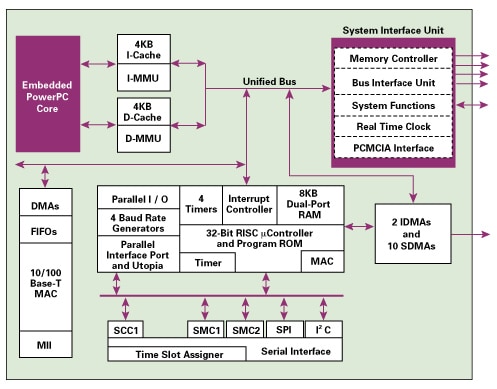

The MPC855T is a versatile one-chip integrated microprocessor and peripheral combination designed for lower cost access equipment that requires fast ethernet support capable of 100 Mbps. This member of the MPC860 PowerQUICC™ family combines an MPC8xx core processor along with NXP® Semiconductors's own Communication Processor Module, a separate RISC engine specifically designed to offload communication tasks from the MPC8xx core.

It differs from existing PowerQUICC® family members in that the MPC855T features only one Serial Communications Controller instead of four. In addition, the MPC855T is manufactured in Our 0.32µ process technology allowing for 3.3 volt core operation and 3.3 volt I/O.

The MPC855T is packaged in a 357-pin BGA package and is footprint-compatible with existing MPC860 PowerQUICC designs. The MPC855T is also available at 50, 66, and 80 MHz and is supported by over 50 third party tool vendors.