KIT-TPLSNIFEVBツールのスタート・ガイド

サインイン 進行状況を保存するには アカウントをお持ちでない方 アカウントを作成する。

お客様の KIT-TPLSNIFEVB

1. 使用を開始する

このページでは、KITTPLSNIFEVBツールをセットアップして使用する手順について説明します。

1.1 キットの内容と同梱物一覧

KIT-TPLSNIFEVBには以下のものが含まれています。

- 組立て済み/テスト済みのTPLスニファ・ドングル(静電気防止バッグ入り)

- ロジック・アナライザ接続ケーブル(8ピン・ヘッダ付き)

- ETPLバス接続ツイスト・ケーブル(2ピン・ヘッダ付き)

1.2 追加ハードウェアおよびソフトウェア

TPLスニファは、USB micro-Bコネクタを介して、50 mA(平均)および150 mA(ピーク)の5.0 V電源のみを必要とします(パワー・バンク、またはコンピュータに接続されたUSB ケーブルなどから給電)。

TPLスニファから供給されるデータを分析するには、ロジック・アナライザ(Saleaeロジック・アナライザなど)と対応ソフトウェアが必要です。

オプションとして、TPLフレームをデコードできるようにする、Saleaeロジック・アナライザ・ソフトウェア向けのプラグインと拡張機能を提供しています。詳細については、セクション4をご覧ください。

2. ハードウェアの入手

2.1 ボードの特長

- ETPL機能と他のすべての回路間の内部ガルバニック絶縁

- 監視対象ETPLバスの任意のポイントへの接続

- ETPLラインへの負荷が最小限

- Saleae Logic 8およびLogic Pro 8/16アナライザ・シリーズとピン互換性のある付属のケーブルを使用したロジック・アナライザ接続

- 5.0 V電源(通常はUSBパワー・バンクまたはコンピュータに接続されたUSBケーブル)からUSBコネクタを介して給電

- パワー・バンクの自動切断を防止するキープアライブ機能を統合

2.2 ボードの説明

KIT-TPLSNIFEVBボードは、TPLスニファとも呼ばれ、ロジック・アナライザ(Saleaeロジック・アナライザが望ましい)および対応ソフトウェアと連携して動作し、エレクトリカル・トランスポート・プロトコル・リンク (ETPL) 信号の分析に役立ちます。

任意のETPLバスに配置され、すべてのメッセージを非侵入的にリッスンし、バス上のフレーム・トラフィックを監視します(TPLスニファはリッスン・モードでのみ作動します)。該当する受信データ(SPI形式)はANALYZER出力コネクタに出力され、そこからロジック・アナライザとそのソフトウェアに接続されて、さらに分析が行われます。

2.3 ボードのコンポーネント

KIT-TPLSNIFEVBツールの概要

3. ハードウェアの構成

TPLスニファには、両側の側面に一連のコネクタがあります。片側はETPLバス接続専用で、反対側に他のすべてのコネクタがあります。これら両側は相互にガルバニック絶縁されています。 ETPLバス・コネクタは、ハウジング上の他のすべてのアクセス可能なポイントから絶縁されています。

3.1 ETPLバスへの接続

ETPLコネクタはハウジングの片側にあり、極性の+と-の表示とともに、TPL_INおよびTPL_OUTと記されています。正しい極性に接続することは、スニファが適切に機能するために不可欠であり、これは大抵の場合、スニファリングされるシステムにとっても同様です。

一方で、INとOUTという用語の使用は慣習に倣っており、2つのコネクタはTPLスニファ内で電気的に並列接続されています。これらは物理的に全く同じものであるため、特定のユース・ケースにおけるワイヤの接続を容易にします。たとえば、デイジー・チェーン接続の場合、元のETPLバスを切断し、両端をTPLスニファの各コネクタに接続する必要があります。他にも、ETPLバスにTPLスニファへの接続に使用できる差動端が1つしかない場合などでは、極性さえ間違っていなければ、TPL_INコネクタとTPL_OUTコネクタ間で相違はありません。

原則として、元のETPLバスからスタブを作成する場合には、その長さをできるだけ短くする必要があります。

3.2 オプションのETPLバス負荷

TPLスニファは、デフォルトでETPLバスへの負荷が最小限となるように設計されています。そのため、終端インピーダンスは一切付加されず、バス側から見た差動負荷は、1:1比のT1絶縁トランスによって高電圧側に反射されるMC33664の入力インピーダンスの負荷となります。

デフォルト以外のインターフェースを使用する場合は、PCBで次の設定を行うことができます。

- 標準の150 Ωの終端を用いる場合は、裏面にある2つのジャンパ

JP1とJP2を(はんだで)閉じる必要があります。 - PCBの表面には、TPLバス・インターフェースのさまざまな負荷に対応するために、追加コンポーネント用の実装領域が設けられています。これらは、

R13(デフォルトでは非実装)、R14、R15(デフォルトで0 Ω)になります。

3.3 電源およびデータの接続

ケースのETPLコネクタと反対側の面に、TPLスニファで使用可能な他のすべてのコネクタがあります。

- グランド・バナナ・プラグ:必要に応じて、TPLスニファのグランドを別の電位に接続するために使用されます。回路図では

J5と表示されています。使用例によっては、TPLスニファ、電源、ロジック・アナライザ、および関連するPCを含むシステム全体が、電気的フローティング・ブロックとなる場合があります。このコネクタを使用すると、システム(たとえば、TPLスニファや、そのグランドがTPLスニファのグランドに接続されているその他のシステム)のグランド電位を、別の任意の電位、すなわち保護アースまたは車両のシャーシ・グランド (KL31) に設定することができます。 - データ出力8ピンコネクタ:バッファされたSPI信号をロジック・アナライザに出力します。回路図では

J3と表示されています。 - パワーオンLEDインジケータUM11650:この文書に記載されているすべての情報は、法的免責事項の対象となります。© NXP B.V. 2021. All rights reserved. ユーザー・マニュアルRev. 1 - 2021年7月29日 7 / 14 NXP Semiconductors UM11650 KIT-TPLSNIFEVBツール

- USB micro-Bコネクタ:5.0 V電源に接続します。回路図では

J4と表示されています。

3.4 ロジック・アナライザへの接続

データ出力コネクタ (J3) は、ロジック・アナライザへのインターフェースとして、SPI形式に変換されたTPLメッセージの転送に使用される8ピン4x2オス・コネクタです。

信号はすべて、TPLスニファ(出力側)からロジック・アナライザ(入力側)への一方向に流れます。

TPLスニファは、シグナル・インテグリティを損なうことなくロジックとタイミングの情報を維持できる状態で、ロジック・アナライザへのケーブル接続長を最大2 mと比較的長めにできるよう設計されています。

これは、次の2つの規則がどちらも満たされている場合にのみ適用されます。

- 接続に使用するケーブルは、特性インピーダンスが100 Ωのものである必要があります。これは、標準のIDCリボン・ケーブルに通常見られるインピーダンスです。

- ケーブルのロジック・アナライザ側には、オシロスコープからのHigh-Z入力(例:15 pF || 1 ΜΩ、またはより良好な5 pF || 10 ΜΩ)やロジック・アナライザからのデジタル入力(例:10 pF || 2 ΜΩ)などの高インピーダンス終端のみを取り付けます。

これらの規則に従わない場合、ケーブル長が十分に短く(15 cm未満)、ケーブルの反射を無視できる場合を除き、TPLスニファの正しい動作は保証されません。

シグナル・インテグリティの確保とEMIの低減のために、表Xに示すピン配置を使用してデータ・ラインとグランド電位をインターリーブします。

TPLスニファのデータ出力ラインとETPL入力は、ESD抑制デバイスによって内部で保護されています。ただし、その場合でも、TPLスニファの取り扱いおよび使用時には標準的な静電気対策を講じる必要があります。

次の表に、データ出力コネクタのピン配置を示します。

| ピン | 信号 | 説明 |

|---|---|---|

| 1 | INTB | SPI割込み信号 |

| 2 | GND | グランド |

| 3 | RXCLK | SPIバス・クロック |

| 4 | GND | グランド |

| 5 | RXDATA | SPIバス・データ |

| 6 | GND | グランド |

| 7 | RXCSB | SPIチップ・セレクト |

| 8 | GND | グランド |

付属の8ピン接続ケーブルは、青いワイヤ(NXPのロゴがある側)を上に、黒いワイヤを下にして、ANALYZERコネクタに差し込んでください。

3.5 Saleaeロジック・アナライザとのインターフェース

付属の8ピン・コネクタ・ケーブルは、Saleae Logic 8およびLogic Pro 8/16アナライザ・シリーズの入力コネクタに取り付けます。Saleaeロジック・アナライザを接続するには、青いワイヤ(Saleaeのロゴがある側)を上に、黒いワイヤを下にしてケーブルを差し込んでください。

Saleaeでは、取得した信号をデコードするのに役立つソフトウェア・インターフェースを製品とともに提供しています。詳細については、Saleaeウェブサイトをご覧ください。

TPLフレームをデコードできるようにする、Saleaeロジック・アナライザ・ソフトウェア向けのプラグインおよび拡張機能も利用可能です。詳細については、セクション4を参照してください。

3.6 TPLスニファへの給電

TPLスニファには、通常はパワー・バンクまたはコンピュータに接続されたUSB ケーブルから、USB micro-Bコネクタ(J4、PWRと表記)を介して、50 mA(平均)および150 mA(ピーク)の5.0 Vを給電できます。

3.7 パワー・バンクのキープアライブ機能

キープアライブ機能の目的は、多くの民生用USBパワー・バンクに搭載されている自動切断機能の作動を防止することです。このような切断は、TPLスニファ回路単独での消費電力が10 mA~20 mAの範囲に制限されているために発生する傾向があります。そのため、スニファは、5.8秒間にわたって、20%のデューティ・サイクルで150 mAの内部消費電力を追加で有効にします(すべての値は目安です)。これは、ほとんどのパワー・バンクの通電を維持するのに十分な負荷をシミュレートしています。

パワー・バンクでTPLスニファに給電した直後にパワーオンLEDインジケータが消灯する場合は、別のモデルのパワー・バンクを試すことを検討してください。

4. ソフトウェアの入手

4.1 Saleaeロジック・ソフトウェア用TPLデコーダ・ツール

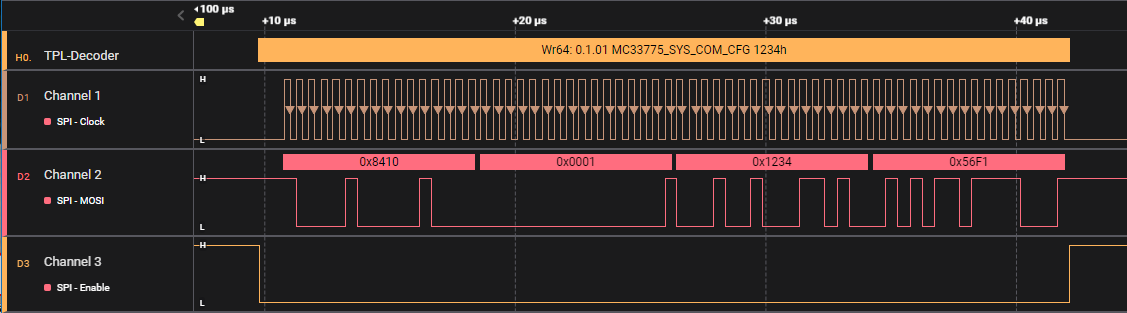

TPLデコーダは、Saleaeロジック・ソフトウェア用のハイ・レベル・アナライザ (HLA) 拡張機能です。これは、複数の物理層でNXPのTPLプロトコルをデコードするのに役立ちます。

このツールは、NXPのBMS通信デコーダ・エコシステムの一部でもあり、エレクトリカル・トランスポート・プロトコル・リンク (ETPL) 信号の取得を容易にするKIT-TPLSNIFEVBハードウェア・ボードと連携して動作できます。

4.2 パッケージの内容

ダウンロード可能なパッケージには、TPLデコーダ・インストーラのほかに、リリース・ノートとソフトウェア・コンテンツ・レジスタ (SCR) ファイルが含まれています。最新バージョンでカバーされている対応デバイスと物理層の詳細については、リリース・ノートのファイルを参照してください。

4.3 前提条件

TPLデコーダは、Saleaeロジック・ソフトウェア用のハイ・レベル・アナライザ (HLA) 拡張機能です。したがって、TPLデコーダをインストールする前に、推奨バージョンのSaleaeロジック・ソフトウェア(リリース・ノートのファイルを参照)をインストールしておく必要があります。Saleaeのウェブサイトにアクセスして、Saleaeロジック・ソフトウェアをダウンロードしてください。

4.4 インストール

インストール手順については、リリース・ノートのファイルを参照してください。

4.5 使用

TPLデコーダの使用の手引きは、Saleaeロジック・ソフトウェアの[Extensions(拡張機能)]メニューにある[TPL Decoder(TPLデコーダ)]をクリックすることで直接入手できます。