車載ネットワーク・プロセッシング向けS32Gリファレンス・デザイン・ボード3のスタート・ガイド

このドキュメントの内容

-

パッケージの内容

-

ソフトウェアの入手

-

接続

-

実行

サインイン 進行状況を保存するには アカウントをお持ちでない方 アカウントを作成する。

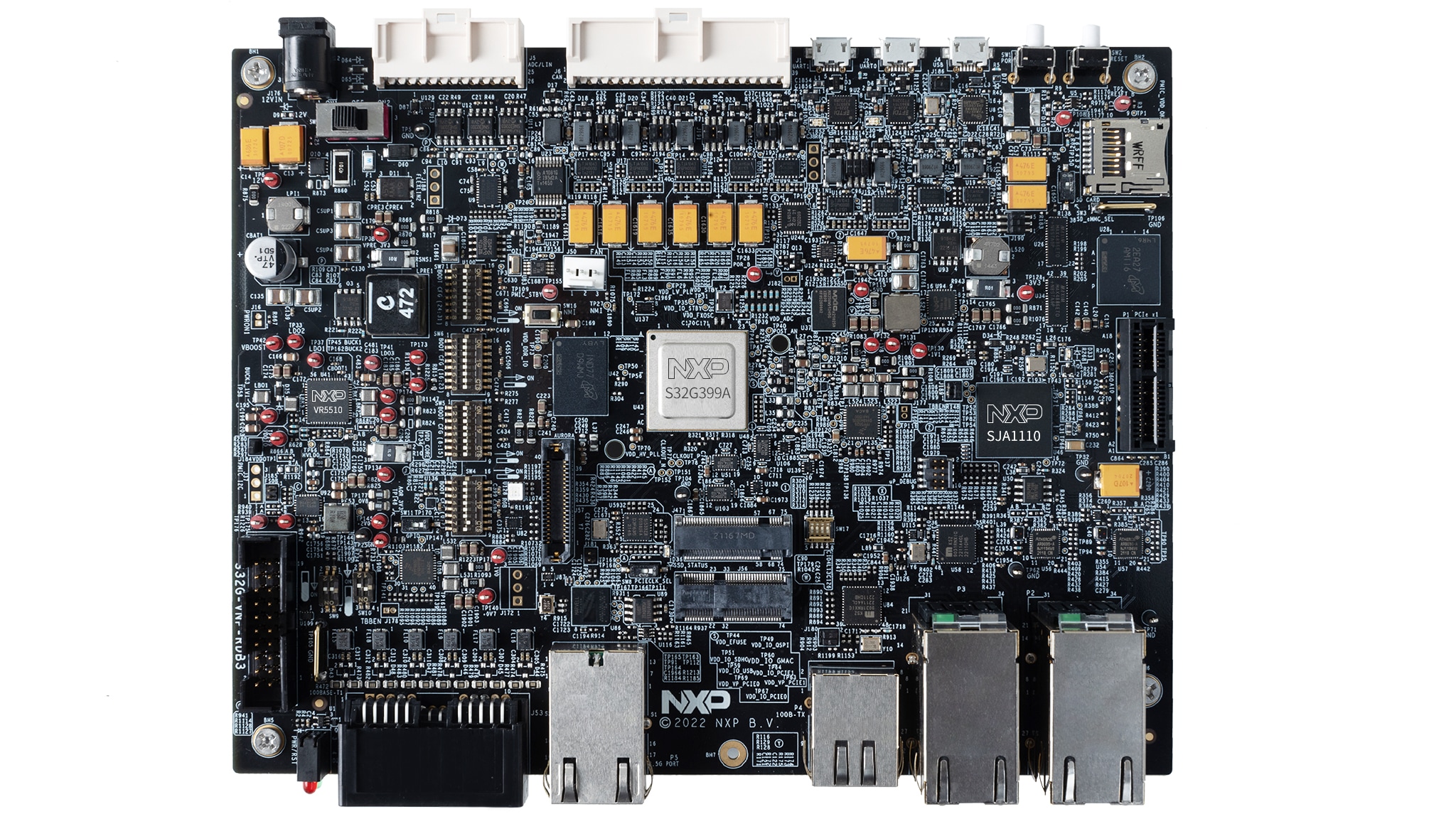

お客様の S32G3車載ネットワーキング・リファレンス・デザイン

1. パッケージの内容

1.1 車載ネットワーク・プロセッシング向けS32G-VNP-RDB3リファレンス・デザイン・ボードについて

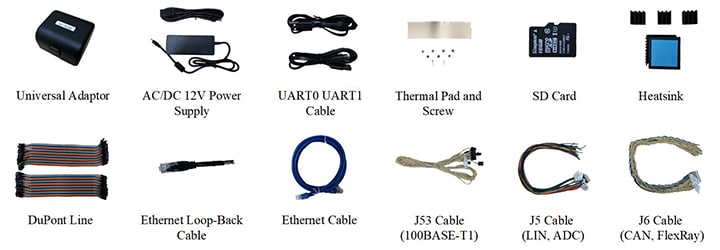

1.2 ボード・キット一式について

2. ソフトウェアの入手

車載ソフトウェア・パッケージ・マネージャの使用方法について

2.1 コンソール用のターミナル・エミュレータをインストールする

Tera Term、Puttyなど、使い慣れたターミナル・エミュレータをインストールします。

Tera Term 2.3の使用をお勧めします。Tera Termは、UTF-8プロトコルをサポートするオープン・ソースの無料ソフトウェア・ターミナル・エミュレータです。TTSSHはSSH2プロトコルをサポートするようになりました(元のバージョンはSSH1をサポートしています)。

Tera Termのダウンロード2.2 FTDI CDM WHQLドライバをインストールする

FTDI CDM v2.12.28 WHQLドライバは、FTDIチップからのシリアル設定のために使用されます。

FTDI CDMドライバのダウンロード3. 接続

S32G-VNP-RDB3ボードの動作テストを行いましょう。

3.1 SDカードを接続する

SDカードには工場出荷時にLinux BSPイメージがプリロードされています。SDカードをS32G-VNP-RDB3ボードの対応スロットに差し込んでください。

3.2 UARTケーブルを接続する

UARTケーブルのMicro-ABインターフェースを使用して、S32G-VNP-RDB3のUART0ポートに接続します。

UARTケーブルのtype Aインターフェースを使用してPCに接続します。

3.3 12 V電源を接続する

S32G-VNP-RDB3の12 V電源ジャックに電源を接続します。

4. 実行

4.1 コンソールをセットアップする

- ターミナル・エミュレータでコンソールを開きます。

- PCの「デバイス・マネージャ」に表示されるシリアル・ポートを選択し、[OK]をクリックします。

- [Setup(設定)]>[Serial Port(シリアル・ポート)]の順に選択し、ボーレートとして

115200を選択します

4.2 ボードの電源をオンにする

S32G-VNP-RDB3ボードの左側にある電源スイッチSW15をオンに切り替えます。左側というのは、1.1の画像と同じ方向から見たときの左側です

4.3 Linux BSPを実行する

Linux BSPはSDカードから自動的に実行されます。

Tera Termのコンソール・ディスプレイに、Linux BSPの実行ログが表示されます。

LLCE CAN/LIN MCALドライバの統合

高レベルのコード構造

Low Latency Communication Engine (LLCE) 1.0.0ドライバはS32DS 3.4環境に統合されていないため、ここではLLCE CAN/LIN MCALドライバをS32DSに簡単に統合する方法をご紹介します。

ソフトウェア・パッケージの構造:

ハードウェアとソフトウェアの要件

| Windows OSとシリアル・コンソールを搭載したホストPC | ||

|---|---|---|

| S32G-VNP-RDB3 REV C/D |

- |

|

| LLCEデモ・コード | ||

| リアルタイム・ドライバ (RTD) 1.0.0 | ||

| Low Latency Communication Engine (LLCE) 1.0.0 | ||

| S32 Design Studio for S32 Platform(LLCEプロジェクトのビルド) | ||

| S32 Design Studio for S32 Platform(LLCE用のMCAL設定) | ||

S32G-VNP-RDB3の接続

LLCE CAN/LINコネクタとUART0コネクタを接続し、S32G-VNP-RDB3の電源をオンにします。

S32DSでの新規プロジェクトの作成

S32 Design Studio for S32 platformを起動して、[File(ファイル)]>[New S32DS Application Project(新規S32DSアプリケーション・プロジェクト)]の順に選択します。

[Project name(プロジェクト名)]でS32G274A_Rev2_Cortex-M7を選択して、[Next(次へ)]をクリックします。

Cortex-M7_0のみを選択し、[SDKs]としてRTD1.0.0を選択したら、[Finish(完了)]をクリックします。

プロジェクトを右クリックし、[New(新規作成)]>[Source Folder(ソース・フォルダ)]の順に選択して、llceという名前のフォルダを作成します。

LLCE CAN/LIN関連のソース・コードをllceフォルダにコピーし 、main.cを置き換えて、LLCE CAN/LIN関連のソース・コードをプロジェクトに統合します。

プロジェクトを右クリックし、[Properties(プロパティ)]>[C/C++ Build(C/C++ビルド)]>[Settings(設定)]>[Standard S32DS C Compiler(標準S32DS Cコンパイラ)]>[Include(含める)]の順に選択して、次のパスを追加します。

"${ProjDirPath}/llce\can_lin_common"

"${ProjDirPath}/llce\platform_common\firmware_loading"

"${ProjDirPath}/llce\platform_common\platform_init"

"${ProjDirPath}/llce\plugins\Rte_TS_T40D11M10I0R0\src"

"${ProjDirPath}/llce\plugins\Rte_TS_T40D11M10I0R0\include"

"${ProjDirPath}/llce\plugins\Can_43_LLCE_TS_T40D11M10I0R0\src"

"${ProjDirPath}/llce\plugins\Can_43_LLCE_TS_T40D11M10I0R0\include"

"${ProjDirPath}/llce\plugins\CanIf_TS_T40D11M10I0R0\include"

"${ProjDirPath}/llce\plugins\Lin_43_LLCE_TS_T40D11M10I0R0\src"

"${ProjDirPath}/llce\plugins\Lin_43_LLCE_TS_T40D11M10I0R0\include"

"${ProjDirPath}/llce\plugins\LinIf_TS_T40D11M10I0R0\include"

"${ProjDirPath}/llce\plugins\Os_TS_T40D11M10I0R0\include"

"${ProjDirPath}/llce\plugins\Os_TS_T40D11M10I0R0\src"

"${ProjDirPath}/llce\plugins\EcuM_TS_T40D11M10I0R0\src"

"${ProjDirPath}/llce\plugins\EcuM_TS_T40D11M10I0R0\include"

"${ProjDirPath}/llce\Tresos_output\include"

"${ProjDirPath}/llce\Tresos_output\src"Project_Settings > Linker_Files > linker_ram.ldのパスをたどります

.llce_boot_end、.can_43_llce_sharedmemory、.lin_43_llce_sharedmemoryの後ろに、(NOLOAD)を追加します

- さらに、

init_sramメモリ・ノードを次のように変更します。

[ConfigTools(設定ツール)]>[Clocks(クロック)]を開き、llce_can/linクロックを40 MHzに設定します

[ConfigTools(設定ツール)]>[Peripherals(ペリフェラル)]を開き、[OS component(OSコンポーネント)]からfreertosを追加します。

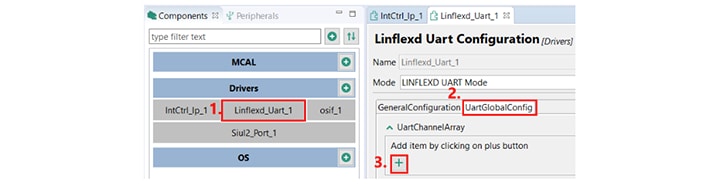

[ConfigTools(設定ツール)]>[Peripherals(ペリフェラル)]を開き、[Drivers component(ドライバ・コンポーネント)]からIntCtrl_IpおよびLinflexd_Uartドライバを追加します。

IntCtrl_Ipをダブルクリックし 、新しい割込みコントローラを追加してLINFLEXD0_ IRQnを有効にします

Linflexd_Uart_1をダブルクリックし 、新しいUartGlobalConfigをデフォルト設定で追加します。

[ConfigTools(設定ツール)]>[Pins(ピン)]を開いて、LINFlexD_0のピン(PC_09とPC_10)を設定し、[Update code(コードを更新)]をクリックします

プロジェクトを右クリックし、[Properties(プロパティ)]>[C/C++ Build(C/C++ビルド)]>[Settings(設定)]>[Target Processor(対象プロセッサ)]の順に選択して、[Float ABI(フロートABI)]を[FP instructions (hard)(FP命令(ハード))]に設定します。

プロジェクトを右クリックし、[Properties(プロパティ)]>[C/C++ Build(C/C++ビルド)]>[Settings(設定)]>[Preprocessor(プリプロセッサ)]の順に選択して、USING_OS_FREERTOSおよびENABLE_FPUを追加します

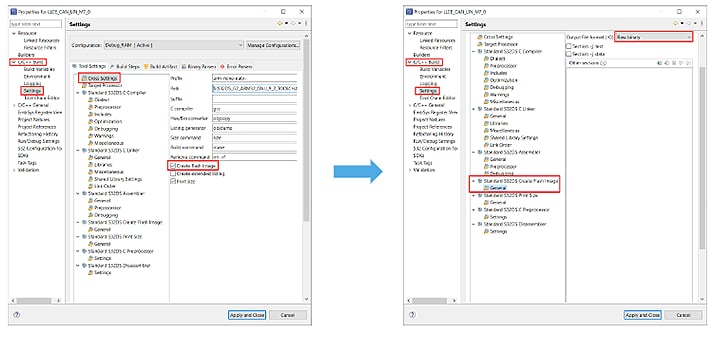

プロジェクトをビルドすると、LLCE_CAN_LIN_M7_0.elfが生成されます。以下の手順に従って、LLCE_CAN_LIN_M7_0.elfをLLCE_CAN_LIN_M7_0.binに変換します。

- プロジェクト・ファイルを右クリックして、[Properties(プロパティ)]>[C/C++ Build(C/C++ビルド)]>[Settings(設定)]>[Cross Settings(クロス設定)]を開きます。[Create flash Image(フラッシュ・イメージの作成)]オプションを有効にして、[Apply and Close(適用して閉じる)]をクリックします

- プロジェクト・ファイルをもう一度右クリックし、[Properties(プロパティ)]>[C/C++ Build(C/C++ビルド)]>[Settings(設定)]>[Standard S32DS Create Flash Image(標準S32DSフラッシュ・イメージの作成)]を開きます。出力ファイル形式を

Raw binary(Rawバイナリ)に変更して、[Apply and Close(適用して閉じる)]をクリックします - プロジェクトのリビルド

S32DS 3.4 IVTツールに基づいてLLCE_CAN_LIN_M7_0_IVT.binを生成します。

- [DCD]を選択し、スクリプト・ディレクトリを追加します

- [Application bootloader(アプリケーション・ブートローダ)]を選択し、ディレクトリを追加します

- [RAM start pointer(RAMスタート・ポインタ)] 、[RAM entry pointer(RAMエントリ・ポインタ)] 、[Codelength(コード長)]に入力します

- [Align(位置合わせ)]ボタンをクリックします

- [Export Image(イメージのエクスポート)]をクリックして、「blob」バイナリを保存します

- [Boot Target(ブート対象)]で

M7_0を選択します - [Boot device type(ブート・デバイスの種類)]で

[QuadSPI Serial Flash(QuadSPIシリアル・フラッシュ)]を選択します - [Export Blob Image(Blobイメージのエクスポート)]をクリックし、バイナリを

LLCE_CAN_LIN_M7_0_IVT.binという名前で保存します

LCCE CAN/LINテスト

S32G-VNP-RDB3をシリアル・ブート・モードに設定するには、SW9 [0:1]とSW10 [0:1]の両方をOFF:OFFに設定します

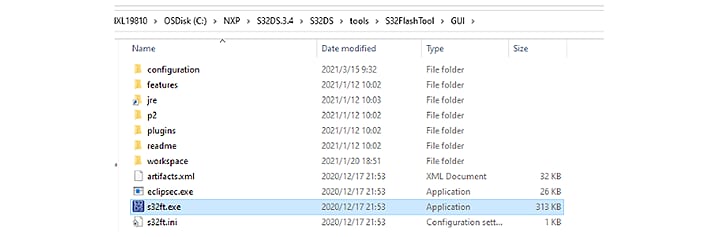

ボードの電源をオンにして、S32DS 3.4インストール・フォルダ内にあるs32ft.exeフラッシュ・ツールを開きます。

フラッシュ・ツールを使用して、LLCE_CAN_LIN_M7_0_IVT.binをQSPI NORフラッシュにアップロードします。

ターゲット:S32Gxxx。アルゴリズム: MX25UW51245G。

COM:ホストPCのUART0に対応するCOM番号を確認してください。

[Upload target and algorithm to hardware(ターゲットとアルゴリズムをハードウェアにアップロード)]をクリックして、ハードウェアを初期化します。[Upload binary to device(バイナリをデバイスにアップロード)]をクリックし、開始アドレスを0x00000に設定した後で、LLCE_CAN_LIN_M7_0_IVT.binをQSPIにロードし、[OK]をクリックします。

S32G-VNP-RDB2をQSPIブート・モードに設定します。それには、SW9 [0:1]をOFF:OFFに設定し、SW10 [0:1]をON:OFF(RCONからのブートの場合)に設定し、さらにSW4 [6:8]をOFF:OFF:OFF(QSPIフラッシュからのブート)に設定します。

LLCE CAN0をLLCE CAN1に接続し、LLCE LIN2(リーダ)をLLCE LIN3(フォロワ)に接続します。

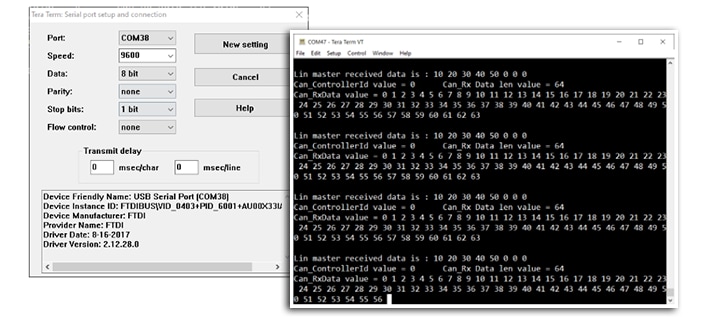

シリアル・コンソール(Tera Termなど)を開き、ホストPCのUART0のビットレートを9600に設定します。ボードの電源をオンにして、コンソールの出力を待ちます。

S32G-VNP-RDB3のS32G274A Arm® Cortex®-M7コアのlwIPおよびFreeRTOSを使用して、PFEイーサネット・インターフェースを有効にします

S32GのM7コアのlwIP (Lightweight IP) スタックとFreeRTOSを使用して、パケット転送エンジン (PFE) イーサネット・インターフェースを有効化するサンプル・プロジェクトです。これはS32 Design Studioプロジェクトのサンプルであり、主にLWIPとPFE MCALドライバで構成されています。

PFEイーサネット・インターフェースの有効化

S32 Design Studio for S32 platformを起動し、[Existing Projects into Workspace(既存プロジェクトをワークスペースにインポート)]オプションを使用してサンプル・プロジェクトをインポートします 。

ロードが終わったら、[Build Project(プロジェクトをビルド)]オプションをクリックします。ビルドが完了したら、結果を取得します。

SRAMをクリアするために、dcd_sram_init.bin DCDファイルを選択して、IVTイメージを作成します。

アプリケーション・ブート・イメージのRAMスタート・ポインタを0x34000000に設定し、RAMエントリ・ポインタを0x34001000に設定します 。

次にテスト用として、最終的なblobイメージをSDカードに書き込みます。

Linux BSP実行ログ

Linux BSP実行ログ

U-Boot 2019.04+ga53a9fa1e9 (Aug 31 2020 - 05:07:39 +0000)

CPU: NXP S32G274A rev. 2.1.0

Reset cause: Power-On Reset

Model: NXP S32G27x

Board: NXP S32G274A-RDB

DRAM: 512 MiB

CA53 core 1 running.

CA53 core 2 running.

CA53 core 3 running.

All (4) cores are up.

MMC: FSL_SDHC: 0

Loading Environment from MMC... OK

Using external clock for PCIe0

Configuring PCIe0 as RootComplex(x2)

Using external clock for PCIe1

Frequency 125Mhz configured for PCIe1

Configuring PCIe1 as SGMII(x2) [XPCS0 2.5G, XPCS1 OFF]

PCIe0: Failed to get link up

Pcie0: LINK_DBG_1: 0x00000000, LINK_DBG_2: 0x00000800 (expected 0x000000d1)

DEBUG_R0: 0x0052a300, DEBUG_R1: 0x08200000

PCIe1: Not configuring PCIe, PHY not configured

In: serial

Out: serial

Err: serial

Net: EQOS phy: rgmii fixed-link

Warning: eth_eqos (eth0) using random MAC address - 8a:54:02:e5:1f:1a

eth0: eth_eqos PFE: emac0: sgmii emac1: none emac2: rgmii

Warning: eth_pfeng using MAC address from ROM

, eth1: eth_pfeng

Hit any key to stop autoboot: 0

PFE: emac0: sgmii emac1: none emac2: rgmii

PFE: emac0: sgmii emac1: none emac2: rgmii

switch to partitions #0, OK

mmc0 is current device

9158664 bytes read in 400 ms (21.8 MiB/s)

Booting from mmc ...

9158664 bytes read in 385 ms (22.7 MiB/s)

27786 bytes read in 7 ms (3.8 MiB/s)

## Flattened Device Tree blob at 83e00000

Booting using the fdt blob at 0x83e00000

Loading Device Tree to 000000009fafa000, end 000000009fb03c89 ... OK

Reserving 2048k off the top of [c0000000-dfffffff] for protected RAM

DT: Enabling PFE

DT: Enabling PFE_EMAC_0

DT: pfe0 set to 00:01:be:be:ef:11

DT: Disabling PFE_EMAC_1

DT: Enabling PFE_EMAC_2

DT: pfe2 set to 00:01:be:be:ef:33

DT: Enabling GMAC

Starting kernel ...

[ 0.000000] Booting Linux on physical CPU 0x0000000000 [0x410fd034]

[ 0.000000] Linux version 4.19.59-rt24+ged566620fe59 (oe-user@oe-host) (gcc version 9.2.0 (GCC)) #1 SMP PREEMPT Tue Aug 25 10:01:34 UTC 2020

[ 0.000000] Machine model: Freescale S32G275

[ 0.000000] earlycon: linflex0 at MMIO 0x00000000401c8000 (options '115200n8')

[ 0.000000] bootconsole [linflex0] enabled

[ 0.000000] cma: Reserved 256 MiB at 0x00000000cfc00000

[ 0.000000] random: get_random_bytes called from start_kernel+0x94/0x3f0 with crng_init=0

[ 0.000000] percpu: Embedded 21 pages/cpu s48920 r8192 d28904 u86016

[ 0.000000] Detected VIPT I-cache on CPU0

[ 0.000000] CPU features: enabling workaround for ARM erratum 845719

[ 0.000000] CPU features: detected: Kernel page table isolation (KPTI)

[ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 900415

[ 0.000000] Kernel command line: console=ttyLF0,115200 root=/dev/mmcblk0p2 rootwait rw earlycon nohz=off coherent_pool=64M

[ 0.000000] Dentry cache hash table entries: 524288 (order: 10, 4194304 bytes)

[ 0.000000] Inode-cache hash table entries: 262144 (order: 9, 2097152 bytes)

[ 0.000000] software IO TLB: mapped [mem 0xcbc00000-0xcfc00000] (64MB)

[ 0.000000] Memory: 3151736K/3651584K available (6078K kernel code, 368K rwdata, 2024K rodata, 448K init, 215K bss, 237704K reserved, 262144K cma-reserved)

[ 0.000000] rcu: Preemptible hierarchical RCU implementation.

[ 0.000000] Tasks RCU enabled.

[ 0.000000] NR_IRQS: 64, nr_irqs: 64, preallocated irqs: 0

[ 0.000000] GICv3: Distributor has no Range Selector support

[ 0.000000] GICv3: no VLPI support, no direct LPI support

[ 0.000000] ITS: No ITS available, not enabling LPIs

[ 0.000000] GICv3: CPU0: found redistributor 0 region 0:0x0000000050880000

[ 0.000000] arch_timer: cp15 timer(s) running at 5.00MHz (virt).

[ 0.000000] clocksource: arch_sys_counter: mask: 0xffffffffffffff max_cycles: 0x127350b88, max_idle_ns: 440795202120 ns

[ 0.000005] sched_clock: 56 bits at 5MHz, resolution 200ns, wraps every 4398046511100ns

[ 0.008351] Console: colour dummy device 80x25

[ 0.012468] Calibrating delay loop (skipped), value calculated using timer frequency.. 10.00 BogoMIPS (lpj=20000)

[ 0.022689] pid_max: default: 32768 minimum: 301

[ 0.027433] Mount-cache hash table entries: 8192 (order: 4, 65536 bytes)

[ 0.033989] Mountpoint-cache hash table entries: 8192 (order: 4, 65536 bytes)

[ 0.065168] ASID allocator initialised with 32768 entries

[ 0.078243] rcu: Hierarchical SRCU implementation.

[ 0.106732] smp: Bringing up secondary CPUs ...

[ 0.151077] Detected VIPT I-cache on CPU1

[ 0.151111] GICv3: CPU1: found redistributor 1 region 0:0x00000000508a0000

[ 0.151147] CPU1: Booted secondary processor 0x0000000001 [0x410fd034]

[ 0.191123] Detected VIPT I-cache on CPU2

[ 0.191151] GICv3: CPU2: found redistributor 100 region 0:0x00000000508c0000

[ 0.191179] CPU2: Booted secondary processor 0x0000000100 [0x410fd034]

[ 0.231190] Detected VIPT I-cache on CPU3

[ 0.231209] GICv3: CPU3: found redistributor 101 region 0:0x00000000508e0000

[ 0.231225] CPU3: Booted secondary processor 0x0000000101 [0x410fd034]

[ 0.231310] smp: Brought up 1 node, 4 CPUs

[ 0.287500] SMP: Total of 4 processors activated.

[ 0.292184] CPU features: detected: GIC system register CPU interface

[ 0.298610] CPU features: detected: 32-bit EL0 Support

[ 0.306755] CPU: All CPU(s) started at EL1

[ 0.310521] alternatives: patching kernel code

[ 0.315555] devtmpfs: initialized

[ 0.322790] clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 7645041785100000 ns

[ 0.332215] futex hash table entries: 1024 (order: 4, 65536 bytes)

[ 0.344747] pinctrl core: initialized pinctrl subsystem

[ 0.350441] NET: Registered protocol family 16

[ 0.355564] vdso: 2 pages (1 code @ (____ptrval____), 1 data @ (____ptrval____))

[ 0.392905] DMA: preallocated 65536 KiB pool for atomic allocations

[ 0.398961] Serial: AMBA PL011 UART driver

[ 0.418631] HugeTLB registered 2.00 MiB page size, pre-allocated 0 pages

[ 0.430451] vgaarb: loaded

[ 0.433060] SCSI subsystem initialized

[ 0.436769] usbcore: registered new interface driver usbfs

[ 0.442312] usbcore: registered new interface driver hub

[ 0.447384] usbcore: registered new device driver usb

[ 0.453176] pps_core: LinuxPPS API ver. 1 registered

[ 0.457793] pps_core: Software ver. 5.3.6 - Copyright 2005-2007 Rodolfo Giometti

[ 0.467201] PTP clock support registered

[ 0.471596] clocksource: Switched to clocksource arch_sys_counter

[ 0.484113] NET: Registered protocol family 2

[ 0.488818] tcp_listen_portaddr_hash hash table entries: 2048 (order: 3, 32768 bytes)

[ 0.496354] TCP established hash table entries: 32768 (order: 6, 262144 bytes)

[ 0.503842] TCP bind hash table entries: 32768 (order: 7, 524288 bytes)

[ 0.510687] TCP: Hash tables configured (established 32768 bind 32768)

[ 0.517015] UDP hash table entries: 2048 (order: 4, 65536 bytes)

[ 0.522981] UDP-Lite hash table entries: 2048 (order: 4, 65536 bytes)

[ 0.529527] NET: Registered protocol family 1

[ 0.533974] RPC: Registered named UNIX socket transport module.

[ 0.539558] RPC: Registered udp transport module.

[ 0.544245] RPC: Registered tcp transport module.

[ 0.548927] RPC: Registered tcp NFSv4.1 backchannel transport module.

[ 0.555533] Unpacking initramfs...

[ 0.558752] Initramfs unpacking failed: junk in compressed archive

[ 0.608954] Freeing initrd memory: 98304K

[ 0.614005] workingset: timestamp_bits=62 max_order=20 bucket_order=0

[ 0.620989] fuse init (API version 7.27)

[ 0.625222] Block layer SCSI generic (bsg) driver version 0.4 loaded (major 250)

[ 0.632285] io scheduler noop registered

[ 0.636187] io scheduler deadline registered

[ 0.640470] io scheduler cfq registered (default)

[ 0.645129] io scheduler mq-deadline registered

[ 0.649637] io scheduler kyber registered

[ 0.654050] s32g275-siul2-pinctrl 4009c240.siul2-pinctrl0: initialized s32 pinctrl driver

[ 0.662296] s32g275-siul2-pinctrl 44010400.siul2-pinctrl1: initialized s32 pinctrl driver

[ 0.677252] s32gen1-pcie 40400000.pcie: Configuring as RootComplex

[ 0.683162] s32gen1-pcie 40400000.pcie: Allocated line 0 for interrupt 66 (msi)

[ 0.690394] s32gen1-pcie 40400000.pcie: host bridge /pcie@40400000 ranges:

[ 0.697258] s32gen1-pcie 40400000.pcie: IO 0x5800003000..0x5800012fff -> 0x00000000

[ 0.705159] s32gen1-pcie 40400000.pcie: MEM 0x5800013000..0x5840012fff -> 0x00013000

[ 1.711594] s32gen1-pcie 40400000.pcie: Phy link never came up

[ 2.715593] s32gen1-pcie 40400000.pcie: Phy link never came up

[ 2.721209] s32gen1-pcie 40400000.pcie: PCI host bridge to bus 0000:00

[ 2.727606] pci_bus 0000:00: root bus resource [bus 00-ff]

[ 2.733071] pci_bus 0000:00: root bus resource [io 0x0000-0xffff]

[ 2.739231] pci_bus 0000:00: root bus resource [mem 0x5800013000-0x5840012fff] (bus address [0x00013000-0x40012fff])

[ 2.753103] pci 0000:00:00.0: BAR 0: assigned [mem 0x5800100000-0x58001fffff 64bit pref]

[ 2.760871] pci 0000:00:00.0: BAR 6: assigned [mem 0x5800020000-0x580002ffff pref]

[ 2.768409] pci 0000:00:00.0: PCI bridge to [bus 01-ff]

[ 2.773976] pcieport 0000:00:00.0: Signaling PME with IRQ 92

[ 2.779439] pcieport 0000:00:00.0: AER enabled with IRQ 92

[ 2.785178] s32gen1-pcie 44100000.pcie: u-boot did not initialize PCIE PHY; is u-boot compiled with PCIE support?

[ 2.796282] 401c8000.serial: ttyLF0 at MMIO 0x401c8000 (irq = 30, base_baud = 7812500) is a FSL_LINFLEX

[ 2.807429] console [ttyLF0] enabled

[ 2.807429] console [ttyLF0] enabled

[ 2.814711] bootconsole [linflex0] disabled

[ 2.814711] bootconsole [linflex0] disabled

[ 2.823540] 401cc000.serial: ttyLF1 at MMIO 0x401cc000 (irq = 31, base_baud = 7812500) is a FSL_LINFLEX

[ 2.833381] 402bc000.serial: ttyLF2 at MMIO 0x402bc000 (irq = 57, base_baud = 7812500) is a FSL_LINFLEX

[ 2.847880] libphy: Fixed MDIO Bus: probed

[ 2.852463] vcan: Virtual CAN interface driver

[ 2.857005] slcan: serial line CAN interface driver

[ 2.861981] slcan: 10 dynamic interface channels.

[ 2.866780] CAN device driver interface

[ 2.871567] flexcan 401b4000.flexcan: device registered (reg_base=(____ptrval____), irq(s):

[ 2.880094] flexcan 401b4000.flexcan: 26

[ 2.884186] flexcan 401b4000.flexcan: 27

[ 2.888282] flexcan 401b4000.flexcan: 28

[ 2.892373] flexcan 401b4000.flexcan: 29

[ 2.896464] flexcan 401b4000.flexcan: )

[ 2.901043] flexcan 402a8000.flexcan: device registered (reg_base=(____ptrval____), irq(s):

[ 2.909570] flexcan 402a8000.flexcan: 49

[ 2.913662] flexcan 402a8000.flexcan: 50

[ 2.917758] flexcan 402a8000.flexcan: 51

[ 2.921849] flexcan 402a8000.flexcan: 52

[ 2.925943] flexcan 402a8000.flexcan: )

[ 2.930403] flexcan 402b2000.flexcan: device registered (reg_base=(____ptrval____), irq(s):

[ 2.938925] flexcan 402b2000.flexcan: 53

[ 2.943017] flexcan 402b2000.flexcan: 54

[ 2.947112] flexcan 402b2000.flexcan: 55

[ 2.951202] flexcan 402b2000.flexcan: 56

[ 2.955296] flexcan 402b2000.flexcan: )

[ 2.959458] e1000e: Intel(R) PRO/1000 Network Driver - 3.2.6-k

[ 2.965411] e1000e: Copyright(c) 1999 - 2015 Intel Corporation.

[ 2.972162] s32cc-dwmac 4033c000.ethernet: PTP uses main clock

[ 2.978119] s32cc-dwmac 4033c000.ethernet: no reset control found

[ 2.984348] s32cc-dwmac 4033c000.ethernet: phy mode set to RGMII

[ 2.990598] s32cc-dwmac 4033c000.ethernet: User ID: 0x10, Synopsys ID: 0x51

[ 2.997708] s32cc-dwmac 4033c000.ethernet: DWMAC4/5

[ 3.002776] s32cc-dwmac 4033c000.ethernet: DMA HW capability register supported

[ 3.010231] s32cc-dwmac 4033c000.ethernet: RX Checksum Offload Engine supported

[ 3.017681] s32cc-dwmac 4033c000.ethernet: TX Checksum insertion supported

[ 3.024693] s32cc-dwmac 4033c000.ethernet: Wake-Up On Lan supported

[ 3.031111] s32cc-dwmac 4033c000.ethernet: Enabled workarounds for s32g274a platform

[ 3.039012] s32cc-dwmac 4033c000.ethernet: Enable RX Mitigation via HW Watchdog Timer

[ 3.047005] s32cc-dwmac 4033c000.ethernet (unnamed net_device) (uninitialized): device MAC address b2:87:c5:05:03:51

[ 3.057732] s32cc-dwmac 4033c000.ethernet: Enabling HW TC (entries=256, max_off=256)

[ 3.065723] libphy: stmmac: probed

[ 3.069942] mdio_bus stmmac-0: MDIO device at address 4 is missing.

[ 3.076566] mdio_bus stmmac-0: MDIO device at address 5 is missing.

[ 3.083183] mdio_bus stmmac-0: MDIO device at address 6 is missing.

[ 3.089805] mdio_bus stmmac-0: MDIO device at address 7 is missing.

[ 3.096702] usbcore: registered new interface driver asix

[ 3.102259] usbcore: registered new interface driver ax88179_178a

[ 3.108505] usbcore: registered new interface driver cdc_ether

[ 3.114488] usbcore: registered new interface driver net1080

[ 3.120294] usbcore: registered new interface driver cdc_subset

[ 3.126368] usbcore: registered new interface driver zaurus

[ 3.132096] usbcore: registered new interface driver cdc_ncm

[ 3.137903] usbcore: registered new interface driver qmi_wwan

[ 3.143961] ehci_hcd: USB 2.0 'Enhanced' Host Controller (EHCI) Driver

[ 3.150624] ehci-pci: EHCI PCI platform driver

[ 3.155231] usbcore: registered new interface driver cdc_wdm

[ 3.161037] usbcore: registered new interface driver uas

[ 3.166502] usbcore: registered new interface driver usb-storage

[ 3.172716] usbcore: registered new interface driver option

[ 3.178429] usbserial: USB Serial support registered for GSM modem (1-port)

[ 3.199421] ci_hdrc ci_hdrc.0: EHCI Host Controller

[ 3.204545] ci_hdrc ci_hdrc.0: new USB bus registered, assigned bus number 1

[ 3.231610] ci_hdrc ci_hdrc.0: USB 2.0 started, EHCI 1.00

[ 3.237248] usb usb1: New USB device found, idVendor=1d6b, idProduct=0002, bcdDevice= 4.19

[ 3.245680] usb usb1: New USB device strings: Mfr=3, Product=2, SerialNumber=1

[ 3.253045] usb usb1: Product: EHCI Host Controller

[ 3.258024] usb usb1: Manufacturer: Linux 4.19.59-rt24+ged566620fe59 ehci_hcd

[ 3.265299] usb usb1: SerialNumber: ci_hdrc.0

[ 3.270158] hub 1-0:1.0: USB hub found

[ 3.274009] hub 1-0:1.0: 1 port detected

[ 3.279363] s32gen1-rtc 40060000.rtc: rtc core: registered s32gen1_rtc as rtc0

[ 3.287677] sdhci: Secure Digital Host Controller Interface driver

[ 3.293980] sdhci: Copyright(c) Pierre Ossman

[ 3.298424] sdhci-pltfm: SDHCI platform and OF driver helper

[ 3.335639] mmc0: SDHCI controller on 402f0000.usdhc [402f0000.usdhc] using ADMA

[ 3.343511] usbcore: registered new interface driver usbhid

[ 3.350217] usbhid: USB HID core driver

[ 3.354483] NET: Registered protocol family 10

[ 3.360292] Segment Routing with IPv6

[ 3.364089] sit: IPv6, IPv4 and MPLS over IPv4 tunneling driver

[ 3.370606] NET: Registered protocol family 17

[ 3.375154] can: controller area network core (rev 20170425 abi 9)

[ 3.381881] NET: Registered protocol family 29

[ 3.386451] can: raw protocol (rev 20170425)

[ 3.390809] can: broadcast manager protocol (rev 20170425 t)

[ 3.396588] can: netlink gateway (rev 20170425) max_hops=1

[ 3.396646] mmc0: new high speed SDHC card at address 5048

[ 3.408886] mmcblk0: mmc0:5048 SD16G 14.4 GiB

[ 3.413449] s32gen1-rtc 40060000.rtc: setting system clock to 2018-08-10 18:00:00 UTC (1533924000)

[ 3.424338] mmcblk0: p1 p2

[ 3.432587] EXT4-fs (mmcblk0p2): mounting ext3 file system using the ext4 subsystem

[ 3.564012] EXT4-fs (mmcblk0p2): recovery complete

[ 3.572759] EXT4-fs (mmcblk0p2): mounted filesystem with ordered data mode. Opts: (null)

[ 3.580548] VFS: Mounted root (ext3 filesystem) on device 179:2.

[ 3.586575] devtmpfs: mounted

[ 3.589629] Freeing unused kernel memory: 448K

[ 3.593954] Run /sbin/init as init process

INIT: version 2.88 booting

[ 3.712010] random: fast init done

Starting udev

[ 3.999267] udevd[797]: starting version 3.2.8

[ 4.008995] random: udevd: uninitialized urandom read (16 bytes read)

[ 4.016322] random: udevd: uninitialized urandom read (16 bytes read)

[ 4.022469] random: udevd: uninitialized urandom read (16 bytes read)

[ 4.057252] udevd[798]: starting eudev-3.2.8

[ 4.608718] pfeng: loading out-of-tree module taints kernel.

[ 4.639285] pfeng 46000000.pfe: pfeng, ethernet driver loading ...

[ 4.645189] pfeng 46000000.pfe: Found reserved memory at p0x83400000 size 0xc00000

[ 4.652905] pfeng 46000000.pfe: Cbus addr 0x46000000 size 0x1000000

[ 4.658939] pfeng 46000000.pfe: firmware-name: s32g_pfe_class.fw

[ 4.665015] pfeng 46000000.pfe: HIF channel 0 in SC mode

[ 4.670227] pfeng 46000000.pfe: pfe0 linked to EMAC 0

[ 4.675259] pfeng 46000000.pfe: HIF channel 2 in SC mode

[ 4.680547] pfeng 46000000.pfe: pfe2 linked to EMAC 2

[ 4.685586] pfeng 46000000.pfe: TX clocks for interface pfe2 installed

[ 4.692086] pfeng 46000000.pfe: HIF channels mask: 0x0005

[ 4.697477] pfeng 46000000.pfe: Interface selected: EMAC0: 0x4 EMAC1: 0xffffffed EMAC2: 0x8

[ 4.718907] pfeng 46000000.pfe: Firmware: s32g_pfe_class.fw [size: 166088 bytes]

[ 4.725991] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_platform_master.c:2718] INF: PFE CBUS p0x(____ptrval____) mapped @ v0x(____ptrval____)

[ 4.744578] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_platform_master.c:2769] INF: Detected per block IRQ mode (S32G)

[ 4.756488] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_platform_master.c:1381] INF: BMU1 buffer base: p0x(____ptrval____)

[ 4.770845] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_platform_master.c:1428] INF: BMU2 buffer base: p0x(____ptrval____) (2097152 bytes)

[ 4.786777] [/usr/src/debug/pfe/0.8.0-r0/git/sw/oal/.//src/oal_irq_linux.c:156] INF: register IRQ 85 by name 'PFE BMU IRQ'

[ 4.797626] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_bmu_csr.c:117] INF: BMU_EMPTY_INT (BMU @ p0x(____ptrval____)). Pool ready.

[ 4.810671] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_bmu_csr.c:117] INF: BMU_EMPTY_INT (BMU @ p0x(____ptrval____)). Pool ready.

[ 4.894305] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_platform_master.c:1779] INF: Firmware .elf detected

[ 4.905177] [/usr/src/debug/pfe/0.8.0-r0/git/sw/elf/src/elf.c:1379] INF: ELF_Open: File format: Elf32

[ 4.914375] [/usr/src/debug/pfe/0.8.0-r0/git/sw/elf/src/elf.c:1380] INF: ELF_Open: File endian: Alien (Big)

[ 4.924123] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_platform_master.c:1788] INF: Uploading CLASS firmware

[ 4.935472] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/src/pfe_pe.c:1480] INF: pfe_ct.h file version"d6aa29e94e07a9cfbf1ccebb03994057"

[ 4.950316] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/src/pfe_pe.c:1480] INF: pfe_ct.h file version"d6aa29e94e07a9cfbf1ccebb03994057"

[ 4.964705] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/src/pfe_pe.c:1480] INF: pfe_ct.h file version"d6aa29e94e07a9cfbf1ccebb03994057"

[ 4.979092] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/src/pfe_pe.c:1480] INF: pfe_ct.h file version"d6aa29e94e07a9cfbf1ccebb03994057"

[ 4.993477] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/src/pfe_pe.c:1480] INF: pfe_ct.h file version"d6aa29e94e07a9cfbf1ccebb03994057"

[ 5.007866] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/src/pfe_pe.c:1480] INF: pfe_ct.h file version"d6aa29e94e07a9cfbf1ccebb03994057"

[ 5.022273] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/src/pfe_pe.c:1480] INF: pfe_ct.h file version"d6aa29e94e07a9cfbf1ccebb03994057"

[ 5.036663] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/src/pfe_pe.c:1480] INF: pfe_ct.h file version"d6aa29e94e07a9cfbf1ccebb03994057"

[ 5.051046] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/src/pfe_pe.c:1738] INF: [FW VERSION] 0.8.0, Build: Mar 31 2020, 11:41:35 (c768f3e), ID: 0x31454650

[ 5.064955] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/src/pfe_pe.c:1747] INF: [PE 0 MMAP]

[ 5.064955] DMEM Heap Base: 0x20001150 (11952 bytes)

[ 5.064955] PHY IF Base : 0x20000aac (288 bytes)

[ 5.084143] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_emac_csr.c:308] INF: The PHY mode selection is done using a HW interface. See the 'phy_intf_sel' signal.

[ 5.100102] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_emac_csr.c:308] INF: The PHY mode selection is done using a HW interface. See the 'phy_intf_sel' signal.

[ 5.115924] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_emac_csr.c:308] INF: The PHY mode selection is done using a HW interface. See the 'phy_intf_sel' signal.

[ 5.131597] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_platform_master.c:2149] INF: SAFETY instance created

[ 5.142830] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_platform_master.c:2163] INF: Watchdog instance created

[ 5.155192] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_platform_master.c:1913] INF: Routing table created, Hash Table @ p(____ptrval____), Pool @ p(____ptrva(65536 bytes)

[ 5.280190] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/src/pfe_l2br.c:643] INF: Fall-back bridge domain @ 0x20000a98 (class)

[ 5.293618] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_platform/hw/s32g/pfe_platform_master.c:2913] INF: Enabling the CLASS block

[ 5.364627] pfeng 46000000.pfe pfe0 (uninitialized): setting MAC addr: 00:01:be:be:ef:11

[ 5.372937] pfeng 46000000.pfe pfe0: registered

[ 5.400167] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_hif_drv/src/pfe_hif_drv_sc.c:320] INF: Attempt to register HIF client: pfe0

[ 5.411299] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_hif_drv/src/pfe_hif_drv_sc.c:385] INF: HIF client pfe0 id 0 registered

[ 5.422440] pfeng 46000000.pfe pfe0: Register HIF client pfe0 for logif (____ptrval____)

[ 5.430444] pfeng 46000000.pfe pfe2 (uninitialized): setting MAC addr: 00:01:be:be:ef:33

[ 5.438896] pfeng 46000000.pfe pfe2: registered

[ 5.468519] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_hif_drv/src/pfe_hif_drv_sc.c:320] INF: Attempt to register HIF client: pfe2

[ 5.479651] [/usr/src/debug/pfe/0.8.0-r0/git/sw/pfe_hif_drv/src/pfe_hif_drv_sc.c:385] INF: HIF client pfe2 id 1 registered

[ 5.490788] pfeng 46000000.pfe pfe2: Register HIF client pfe2 for logif (____ptrval____)

[ 5.498865] libphy: PFEng Ethernet MDIO: probed

[ 5.503428] mdio_bus PFEng Ethernet MDIO.pfe2: MDIO device at address 1 is missing.

[ 5.511055] mdio_bus PFEng Ethernet MDIO.pfe2: MDIO device at address 2 is missing.

[ 5.579136] loading NXP PHY driver: [autonomous mode]

[ 5.677591] sja1105pqrs spi1.0: Loading SJA1105P SPI driver

[ 5.682940] sja1105pqrs spi1.0: Detected device id is invalid: ffffffff

[ 5.689435] sja1105pqrs spi1.0: SJA1105P SPI Failed to read Device Id

[ 5.712578] EXT4-fs (mmcblk0p2): re-mounted. Opts: (null)

Fri Aug 28 01:21:01 UTC 2020

[ 5.995835] urandom_read: 3 callbacks suppressed

[ 5.995844] random: dd: uninitialized urandom read (512 bytes read)

INIT: Entering runlevel: 5

Configuring network interfaces... ifup: don't have all variables for eth0/inet

Starting syslogd/klogd: done

Starting random number generator daemon[ 6.197407] random: rngd: uninitialized urandom read (4 bytes read)

[ 6.203438] random: rngd: uninitialized urandom read (4 bytes read)

.

[ 6.211508] random: crng init done

[ 6.214604] random: 1 urandom warning(s) missed due to ratelimiting

Starting OpenBSD Secure Shell server: sshd

done.

Auto Linux BSP 1.0 s32g274ardb /dev/ttyLF0

s32g274ardb login:

S32G-VNP-RDB3のテスト用セットアップ

S32G-VNP-RDB3のテスト用セットアップ

使用するPFEインターフェースに応じて、適切なポートを接続し、ボードの電源をオンにしてテストを行います。

pingテストを実行し、接続を確認します。

serdesフォルダを展開して 、プロジェクト・ディレクトリに追加します。[Project Explorer(プロジェクト・エクスプローラ)内のフォルダを右クリックし、[Build path(ビルド・パス)]>[Add to (追加先)]>[Debug_RAM]の順に選択して、プロジェクトにserdesのソース・コードを含めます。

ボードの設定に合わせてserdesの初期化パラメータを変更します。

Eth_43_PFE_init()の前にserdes_init()を呼び出してください

serdes_init();

oal_mm_init(NULL);

Eth_43_PFE_Init(NULL_PTR);設計・リソース

サポート

トレーニング

- S32GでのAIベースDL車両ヘルス・マネジメント (VHM) ソリューション開発の自動化

- S32Gを利用した安全でセキュアなゾーン・アーキテクチャへの移行

- S32Gでのタイム・センシティブ・ネットワーク (TSN) プロトコルを使用したセキュアな車載ゲートウェイ・ソリューションの設計

- AWSコネクテッド・モビリティ・ソリューションとS32Gを使用した車載クラウド・サービス・アプリケーションの開発

- GoldBox、GreenBox、AWSクラウド・サービスを使用したコネクテッドEVマネジメント・システムの実現

- AWSコネクテッド・モビリティ・ソリューションを使用した高度な車載クラウド・サービス・アプリケーション

- S32GでのAirbiquity OTAmatic®を使用したOTA車載ソフトウェア・アップデートとデータ・マネジメントのオーケストレーション

- The Fusion Projectによる機械学習ベースのデータ・ライフサイクルを利用したコネクテッド・インテリジェント・ビークルの実現

フォーラム

NXP S32G VNP RDB3用のコミュニティで他のエンジニアと交流し、NXP S32G VNP RDB3を利用した設計に関する専門的なアドバイスを受けることができます。