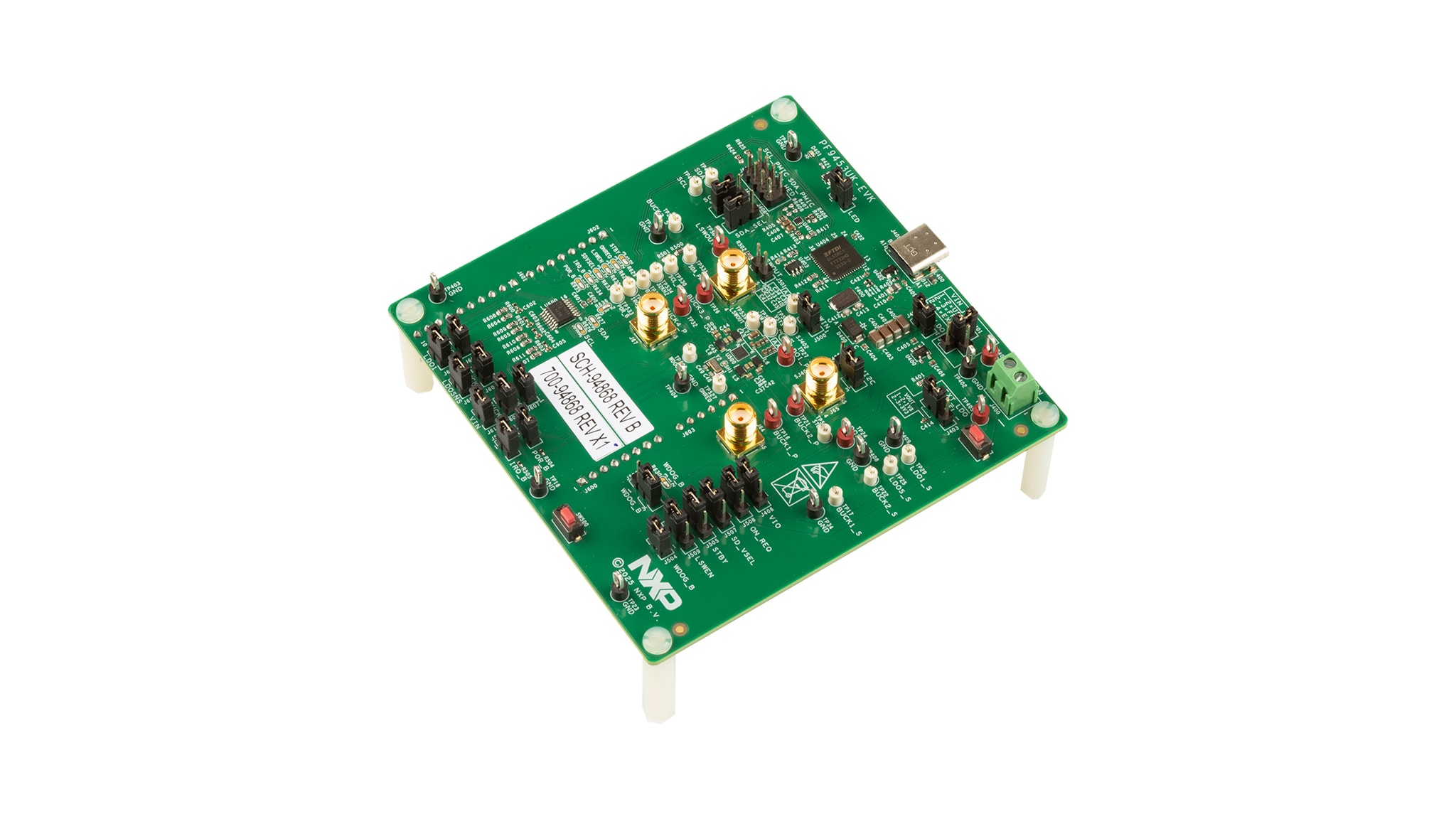

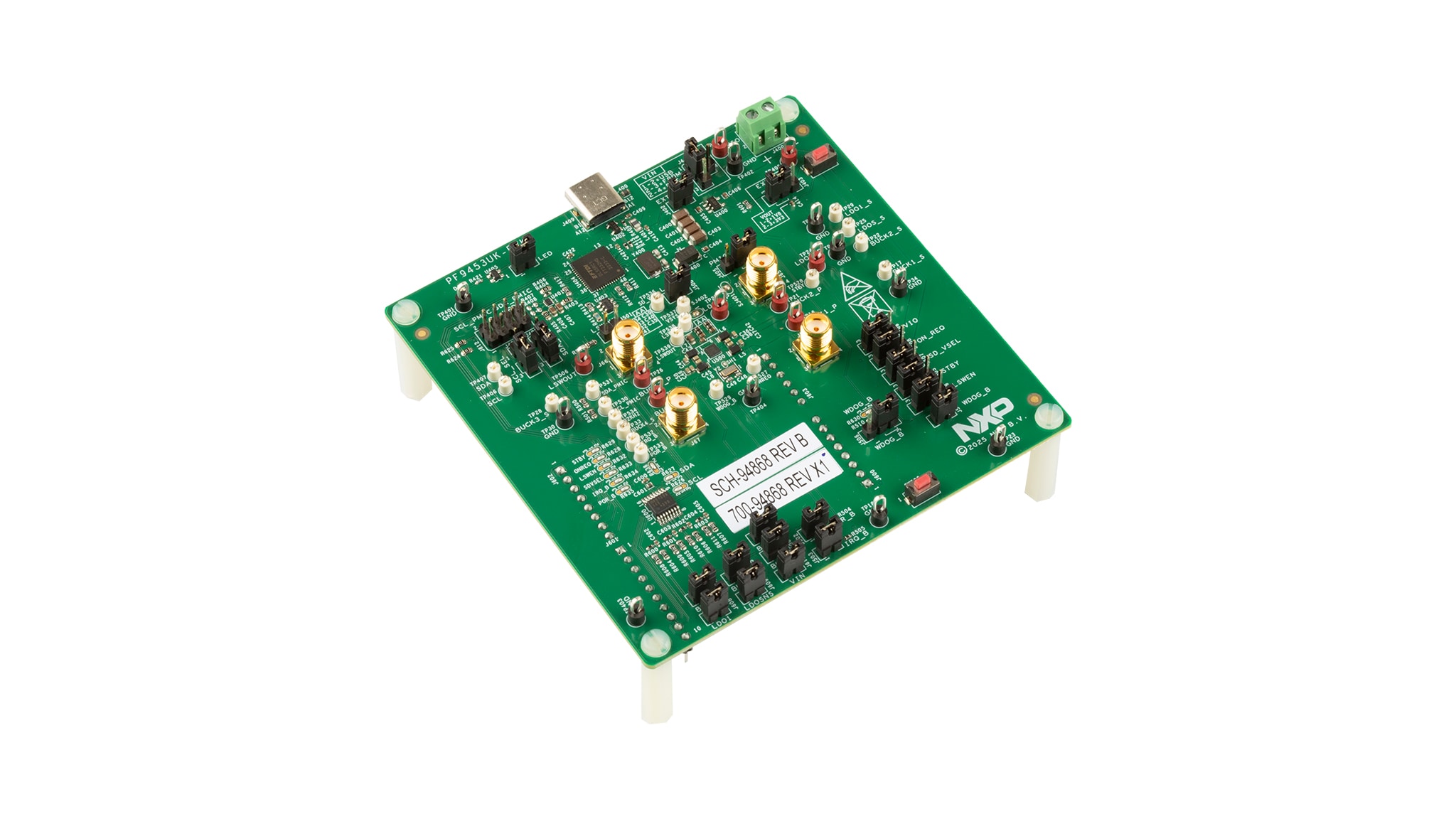

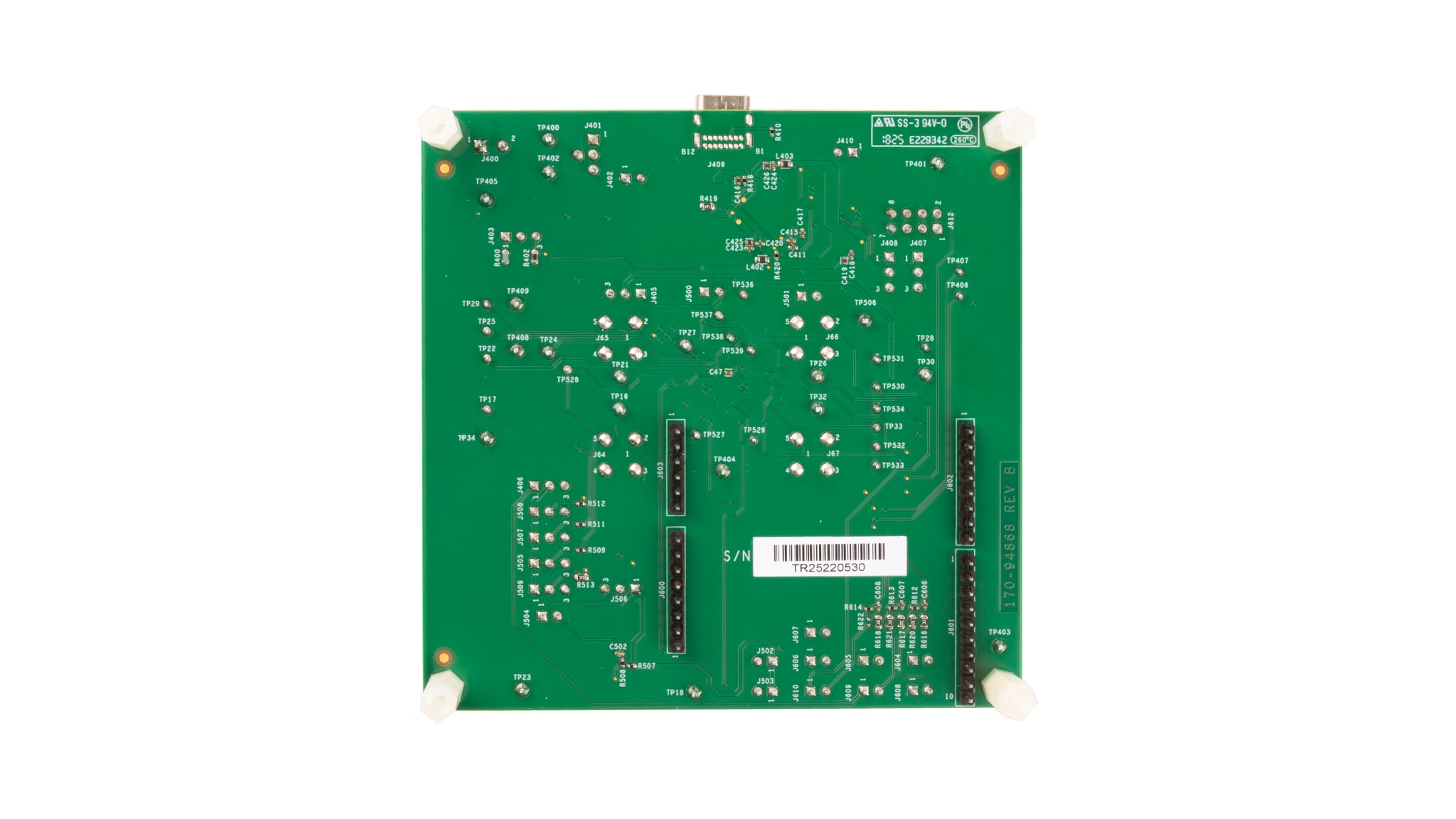

PF9453UK-EVK

アクティブ

PF9453 WLCSP Low Power Multi-Rail PMIC Evaluation Board.

キットの内容

- PF9453UK-EVK評価ボード1個。機能と特長の評価を可能にします

- USB Type Cケーブル1本