アプリケーション・ノート (2)

エラッタ (1)

-

SGTL5000 Silicon Errata - Errata[SGTL5000ER]

データ・シート (1)

ユーザ・ガイド (1)

-

KITSGTL5000 Evaluation Platform - User Guide[KTSGTL5000UG]

お客様の素早い設計とより早い製品化を実現する、技術情報と専門知識をご紹介します。

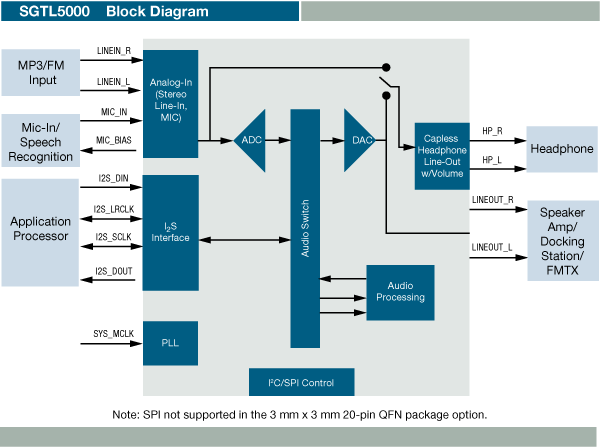

The SGTL5000 is a low-power stereo codec designed to provide a comprehensive audio solution for portable products that require line-in, mic-in, line-out, headphone-out and digital I/O.

Featuring:

注: 製品の特徴を見るには、このウィンドウを閉じます。.

|

|

|

|

|

|

|

|---|---|---|---|---|---|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

クイック・リファレンス ドキュメンテーションの種類

5 ドキュメント

コンパクトリスト

セキュアファイルの読み込み中、しばらくお待ちください。

1 設計・ファイル

完全な内訳を受け取ります。 製品の設置面積などについては、 eCad ファイル.

セキュアファイルの読み込み中、しばらくお待ちください。

2 ハードウェア提供

この製品をサポートするその他のパートナー製品を見つけるには、当社の Web サイトにアクセスしてください パートナーマーケットプレイス.

クイック・リファレンス ソフトウェア・タイプ.

1 ソフトウェア・ファイル

注: より快適にご利用いただくために、ソフトウェアのダウンロードはデスクトップで行うことを推奨します。

セキュアファイルの読み込み中、しばらくお待ちください。

2 エンジニアリング・サービス

There are no results for this selection.

この製品をサポートするその他のパートナー製品を見つけるには、当社の Web サイトにアクセスしてください パートナーマーケットプレイス.