TJA1410-EVBのスタート・ガイド

このドキュメントの内容

-

パッケージの内容

-

ハードウェアについて

-

ハードウェアの構成

サインイン 進行状況を保存するには アカウントをお持ちでない方 アカウントを作成する。

お客様の TJA1410-EVB

1. パッケージの内容

NXPのアナログ製品開発ボードは、NXP製品の評価を目的とした使いやすいプラットフォームです。さまざまなアナログ・ソリューション、ミックスド・シグナル・ソリューション、パワー・ソリューションに対応しています。実績のある大容量テクノロジを使用したモノリシック集積回路およびシステム・イン・パッケージ (SiP) デバイスを搭載しています。NXP製品は、最先端システムへの電源供給において、より長いバッテリー寿命、より小さいフォーム・ファクタ、より少ない部品数、より低いコスト、改善されたパフォーマンスを実現します。このページでは、TJA140-EVBをセットアップして使用する手順について説明します。

1.1 キットの内容

- TJA1410-EVBと2個のプラグイン・コネクタ(静電気防止バッグ入り)

1.2 追加ハードウェア

- TJA1410-EVBを使用して10BASE-T1Sアプリケーションのプロトタイピングを行うには、統合デジタル物理層デバイス (PHY) を備えたホスト・デバイスが必要です。ホスト・ボードのオプションには以下のものがあります。

- S32K5MMA-MB

- S32K566-EVB

- 電源:3.3 V

- コネクタの互換性によっては、TJA1410-EVBをホスト・ボードに接続するためにリボン・ケーブルが必要になる場合があります。

2. ハードウェアについて

2.1 ボードの特長

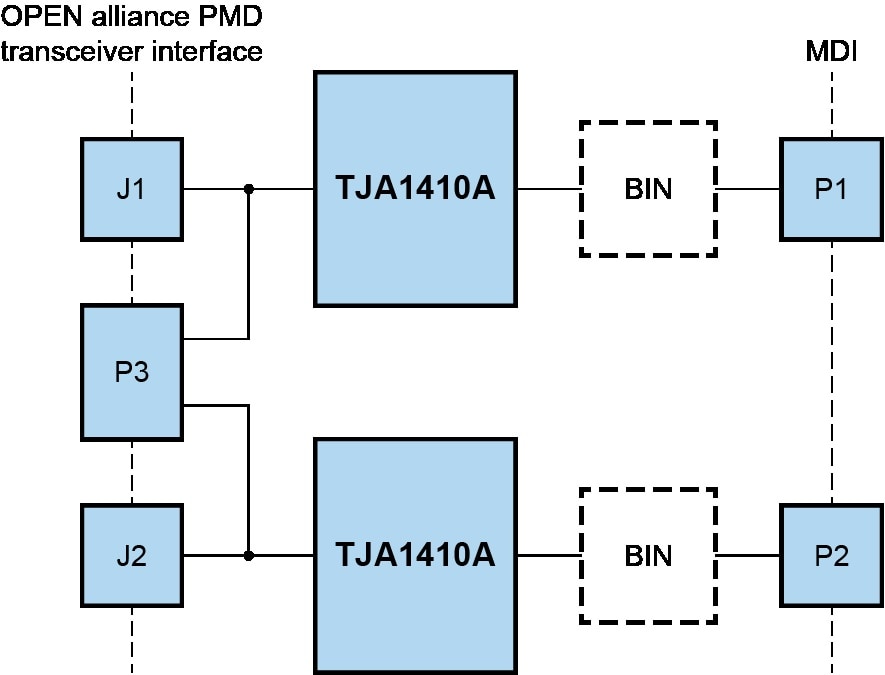

TJA1410-EVBには、2つの10BASE-T1S PMDトランシーバ・チャネルが搭載されています。この評価ボードは、以下のコンポーネントで構成されています。

- TJA1410A 10BASE-T1Sイーサネット物理媒体依存 (PMD) トランシーバ

- エンドノード終端ジャンパ

- 媒体依存インターフェース (MDI) コネクタ

- OPEN Alliance PMDトランシーバ・インターフェース・コネクタの2つのオプション

- 電源インジケータLED

- 2つの240 μΗコモンモード・チョーク (CMC)

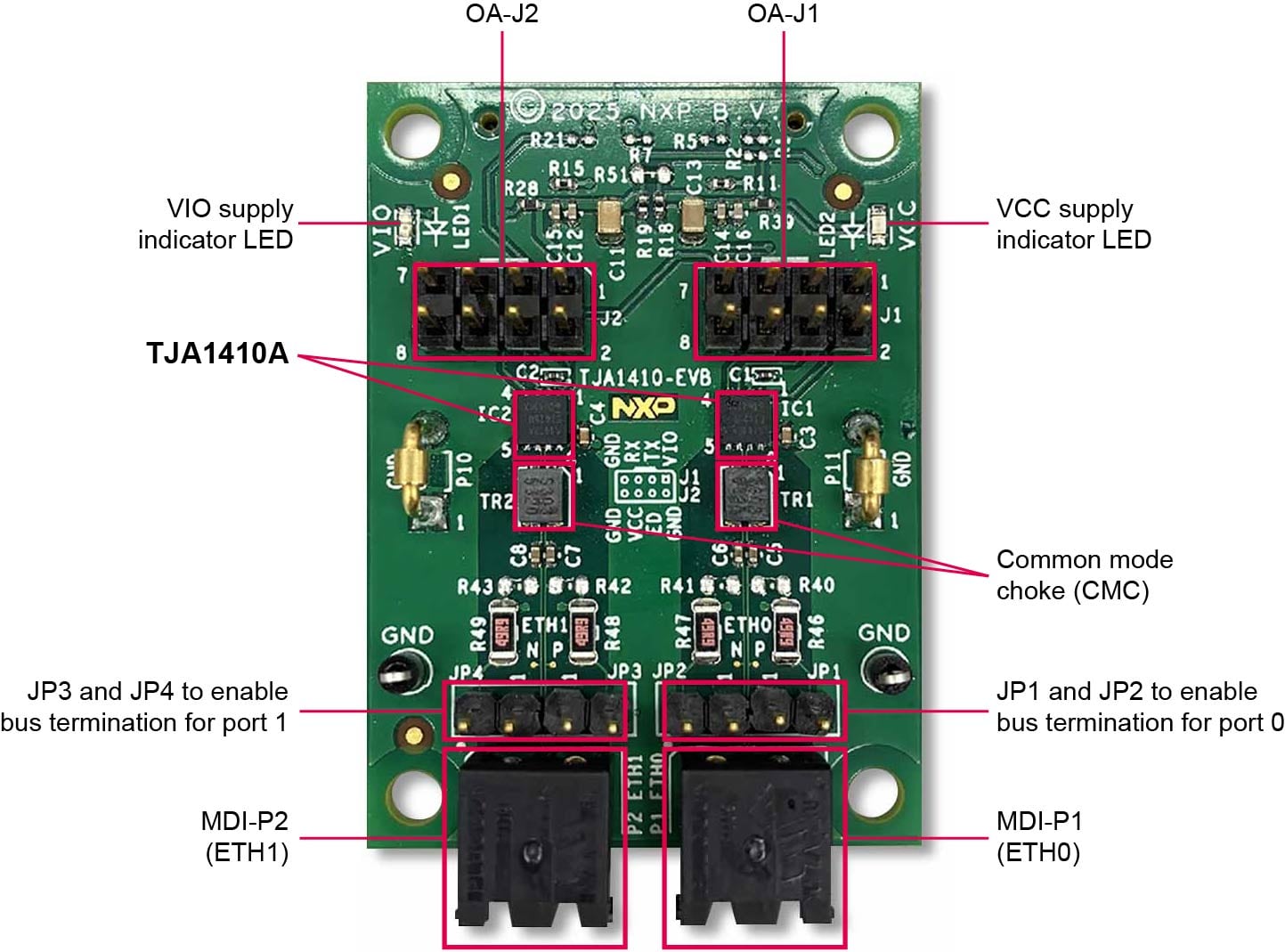

2.3 評価ボードの主要コンポーネント

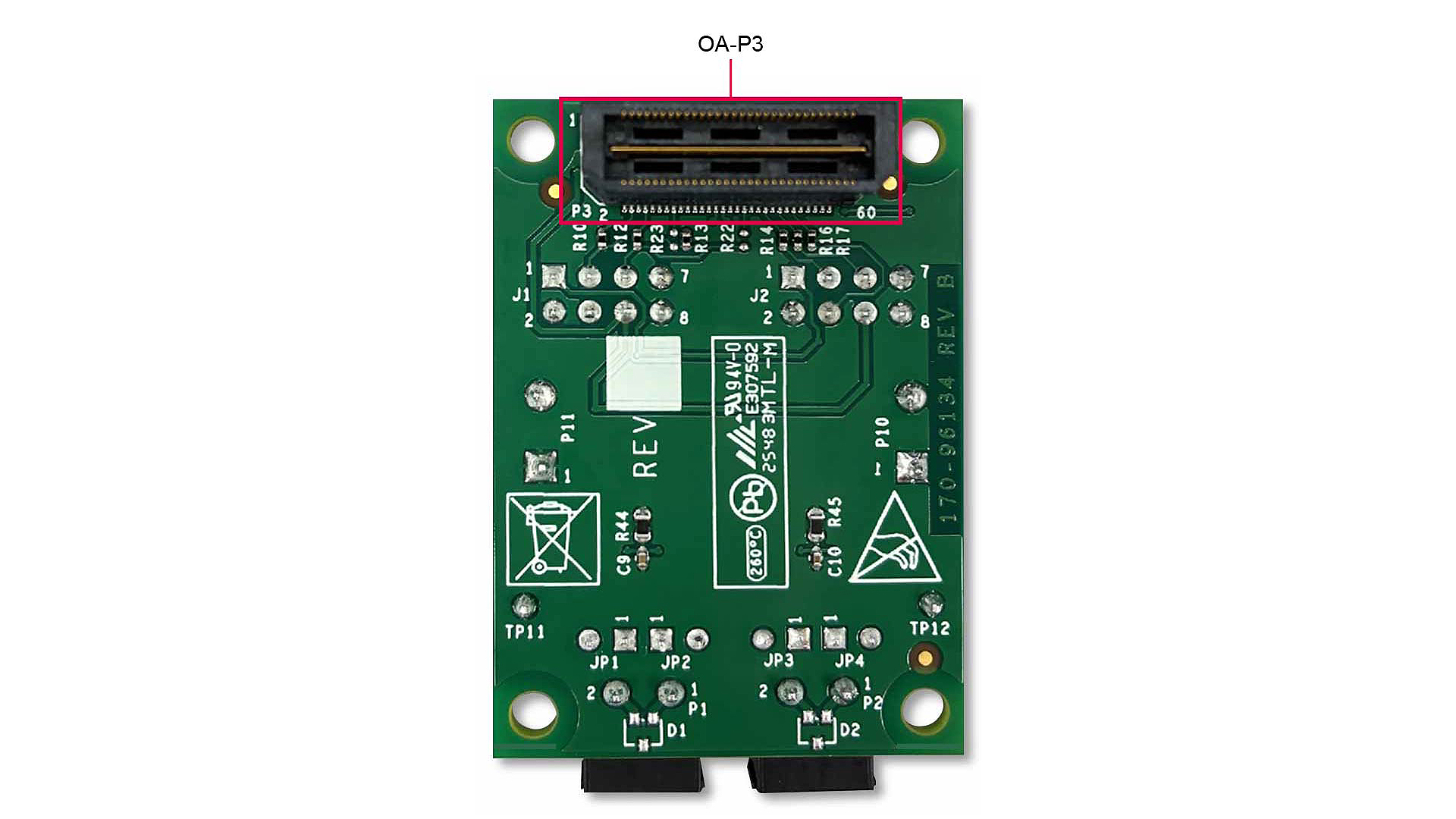

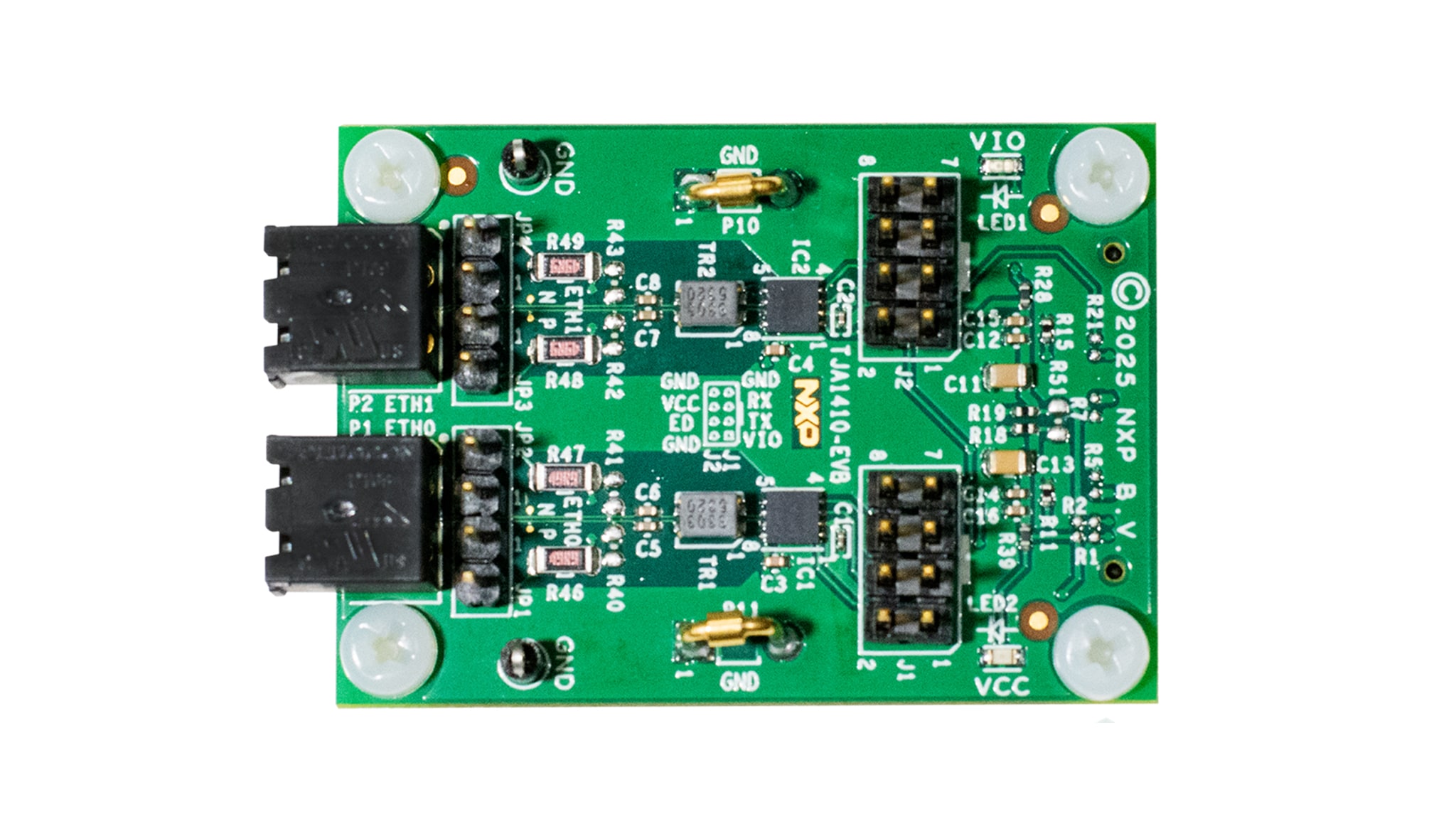

図2は、TJA1410-EVBの概要と、ボード上のコンポーネントの位置を示しています。TJA1410-EVBの裏側(図3)では、OA-J1およびOA-J2の代わりにコネクタ (OA-P3) を使用できます。表1に、コンポーネントの詳細を示します。

| 番号 | 説明 |

|---|---|

| OA-J1 | ポート1のOPEN Alliance 10BASE-T1S PMDトランシーバ用のデジタル・インターフェースおよび電源コネクタ |

| OA-J2 | ポート2のOPEN Alliance 10BASE-T1S PMDトランシーバ用のデジタル・インターフェースおよび電源コネクタ |

| OA-P3 | ポート1および2のOPEN Alliance 10BASE-T1S PMDトランシーバ用のデジタル・インターフェースおよび電源コネクタ |

VIO電源インジケータLED |

VIO電源が利用可能な場合は、VIO電源インジケータLEDが点灯します |

| VCC電源インジケータLED | VCC電源が利用可能な場合は、VCC電源インジケータLEDが点灯します |

| TJA1410A | 3.3 V VIO電源向けのOPEN Alliance 10BASE-T1S PMDトランシーバのバリエーション |

| コモンモード・チョーク (CMC) | OPEN Alliance 10BASE-T1Sのコモンモード・チョーク用EMCテスト仕様に準拠したCMC |

ポート0のJP1およびJP2バス終端 |

ジャンパ・ピンはエンド・ノードのバス終端となります。ポート0でエンドノード終端をイネーブルにするには、JP1とJP2の両方にジャンパ・ソケットが取り付けられている必要があります |

ポート1のJP3およびJP4バス終端 |

ジャンパ・ピンはエンドノードのバス終端を提供します。ポート1でエンドノード終端をイネーブルにするには、JP3とJP4の両方にジャンパ・ソケットが取り付けられている必要があります |

| MDI-P1 | ポート1の媒体依存インターフェース |

| MDI-P2 | ポート2の媒体依存インターフェース |

2.4 評価ボードのコネクタ

| コネクタ・ピン | 信号 | 説明 |

|---|---|---|

| OA-Jx-1 | VIO |

TJA1410A向けのVIOインターフェース電源電圧。デジタルI/Oセルおよびウェイクアップ検出回路への電力供給に使用 |

| OA-Jx-2/-7/-8 | GND |

グランド |

| OA-Jx-3 | TX_x |

TJA1410Aのデータ送信信号 |

| OA-Jx-4 | ED_x |

TJA1410Aのエネルギー検出信号 |

| OA-Jx-5 | RX_x |

TJA1410Aのデータ受信信号 |

| OA-Jx-6 | VCC |

TJA1410Aトランシーバの電源電圧 |

| コネクタ・ピン | 信号 | 説明 |

|---|---|---|

| OA-P3-28 | VCC |

TJA1410Aトランシーバの電源電圧 |

| OA-P3-30 | VIO |

TJA1410A向けのVIOインターフェース電源電圧。デジタルI/Oセルおよびウェイクアップ検出回路への電力供給に使用 |

| OA-P3-6/-44 | GND |

グランド |

| OA-P3-4 | TX_0 |

TJA1410Aのポート0のデータ送信信号 |

| OA-P3-8 | RX_0 |

TJA1410Aのポート0のデータ受信信号 |

| OA-P3-16 | ED_0 |

TJA1410Aのポート0のエネルギー検出信号 |

| OA-P3-42 | TX_1 |

TJA1410Aのポート1のデータ送信信号 |

| OA-P3-46 | RX_1 |

TJA1410Aのポート1のエネルギー検出信号 |

| OA-P3-50 | ED_1 |

TJA1410Aはデータ信号ポート1を受信 |

| OA-P3-1 | (VCC) |

0 Ω抵抗の構成による代替VCCピン配置オプション(デフォルト:非接続) |

| OA-P3-3 | (VIO) |

0 Ω抵抗の構成による代替VIOピン配置オプション (デフォルト:未接続) |

| OA-P3-11/-33 | (GND) |

0 Ω抵抗の構成による代替GNDピン配置オプション(デフォルト:未接続) |

| OA-P3-16 | (TX_0) |

0 Ω抵抗の構成による代替TX_0ピン配置オプション(デフォルト:未接続) |

| OA-P3-36 | (RX_0) |

0 Ω抵抗の構成による代替RX_0ピン配置オプション(デフォルト:未接続) |

| OA-P3-43 | (ED_0) |

0 Ω抵抗の構成による代替ED_0ピン配置オプション(デフォルト:未接続) |

| コネクタ・ピン | 信号 | 説明 |

|---|---|---|

| MDI-Px-1 | BI_DAx_n | MDIコネクタのマイナス端子 |

| MDI-Px-2 | BI_DAx_p | MDIコネクタのプラス端子 |

2.5 評価ボードのジャンパ

| ジャンパ | 設定 | 説明 |

|---|---|---|

JP1およびJP2 |

開 | ポート0のドロップノード終端 |

| 閉 | ポート0のエンドノード終端 | |

JP3およびJP4 |

開 | ポート1のドロップノード終端 |

| 閉 | ポート1のエンドノード終端 |

| LED | ステータス | 説明 |

|---|---|---|

VIO LED |

オン | VIO電源がオン |

| オフ | VIO電源がオフ |

|

VCC LED |

オン | VCC電源がオン |

| オフ | VCC電源がオフ |

3. ハードウェアの構成

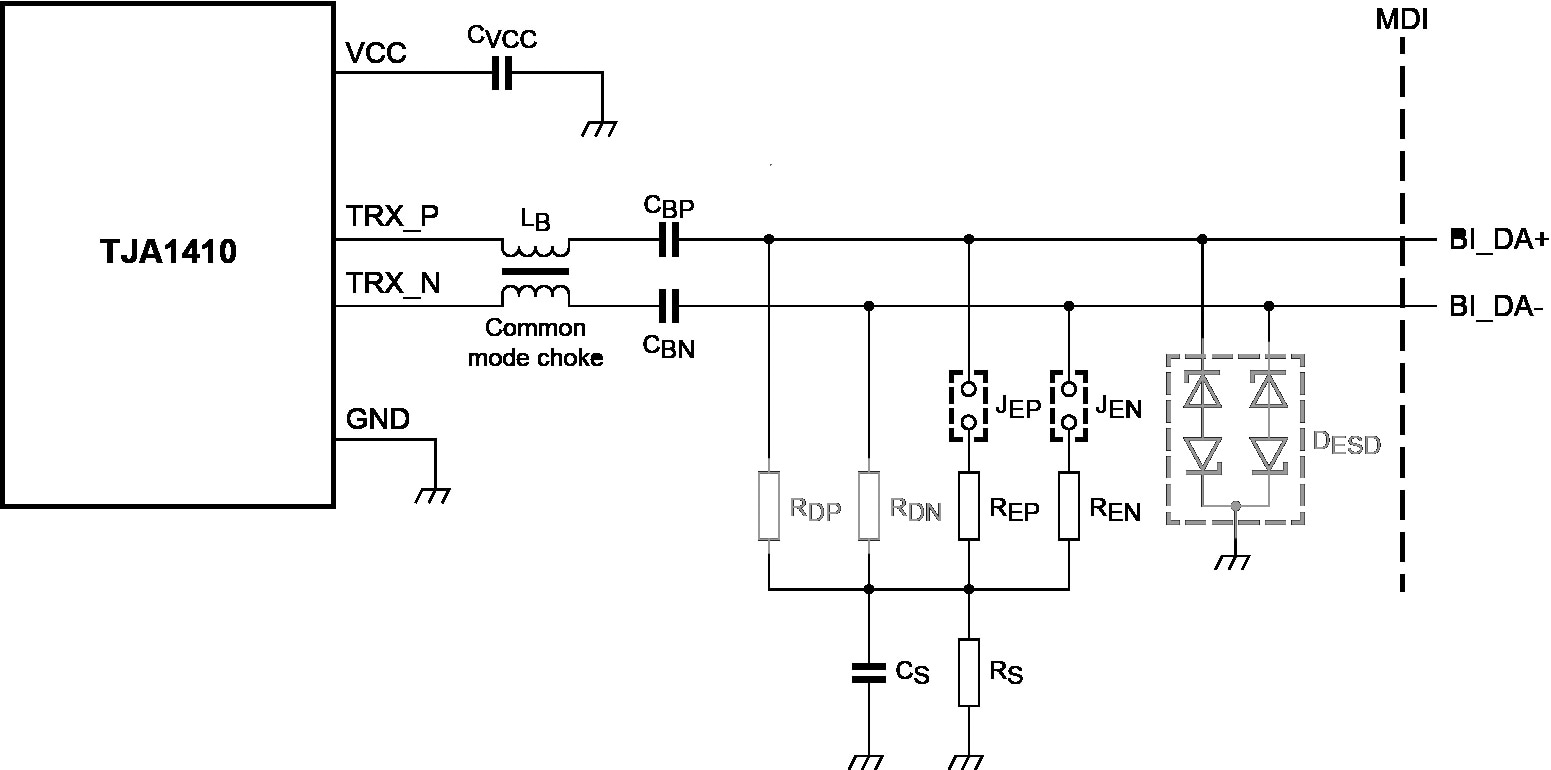

3.1 バス・インターフェース・ネットワーク回路

図4は、TJA1410 EVBのBIN回路を示しています。この回路は、OPEN Allianceのシステム実装仕様に従っています(リファレンス5を参照)。JEPとJENは、バス終端を設定するジャンパです。表7に、BIN回路のコンポーネントの一覧と説明を示します。

TJA1410-EVBには2つのイーサネット・ポートが搭載されています。それぞれのポートに同一のBIN回路があります。未搭載のコンポーネントは、BIN回路を適応させるオプションを提供するオプションのコンポーネントです。

| 記号 | 回路図のリファレンス | 値 | 説明 |

|---|---|---|---|

| LB | TR1、TR2 |

240 µH | リファレンス4に従った一般的なCMC |

| CBP、CBN | C5、C6、C7、C8 |

100 nF | リファレンス5に従ったブロッキング・キャパシタ |

| JEP、JEN | JP1、JP2、JP3、JP4 |

— | バス終端を設定するジャンパ |

| REP、REN | R46、R47、R48、R49 |

49.9 Ω | リファレンス5に従ったエンドノード終端 |

| RDP、RDN | R40、R41、R42、R43 |

未搭載(1.5 kΩ) | リファレンス5に従ったオプションのドロップノード終端 |

| RS | R44、R45 |

100 kΩ | リファレンス5に従ったオプションの分割フィルタ抵抗 |

| CS | C9、C10 |

47 nF | リファレンス5に従ったオプションの分割フィルタ・キャパシタ |

| DESD | D1 |

未搭載 | オプションのESD保護デバイス |

| CVCC | C3、C4 |

1 µF | VCC電源のバッファリング用積層セラミック・キャパシタ |