Software Defined Radio Processor for V2X Communication

The SAF5100 is available in a Ball Grid Array (BGA) package occupying small Printed-Circuit Board (PCB) real estate and is suitable for multi-layer PCBs.

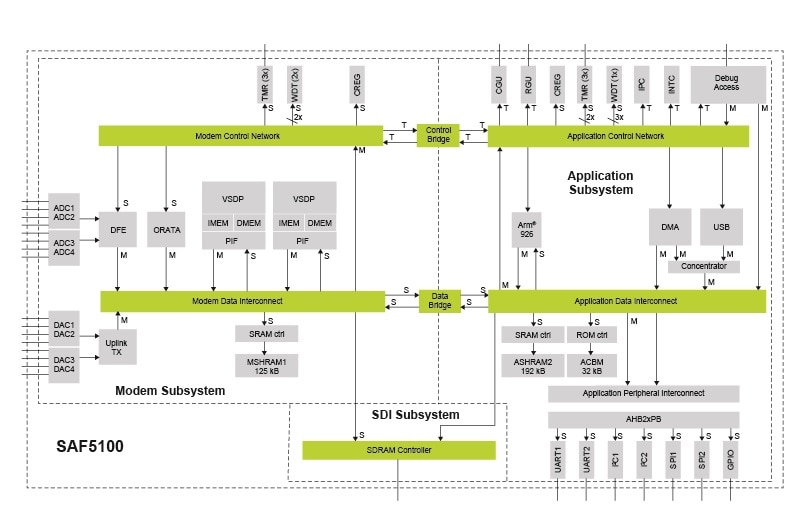

The SAF5100 this baseband processor includes Analog-to-Digital Converters (ADC) and Digital-to-Analog Converters (DAC) for interfacing with an external transceiver. Digital components included are:

- Digital Signal Processors (DSP) for advanced radio (de)modulation

- Hardware Accelerators (HWA) for IEEE 802.11p WiFi standard PHYsical layer (PHY) reception

- A microcontroller core for IEEE 1609.4 Medium Access Control (MAC)/Logical Link Control (LLC) processing

- Several standard interfaces such as Universal Serial Bus (USB) and SPI are included for connecting to an external host

The SAF5100 is available with an executable of a firmware comprising PHY/MAC (IEEE 802.11p and ETSI EN 302 663) and LLC (IEEE 1609.4 and ETSI EN 302 663) to be loaded into the RAM of the SAF5100.

製品詳細

Features

- Compliant with IEEE 802.11p and IEEE 1609.4

- Compliant with ETSI EN 302 663

- Compliant with ARIB T55 and ARIB T75 standards

- Dual channel handling for diversity and concurrent control and service channel reception

- Dual channel handling for cyclic transmit diversity transmission

- Digital baseband processing, including In-phase Quadrature Compensation (IQC), Automatic Gain Control (AGC) control, decimation

- DSP processing for demodulation and improvement algorithms

- Outer receiver HWA for channel decoding and encoding

- Arm processor domain for control Software (SW), interfacing and ITS MAC/LLC handling

- Configurable booting from external serial flash or through the host (USB, SPI)

- USB 2.0 high-speed peripheral interface

- Qualified in accordance with AEC-Q100 Qualified

- Synchronous Dynamic Random Access Memory (SDRAM) interface is not used for ITS applications

- Serial communication ports, including Inter-Integrated Circuit bus (I2C-bus), Serial Peripheral Interface (SPI), Universal Asynchronous Receiver/Transmitter (UART)

- Hardware timers and pulse width modulation blocks

- Optional Elliptic Curve Digital Signature Algorithm (ECDSA) accelerator for authentication verification of messages

設計・リソース

ハードウェア

3 ハードウェア提供

-

コンパニオン・シリコンとモジュール

コンパニオン・シリコンとモジュールV2X Radio Module

-

コンパニオン・シリコンとモジュール

コンパニオン・シリコンとモジュールV2X On Board Unit

-

コンパニオン・シリコンとモジュール

コンパニオン・シリコンとモジュールV2X Roadside Unit

ソフトウェア

エンジニアリング・サービス

NXPから直接サポートを受けるには、以下のサイトをご覧ください。 エンジニアリング・サービス.

1 エンジニアリング・サービス

-

インディペンデントデザインハウス (IDH)

V2X(Vehicle To Everything Turnkey Solution

本製品をサポートするパートナーの一覧は、 パートナーマーケットプレイス.