## **UM12269**

# SJA1110 multi-gig secure evaluation board Rev. 1.0 — 28 April 2025

**User manual**

#### **Document information**

| Information | Content                                                                                                                      |

|-------------|------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | SJA1110, SJA1110A, SJA1110B, SJA1110C, SJA1110D, SJA1110-MGS-EVM, evaluation board, TJA1121, TJA1104, SMI, SPI, MACsec, TC10 |

| Abstract    | This document describes the operation of the SJA1110-MGS-EVM evaluation board.                                               |

#### SJA1110 multi-gig secure evaluation board

#### **IMPORTANT NOTICE**

#### For engineering development or evaluation purposes only

NXP provides the product under the following conditions:

This evaluation kit is for use of ENGINEERING DEVELOPMENT OR EVALUATION PURPOSES ONLY. It is provided as a sample IC pre-soldered to a printed-circuit board to make it easier to access inputs, outputs and supply terminals. This evaluation board may be used with any development system or other source of I/O signals by connecting it to the host MCU computer board via off-the-shelf cables. This evaluation board is not a Reference Design and is not intended to represent a final design recommendation for any particular application. Final device in an application heavily depends on proper printed-circuit board layout and heat sinking design as well as attention to supply filtering, transient suppression, and I/O signal quality.

The product provided may not be complete in terms of required design, marketing, and or manufacturing related protective considerations, including product safety measures typically found in the end device incorporating the product. Due to the open construction of the product, it is the responsibility of the user to take all appropriate precautions for electric discharge. In order to minimize risks associated with the customers' applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. For any safety concerns, contact NXP sales and technical support services.

SJA1110 multi-gig secure evaluation board

#### 1 Introduction

This document is the user guide for the SJA1110-MGS evaluation board (SJA1110-MGS-EVM). The SJA1110-MGS-EVM is a compact, cost-effective multi-gig secure evaluation board, ideal for automotive Ethernet use cases. Consisting of the SJA1110 switch along with TJA1121 and TJA1104 PHYs, the board demonstrates MACsec security on both PHYs and enables rapid prototyping with integrated software examples based on Real-Time Drivers (RTDs).

Note that this board is not intended to be used for PMA testing of the internal and external PHYs. Signals that would be needed to take such measurements are not available at the SMA connectors.

## 2 Finding kit resources and information on the NXP web site

NXP Semiconductors provides online resources for their evaluation board and supported device(s) on nxp.com.

The information page for the SJA1110-MGS-EVM is at <a href="http://www.nxp.com/SJA1110-MGS-EVM">http://www.nxp.com/SJA1110-MGS-EVM</a>. The information page provides overview information, product details, documentation, software and tools.

## 3 Getting ready

The supplied kit contents, additional hardware and a Windows PC workstation with installed software are needed to work with the SJA1110-MGS-EVM.

#### 3.1 Kit contents

- · Assembled and tested SJA1110-MGS-EVM evaluation board in an antistatic bag

- Twisted-pair cable with MATEnet connectors

- · Quick start guide

SJA1110 multi-gig secure evaluation board

## 4 Getting to know the hardware

## 4.1 Board image

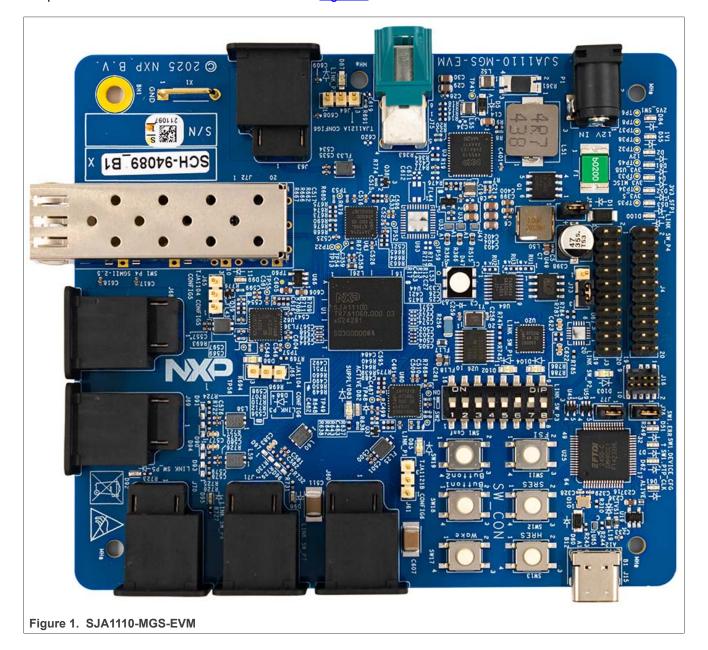

A top view of the SJA1110-MGS-EVM is shown in Figure 1. Board dimensions are 105 mm x 118 mm.

SJA1110 multi-gig secure evaluation board

#### 4.2 Board features

- · SJA1110D secure variant

- Power supply based on VR5510 PMIC using a single 12 volt input

- · Ethernet ports:

- 3x 100BASE-T1 (SJA1110 internal PHYs)

- 1x 100BASE-T1 Ethernet port using the TJA1104B automotive Ethernet PHY

- 2x 1000BASE-T1 Ethernet port using the TJA1121A/B automotive Ethernet PHY

- 1x SFP+ cage

- 1x 2.5G Ethernet port using the TJA1230 automotive Ethernet PHY (not available on Rev. 1.0 of the board)

- JTAG connector to access ARM core of SJA1110

- Several LEDs controlled by HW and SW displaying useful information

- Multiple DIP switches to change specific settings

- USB-C connector for SPI access

### 4.3 Block diagram

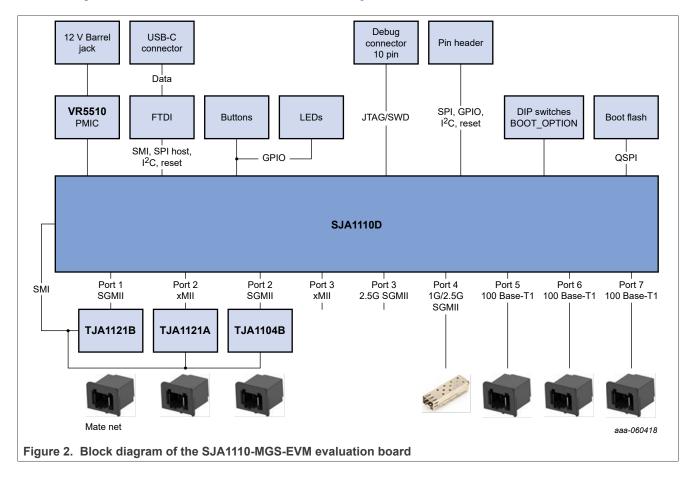

A block diagram of the SJA1110-MGS-EVM is shown in Figure 2.

SJA1110 multi-gig secure evaluation board

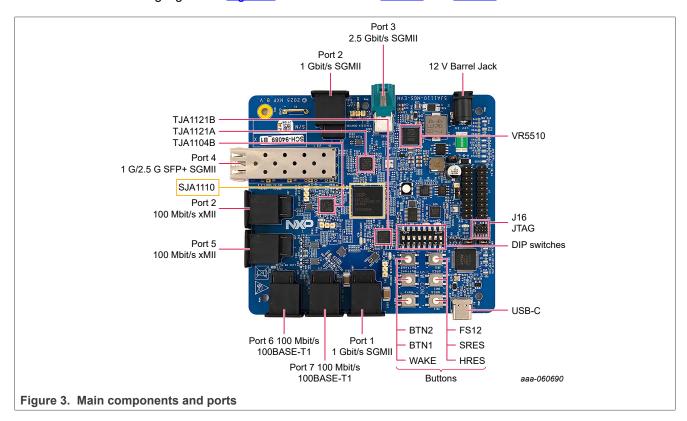

#### 4.4 Board overview

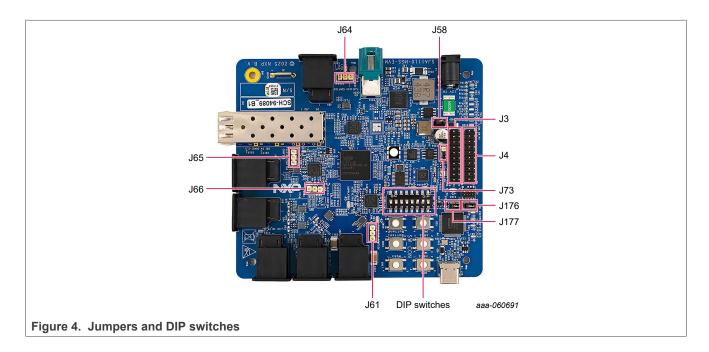

The main components and ports on the SJA1110-MGS-EVM are indicated and labelled in <u>Figure 3</u>. Jumpers and DIP switches are highlighted in <u>Figure 4</u> and described in <u>Table 1</u> and <u>Table 2</u>.

## SJA1110 multi-gig secure evaluation board

Table 1. Jumpers on SJA1110-MGS-EVM

| Jumper | Function                       |

|--------|--------------------------------|

| J3     | debug header (see Section 4.9) |

| J4     | debug header (see Section 4.9) |

| J58    | 12 V power supply              |

| J61    | TJA1121B PHY role              |

| J64    | TJA1121A PHY role              |

| J65    | TJA1104B pin strap option      |

| J66    | TJA1104B pin strap option      |

| J73    | VDDA18_OTP_IN supply           |

| J76    | enable SOFT_RESET_N            |

| J77    | enable HARD_RESET_N            |

#### Table 2. SJA1110-MGS-EVM DIP switches

| DIP switch | Signal                      | Comment                                                                                             |

|------------|-----------------------------|-----------------------------------------------------------------------------------------------------|

| SW2.1      | SW1_PHY_AUTO_MODE           | Autonomous mode for internal PHYs 0 = autonomouse mode 1 = managed mode                             |

| SW2.2      | SW1_PHY_AUTO_POL_DET        | Polarity detection for internal PHYs 0 = polarity detection enabled 1 = polarity detection disabled |

| SW2.3      | SW1_PHY_M_S5                | Leader/follower settings for internal                                                               |

| SW2.4      | SW1_PHY_M_S6 PHY on ports 5 | PHY on ports 5 to 7                                                                                 |

| SW2.5      | SW1_PHY_M_S7                | 1 = follower                                                                                        |

| SW2.6      | SW1_BOOT_OPTION0            | SJA1110 boot option selector                                                                        |

| SW2.7      | SW1_BOOT_OPTION1            | SJA1110 boot option selector                                                                        |

| SW2.8      | n.c.                        | unused                                                                                              |

#### Table 3. SJA1110 boot options

| SW2.6 | SW2.7 | Boot mode |

|-------|-------|-----------|

| ON    | ON    | NVM       |

| OFF   | OFF   | SDL       |

In NVM boot mode, the SJA1110 firmware boots from the external Flash memory on the board.

In SDL boot mode, the SJA1110 waits for a companion device to load the firmware via the SPI\_HAP interface. SPI\_HAP is a multiplexed SPI interface used to load firmware onto the device (SPI\_HOST, via CS1) and for register-level access (SPI\_AP, via CS0).

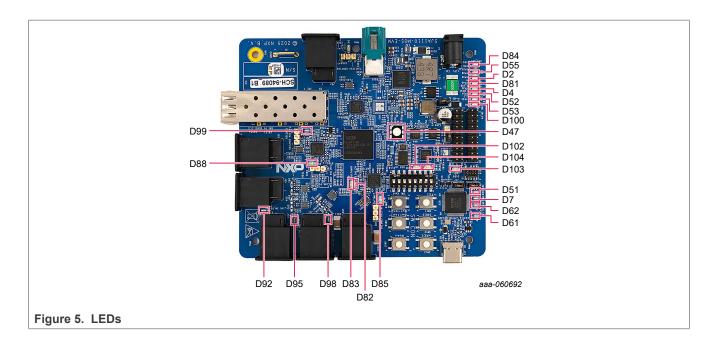

A number of LEDs are provided to indicate component, supply and port status. The LEDs are labelled in <u>Figure 5</u> and detailed in <u>Table 4</u> to <u>Table 7</u>. Some of the LED are hardware-controlled while others are controlled by the firmware running on the SJA1110.

#### SJA1110 multi-gig secure evaluation board

#### Table 4. Voltage LEDs

| LED | SW/HW controlled | Indicates when lit                        |

|-----|------------------|-------------------------------------------|

| D2  | hardware         | 12 V supply present                       |

| D81 | hardware         | 3.3 V USB supply present                  |

| D4  | hardware         | 3.3 V LED supply present                  |

| D52 | hardware         | 3.3 V supply for PHYs and SJA1110 present |

| D53 | hardware         | 3.3 V supply for SFP+ cage supply present |

| D55 | hardware         | 1.1 V supply for SJA1110                  |

| D54 | hardware         | 2.2 V LDO output from SJA1110 present     |

#### Table 5. SJA1110 status LEDs

| LED | SW/HW controlled | Indicates when lit                            |

|-----|------------------|-----------------------------------------------|

| D7  | hardware         | SJA1110 holds a valid configuration           |

| D61 | software         | indicates firmware running on SJA1110         |

| D62 | hardware         | PTP clock output on SJA1110 on (PTP_CLK)      |

| D51 | hardware         | fail-safe output on SJA1110 triggered (ERR_N) |

| D49 | hardware         | soft or hard reset generated                  |

| D47 | software         | multi-purpose RGB LED                         |

#### Table 6. PHY status LEDs

| 14010 01 1111 044440 ====0 |                  |                    |

|----------------------------|------------------|--------------------|

| LED                        | SW/HW controlled | Indicates when lit |

| D82                        | hardware         | INH pin high       |

UM12269 All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

#### SJA1110 multi-gig secure evaluation board

Table 6. PHY status LEDs...continued

| LED  | SW/HW controlled | Indicates when lit     |

|------|------------------|------------------------|

| D83  | hardware         | 3.3 V supply present   |

| D85  | hardware         | TJA1121B MDI link-up   |

| D102 | software         | TJA1121B SGMII link-up |

| D87  | hardware         | TJA1121A MDI link-up   |

| D103 | software         | TJA1121A RGMII link-up |

| D88  | hardware         | TJA1104B MDI link-up   |

| D104 | software         | TJA1104B SGMII link-up |

| D92  | software         | SJA1110 port 5 link-up |

| D95  | software         | SJA1110 port 6 link-up |

| D98  | software         | SJA1110 port 7 link-up |

Table 7. SPF+ cage LEDs

| LED  | SW/HW controlled | Indicates when lit          |

|------|------------------|-----------------------------|

| D100 | software         | SFP port link-up to SJA1110 |

| D99  | hardware         | SFP present                 |

#### 4.5 PHYs

#### 4.5.1 SMI addresses

<u>Table 8</u> provides an overview of the SMI addresses of the onboard PHYs (internal and external). To prevent them being misconfigured, the SMI addresses can only be changed by soldering and not via DIP switches.

Table 8. PHY SMI addresses

| Device                 | SMI address |

|------------------------|-------------|

| TJA1121B               | 1           |

| TJA1121A               | 2           |

| TJA1104B               | 3           |

| unused                 | 4           |

| Internal 100BASE-T1 P5 | 5           |

| Internal 100BASE-T1 P6 | 6           |

| Internal 100BASE-T1 P7 | 7           |

SJA1110 multi-gig secure evaluation board

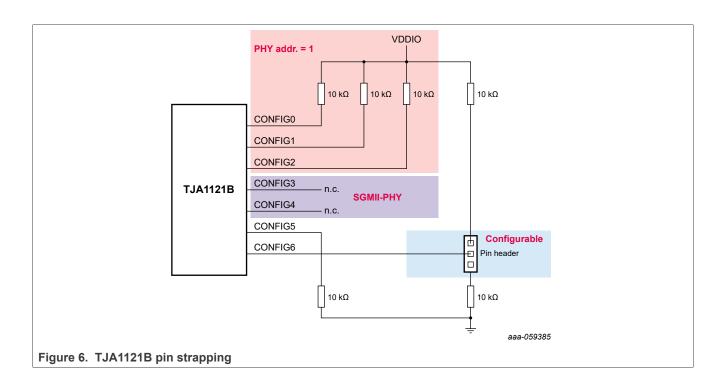

#### 4.5.2 TJA1121B

The TJA1121B is configured automatically via pin strapping.

CONFIG6 pin strapping can be changed using the pin header. It controls the following miscellaneous settings:

- PHY role (follower or leader)

- Autonomous mode<sup>1</sup>

Pin strapping changes will only be applied after a reset has been completed. This can be triggered by pressing the HRES button or by a power-on reset.

Table 9. CONFIG6 settings

| Pin header CONFIG6 | Leader/follower | AUTONOMOUS mode |

|--------------------|-----------------|-----------------|

| open               | leader          | enabled         |

| HIGH               | follower        | enabled         |

| LOW                | disabled        | disabled        |

<sup>1</sup> Unlike the TJA1104, polarity correction cannot be selected via pin strapping. The default configuration is 'enabled', which can be changed via register configuration.

SJA1110 multi-gig secure evaluation board

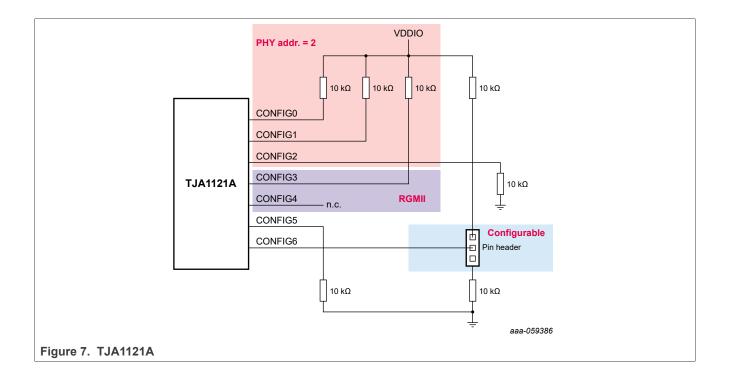

#### 4.5.3 TJA1121A

The TJA1121A is configured automatically via pin strapping.

CONFIG6 pin strapping can be changed using the pin header. It controls the following miscellaneous settings:

- PHY role (follower or leader)

- Autonomous mode<sup>2</sup>

Pin strapping changes will only be applied after a reset has been completed. This can be triggered by pressing the HRES button or by a power-on reset.

Table 10. CONFIG6 settings

| Pin header CONFIG6 | Leader/follower | AUTONOMOUS mode |

|--------------------|-----------------|-----------------|

| open               | leader          | enabled         |

| HIGH               | follower        | enabled         |

| LOW                | disabled        | disabled        |

<sup>2</sup> Unlike the TJA1104, polarity correction cannot be selected via pin strapping. The default configuration is 'enabled', which can be changed via register configuration.

SJA1110 multi-gig secure evaluation board

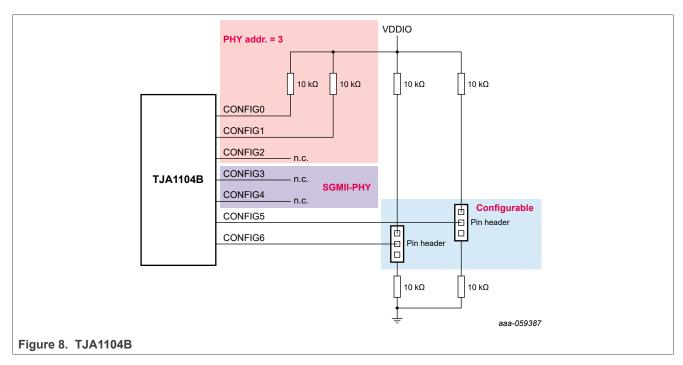

#### 4.5.4 TJA1104B

The TJA1104B is configured automatically via pin strapping.

Pin headers for CONFIG5 and CONFIG6 can be used to change a number of pin strapping settings, as detailed in <u>Table 11</u>:

Table 11. CONFIG5/6 pin strapping settings

| Leader/follower | Autonomous | Polarity correction | CONFIG5 | CONFIG6 |

|-----------------|------------|---------------------|---------|---------|

| leader          | enabled    | enabled             | 0       | 0       |

| leader          | disabled   | enabled             | 0       | Н       |

| follower        | enabled    | enabled             | 0       | L       |

| follower        | disabled   | enabled             | Н       | 0       |

| leader          | enabled    | disabled            | Н       | Н       |

| leader          | disabled   | disabled            | Н       | L       |

| follower        | enabled    | disabled            | L       | 0       |

| follower        | disabled   | disabled            | L       | Н       |

| reserved        | reserved   | reserved            | L       | L       |

Pin strapping changes will only be applied after a reset has been completed. This can be triggered by pressing the HRES button or by a power-on reset.

SJA1110 multi-gig secure evaluation board

## 4.6 Power supply

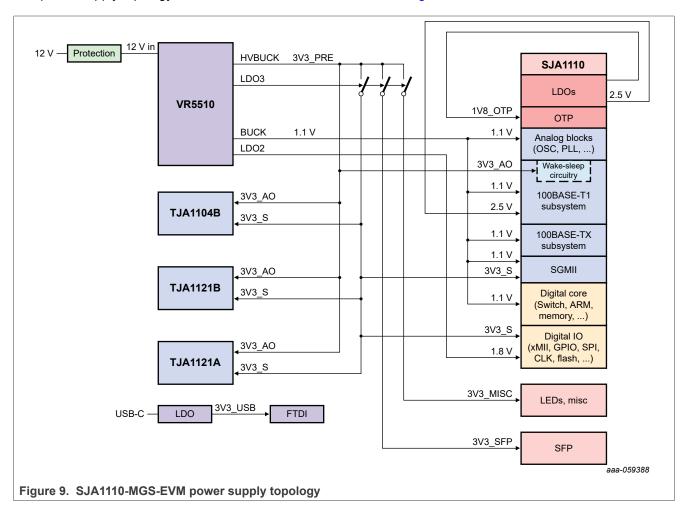

The power supply for the SJA1110-MGS-EVM is built around the VR5510 PMIC to exploit and demonstrate synergies with S32G projects.

The board is powered by a single 12 V input. It is advised to use an adapter that can deliver at least 1 A of current. The power connector is a barrel connector for standard DC plugs. It is connected to the PMIC via a jumper (J58).

The power supply topology of the SJA1110-MGS-EVM is shown in Figure 9.

The input protection includes polarity protection (serial schottky), a self-healing PTC and an EMC filter.

SJA1110 multi-gig secure evaluation board

#### 4.7 Interfaces

#### 4.7.1 SMI

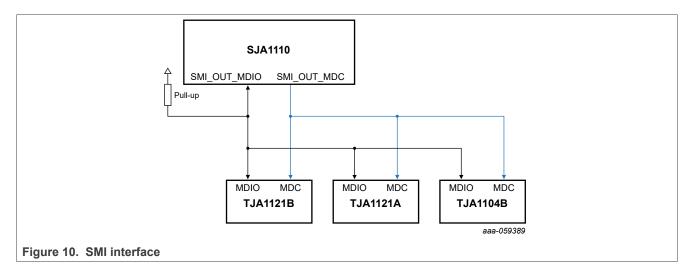

All external PHYs are connected to the SMI\_OUT\_MDIO and SMI\_OUT\_MDC pins on the SJA1110. Thus, the switch has register-level access to the external PHYs. This can be used for advanced configuration or to obtain status information (e.g. TC10, BIST, SQI, etc.). An overview of the SMI addresses can be found in Section 4.5.1.

#### 4.7.2 SPI

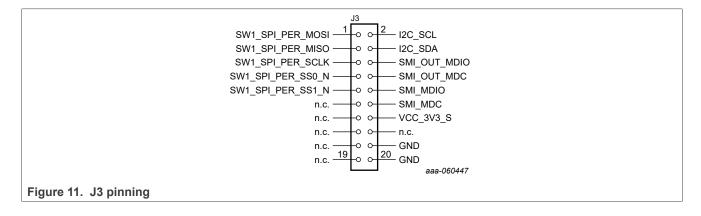

The SPI\_PER interface on the SJA1110 is available on pin header J3, allowing another device to be connected to this interface. The SJA1110 be used as SPI leader to this device.

A typical use-case would be a cascaded switch architecture with two switches, in which one switch loads the configuration to the seconds switch via SPI.

#### 4.8 GPIO extender

The PCAL9722 is a 22-bit general purpose I/O extender that provides remote I/O extension for many microcontroller families via the SPI interface. It is used to extend the 16 I/O pins on the SJA1110. <u>Table 12</u> provides an overview of signals connected to the GPIO extender.

Table 12. GPIO pin extender

| Port extender pin | Signal         | Remark                   |

|-------------------|----------------|--------------------------|

| P0_0              | RESET_TJA1104B | -                        |

| P0_1              | RESET_TJA1121A | -                        |

| P0_2              | RESET_TJA1121B | -                        |

| P0_3              | RESET_TJA1230  | reserved for future use  |

| P0_4              | GPIO1_J4       | connect to pin header J4 |

| P0_5              | GPIO2_J4       | connect to pin header J4 |

| P0_6              | GPIO3_J4       | connect to pin header J4 |

| P0_7              | GPIO4_J4       | connect to pin header J4 |

## SJA1110 multi-gig secure evaluation board

Table 12. GPIO pin extender...continued

| Port extender pin | Signal     | Remark                      |

|-------------------|------------|-----------------------------|

| P1_0              | SW1_P1_LED | link LED switch xMII port 1 |

| P1_1              | SW1_P2_LED | link LED switch xMII port 2 |

| P1_2              | SW1_P3_LED | link LED switch xMII port 3 |

| P1_3              | SW1_P4_LED | link LED switch xMII port 4 |

| P1_4              | SW1_P5_LED | link LED switch port 5      |

| P1_5              | SW1_P6_LED | link LED switch port 6      |

| P1_6              | SW1_P7_LED | link LED switch port 7      |

#### 4.9 Debug headers

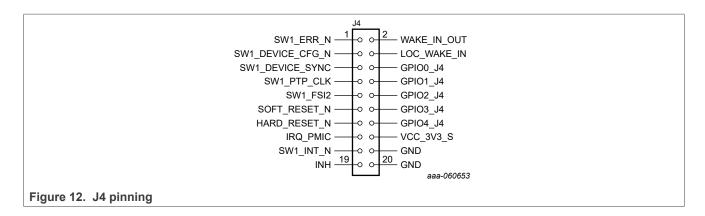

Two debug headers (J3 and J4) are provided on the board to make the following signal groups available:

- I2C bus

- SMI interface (MDC, MDIO)

- SPI leader interface (SPI\_PER)

- TC10 related signals (WAKE\_IN\_OUT, LOC\_WAKE\_IN, INH)

- 4 GPIOs from GPIO extender

- PTP related pins (DEVICE SYNC, PTP CLK)

- Switch status pins (ERR\_N, DEVICE\_CFG\_N)

- Reset lines (SOFT\_RESET\_N, HARD\_RESET\_N)

J3 and J4 pinning is shown in Figure 11 and Figure 12.

#### SJA1110 multi-gig secure evaluation board

## 5 Revision history

#### Table 13. Revision history

| Document ID   | Release date  | Description     |

|---------------|---------------|-----------------|

| UM12269 v.1.0 | 28 April 2025 | Initial version |

#### SJA1110 multi-gig secure evaluation board

## **Legal information**

#### **Definitions**

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

#### **Disclaimers**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at https://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**HTML publications** — An HTML version, if available, of this document is provided as a courtesy. Definitive information is contained in the applicable document in PDF format. If there is a discrepancy between the HTML document and the PDF document, the PDF document has priority.

**Translations** — A non-English (translated) version of a document, including the legal information in that document, is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

Security — Customer understands that all NXP products may be subject to unidentified vulnerabilities or may support established security standards or specifications with known limitations. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP.

NXP has a Product Security Incident Response Team (PSIRT) (reachable at <a href="PSIRT@nxp.com">PSIRT@nxp.com</a>) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

#### Suitability for use in automotive applications (functional safety) -

This NXP product has been qualified for use in automotive applications. It has been developed in accordance with ISO 26262, and has been ASIL classified accordingly. If this product is used by customer in the development of, or for incorporation into, products or services (a) used in safety critical applications or (b) in which failure could lead to death, personal injury, or severe physical or environmental damage (such products and services hereinafter referred to as "Critical Applications"), then customer makes the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, safety, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. As such, customer assumes all risk related to use of any products in Critical Applications and NXP and its suppliers shall not be liable for any such use by customer. Accordingly, customer will indemnify and hold NXP harmless from any claims, liabilities, damages and associated costs and expenses (including attorneys' fees) that NXP may incur related to customer's incorporation of any product in a Critical Application.

$\ensuremath{\mathsf{NXP}}\xspace \ensuremath{\mathsf{B.V.}}\xspace - \ensuremath{\mathsf{NXP}}\xspace \ensuremath{\mathsf{B.V.}}\xspace$  is not an operating company and it does not distribute or sell products.

#### **Trademarks**

Notice: All referenced brands, product names, service names, and trademarks are the property of their respective owners.

NXP — wordmark and logo are trademarks of NXP B.V.

## SJA1110 multi-gig secure evaluation board

## **Contents**

| 1     | Introduction                          | 3  |

|-------|---------------------------------------|----|

| 2     | Finding kit resources and information |    |

|       | on the NXP web site                   | 3  |

| 3     | Getting ready                         | 3  |

| 3.1   | Kit contents                          | 3  |

| 4     | Getting to know the hardware          | 4  |

| 4.1   | Board image                           | 4  |

| 4.2   | Board features                        | 5  |

| 4.3   | Block diagram                         | 5  |

| 4.4   | Board overview                        | 6  |

| 4.5   | PHYs                                  | 9  |

| 4.5.1 | SMI addresses                         | 9  |

| 4.5.2 | TJA1121B                              | 10 |

| 4.5.3 | TJA1121A                              | 11 |

| 4.5.4 | TJA1104B                              | 12 |

| 4.6   | Power supply                          | 13 |

| 4.7   | Interfaces                            | 14 |

| 4.7.1 | SMI                                   | 14 |

| 4.7.2 | SPI                                   | 14 |

| 4.8   | GPIO extender                         | 14 |

| 4.9   | Debug headers                         | 15 |

| 5     | Revision history                      |    |

|       | Logal information                     |    |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.