# **UM11623**

# PCA9959HN-ARD evaluation board

Rev. 1 — 21 May 2021

**User manual**

#### **Document information**

| Information | Content                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | PCA9959HN, SPI, Arduino port, EVK, LED, LED driver                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Abstract    | The PCA9959HN-ARD evaluation board is a daughter card equipped with Arduino ports, designated for easy test and design of the PCA9959HN IC, 24-channel SPI serial bus 63 mA / 5.5 V constant current LED driver. The board is fully compliant with IMXRT1050-EVKB, LPCXpresso55S69 (LPC55S69-EVK) and i.MX 8M Mini LPDDR4 EVK (8MMINILPD4-EVK, 8MMINID4-EVK), including GUI software control. The board can be attached to any device equipped with Arduino ports. |

PCA9959HN-ARD evaluation board

# 1 Revision history

#### Table 1. Revision history

| Rev | Date       | Description     |

|-----|------------|-----------------|

| v.1 | 05/05/2021 | Initial version |

PCA9959HN-ARD evaluation board

#### 2 Introduction

This document describes the PCA9959HN-ARD evaluation board. The evaluation board is built around the PCA9959HN, a 24-channel SPI serial bus 63 mA / 5.5 V constant current LED driver produced by NXP Semiconductors. The evaluation board serves as a daughter card that can be connected through an Arduino port to various Arduino compatible (including original Arduino Uno R3) EVK / motherboards for testing and measuring the characteristics of the PCA9959HN Device Under Test (DUT).

The PCA9959HN-ARD daughter card communicates through the Arduino port with the host device via the high-speed SPI bus (up to 10 MHz clock frequency). The board is equipped with a pair of Fuji connectors that supports a SPI daisy chain scalable architecture. Thus, users can create a stack of similar boards that share SPI bus. The Fuji connectors are of the board-to-board type, allowing the user to attach the boards in a vertical stack instead of connecting link cables between the boards. Alongside the SPI bus, three additional digital lines allow the mother board to control the DUT through the Arduino port or the Fuji connectors.

Power is delivered from the mother board (EVK) through the Arduino port. The power rails are shared with the Fuji connectors, so the DUT can be powered either from the Arduino connectors or the Fuji connectors.

The board contains four RGB LEDs and 12 white LEDs allocated to all 24 outputs of the PCA9959HN DUT. The board also contains jumpers and connectors that allow users to disconnect the onboard LEDs, to perform short tests, and to connect external LEDs to PCA9959HN outputs.

Additionally, a Graphical User Interface (Windows platform) is provided to facilitate the evaluation of the daughter board. The GUI is used in combination with the following NXP evaluation boards: IMXRT1050 EVK board, LPCXpresso55S69 development board, and i.MX 8M Mini LPDDR4 EVK board.

## 3 Finding kit resources and information on the NXP web site

NXP Semiconductors provides online resources for this evaluation board and its supported device(s) at <a href="http://www.nxp.com">http://www.nxp.com</a>.

The information page for the PCA9959HN-ARD evaluation board is at <a href="http://www.nxp.com/PCA9959HN-ARD">http://www.nxp.com/PCA9959HN-ARD</a>. The information page provides overview information, documentation, software and tools, parametrics, ordering information and a **Getting Started** tab. The **Getting Started** tab provides quick-reference information applicable to using the PCA9959HN-ARD evaluation board, including the downloadable assets referenced in this document.

#### 3.1 Collaborate in the NXP community

The NXP community is for sharing ideas and tips, ask and answer technical questions, and receive input on just about any embedded design topic.

The NXP community is at <a href="http://community.nxp.com">http://community.nxp.com</a>.

### 4 Getting ready

Working with the PCA9959HN-ARD requires the kit contents, additional hardware, and a Windows PC workstation with installed software.

UM11623

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved

#### PCA9959HN-ARD evaluation board

#### 4.1 Kit contents

- · Assembled and tested evaluation board in an anti-static bag

- · Quick Start Guide

### 4.2 Assumptions

Familiarity with the SPI bus is helpful but not required.

#### 4.3 Static handling requirements

#### **CAUTION**

This device is sensitive to ElectroStatic Discharge (ESD). Therefore care should be taken during transport and handling. You must use a ground strap or touch the PC case or other grounded source before unpacking or handling the hardware.

#### 4.4 Minimum system requirements

This evaluation board requires a Windows PC workstation. Meeting these minimum specifications should produce great results when working with this evaluation board.

- PC with Windows 10 operating system

- One USB port (either 3.0 or 2.0 or 1.1 compatible)

- One of three EVK boards (MIMXRT1050-EVK, LPC55S69-EVK, 8MMINILPD4-EVK) along with the associated firmware / GUI software

- USB cable for power and data connection between PC and EVK board (if not included in the EVK package)

PCA9959HN-ARD evaluation board

## 5 Getting to know the hardware

#### 5.1 PCA9959HN-ARD features

- · Combined Arduino port/Fuji connector for data and power

- · Multiple board connections in stack architecture

- · Onboard LEDs for all 24 outputs of the DUT IC

- Onboard jumpers for LED connection, and short tests

- · Onboard connectors for external LEDs

- Fully compliant with IMXRT1050 EVK board, including GUI (Windows 10)

- Fully compliant with LPCXpresso55S69 development board, including GUI (Windows 10)

- Compliant with 8MMINILPD4-EVK board, including GUI for Windows 10 (see Note)

**Note:** i.MX Mini LPDDR4 EVK boards require the use of an IMX8MMINI-IARD interposer board between the EVK and PCA9959HN-ARDUINO daughter board (see IMX8MMINI-IARD User Manual).

#### 5.2 Kit featured components

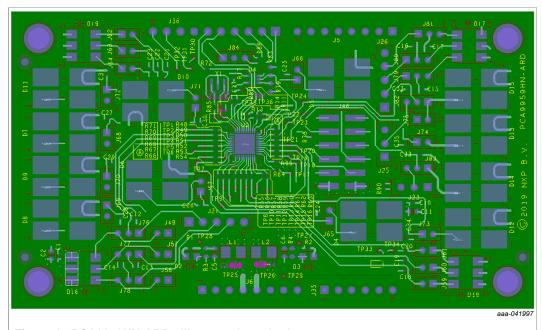

Figure 1 shows the top silkscreen of the board,

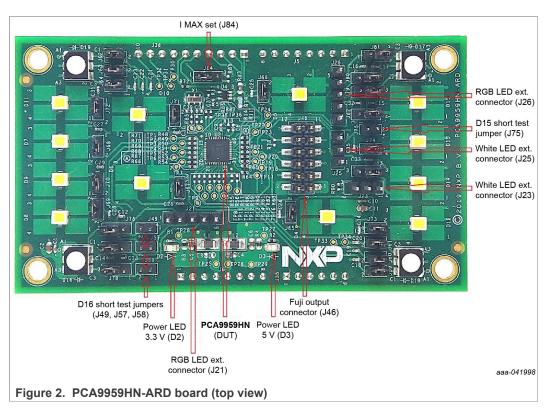

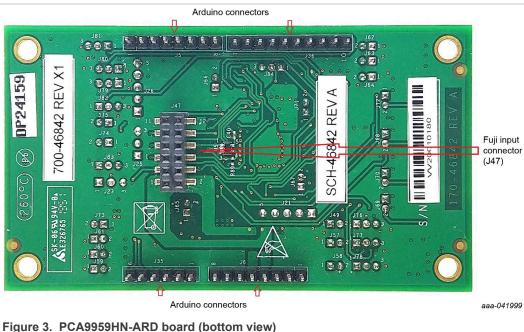

See <u>Figure 2</u> and <u>Figure 3</u> for top and bottom view of the PCA9959HN-ARD daughter card. The following figures allow users to quickly find the location of the board components involved in test and measurement evaluations. The Arduino port connectors (J5, J6, J35, J36) are located on the bottom side of the board.

Figure 1. PCA9959HN-ARD silkscreen (top view)

#### PCA9959HN-ARD evaluation board

#### 5.3 Block diagram

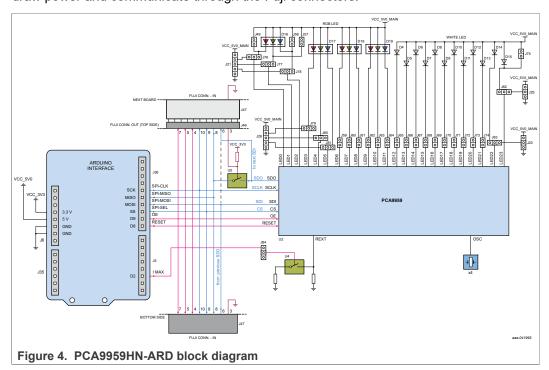

<u>Figure 4</u> shows a block diagram of the PCA9959HN-ARD daughter board. The block diagram includes Arduino interface (J5, J6, J35, and J36 connectors) and the data lines connected to the port. The blue lines in the drawing refer to the SPI bus and the purple lines represents the control bus. The J46 and J47 connectors are Fuji connectors

#### PCA9959HN-ARD evaluation board

(see Section 5.5 "Fuji connectors"). J46 is the Fuji output connector (pin header) and is located on the top layer of the board. J46 is intended to be mated with a similar Fuji input connector (J47) on a board mounted directly on top of the first board. In this way, several boards can be connected in a stack. J47 is the Fuji input connector and is located on the bottom side of the board, in the same physical place as J46. The first board is powered and communicates through the Arduino connectors; the other attached boards draw power and communicate through the Fuji connectors.

#### 5.4 Arduino port

The connectors J5, J6, J35, and J36 are the mated pin headers of Arduino Uno R3 connectors, having the same electrical function and being placed on the board so that the daughter board can be directly inserted in the Arduino port. The daughter board circuit uses only seven signal lines. Table 2 shows the Arduino connector pins and how they are used in the circuit (see SPF-46842.pdf schematic file).

Table 2. Pin chart of Arduino connectors and their usage

| Ref Des    | # | Arduino label | PCA9959HN-ARD function |

|------------|---|---------------|------------------------|

|            | 1 | NC            | Not used               |

|            | 2 | IOREF         | Not used               |

|            | 3 | RESET         | Not used               |

| J6 (Power) | 4 | 3.3V          | Power supply           |

| Jo (Fower) | 5 | 5V            | Not used               |

|            | 6 | GND           | Power supply return    |

|            | 7 | GND           | Power supply return    |

|            | 8 | Vin           | Not used               |

#### PCA9959HN-ARD evaluation board

Table 2. Pin chart of Arduino connectors and their usage...continued

| Ref Des               | #  | Arduino label           | PCA9959HN-ARD function    |

|-----------------------|----|-------------------------|---------------------------|

|                       | 1  | A0                      | Not used                  |

|                       | 2  | A1                      | Not used                  |

| J35 (analog, digital, | 3  | A2                      | Not used                  |

| l <sup>2</sup> C)     | 4  | A3                      | Not used                  |

|                       | 5  | A4 / SDA <sup>[1]</sup> | Not used                  |

|                       | 6  | A5 / SCL [1]            | Not used                  |

|                       | 1  | D0 / RX                 | Not used                  |

|                       | 2  | D1 / TX                 | Not used                  |

|                       | 3  | D2                      | REXT SELECT (SW_EN)       |

| J5 (digital, UART,    | 4  | D3 / PWM                | Not used                  |

| PWM)                  | 5  | D4                      | Not used                  |

|                       | 6  | D5 / PWM                | Not used                  |

|                       | 7  | D6 / PWM                | Not used                  |

|                       | 8  | D7                      | Not used                  |

|                       | 1  | D8                      | RESET (RESET_B_D8)        |

|                       | 2  | D9 / PWM                | OUTPUT ENABLE (OE_B_D9)   |

|                       | 3  | D10 / SS / PWM          | SPI – SELECT (SPI_C0_D10) |

|                       | 4  | D11 / MOSI / PWM        | SPI – MOSI (SPI_MOSI_D11) |

| J36 (mixed)           | 5  | D12 / MISO              | SPI – MISO (SPI_MISO_D12) |

| JJO (IIIIXEU)         | 6  | D13 / SCK               | SPI – CLOCK (SPI_CLK)     |

|                       | 7  | GND                     | Power supply return       |

|                       | 8  | AREF                    | Not used                  |

|                       | 9  | A4 / SDA <sup>[1]</sup> | Not used                  |

|                       | 10 | A5 / SCL [1]            | Not used                  |

<sup>[1]</sup> A4 / SDA common line for J2 - 5 and J4 - 9. A5 / SCL common line for J2 - 6 and J4 - 10.

#### 5.5 Fuji connectors

Fuji connectors J46 and J47 allow several PCA9959HN-ARD daughter boards to be configured in a stack architecture. The connector J46 is the Fuji output pin header placed on top of the layout. Fuji connector J46 is the pin receptacle located on the bottom of the layout. When two boards are connected, J47 of the secondary board is inserted into Fuji output connector (J46) of the primary (base) daughter board. Table 3 shows the pin map of Fuji connectors and the function of the pins.

Table 3. Pin chart of Fuji connectors and their functions

| J46 | Fuji output connector (top)        | J47 | Fuji input connector (top)                                   |

|-----|------------------------------------|-----|--------------------------------------------------------------|

| 1   | 3.3 V rail distribution            | 1   | 3.3 V rail distribution                                      |

| 2   | 5 V rail distribution              | 2   | 5.0 V rail distribution                                      |

| 3   | Input control of switch U5         | 3   | Connected to GND. Close the switch U5 of the previous board. |

| 4   | I MAX (R EXT) control distribution | 4   | I MAX (R EXT) control distribution                           |

| 5   | RESET distribution                 | 5   | RESET distribution                                           |

#### PCA9959HN-ARD evaluation board

Table 3. Pin chart of Fuji connectors and their functions...continued

| J46 | Fuji output connector (top)                  | J47 | Fuji input connector (top)            |

|-----|----------------------------------------------|-----|---------------------------------------|

| 6   | SDO (U2) distribution to next board SDI (U2) | 6   | SDO (U2) from previous board          |

| 7   | OE distribution                              | 7   | OE distribution                       |

| 8   | SDO (U2) from last board to SPI-MISO         | 8   | SDO (U2) from next board (SDO bridge) |

| 9   | SPI – CS distribution                        | 9   | SPI – CS distribution                 |

| 10  | SPI – CLOCK distribution                     | 10  | SPI – CLOCK distribution              |

| 11  | GND                                          | 11  | GND                                   |

| 12  | GND                                          | 12  | GND                                   |

#### 5.6 SPI bus

The SPI bus has a daisy chain architecture. When a single daughter board (inserted in the Arduino port) is used, the MOSI line (J36, pin 4) goes from Arduino port to the DUT SDI input (U2, pin 6). The signal is turned back from SDO (U2, pin 4) through the switch U5 (closed), to the MISO input of the Arduino port (J36, pin 5). U5 is closed because the control input is pulled up (high state) through R89. When a secondary board is inserted into the Fuji output connector, the U5 control input located on the first board is pulled down to ground through pin 3 of J46 and J47 of the next board. The switch U5 (first board) is open, the signal path of the SPI is: MOSI (Arduino port) – SDI input (U2, first board) – SDO output (U2, first board) – pin 6 (J46 first board) – pin 6 (J47 second board) – SDI (U2, second board) – SDO (U2, second board) – U5 (second board which is closed) – pin 8 (J47, second board) – pin 8 (J46, first board) – MISO (Arduino port). The daisy chain loop is then closed through both DUTs on the two interconnected daughter boards. The SPI clock and chip select lines are sent directly to the DUT (U2) on the first card, and through the Fuji connectors to the secondary card.

For SPI characteristics and data format, see the PCA9959 data sheet Table 1 and Table 2, which details the pin map of the Arduino port and the Fuji connectors.

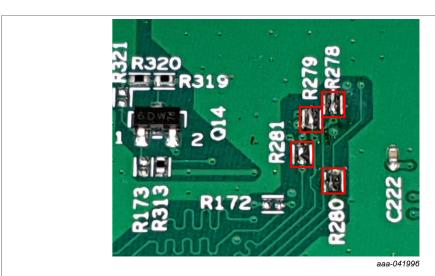

**Note:** For IMXRT1050 EVK, the SPI lines on the EVK board are not linked to the Arduino connector. Before using the EVK, the user must populate the DNP 0  $\Omega$  resistors R278 to R281 (see the EVK schematic diagram file SPF-30168\_A1.pdf, available at www.nxp.com.

#### PCA9959HN-ARD evaluation board

Figure 5. Location of the 0  $\Omega$  resistors R278 to R281 on the MIMXRT1050-EVK board

#### 5.7 Control bus

The control bus contains three additional control lines (purple color in <u>Figure 4</u>): OE (Output Enable), RESET, and I MAX. OE and RESET are routed to the OE and RESET inputs of the DUT, directly from Arduino port for the first (or base daughter board) and through Fuji connectors for the additional boards (pin 5, and pin 7).

The I MAX line controls the switch U4. When U4 is open, the resistor R83 is connected between the REXT input of the PCA9959HN (pin 39) and ground. R83 sets the maximum current delivered at the outputs of the DUT at 20 mA. When U4 is closed, R79 is paralleled with R83, the resulting maximum current increases to 50 mA. For more details regarding control lines, see the PCA9959 data sheet Table 1 and Table 2.

#### 5.8 LED section

The PCA9959HN features 24 LED drivers (PWM controlled, current sink sources). Four RGB LEDs are allocated to the first outputs (LED0 to LED11). The outputs LED12 to LED23 drives white LEDs. The LEDs can be disconnected from the IC outputs with jumpers.

The RGB LED D16 has jumpers connected in parallel for short testing. The jumpers J76 to J81 allow the user to redirect the corresponding output lines of D16 and D17 RGB LEDs from the onboard LEDs to the RGB LED external connectors (J21 and J26). Using the connectors, the user can easily attach external LEDs for testing. In the same manner, the corresponding lines of white LEDs D14 and D15 can be redirected with J82 and J83 jumpers to white LED external connectors J23 and J25.

#### 5.9 Power distribution

The power supply is provided from the EVK mother board for the first card, and through the Fuji connectors for all additional cards. There are two power rails: 3.3 V and 5.0 V. The main power consumption is from the 5.0 V power rail. The necessary current for one daughter board when all LEDs are turned ON is 1.2 A (I MAX: 50 mA). Due to current limitations, the number of boards installed in the stack is limited. The limitation depends

#### PCA9959HN-ARD evaluation board

on the type of EVK being used and the current rating of the Arduino/Fuji connectors (approx. 4.5 A). The current limitation as a function of the EVK is as follows:

- IMXRT1050 EVK:

- EVK powered from USB: limited by the current rating of the USB connector max. 2 boards

- EVK powered from power barrel connector (J2): limited by power rating of Arduino / Fuji connectors – max. 3 boards

- LPCXpresso55S69 EVK: limited by the current rating of the USB connector max. 2 boards

- i.MX LPDDR4 EVK: limited by the current delivered by the EVK power supply max. 2 boards

The onboard LED D2 is a 3.3 V rail indicator, and D3 is a 5.0 V rail indicator.

#### 5.10 Schematic, board layout and bill of materials

The schematic, board layout and bill of materials for the PCA9959HN-ARD evaluation board are available at <a href="http://www.nxp.com/PCA9959HN-ARD">http://www.nxp.com/PCA9959HN-ARD</a>.

PCA9959HN-ARD evaluation board

### 6 Installing and configuring software tools

PCA9959HN-ARD evaluation board is designed and built as a daughter board able to work with a mother board equipped with an Arduino port. The board was built to be fully compatible with the following NXP evaluation boards:

- MIMXRT1050-EVK

- LPC55S69-EVK

- 8MMINILPD4-EVK

Each of the above evaluation/development boards is supported by firmware that can be downloaded from the NXP site (<a href="www.nxp.com">www.nxp.com</a>). Before beginning to use a paired EVK – PCA9959HN-ARD configuration, the EVK motherboard must be programmed with the corresponding firmware package. Additionally, a GUI application (Windows 10) is available for download from the NXP site, allowing rapid testing and operation of the PCA9959HN-ARD daughter board in conjunction with the EVK. The GUI application is common for all three EVKs and for the PCA995x LED Controller development card family, manufactured by NXP (PCA9957, PCA9959, and PCA9955B ICs).

For details regarding installation of the EVK firmware and GUI host software, see <u>UM11581</u>, <u>Arduino shields GUI and firmware installation manual</u>.

Once the software is installed, the first step is to select the correct EVK from the graphical interface. The board can then be controlled from the GUI interface. See Section 7 "Configuring the hardware" and Section 8 "GUI description" for more details on using the GUI software to operate the PCA9959HN-ARD.

PCA9959HN-ARD evaluation board

### 7 Configuring the hardware

### 7.1 Using the PCA9959HN-ARD with MIMXRT1050-EVK board

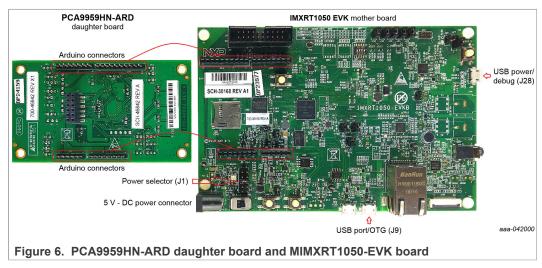

<u>Figure 6</u> shows the required hardware for operation of the PCA9959HN-ARD daughter board with MIMXRT1050-EVK.

The following hardware is necessary when working with this kit:

- One MIMXRT1050-EVK board

- One PCA9959HN-ARD daughter board

- One USB-A/USB Micro-B cable

- A PC with Windows 10 operating system

The MIMXRT1050-EVK mother board can be powered by one of the following three methods:

- Connecting an external 5 VDC power supply to the barrel power connector (J2) on the board

- Connecting a USB cable from the PC to the Micro-B USB connector (J9) on the board

- Connecting a USB cable from the PC to the USB connector (J28) on the board. When

the PC is connected in this fashion, the USB port can simultaneously act as a debug

interface. Therefore, by using a single USB cable connected to J28, the EVK can be

powered and at the same time linked to the PC for data exchange.

The older USB ports (from PC) are not able to deliver the necessary current (500 mA), before establishing the communication, use an external power supply (connected to J2).

From J1 on the EVK board (see <u>Figure 6</u>), the user can select the power configuration for the mother board. For more details, see <u>i.MX RT1050 Evaluation Kit</u>.

To configure the hardware and workstation, complete the following procedure:

- 1. On the MIMXRT1050-EVK board, populate R278, R279, R280, R281 with zero-ohm resistors (0402 package) to link the SPI lines to the Arduino connector (see Note in Section 5.6 "SPI bus").

- 2. Configure the suitable power configuration of EVK (J1). If using J28 for power supply, the J1 jumper shall be placed in position 5-6. If using an external power supply (connected to J2), the jumper J1 is placed in position 1-2.

#### PCA9959HN-ARD evaluation board

- 3. Insert the PCA9959HN-ARD daughter card into the Arduino connector on the EVK. See Figure 6.

- 4. Using USB connector J28, connect the EVK board to a USB port on the computer.

- 5. Install the IMXRT1050 target firmware (download from NXP site and see UM11581 for step-by-step instructions).

- 6. Install GUI application on PC (see <u>UM11581</u>, <u>Arduino shields GUI and firmware</u> installation manual).

- 7. Open the GUI application to operate the device from the PC. For details regarding GUI operation, see Section 8 "GUI description".

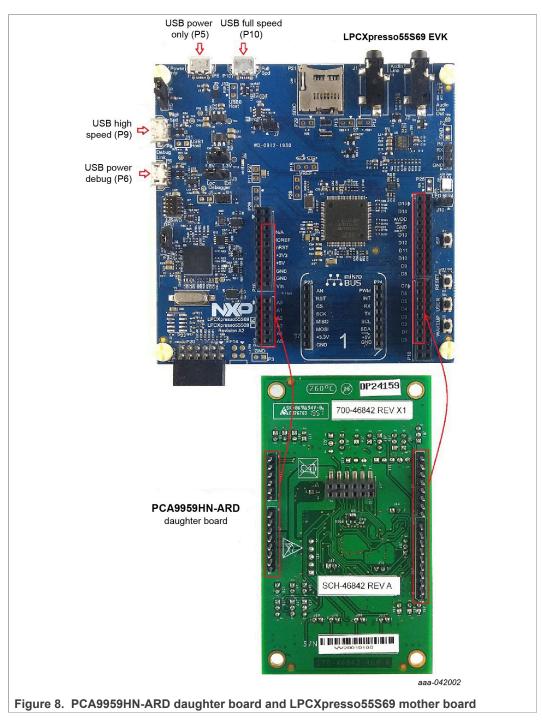

#### 7.2 Using the PCA9959HN-ARD with an LPCXpresso55S69 development board

Figure 8 shows the necessary hardware involved when using the PCA9959HN-ARD board with an LPCXpresso55S69 board. This configuration consists of:

- One LPCXpresso55S69 development board

- One PCA9959HN-ARD daughter board

- One USB-A/USB Micro-B cable

- A PC with Windows 10 operating system

The LPCXpresso55S69 development board is equipped with four USB Micro-B connectors: P5, P6, P9, and P10. The board can be powered through any USB port. Using P6 USB connector to connect the board to the PC simplifies the start-up operation because P6 is designated for debugging and the USB cable, thus accomplishing two tasks at the same time: powering the board, and serving as a data link between the EVK board and PC. For more details, see LPCXpresso55S69 Development Board.

#### PCA9959HN-ARD evaluation board

The following steps describe how to assemble, power up, program, and operate the configuration shown in Figure 8:

- 1. Insert the PCA9959HN-ARD daughter card to P16 P19 connectors located on LPCXpresso55S69 development board (see the marked pins of P16 P19, Figure 8).

- 2. Connect the development board using port P6 USB port of PC.

- 3. Install the LPCXpresso55S69 target firmware (download from NXP site and see <a href="UM11581"><u>UM11581</u></a> for step-by-step instructions).

#### PCA9959HN-ARD evaluation board

- 4. Install GUI application on PC (see <u>UM11581</u>, <u>Arduino shields GUI and firmware installation manual</u>).

- 5. Open the GUI application to operate the device from the PC. For details regarding GUI operation, see Section 8 "GUI description".

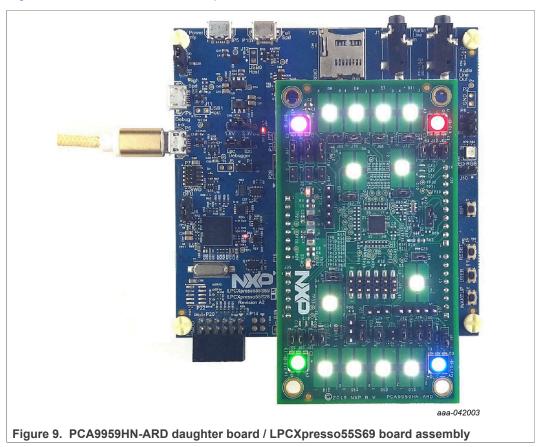

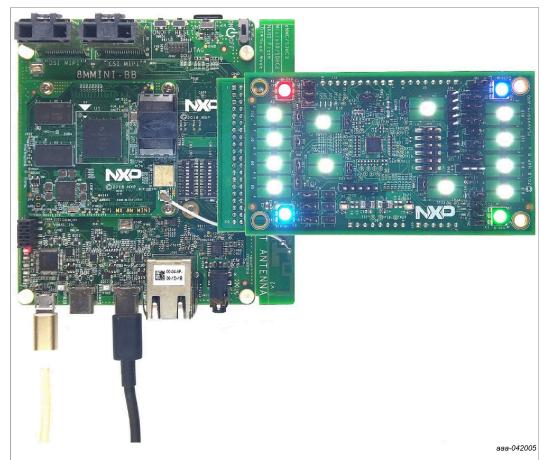

Figure 9 shows the two boards in operation.

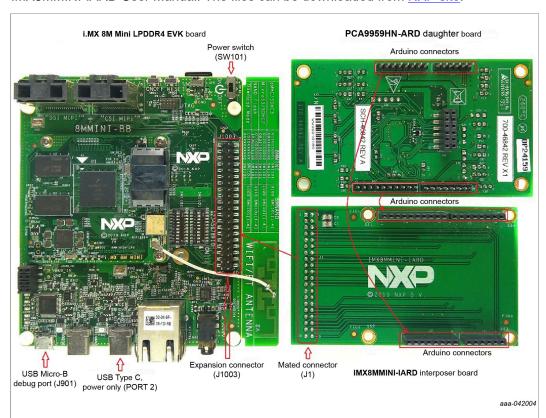

### 7.3 Using the PCA9959HN-ARD with an i.MX 8M Mini LPDDR4 EVK

When 8MMINILPD4-EVK board is used with the PCA9959HN-ARD board, a third board (IMX8MMINI-IARD interposer board) must be used, especially designed and built as EVK – daughter board interconnection. The EVK board i.MX 8M Mini LPDDR4 is not equipped with an Arduino port; instead it has a 2 x 20 pin expansion connector (J1003, see i.MX 8M Mini LPDDR4 EVK user manual). J1003 is a multipurpose port, containing various digital I/O lines, including specialized I<sup>2</sup>C and SPI buses. Starting from the expansion connector pin chart, an Arduino port interposer board was developed, with the role of signal-to-signal bridge between the 2 x 20 connector pins on the i.MX 8M Mini LPDDR4 EVK and the mated connectors of the Arduino port present on the PCA9959HN-ARD daughter board.

Figure 10 shows how these three boards are connected. This configuration consists of:

- One 8MMINILPD4-EVK board

- One PCA9959HN-ARD board

- One IMX8MMINI-IARD interposer board

- One USB-A / USB-C cable

PCA9959HN-ARD evaluation board

- One USB-A / USB Micro-B cable

- A PC with Windows 10 operating system

It is recommended to attach the PCA9959HN-ARD to the Arduino connectors of the IMX8MMINI-IARD interposer board first, and then the resulting assembly to the i.MX 8M Mini LPDDR4 EVK. This can be done by plugging J1 connector located on the interposer board to J1003 connector on the EVK.

To power up the EVK, an USB-C type cable connected to PORT 2 of the EVK is used. The power switch SW101 on the EVK board must be set to ON position to power up the setup. Data communication is achieved by routing a separate USB (Micro-B type) cable from a USB port on the PC to debug port (J901) on the EVK (see <u>Figure 10</u> and <u>Figure 11</u>).

For more details regarding the power-up and operation of the setup assembly, see *i.MX* 8M Mini LPDDR4 EVK Board Hardware User's Guide (IMX8MMEVKHUG.pdf), and IMX8MMINI-IARD User Manual. The files can be downloaded from NXP site.

Figure 10. PCA9959HN-ARD daughter board, IMX8MMINI-IARD interposer board, and 8MMINILPD4-EVK board assembly

To configure the hardware and workstation, complete the following procedure:

- 1. Insert the PCA9959HN-ARD onto the IMX8MMINI-IARD interposer board Arduino connectors (located on the top side).

- 2. Attach IMX8MMINI-IARD connector J1 (located on the bottom of the board) into J1003 expansion board located on the top side of i.MX 8M Mini LPDDR4 EVK (see Figure 10).

- 3. Power-up the EVK board using an USB Type C cable attached to Port 2.

- 4. Connect the EVK to the PC using a USB Micro-B cable attached to J901 debug port.

#### PCA9959HN-ARD evaluation board

- 5. Place SW101 in the ON position to power-up the boards.

- 6. Install the MIMXRT1050 target firmware (download from NXP site and see <a href="UM11581"><u>UM11581</u></a> for step-by-step instructions).

- 7. Install GUI application on PC (see <u>UM11581</u>, <u>Arduino shields GUI and firmware installation manual</u>).

- 8. Open the GUI application to operate the device from the PC. For details regarding GUI operation, see <u>Section 8 "GUI description"</u>.

Figure 11. PCA9959HN-ARD daughter board / 8MMINILPD4-EVK board operation

#### 7.4 Using the PCA9959HN-ARD with another device

The PCA9959HN-ARD daughter board can be operated with other EVK board, with an Arduino port. In this case, a firmware shall be developed according with PCA9959 specifications, and then attach PCA9959HN-ARD daughter board to the EVK to operate the board.

For non-Arduino devices, using the pin chart of Arduino connectors (see <u>Table 2</u>), make the necessary electrical connections (for power, SPI bus and control lines). Use PCA9959 data sheet for firmware development, according with IC specifications. Ensure accurate electrical connections and avoid data conflicts on the signal lines to prevent IC damage.

PCA9959HN-ARD evaluation board

### 8 GUI description

A GUI application is available for the three EVK boards from NXP Semiconductors. The application is common for all EVKs/development boards.

This section describes the GUI application and how the user can control the PCA9959HN-ARD daughter board from the graphical interface. First, install the GUI package and software on the PC (Windows 10). For more details, see <u>UM11581</u>.

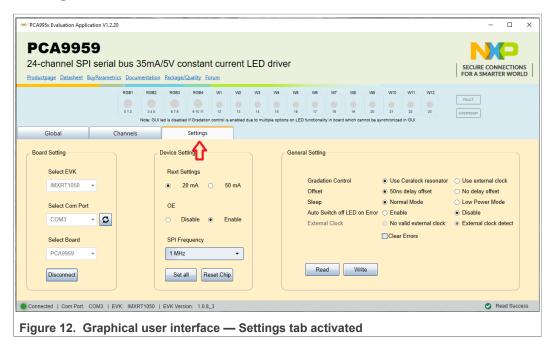

Once installation is complete, make sure that one of the three supported EVKs with the attached PCA9959HN-ARD daughter board is connected to the PC and powered-on. Open the NXP\_GUI(PCA995x) GUI application. An interface appears as shown in Figure 12.

#### 8.1 Settings

The GUI application starts with the **Settings** tab (marked with red arrow). In the right side of the blue region are located two read-only flags mapped in "MODE2 register (#01h). The **FAULT** flag indicates that the PCA9959HN-ARD's internal controller has detected an LED output error (no load, short). The **OVERTEMP** flag indicates that the PCA9959 die temperature exceeds its specified limit (see section 7.2.3 "LED error detection" and section 7.2.4 "Overtemperature protection" in PCA9959 data sheet).

**Note:** Due to the absence of status registers for the LED outputs in the PCA9959 IC, for the PCA9959HN-ARD board, the LED indicators on the GUI are not indicating the status of the onboard LEDs (there is no information to be read and displayed in the GUI).

Below the LED indicators are three sections: **General Setting** on the right, **Device Setting** in the middle, and **Board Setting** on the left.

**Board Setting** parameters are:

• **Select EVK** displays a list of EVKs. Selecting a wrong EVK board causes the connection to fail and a pop-up window with the message: "*Unable to Connect with EVK*" appears on the screen.

#### PCA9959HN-ARD evaluation board

- Select COM Port displays the port selected for the communication. The port is automatically selected by the system and is shown here as (COM3, Figure 12).

- **Select Board** allows the user to select the correct daughter board (the application can support three different boards). In <u>Figure 12</u>, the selected board is **PCA9959**. Selecting the wrong EVK or daughter board, causes the connection to fail and a pop-up window with the message: "*Unable to Connect with Daughter Card*" appears on the screen.

Click Connect to establish the connection with the EVK.

#### **Device Setting** parameters are:

- REXT Settings selects the maximum current delivered by the LED drivers. This

selection is determined by the status of switch U4 on the PCA9959HN-ARD board (see

Section 5 "Getting to know the hardware").

- **OE** controls the OE input of the DUT.

- **SPI Frequency** selects the bus speed. The drop-down box allows the selection of four values: 100 kHz, 1 MHz (default value), 4 MHz, and 10 MHz.

Clicking the **Set All** button at the bottom of the section causes the selected values to be set in the daughter board. Clicking **Reset Chip** returns the DUT's internal registers to their default values.

The PCA9959 device's internal controller has many 8-bit registers that provide detailed control, and error management. The internal registers are organized in four groups of LED gradation control, each LED channel being assigned to one of groups. For each group, PCA9959 supports 64-grid gradation brightness control, allowing for each LED output to be on with individual preset current value, or off. The GUI application is reflecting the PCA9959, allowing the user to set the values of the registers, without any constraint. Therefore, the user must fully understand the internal register map of the PCA9959 device. Additionally, in <a href="Section 9"Operation example">Section 9 "Operation example"</a> a set of instructions are provided, to help the user for quick check of the PCA9959HN-ARD board and understanding how to write the internal registers of the PCA9959 device.

#### **General Settings**

The displayed parameters in the section, belongs to internal registers "MODE1" and "MODE2" (00h, and 01h). See the PCA9959 device data sheet for bit level details regarding the mode registers. Set the values for each parameter and click the Write button to update the PCA9959 mode registers with the desired configuration. The **Read** button brings back the data from the mode register to GUI interface. The status bar located in the bottom side of the interface shows the connection status between the PC and the EVK.

**Note:** Due to high complexity of the internal register map and functions of PCA9959HN IC, for proper operation and testing of the daughter board from GUI application, the user should read in detail the data sheet of PCA9959 IC.

#### PCA9959HN-ARD evaluation board

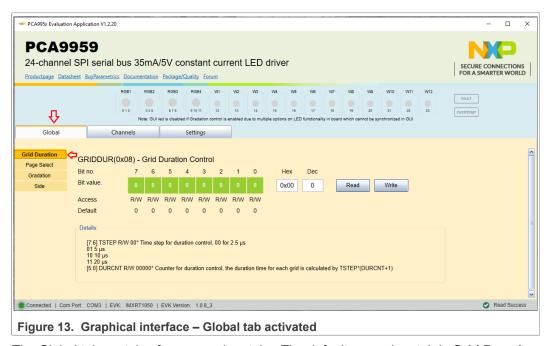

#### 8.2 Global

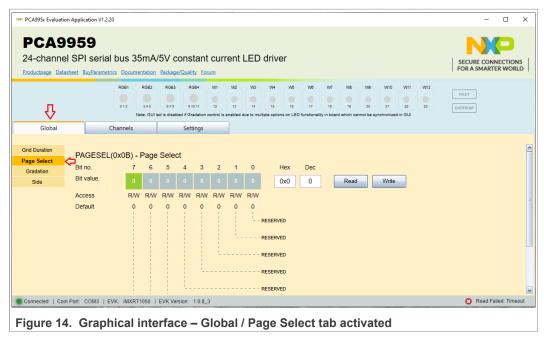

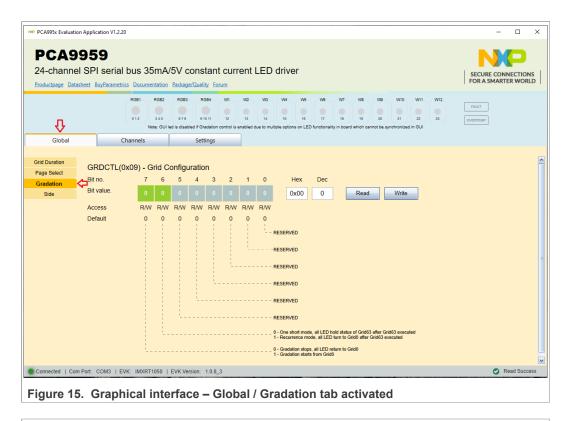

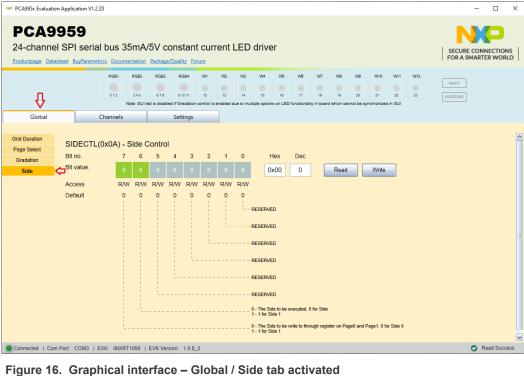

The Global tab contains four secondary tabs. The default secondary tab is **Grid Duration** (see the red arrows in <u>Figure 13</u>). The four secondary tabs set four internal registers of PCA9959 device. <u>Table 4</u> details the names and address of the registers.

Table 4. Secondary tabs under Global

| Secondary tab             | Register name | Register address | Remarks      |

|---------------------------|---------------|------------------|--------------|

| Grid Duration (Figure 13) | GRID_DUR      | #08h             | Read / Write |

| Page Select (Figure 14)   | PAGE_SEL      | #0Bh             | Read / Write |

| Gradation (Figure 15)     | GRD_CTL       | #09h             | Read / Write |

| Side (Figure 16)          | SIDE_CTL      | #0Ah             | Read / Write |

#### PCA9959HN-ARD evaluation board

#### 8.3 Channels

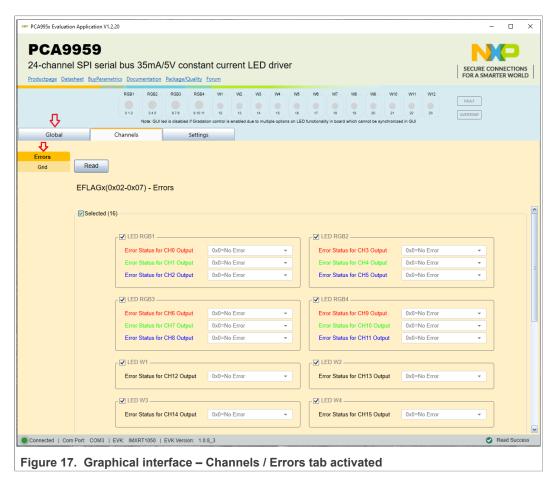

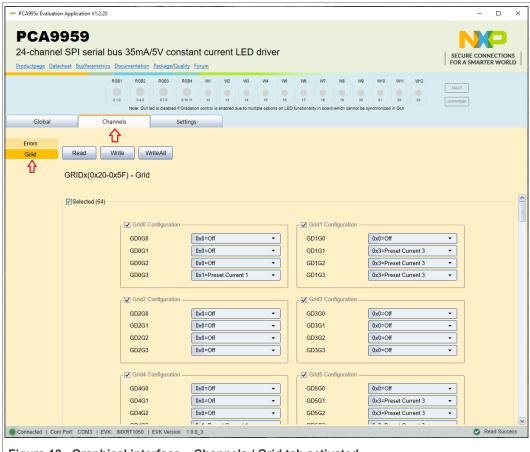

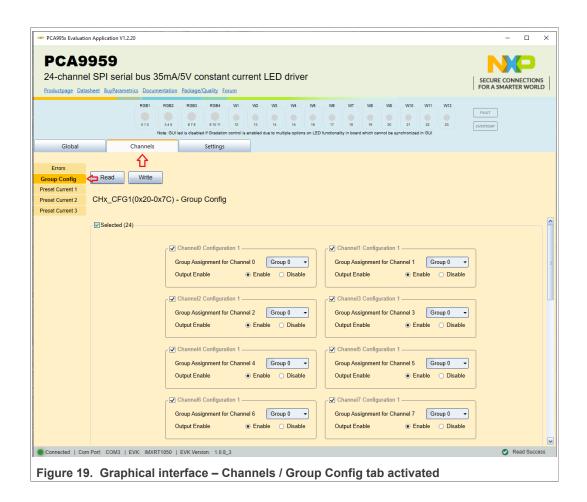

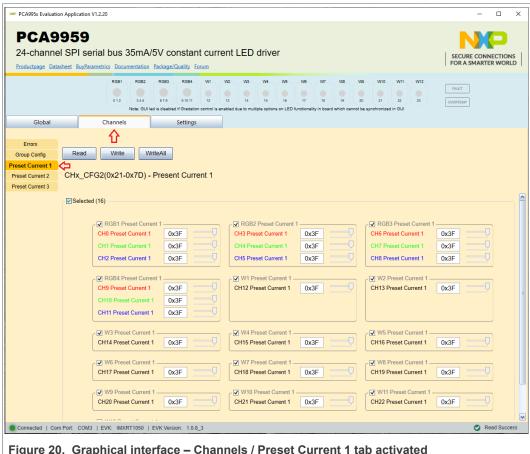

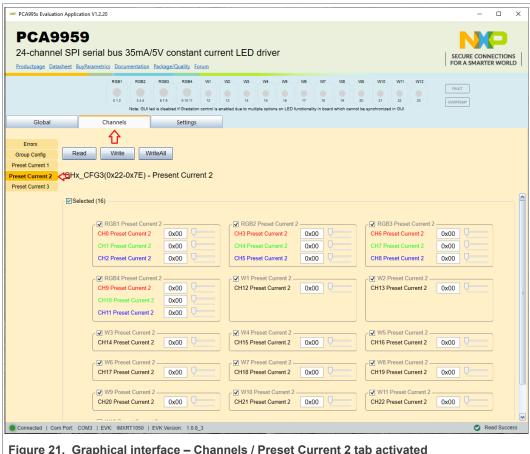

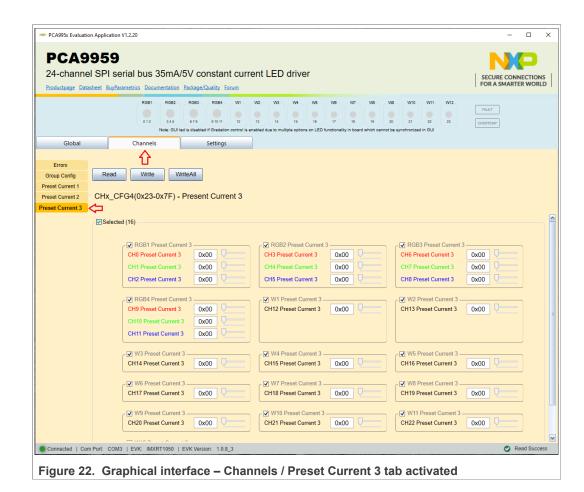

When **Channels** tab is activated, the displayed secondary tabs differ as a function of the value set for PAGE\_SEL register (see <u>Figure 14</u>). <u>Table 5</u> shows the **Channels** secondary tabs when PAGE\_SEL value is 0, while <u>Table 6</u> displays the group of secondary tabs when PAGE\_SEL value is 1.

Table 5. Secondary tabs under Channels - PAGE SEL 0

| Secondary tab               | Register name    | Register HEX | Remarks                  |

|-----------------------------|------------------|--------------|--------------------------|

| Errors ( <u>Figure 17</u> ) | EFLAG0 to EFLAG5 | #02h – #07h  | Read only                |

| Grid (Figure 18)            | GRID0 to GRID63  | #3Fh – #5Fh  | Read / Write / Write All |

Figure 18. Graphical interface - Channels / Grid tab activated

Table 6. Secondary tabs under Channels - PAGE\_SEL 1

| Tab                          | Register name         | Register HEX | Remarks                  |

|------------------------------|-----------------------|--------------|--------------------------|

| Errors (Figure 17)           | EFLAG0 to EFLAG5      | #02h – #07h  | Read only                |

| Group Config (Figure 19)     | CH0_CFG1 to CH23_CFG1 | #20h – #7Ch  | Read / Write             |

| Preset Current 1 (Figure 20) | CH0_CFG1 to CH23_CFG2 | #21h – #7Dh  | Read / Write / Write all |

| Preset Current 2 (Figure 21) | CH0_CFG1 to CH23_CFG3 | #22h – #7Eh  | Read / Write / Write all |

| Preset Current 3 (Figure 22) | CH0_CFG1 to CH23_CFG4 | #23h – #7Fh  | Read / Write / Write all |

Figure 20. Graphical interface - Channels / Preset Current 1 tab activated

Figure 21. Graphical interface - Channels / Preset Current 2 tab activated

#### PCA9959HN-ARD evaluation board

### 9 Operation example

This section details the necessary steps to operate the PCA9959HN-ARD daughter board with one of three EVKs from the GUI. This helps the user for a quick test of the board and to understand the register functionality. After the hardware and GUI software was installed, follow the below steps, to turn on and off one or more LEDs, located on the PCA9959HN-ARD daughter board:

- 1. Open the "NXP GUI(PCA995x)" application on the PC.

- 2. In the Board Setting section, from Select EVK list, select the EVK used in the setup.

- 3. From the Select COM Port list, select the correct COM (if more than one is available).

- 4. From the Select Board list, select PCA9959.

- 5. Click **Connect**. When the connection is established, all onboard LEDs are turned On.

- 6. In the Device Setting section, click **Reset Chip**. The LEDs are turned Off, and a popup window announces the successful chip reset.

- 7. Select "Disable" (for the "OE" input of the DUT), and click **Set all**. This disables the driver outputs inside the DUT.

- 8. In the General Settings section, select "Disable" option for Auto Switch off LED on Error, and then click **Write** to set the data to the internal register of the DUT.

- 9. Click Channels → Grid (see Figure 18).

- 10.In the new window, it can be seen all registers are set "0x0=Off" (the default value). Select for "GD0G0" ("Grid0 Configuration") the value: "0x1=Preset Current 1", and

#### PCA9959HN-ARD evaluation board

then click **WriteAll** button. This command sets all GD[x]G[y] internal registers with the "Preset Current 1" value.

- 11. Click **Global** → **Page Select** (see <u>Figure 13</u>). From the interface set the value "1" for bit 7 (in the displayed byte is the only active bit), and then click **Write**.

- 12.Go back to the **Channels** tab (a new interface appears, because the MSB of "PAGESEL" register was set with the value "1"). Click **Group Config** secondary tab (see Figure 19). Select "Enable" option for the corresponding channel of the LED you want to turn On (use the schematics to identify the corresponding channel). For a quick check of the entire board, select "Enable" for all 24 channels. At the end, click **Write** (to configure the internal registers of the DUT).

- 13.Click Preset Current 1 secondary tab (see Figure 20). From the "Preset Current 1" interface, you can select the desired current for each LED, and then click Write. If the desired current is the same for all selected channels, you can select the current for "CH0 Preset Current 1", and click WriteAll to set all channels with the same preset current.

- 14.Go back to the **Settings** tab, select Enable for OE, and then click **Set all**. The selected LEDs turn On, with the intensity according with the "Preset Current 1" value.

Starting from these steps and using the data sheet, the user can combine different values for the internal registers of the DUT, to understand, and test the functionality of the PCA9959 LED driver.

#### 10 Abbreviations

Table 7. Abbreviations

| Acronym              | Description                  |

|----------------------|------------------------------|

| DNP                  | Do Not Populate              |

| DUT                  | Device Under Test            |

| ESD                  | Electro Static Discharge     |

| EVK                  | Evaluation Board             |

| GUI                  | Graphical User Interface     |

| I <sup>2</sup> C bus | Inter-Integrated Circuit bus |

| IC                   | Integrated Circuit           |

| LED                  | Light Emitting Diode         |

| os                   | Overtemp Shutdown            |

| PC                   | Personal Computer            |

| SPI                  | Serial Peripheral Interface  |

| USB                  | Universal Serial Bus         |

|                      |                              |

#### 11 References

- 1. PCA9959 24-Channel SPI Serial Bus 63 mA/5.5 V Constant Current LED Driver

- 2. MIMXRT1050-EVK i.MX RT1050 Evaluation Kit

- 3. LPC55S69-EVK LPCXpresso55S69 Development Board

- 4. 8MMINILPD4-EVK Evaluation Kit for the i.MX 8M Mini Applications Processor

#### PCA9959HN-ARD evaluation board

### 12 Legal information

#### 12.1 Definitions

**Draft** — A draft status on a document indicates that the content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included in a draft version of a document and shall have no liability for the consequences of use of such information.

#### 12.2 Disclaimers

Limited warranty and liability - Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors. In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products. NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by

customer's third party customer(s). NXP does not accept any liability in this respect.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at http://www.nxp.com/profile/terms, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

Evaluation products — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer. In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages. Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

- Customer understands that all NXP products may be subject to unidentified or documented vulnerabilities. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

#### 12.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

$\ensuremath{\mathsf{NXP}}$  — wordmark and logo are trademarks of NXP B.V.

UM11623

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2021. All rights reserved.

### PCA9959HN-ARD evaluation board

### **Tables**

| Tab. 1.  | Revision history2                          | Tab. 5.  | Secondary tabs under Channels – PAGE_        |    |

|----------|--------------------------------------------|----------|----------------------------------------------|----|

| Tab. 2.  | Pin chart of Arduino connectors and their  |          | SEL 0                                        | 23 |

| <b>T</b> | usage7                                     | Tab. 6.  | Secondary tabs under Channels – PAGE_        |    |

| Tab. 3.  | Pin chart of Fuji connectors and their     |          | SEL 1                                        |    |

|          | functions8                                 | Tab. 7.  | Abbreviations                                | 29 |

| Tab. 4.  | Secondary tabs under Global21              |          |                                              |    |

| Figur    | es                                         |          |                                              |    |

| Fig. 1.  | PCA9959HN-ARD silkscreen (top view)5       | Fig. 13. | Graphical interface – Global tab activated   | 21 |

| Fig. 2.  | PCA9959HN-ARD board (top view)6            | Fig. 14. | Graphical interface – Global / Page Select   |    |

| Fig. 3.  | PCA9959HN-ARD board (bottom view) 6        |          | tab activated                                | 21 |

| Fig. 4.  | PCA9959HN-ARD block diagram7               | Fig. 15. | Graphical interface – Global / Gradation tab |    |

| Fig. 5.  | Location of the 0 Ω resistors R278 to R281 |          | activated                                    | 22 |

|          | on the MIMXRT1050-EVK board10              | Fig. 16. | Graphical interface – Global / Side tab      |    |

| Fig. 6.  | PCA9959HN-ARD daughter board and           |          | activated                                    | 22 |

|          | MIMXRT1050-EVK board13                     | Fig. 17. | Graphical interface – Channels / Errors tab  |    |

| Fig. 7.  | PCF85063AT-ARD daughter board /            |          | activated                                    | 23 |

|          | MIMXRT1050-EVK board assembly14            | Fig. 18. | Graphical interface – Channels / Grid tab    |    |

| Fig. 8.  | PCA9959HN-ARD daughter board and           |          | activated                                    | 24 |

|          | LPCXpresso55S69 mother board 15            | Fig. 19. | Graphical interface – Channels / Group       |    |

| Fig. 9.  | PCA9959HN-ARD daughter board /             |          | Config tab activated                         | 25 |

|          | LPCXpresso55S69 board assembly16           | Fig. 20. | Graphical interface – Channels / Preset      |    |

| Fig. 10. | PCA9959HN-ARD daughter board,              |          | Current 1 tab activated                      | 26 |

|          | IMX8MMINI-IARD interposer board, and       | Fig. 21. | Graphical interface – Channels / Preset      |    |

|          | 8MMINILPD4-EVK board assembly17            |          | Current 2 tab activated                      | 27 |

| Fig. 11. | PCA9959HN-ARD daughter board /             | Fig. 22. | Graphical interface – Channels / Preset      |    |

|          | 8MMINILPD4-EVK board operation 18          |          | Current 3 tab activated                      | 28 |

| Fig. 12. | Graphical user interface — Settings tab    |          |                                              |    |

|          | activated19                                |          |                                              |    |

### PCA9959HN-ARD evaluation board

### **Contents**

| 1    | Revision history                          |    |

|------|-------------------------------------------|----|

| 2    | Introduction                              | 3  |

| 3    | Finding kit resources and information on  |    |

|      | the NXP web site                          | 3  |

| 3.1  | Collaborate in the NXP community          | 3  |

| 4    | Getting ready                             | 3  |

| 4.1  | Kit contents                              |    |

| 4.2  | Assumptions                               | 4  |

| 4.3  | Static handling requirements              |    |

| 4.4  | Minimum system requirements               | 4  |

| 5    | Getting to know the hardware              | 5  |

| 5.1  | PCA9959HN-ARD features                    | 5  |

| 5.2  | Kit featured components                   | 5  |

| 5.3  | Block diagram                             | 6  |

| 5.4  | Arduino port                              | 7  |

| 5.5  | Fuji connectors                           |    |

| 5.6  | SPI bus                                   | 9  |

| 5.7  | Control bus                               |    |

| 5.8  | LED section                               | 10 |

| 5.9  | Power distribution                        | 10 |

| 5.10 | Schematic, board layout and bill of       |    |

|      | materials                                 | 11 |

| 6    | Installing and configuring software tools |    |

| 7    | Configuring the hardware                  | 13 |

| 7.1  | Using the PCA9959HN-ARD with              |    |

|      | MIMXRT1050-EVK board                      | 13 |

| 7.2  | Using the PCA9959HN-ARD with an           |    |

|      | LPCXpresso55S69 development board         | 14 |

| 7.3  | Using the PCA9959HN-ARD with an i.MX      |    |

|      | 8M Mini LPDDR4 EVK                        | 16 |

| 7.4  | Using the PCA9959HN-ARD with another      |    |

|      | device                                    |    |

| 8    | GUI description                           |    |

| 8.1  | Settings                                  |    |

| 8.2  | Global                                    |    |

| 8.3  | Channels                                  |    |

| 9    | Operation example                         |    |

| 10   | Abbreviations                             |    |

| 11   | References                                |    |

| 12   | Legal information                         | 30 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.