# **UM10741** Fm+ development kit OM13320 Rev. 1 – 1 April 2014

**User manual**

### **Document information**

| Info     | Content                                                            |

|----------|--------------------------------------------------------------------|

| Keywords | I2C-bus, Fm+, development tool, PCA9672, PCA9955                   |

| Abstract | User manual for the Fm+ development board (OM13260) kit (OM13320). |

### **Revision history**

| Rev | Date     | Description                  |

|-----|----------|------------------------------|

| 1.0 | 20140401 | User manual; initial release |

# **Contact information**

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

UM10741

User manual

# 1. Introduction

The Fm+ Development Kit (OM13320) is intended for several different tasks: from a hands-on introduction, understanding, and use of the  $l^2$ C-bus (Inter-Integrated Circuit bus), to  $l^2$ C device evaluation, and as a simple product demonstration platform (for trade shows and sales pitches).

The kit has a core Printed-Circuit Board (PCB) assembly, and three add-on PCBs. Other PCBs are available for advanced use or to support newly-released I<sup>2</sup>C-bus components as they are introduced to the market.

The Fm+ Development Kit (OM13320) is supported by a Graphics User Interface (GUI) software program that runs on a Personal Computer (PC) under the Microsoft Windows 7 Operation System. In some uses the GUI is not required, and the Fm+ Development Kit (OM13320) can be run as a standalone demonstration, requiring only an external power adapter (not included).

# 2. Key features

### I<sup>2</sup>C-bus masters

Self-contained PCB with two independent I<sup>2</sup>C buses

Bus 1: On-card I<sup>2</sup>C MCU master (NXP LPC1343)

Bus 2: NXP LPC Xpresso MCU module (not included), and NXP **PCA9665** bus controller

USB interface to on-card MCU (for connection to a PC running the GUI software)

### I<sup>2</sup>C-bus slaves

General Purpose Input/Output (GPIO): PCA9672 (one each on Bus1 and Bus2)

LED driver, with 16 constant current outputs: **PCA9955** (with four RGB and four White LEDs on Bus1)

### Accessory sockets

Connectors for up to four daughter cards, each providing power, Bus1 and Bus2 I<sup>2</sup>C signals

Connector for the Bus Buffer Board **OM13398** (supplied) containing two **PCA9617A** bus buffers

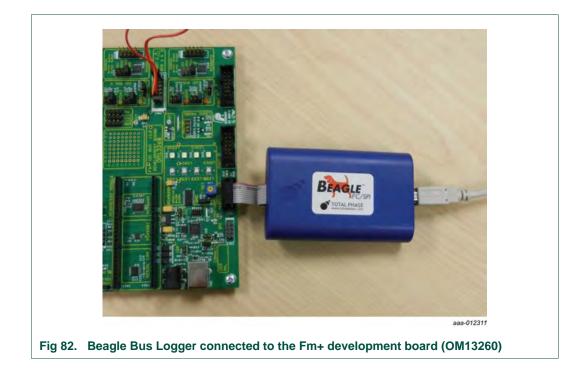

Connector for a third-party I<sup>2</sup>C-bus logger or I<sup>2</sup>C-bus controller (Beagle and Aardvark, from Total Phase)

### I<sup>2</sup>C buses

I<sup>2</sup>C-bus voltage: jumper select 5 V (external) or 3.3 V (on-card 3.3 V regulator) I<sup>2</sup>C-bus pull-up resistors: jumper select of 'high', 'med' or 'low' loading

### **Other features**

SPI ports: One for on-card MCU, two more for LPC Xpresso

Serial Com Port: EIA232 with voltage level shifter and connection to the LPC Xpresso

LED blinker: NXP PCA9901 one-wire with on-card LED

INT (Interrupt) and RST (Reset) Bus signal monitor LEDs (buffered)

Logic probe: Utility LEDs (buffered) to monitor signals by user jumper wire connection External DC input (6 V DC maximum)

Prototype area: Uncommitted  $8\times 8$  100 mil pitch tie points for end user component attachment

Test points and ground: for probe attachment to major signals

Connection of both I<sup>2</sup>C buses together (supplied 2-wire jumper)

# 3. Fm+ development kit quick tour

# 3.1 Kit contents

Before using the kit for the first time, please familiarize yourself with the various components listed in <u>Table 1</u>. See <u>Figure 1</u>.

**Remark:** Each PCB assembly is shipped in an anti-static bag. After the first use, these may be discarded to simplify future storage.

a. Top layer

Fig 1. Fm+ development kit

UM10741

### Table 1. Fm+ development kit contents

| omponents                                      |  |

|------------------------------------------------|--|

| m+ development board (OM13260)                 |  |

| PIO target board (OM13303)                     |  |

| CA9617A bus buffer demo board (OM13398)        |  |

| ridge board (OM13399)                          |  |

| able, USB Type A to Type B                     |  |

| ibbon cable, 10 position (bag of two)          |  |

| umper wires with female terminals (bag of ten) |  |

| horting jumpers (bag of twenty)                |  |

| ardware (bag of M3 screws and standoffs)       |  |

|                                                |  |

### 3.1.1 Box contents

The Fm+ Development Kit (OM13320) contains four PCB assemblies, cables, and loose hardware. These should be retained in the box for future access. Depending upon the desired use, some of the PCB assemblies may be attached to each other, either by plug connection or by 'stacking' the GPIO PCB assemblies above the Fm+ Development Board (OM13260), using the supplied ribbon cables and hardware.

# 3.2 Supplied PCB assemblies

There are four PCB assemblies in the kit. Each has a specific function and not all of them are used at the same time.

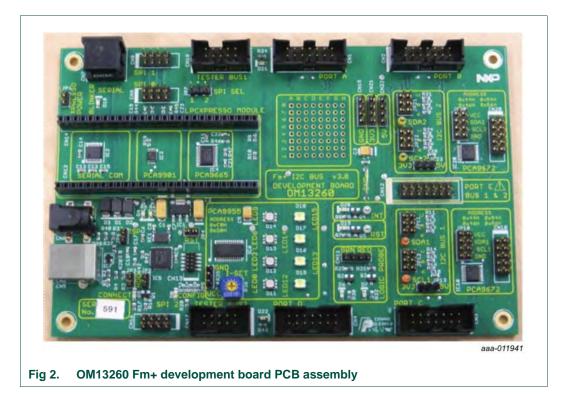

### 3.2.1 Fm+ Development Board (OM13260)

The large PCB, Figure 2, contains two separate I<sup>2</sup>C-bus structures, together with supporting circuitry. Each bus has a bus master, one or more bus slaves, and user options to change the bus voltage and bus pull-up resistors. Adjusting these changes the operation of the buses to suit various goals. In addition, the two buses may be linked together to operate a one I<sup>2</sup>C-bus structure. This can be done with a two-wire jumper (supplied) or the Bus Buffer Board OM133998 (supplied). See figure 3.5. Four identical ports provide access for add-on boards that contain additional I<sup>2</sup>C-bus devices.

# 3.2.2 GPIO target board (OM13303)

Outputs from the GPIO devices on the Fm+ Development Board (OM13260), and those when using GPIO daughter cards (not supplied in the kit), require the GPIO Target Board (OM13303). Each one has eight channels of LED indicator and push-button switches for user input. See Figure 3.

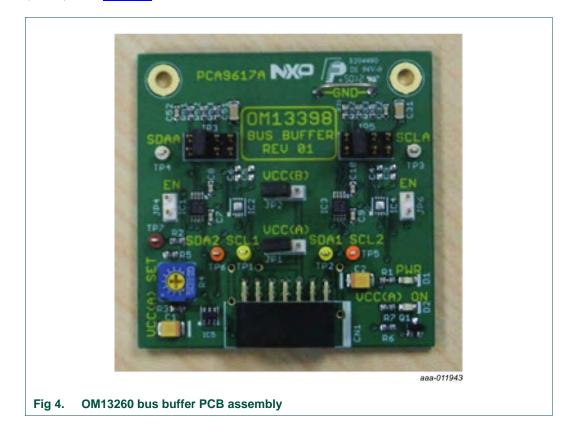

# 3.2.3 PCA9617A bus buffer demo board (OM13398)

Bus buffers bridge two I<sup>2</sup>C-bus segments, which are provided on the Fm+ Development Board (OM13260) by Bus1 and Bus2. Bus buffer daughter cards, such as the PCA9617A Bus Buffer Demo Board (OM13398) (supplied in the kit) can be installed directly on Port E (CN12). See Figure 4.

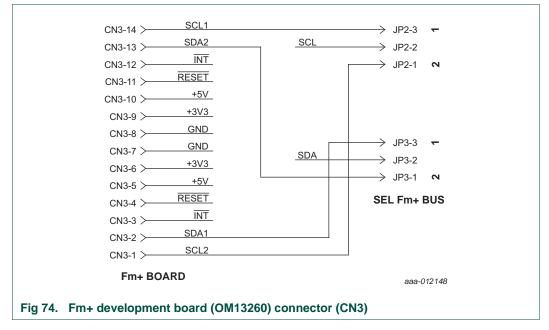

# 3.2.4 Bridge board (OM13398)

Some existing Demo Boards used a single row connector with nine pins. To use these with the Fm+ Development Kit requires the Bridge Board (OM13399, supplied in the kit). See Figure 5.

Fig 5. OM13399 bridge board PCB assembly

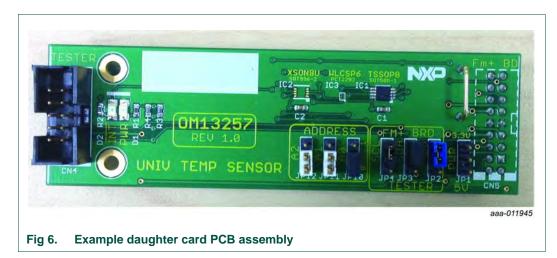

### 3.2.5 Daughter cards (not supplied in the kit)

These are not in the OM13230 kit, and should be obtained separately. Daughter cards hedge against obsolescence so that the Fm+ Development Kit (OM13320) can be used with future devices by adding newly released daughter cards as they become available. An example daughter card is shown in Figure 6.

# 4. First time setup: Fm+ development board kit (OM13320)

# 4.1 Before you begin

To use the Fm+ Development Kit (OM13320) for the first time requires some hardware setup and installation of both firmware (on the Fm+ Development Board OM13260) and software on the attached computer.

The following three steps must be completed:

- 1. Install Jumpers on the Fm+ Development Board (OM13260) (see Section 4.3).

- 2. Install Firmware on the Fm+ Development Board (OM13260) (see Section 4.6).

- Install the NXP GUI Software on the computer to be used with the kit (see <u>Section 4.7</u>).

### 4.2 First time setup of the Fm+ development board (OM13260)

Several jumpers must be installed before using the Fm+ Development Board (OM13260) PCB. The on-board microcontroller (MCU) must contain the appropriate firmware.

To install the firmware requires the connection to a Personal Computer (PC) running Microsoft Windows 7/64 Operating System and a USB port.

### 4.3 OM132680 jumpers

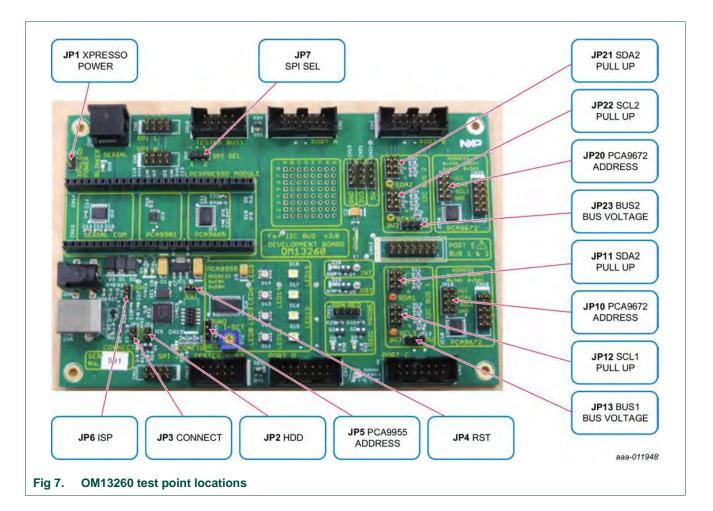

The jumpers and their function are shown in <u>Table 2</u>. Using <u>Figure 7</u> and the table data, install the jumpers.

|        | Own5200 Jumpers |                  |            |

|--------|-----------------|------------------|------------|

| Jumper | Label           | Function         | First time |

| JP1    | XPRESSO POWER   |                  | Close      |

| JP2    | HDD             |                  | Open       |

| JP3    | CONNECT         |                  | Close      |

| JP4    | RST             |                  | Open       |

| JP5    |                 | PCA9955 address  | GND        |

| JP6    | ISP             |                  | Open       |

| JP7    | SPI SEL         |                  | 1          |

| JP10   |                 | PCA9672 address  | GND        |

| JP11   |                 | SDA1 pull-up     | А          |

| JP12   |                 | SCL1 pull-up     | А          |

| JP13   |                 | Bus1 bus voltage | 3V3        |

| JP20   |                 | PCA9672 address  | GND        |

| JP21   |                 | SDA2 pull-up     | А          |

| JP22   |                 | SCL2 pull-up     | А          |

| JP23   |                 | Bus2 bus voltage | 3V3        |

|        |                 |                  |            |

### Table 2. OM13260 jumpers

### 4.4 OM13260 Port E bypass

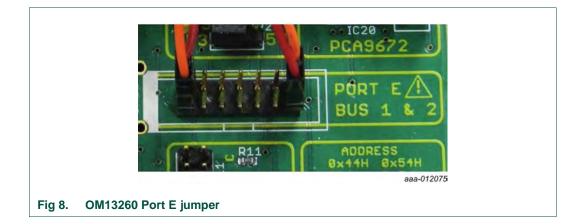

Depending up the intended operation of the Fm+ Development Board (OM13260), Port E (CN12) should be left open, or linked with a jumper wire, or for the attachment of a Bus Buffer Board. The PCA9617A Bus Buffer Demo Board (OM13398) is supplied in the kit.

For the purpose of this quick setup section, install the two-wire jumper (supplied) as shown in Figure 8.

**Remark:** The two-wire jumper requires a twist, as shown. The diagonally opposite pins are linked.

### 4.5 OM13260 mounting hardware

To prevent damage to the table surface, it is recommended that metal hardware (supplied in the kit) is installed in the four mounting holes. This raises the PCB assembly about 6 mm. See Figure 9.

**Remark:** Save the completed Fm+ Development Board, now install the NXP USB Driver.

# 4.6 NXP firmware installation

The micro on the Fm+ Development Board needs firmware running on it to interface with the GUI running on a Windows 7 PC over USB. The board is shipped with a blank microprocessor, so user action is necessary for proper operation.

An installation user manual UM10785 ( $\underline{\text{Ref. 1}}$ ) is available at for a complete explanation of the process. A quick overview is presented here.

- 1. Download NXP\_Fm+\_Eval\_Board\_V1\_0\_firmware.zip from www.nxp.com/demoboard/OM13320.html#documentation

- 2. Connect a USB cable from the PC USB port to CN5.

- 3. Install the Connect (JP3) jumper to connect the USB communications.

- 4. Install the ISP (JP6) jumper to put the MCU into In-System Programming mode.

- 5. Install and then remove RST (JP4) jumper to reset the MCU.

- 6. The MCU will enumerate on the PC as a disk drive called CRP\_DISABLD.

- 7. Delete the file on the MCU (size may vary up to 32 kB).

- 8. Copy the new firmware file **NXP\_Fm\_Eval\_Board\_V1\_0.bin**, extracted from the zip file to the MCU.

- 9. Remove the ISP (JP6) jumper.

- 10. Install and then remove RST (JP4) jumper to reset the MCU.

### 4.7 NXP GUI installation

A Graphical User Interface (GUI) is provided which allows easy manipulation of the devices included on the Fm+ Development Board and many others that can be connected to the board via daughter cards.

An installation user manual UM10785 (<u>Ref. 1</u>) is available for a complete explanation of the process. A quick overview is presented here.

- 1. Download NXP\_Fm\_Board\_V1\_0\_Installation.zip from www.nxp.com/demoboard/OM13320.html#documentation

- 2. Extract NXP Fm+ Board V1.0 Installation.exe and run.

- 3. Follow the instruction prompts. Select the default answers.

This GUI uses a USB Human Interface Driver (HID), so no driver installation is required.

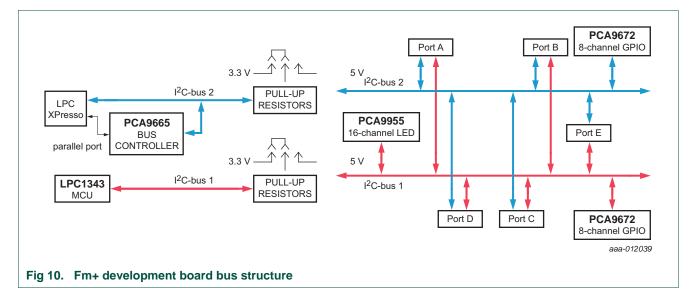

If the firmware and GUI installs are successful, an Fm+ Development Board block diagram is displayed when the GUI executes (Figure 10).

# 5. Fm+ development board (OM13260)

The Fm+ Development Board (OM13260) PCB assembly is self-contained, requiring only DC power to operate. Depending upon the firmware installed on the Fm+ Development Board (OM13260), it can also operate with a connected Personal Computer (PC) via a USB cable.

The modular design of the kit and this board in particular allows accessory boards to be easily connected.

# 5.1 Theory of operation

An I<sup>2</sup>C-bus requires a Master and one or more Slaves. The two bus signals, clock SCL and data SDA, are wired-OR and require pull-ups to a DC power supply. Two similar but separate I<sup>2</sup>C buses each support one Master and at least one Slave device on the board. The two buses may be linked by either a Bus Buffer Board (OM13398 supplied in the kit) or a wire jumper, at the Port E connector (CN12).

The signals from both buses are available simultaneously at each of four connectors, Port A through Port D (CN1 through CN4, respectively). These are intended for attachment of accessory daughter cards, which will be made available as future I<sup>2</sup>C-bus devices are released.

The size of the pull-up resistors can be changed by moving shorting jumpers (JP1, JP2, JP11, and JP12), providing selection of 'Low' 'Med' and 'High' resistor values scaled to the  $Fm+I^2C$ -bus drive strength. When both buses are joined by a jumper wire, the pull-ups are effectively in parallel, and have one-half the stated resistance values.

Operating voltage of the  $I^2$ C-bus depends upon the shorting jumpers (JP13 and JP23) that select either 3.3 V or 5 V connected to the pull-up resistors. Compliant  $I^2$ C-bus devices can tolerate 5.5 V (maximum), regardless of the device operating voltage.

Each bus has a GPIO 8-bit Slave device (PCA9672, IC10 and IC20), and Bus 1 also has an LED Driver 16-channel device (PCA9955, IC6). All sixteen outputs are connected to LEDs, for visual indication. The 8-bit GPIOs require connection of GPIO Target Boards (OM13303, supplied in the kit) to both indicate the output using eight LEDs and allow user input from eight push switches.

An NXP LPC1343 Microcontroller (MCU) serves as both the Bus 1 Master, and the USB link. The firmware on the MCU can be replaced by the In-System Programming (ISP) mode, with data sent over the USB link (CN5).

Bus 2 has a Parallel to I<sup>2</sup>C-bus Controller device (PCA9665, IC6), which is to be driven by an optional NXP LPC Xpresso module (not supplied). That module is also an I<sup>2</sup>C Master and connected to Bus 2.

**Remark:** Although Bus 2 has more than one I<sup>2</sup>C Master, only one is active at any time.

The remaining circuitry is to support the  $I^2C$  devices, and provide communications with the PC over a USB link.

The main operating voltage on the Fm+ Development Board (OM13260) is 3.3 V supplied from a linear regulator (IC1). Some circuits and the optional I<sup>2</sup>C-bus pull-ups may run from 5 V derived either from the USB host (typically a PC) or an AC-DC power supply (not supplied in the kit). The actual voltage is seldom 5 V, due to cable losses, plus an additional drop in a series connected diode used to OR the two inputs. Whichever has the highest voltage has priority.

A shunt Zener diode (6.2 V) protects the board from reverse polarity and overvoltage at the DC Power connector (CN6).

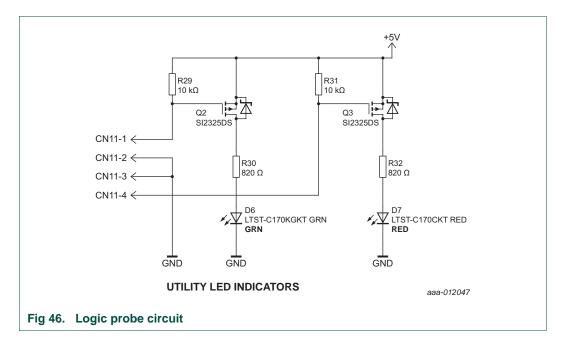

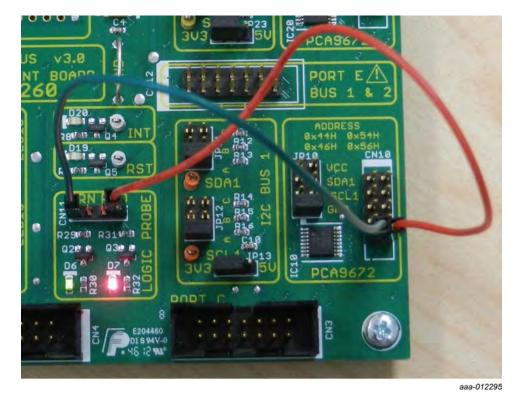

To aid in understanding digital signal levels on the board, two 'logic probe' circuits are provided. These are buffered LEDs (Green, D6 and Red, D7), which light if their respective inputs (CN11) are grounded.

Two global digital signal nets, called INT (interrupt) and RST (reset) connect all  $I^2$ C-bus devices on the board and also the Port A – Port E Daughter Card connectors. These are also connected to the Master (MCU, IC5) on Bus 1, the Master (Bus Controller, IC4), and the LPC Xpresso module.

**Remark:** The I<sup>2</sup>C global Reset is not the same as the MCU Reset. Resetting the MCU will only reset the I<sup>2</sup>C-bus if the MCU firmware is intended to create a global reset.

The test points provide monitoring of interrupts (usually generated by I<sup>2</sup>C-bus Slaves) and software reset of Fm+ class I<sup>2</sup>C-bus devices that have that feature.

Additional buffered LEDs are provided (D19, RST and D20, Interrupt) on the Fm+ Development Board (OM13260) for visual indication.

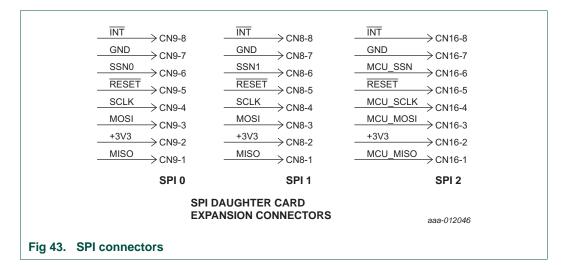

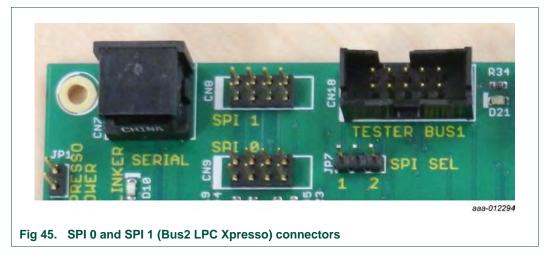

Various MCU and LPC Xpresso signals are made available through additional connectors. These include a serial Port (CN7) with EIA232 voltage level translation (IC2) and SPI Bus signals (SP0, CN9 and SP1, CN8) from the LPC Xpresso module, together with SPI Bus (SP2, CN16) from the MCU (IC5).

A prototyping area is provided for solder connection of components that may be required by an application circuit beyond this board's design. Power supplies and other signals are readily available.

UM10741

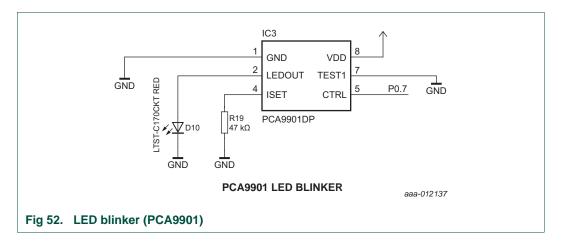

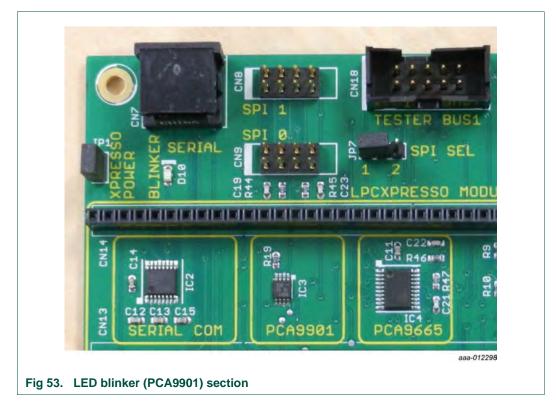

On the Fm+ Development Board (OM13260) V3.0 there is an LED Blinker device (PCA9901, IC3) and LED indicator (D10), while not strictly an I<sup>2</sup>C device as it uses a one-wire protocol, it belongs to the NXP I<sup>2</sup>C-bus product portfolio.

**Remark:** The PCA9901 will be made obsolete, and will not be present on future versions of the Fm+ Development Board (OM13260).

The operation of the Fm+ Development Board (OM13260) is greatly enhanced by third-party tools (not supplied in the kit) that may be attached to either I<sup>2</sup>C-bus through dedicated connectors (Bus1, CN17 and Bus2, CN18), labeled 'TESTER'.

### 5.2 Circuit description

The schematic diagram has multiple sheets. For clarification, only fragments of the schematic are shown here. The full schematic should be downloaded if required. The following pages are divided in to several sections covering the power supply, USB interface, Bus1, Bus2, and support circuits.

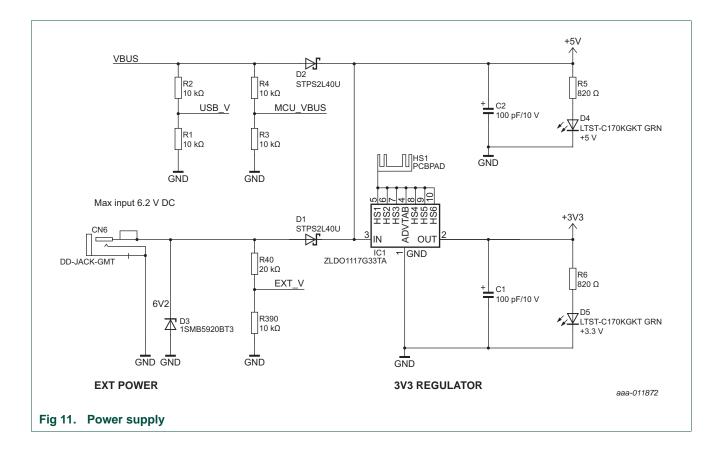

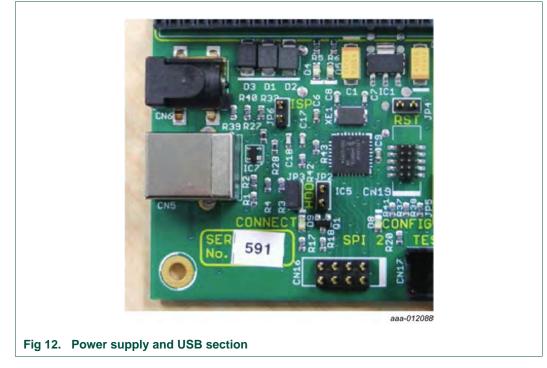

### 5.2.1 Power supply

The Fm+ Development Board (OM13260) operates from DC, either from the USB Host connector (CN5) or an optional external AC-DC power adapter (not supplied in the kit) via connector (CN6). See Figure 11 and Figure 12. Selection of the power source is automatic, using ORing diodes (D1 and D2). The main power on the Fm+ Development Board (OM13260) is 3.3 V from a linear regulator (IC1), but some of the circuits are powered directly from the incoming supply, which is a nominal 5 V. Linear regulator (IC1) uses the PCB bottom layer copper as a heat sink. The Fm+ Development Board (OM13260) external DC input is protected against reverse polarity or overvoltage by Zener diode (D3). Both input sources are scaled by resistor dividers (R1, R2 and R39, R40) and fed to the MCU (IC5) Port1 ADC inputs for voltage level monitoring. The VBUS from the USB Host is fed to the MCU Port 0 so that the MCU can detect that a USB connection is available. Green LED (D4) confirms 5 V, and Green LED (D5) confirms 3.3 V.

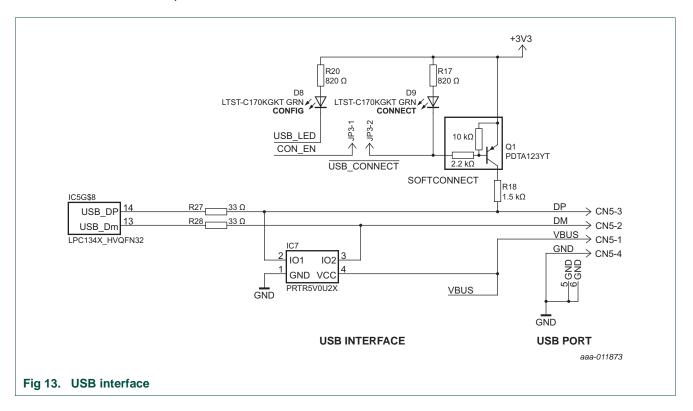

### 5.2.2 USB interface

The USB Host connector (CN5) provides DC power and USB connectivity using the MCU (IC5) hardware interface, see Figure 12 and Figure 13. USB data lines are terminated by resistors (R27 and R28) and protected by an ESD network (IC7). To signal to the host that the USB connection is required, the USB signal DP is pulled to 3.3 V via a resistor (R18) and a transistor (Q1). USB Connection is controlled by the MCU (IC5) via signal CON\_EN and can be disabled by removing a jumper (JP3) 'CONNECT'. When the MCU requests a USB connection, and the jumper (JP3) is installed, the green LED (D9) is ON. MCU activity is displayed by the Heart Beat green LED (D8), which is set to blink at about one per second.

# 5.3 Bus one (Bus1)

There are two almost identical I<sup>2</sup>C buses on the Fm+ Development Board (OM13260), called Bus1 and Bus2. These share a ground and power connection but may be operated independently.

**Remark:** The bus voltage for each  $I^2C$  may be different (for example 3.3 V for one  $I^2C$ -bus, 5 V for the other  $I^2C$ -bus).

### 5.3.1 Bus1 master (MCU LPC1343)

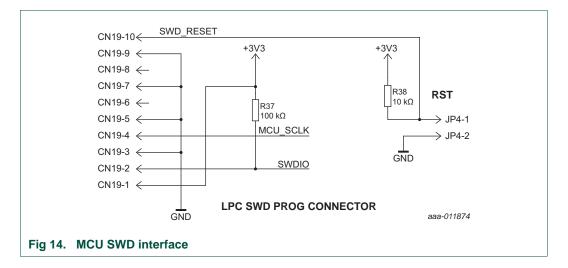

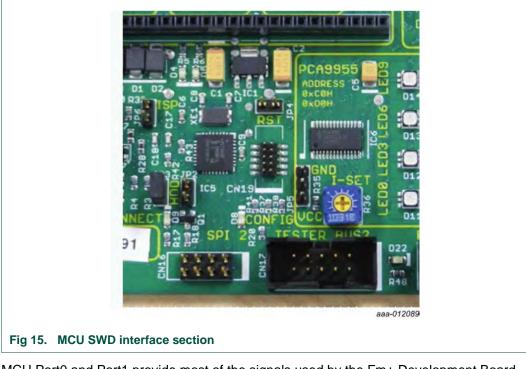

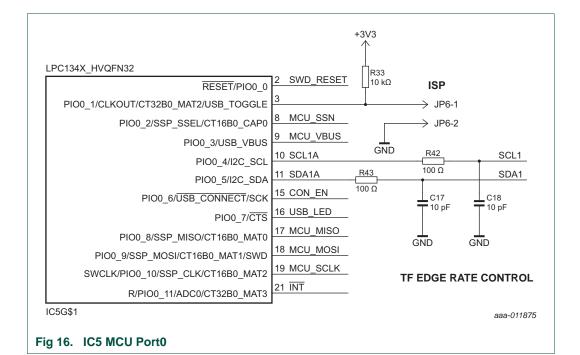

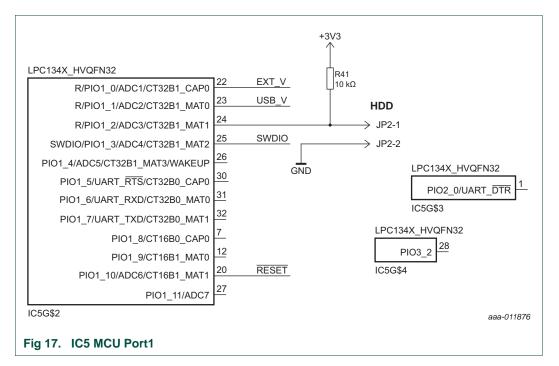

Microcontroller (MCU) (LPC1343, IC5) serves as the Bus1 Master and the USB Bridge. Firmware installed on the Fm+ Development Board (OM13260) is stored in non-volatile memory, which has a limit of 32 kB. The MCU may be programmed through the USB port or the JTAG connector (CN 19), using Single Wire Debug (SWD), see <u>Figure 14</u> and <u>Figure 15</u>. During programming or at other times it may be necessary to reset the MCU, by briefly shorting JP4 (see Figure 15).

**Remark:** An MCU Reset is not the same as an  $I^2C$  Bus Reset. Resetting the MCU will not affect the  $I^2C$ -bus, unless the MCU firmware is designed to issue an  $I^2C$  Bus Reset when it is reset.

MCU Port0 and Port1 provide most of the signals used by the Fm+ Development Board (OM13260), see Figure 16 and Figure 17. I<sup>2</sup>C Bus1 is connected to the MCU Port0 via RC edge rate control networks that provide bus fall time control (SCL1: R42 and C18; SDA1: R43 and C17).

| UM10741 |  |  |

|---------|--|--|

|         |  |  |

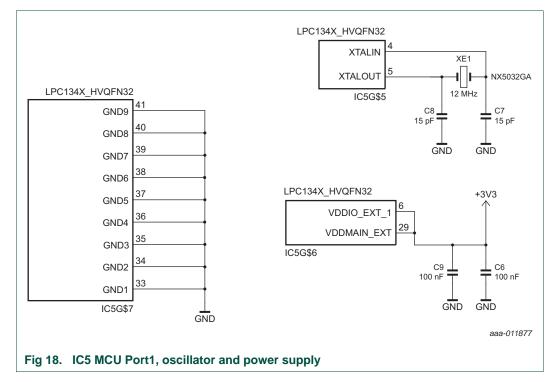

The HVQN32 package has a thermal pad ground connection, and operates from the main 3.3 V supply. The MCU operates with a 12.00 MHz crystal controlled oscillator. The frequency value and accuracy is necessary for correct USB timing (see Figure 18).

### 5.3.2 Bus1 pull-up resistors

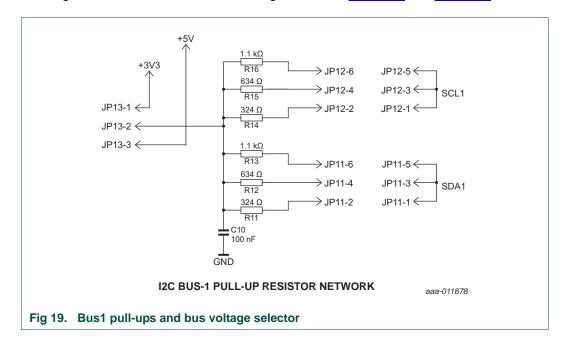

The Bus1 is pulled up to either the 3.3 V or 5 V supplies via JP13. Three different value pull-up resistors are provided by jumper selection, JP11 and JP12. The values of the pull-up resistors are shown in <u>Table 3</u>. Separate pull-ups are provided for the SCL and SDA signal lines. Bus2 has a similar arrangement. See Figure 19 and Figure 20.

### UM10741

# UM10741

### Fm+ development kit OM13320

### Fig 20. Bus1 pull-ups section

### Table 3. Bus pull-up resistors

| Strength | Position | Value  | Bus1 SCL | Bus1 SDA | Bus2 SCL | Bus2 SDA |

|----------|----------|--------|----------|----------|----------|----------|

| LOW      | A        | 1.1 kΩ | R16      | R13      | R26      | R23      |

| MID      | В        | 634 Ω  | R15      | R12      | R25      | R22      |

| HIGH     | С        | 324 Ω  | R14      | R11      | R24      | R21      |

### 5.3.3 LED driver slave (PCA9955)

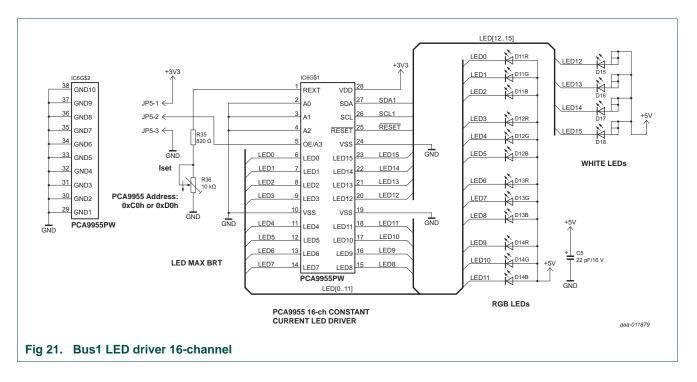

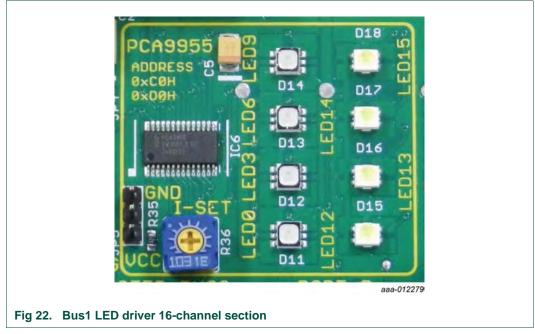

Bus1 is also used to control the LED Driver (PCA9955, IC6). The LED Driver has constant current outputs and is directly connected to the LEDs, without customary series resistors. The LEDs are powered directly from the 5 V supply, thus avoiding further power dissipation in the 3.3 V linear regulator, IC1. The sixteen channels drive eight LED clusters consisting of four White LEDs (LED12 – LED15) and four RGB LED clusters (LED0 – LED11). The maximum current available for each channel is set by R35 and the variable resistor R36. The LEDs use the PCB top metal for heat dissipation, the LED driver is in the HTSSOP28 package has a thermal pad ground connection, and operates from the main 3.3 V supply. See Figure 21 and Figure 22.

UM10741

Operation of all sixteen LEDs at maximum current will overheat the LED driver, which is protected by an internal thermal limiter. The device will shut down and recover when the temperature has fallen.

When powered from the USB port (CN5) the USB Host is typically limited to 500 mA, and it will shut down before the LEDs reach maximum current. Operation from an external DC power supply connection (CN6) is required to drive the LEDs to the maximum current per channel of 57 mA, for a total of approximately 1 A.

**User manual**

The recommended AC-DC adapter is Digikey PN: 62-1132-ND (not supplied). See Figure 23.

The Slave address is set by JP5, summarized in Table 4.

**Remark:** The PCB is marked with hexadecimal (8-bit) address data, but data sheets and the NXP GUI use the 7-bit address values. See Table 4.

### Table 4. LED driver address selection

| JP5 connected to |      |      |      | NXP 7-bit | NXP 7-bit address |      |  |

|------------------|------|------|------|-----------|-------------------|------|--|

|                  |      |      |      | Address   | MSB               | LSB  |  |

| GND              | 0xC0 | 1100 | 0000 | 0x60      | 110               | 0000 |  |

| V <sub>CC</sub>  | 0xD0 | 1101 | 0000 | 0x68      | 110               | 1000 |  |

### 5.3.4 GPIO slave (PCA9672)

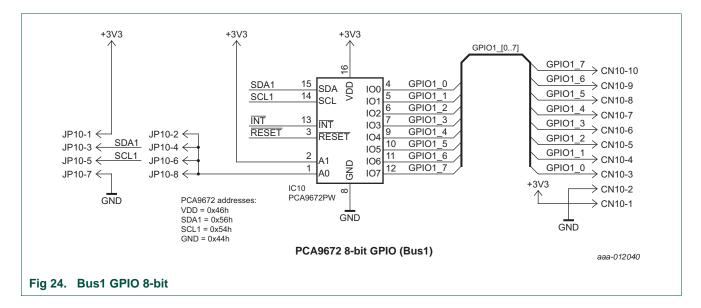

The GPIO (PCA9672, IC10) is connected to Bus1, and provides eight input/output channels at CN10. Jumper JP10 sets the device address to one of four options, depending on whether the A0 pin is connected to GND,  $V_{CC}$ , SCL, or SDA. Bus2 has a similar arrangement for a second GPIO (PCA9672, IC20). See Figure 24 and Figure 25.

**Remark:** The PCB is marked with hexadecimal (8-bit) address data, but data sheets and the NXP GUI use the 7-bit address values. This is summarized in Table 5.

### Table 5. LED driver address selection

| A0 connected to | Hexadecimal 8-bit address |      |      | NXP 7-bit | NXP 7-bit address |      |  |

|-----------------|---------------------------|------|------|-----------|-------------------|------|--|

|                 | Address                   | MSB  | LSB  | Address   | MSB               | LSB  |  |

| GND             | 0x44                      | 0100 | 0100 | 0x22      | 010               | 0010 |  |

| V <sub>CC</sub> | 0x46                      | 0100 | 0110 | 0x23      | 010               | 0011 |  |

| SCL             | 0x54                      | 0101 | 0100 | 0x2A      | 010               | 1010 |  |

| SDA             | 0x56                      | 0101 | 0110 | 0x2B      | 010               | 1011 |  |

UM10741

All information provided in this document is subject to legal disclaimers.

# 5.4 Bus two (Bus2)

The second I<sup>2</sup>C bus on the Fm+ Development Board (OM13260) requires the addition of an NXP LPC Xpresso Module (not included in the kit) to either be the Master, or drive the bus controller (PCA9665, IC4).

There are two almost identical I<sup>2</sup>C buses on the Fm+ Development Board (OM13260), called Bus1 and Bus2. These share a ground and power connection, but may be operated independently.

**Remark:** The bus voltage for each  $I^2C$  maybe different (for example 3.3 V for one  $I^2C$  bus, 5 V for the other  $I^2C$  bus).

### 5.4.1 Bus2 master (LPC Xpresso — MCU LPC1343)

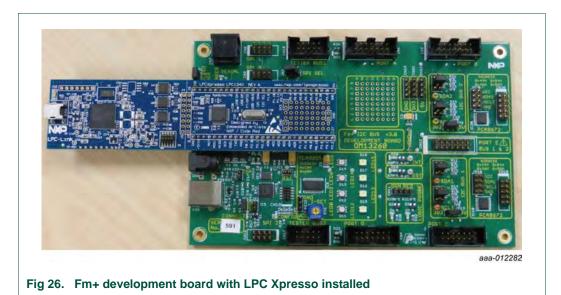

The LPC Xpresso Module contains an NXP LPC1343 MCU (similar to the one on Bus 1) and support circuits called LPC-Link. See <u>Figure 26</u>. The LPC Xpresso requires firmware that is loaded through either the LPC-Link and USB Bridge, or JTAG Single Wire Debug (SWD) connector.

**Remark:** The LPC Xpresso is not compatible with the NXP GUI, and requires the installation of an IDE for code development.

The LPC-Link may be powered from the Fm+ Development Board (OM13260), or from a USB Host (connected to the LPC-Link port). There is a possible conflict that the LCP-Link 3.3 V supply will compete with the Fm+ Development Board (OM13260) 3.3 V supply. To avoid this issue the LPC Xpresso Module can provide its own 3.3 V power by removing jumper JP1 on the Fm+ Development Board (OM13260). See Figure 27.

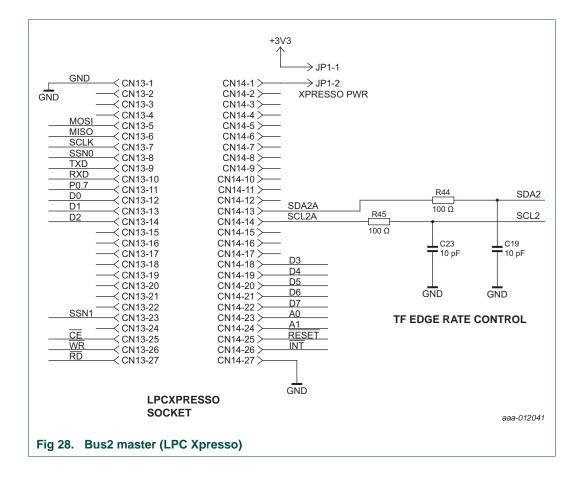

I<sup>2</sup>C Bus2 is connected to the MCU Port0 via RC edge rate control networks that provide bus fall time control (SCL2: R45 and C23; SDA1: R44 and C19). See Figure 28.

### 5.4.2 Bus2 bus master (PCA9665)

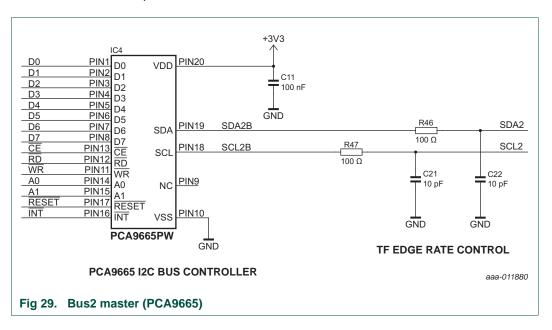

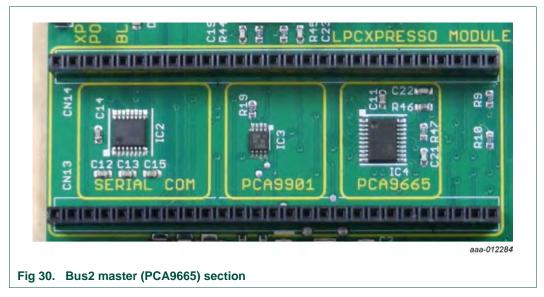

A second Bus Master is connected to Bus2 using a dedicated Bus Controller device (PCA9665 Fm+ parallel bus to I<sup>2</sup>C-bus controller) (IC4). The parallel port side is connected to the LPC Xpresso module (LPC1343 PIO2 and PIO3). The I<sup>2</sup>C side is connected via RC edge rate control networks that provide bus fall time control (SCL2: R47 and C21; SDA2: R46 and C22). See Figure 29 and Figure 30. Note IC4 is physically underneath the LPC Xpresso module.

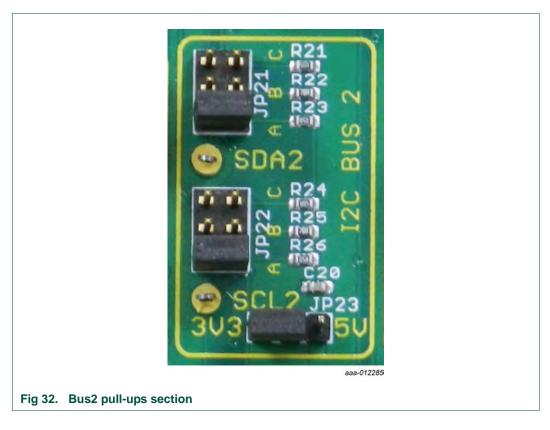

# 5.4.3 Bus2 pull-up resistors

The Bus2 is pulled up to either the 3.3 V or 5 V supplies, via JP23. Three different value pull-up resistors are provided by jumper selection, JP21 and JP22. The values of the pull-up resistors are shown in <u>Table 6</u>. Separate pull-ups are provided for the SCL and SDA signal lines. See <u>Figure 31</u> and <u>Figure 32</u>. Bus1 has a similar arrangement (see <u>Section 5.3.2</u>).

UM10741

| Table 6. | Bus pull-up resistors |        |          |          |          |          |  |

|----------|-----------------------|--------|----------|----------|----------|----------|--|

| Strength | Position              | Value  | Bus1 SCL | Bus1 SDA | Bus2 SCL | Bus2 SDA |  |

| LOW      | А                     | 1.1 kΩ | R16      | R13      | R26      | R23      |  |

| MID      | В                     | 634 Ω  | R15      | R12      | R25      | R22      |  |

| HIGH     | С                     | 324 Ω  | R14      | R11      | R24      | R21      |  |

### 5.5 Daughter card ports

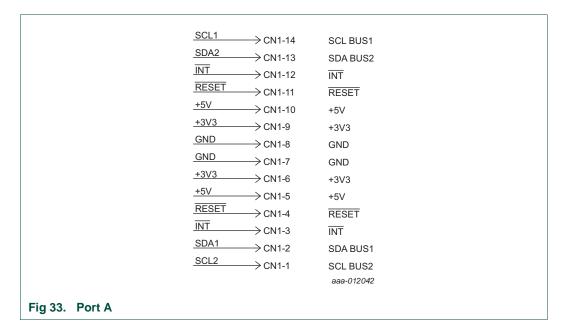

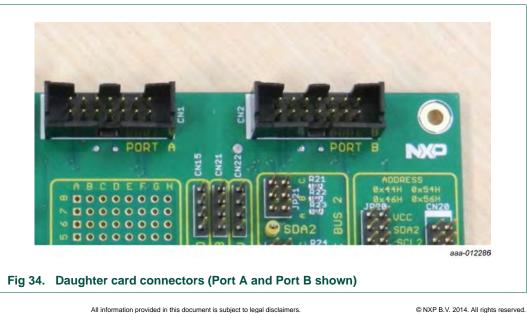

Accessory circuit cards called Daughter Cards may be attached to any ports (Port A - Port D), connectors CN1 - CN4 respectively, see Figure 34. Each port carries the same signals, regardless of physical location. Daughter Cards have jumpers to select whether connection to Bus1 or Bus2 is required. Port A is shown in Figure 33; Port B - Port D are identical, and effectively in parallel.

UM10741

# 5.6 Port E

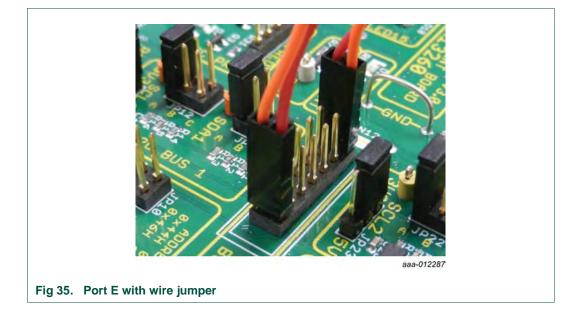

The two independent I<sup>2</sup>C Buses (Bus1 and Bus2) can be joined electrically to create a single I<sup>2</sup>C-bus. The link may be made by wire jumper or by an add-on board with an I<sup>2</sup>C Bus Buffer device installed. The PCA9617A Bus Buffer Demo Board (OM13398) (supplied in the kit) is an example. The Fm+ Development Board (OM13260) may also be operated with nothing connected to Port E (CN12).

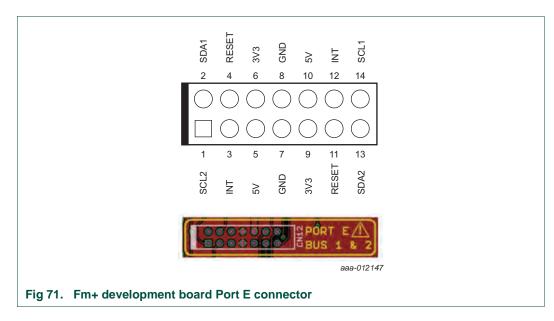

The Port E signal pins are arranged to be symmetrical, permitting the card to be rotated  $180^{\circ}$ , effectively changing the direction of the signals through the card. See <u>Figure 35</u> and <u>Figure 36</u>.

**Remark:** When linked together by wire jumper, the pull-up resistors on each bus are effectively in parallel. The resulting value is therefore one-half of the original value. Pull-up resistors of low value will overload the I<sup>2</sup>C drivers, and effectively stop the bus from operating.

### 5.6.1 Linking both buses together (with a jumper)

30 of 61

### 5.6.2 Linking both buses together (with a bus buffer board)

Fig 36. Port E with bus buffer card (OM13398) installed

# 5.7 Tester connectors (for third-party tools)

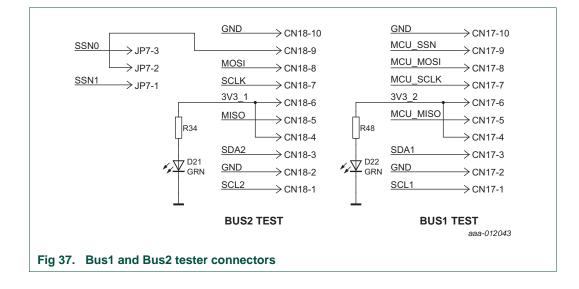

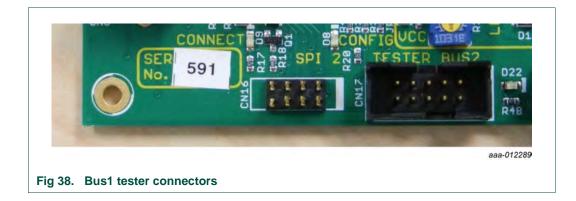

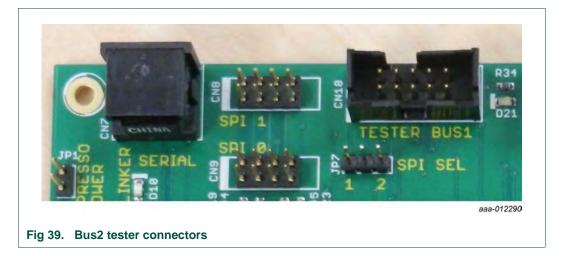

Bus1 may be connected to third-party test equipment via CN17. Bus2 has a similar and independent connection at CN18. See Figure 37, Figure 38 and Figure 39.

**Remark:** Refer to <u>Section 9 "Third-party tools"</u> of this user manual.

### 5.8 Serial communication port

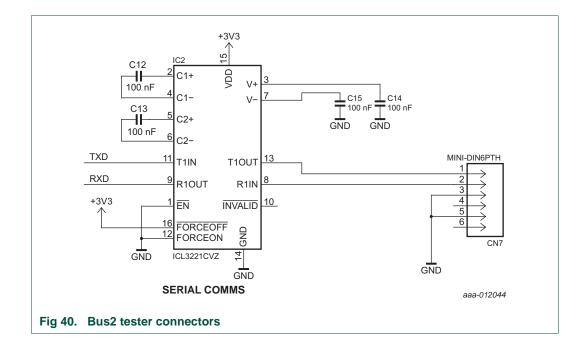

The LCP Xpresso module has a serial comms (communications) port, EIA232 standards compliant using IC2, a voltage level translator. See <u>Figure 40</u>. This is provided for connection to I<sup>2</sup>C Bridge devices that require Serial Communications.

To save space on the PCB, a small mini-DIN connector (CN7) replaces the standard 9-pin DE shell connector. For connection to standard serial comms cables an adapter is required, see <u>Figure 41</u>. The recommended Mini-DIN to DE-9 Adapter is Digikey PN: AE1393-ND (not supplied) See <u>Figure 42</u>.

# 5.9 SPI ports

Both the Bus1 Master MCU and the Bus2 Master LPC Xpresso Module support SPI communications. The Bus1 MCU has one SPI port (SPI2) (CN16) and the LPC Xpresso has two SPI ports (SPI0 and SPI1) (CN9 and CN8, respectively). See Figure 43, Figure 44 and Figure 45. Also refer to Section 9 of this user manual for details on using the tester connector (for third-party tools) with the SPI ports.

UM10741

# 5.10 Logic probe

Most of the I<sup>2</sup>C-bus slaves produce logic signals on their input/output ports. It is necessary to know a logic state. To facilitate this test there are two LEDs with buffers that may be used as a simple 'logic probe'.

To prevent circuit loading the LEDs are buffered by FETs as shown in Figure 46. Green LED (D6) is driven by FET (Q2) when CN11-1 is at or near ground. When CN11-1 is open (or logic 1) the FET is non-conducting, and the LED is off. Red LED (D7) is driven by FET (Q3) when CN11-4 is at or near ground. When CN11-4 is open (or logic 1) the FET is non-conducting, and the LED is off. See Figure 47.

Note that the threshold voltage ( $V_{th}$ ) of the FET is 2.5 V to 4.5 V to ensure it operates correctly on both 3.3 V and 5 V logic levels. The FET source is tied to 5 V, and the gate must therefore be at 2.5 V or lower relative to ground, to turn on the FET and light the LED.

**User manual**

Fig 47. Logic probe section (shown monitoring two GPIO channels from Bus1)

# 5.11 INT and RST indicators

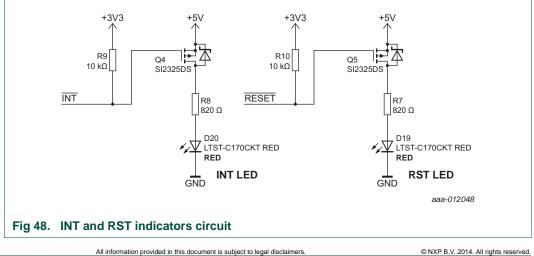

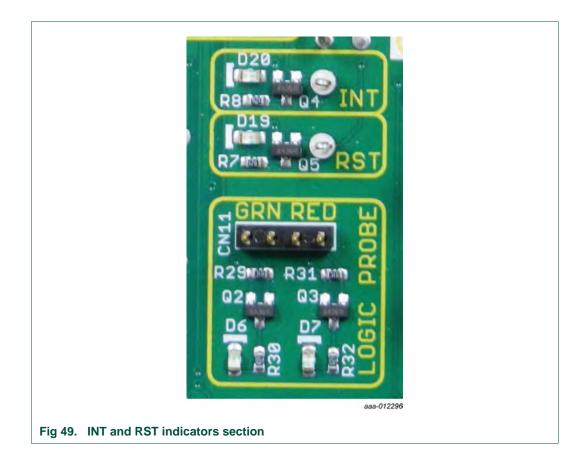

Two global digital signal nets, called INT (interrupt) and RST (reset), connect all I<sup>2</sup>C-bus devices on the board and also the Port A - Port E daughter card connectors. These are also connected to the Master (MCU, IC5) on Bus1, the Master (Bus Controller, IC4), and the LPC Xpresso module. See Figure 48 and Figure 49.

Additional buffered LEDs are provided (D19, RST and D20, Interrupt) on the Fm+ Development Board (OM13260) for visual indication. These buffered LEDs operate in the same fashion as the logic probe (see Section 5.10 "Logic probe").

UM10741

### Fm+ development kit OM13320

### 5.12 Prototype area

Additional circuits may be required to for an application beyond the intended scope of the Fm+ Development Board (OM13260). For example, using different value pull-up resistors than those supplied, or other circuit experiments.

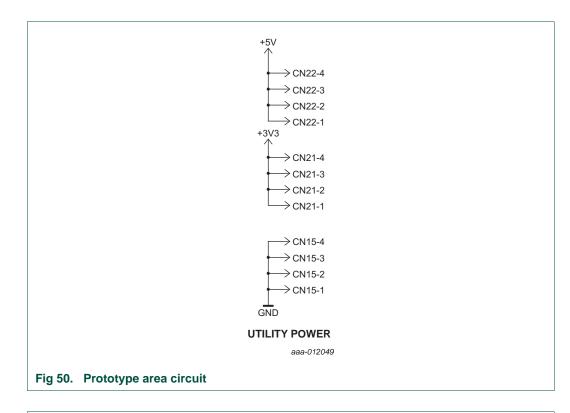

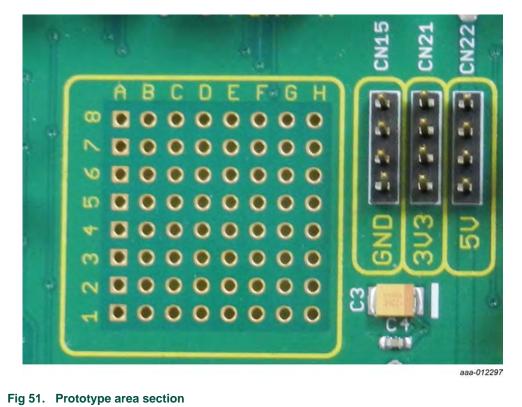

The prototype area is available, and consists of pads and holes on a 100 mil (2.54 mm) grid. Power for these components is made available at several connector points (CN15 is ground, CN21 is +3.3 V, and CN22 is +5 V). See Figure 50 and Figure 51.

### 5.13 LED blinker (PCA9901)

On the Fm+ Development Board (OM13260) V3.0 there is an LED Blinker device (PCA9901, IC3) and LED indicator (D10). While not strictly an I<sup>2</sup>C-bus device, as it uses a one-wire protocol, it belongs to the NXP I<sup>2</sup>C-bus product portfolio.

**Remark:** The PCA9901 will be made obsolete, and will not be present on future versions of the Fm+ Development Board (OM13260).

Refer to the PCA9901 data sheet for details of this device. Note that it is not connected to either I<sup>2</sup>C Bus on the Fm+ Development Board (OM13260). It is connected to the LPC Xpresso module (PIO\_0.7), and that module must be present (and programmed) to drive the PCA9901 device. See Figure 52 and Figure 53.

All information provided in this document is subject to legal disclaimers

# 6. GPIO target board (OM13303)

The GPIO Target Board (OM13303) is used to monitor the Input/Output (I/O) signals from a GPIO. The board has eight channels, each with a push switch and an LED indicator. See Figure 54.

| IN1000   |             |         | ame de la |             |                                                             | 3 M H 23  | 3 - F 8 | a she den        |

|----------|-------------|---------|-----------|-------------|-------------------------------------------------------------|-----------|---------|------------------|

| 108 5454 |             | 5000 SS | SEA COL   |             | 828<br>171<br>171<br>171<br>171<br>171<br>171<br>171<br>171 | and and a |         | 14.41.000        |

| 102 0404 | 132 p.p 571 | 561     | 551       | 541 531     | 521                                                         | 511       | 581     |                  |

|          | R1727 T     | SUKR41  | SUS PS1   | SU4 P11 SU3 | 31 SU2 R21                                                  | 501 811   | SUB PAL | L INT HOR I      |

| Allen    | C89 C91     | 2 040   | uno A     |             |                                                             |           |         | Cal and house to |

### 6.1 Theory of operation

Each of the eight channels operates independently and in the same way. The voltage applied to the input pin is compared in a Windows comparator, which in turn drives a dual color LED. The thresholds for the comparators are set to one-third (logic zero) and two-thirds (logic one) of the supply voltage. These values correspond to the l<sup>2</sup>C-bus logic threshold voltages for the l<sup>2</sup>C-bus specification.

When a push button is pressed, a logic zero is applied the channel, which can be read by the GPIO device to which the GPIO Target Board is attached. A  $2 \times 5$  header is used to connect to the Fm+ Development Board (OM13260) or a GPIO daughter card with a flat ribbon cable (supplied in the kit).

Two connectors are installed, one on each end of the board, and on opposite sides of the PCB to aid in connection without the cables blocking the buttons or LEDs.

There are no option jumpers and no adjustments on the GPIO Target Board (OM13303).

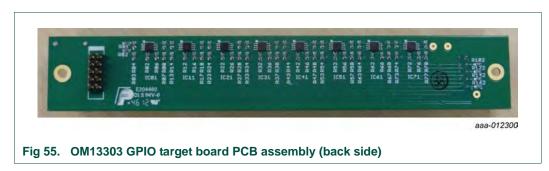

Unlike other PCB assemblies in the Fm+ Development Kit (OM13320), the GPIO Target Board (OM13303) has components on both sides of the PCB. See <u>Figure 55</u>.

### 6.2 Circuit description

The schematic diagram has multiple sheets. For clarification, only fragments of the schematic are shown here. The full schematic should be downloaded if required. The following pages are divided in to several sections covering the window comparator, push switches, bias circuit, and connectors.

### 6.2.1 Window comparator

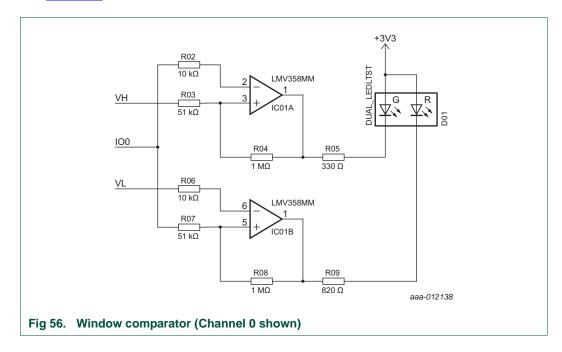

Channel 0 is shown; channels 1 through 7 are identical. The input signal is applied to two comparators, (IC01A and IC01B).

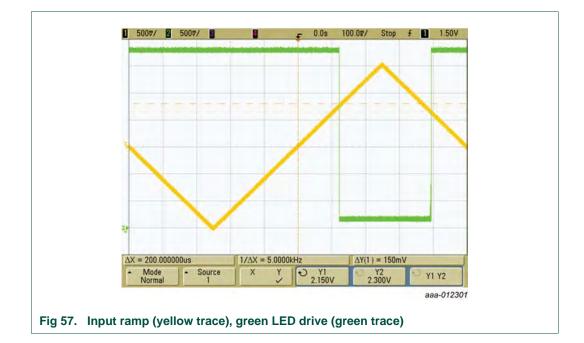

If the input (IO0) is higher than the threshold set by  $V_{IH}$  and resistor divider (R03 and R04), the output of the comparator (IC01A) switches to near ground. This turns on the green LED (D01). Resistor (R04) applies positive feedback hysteresis (about 150 mV) to the comparator, shifting the trip point to a slightly lower voltage, to stop the circuit from oscillation around the switch point.

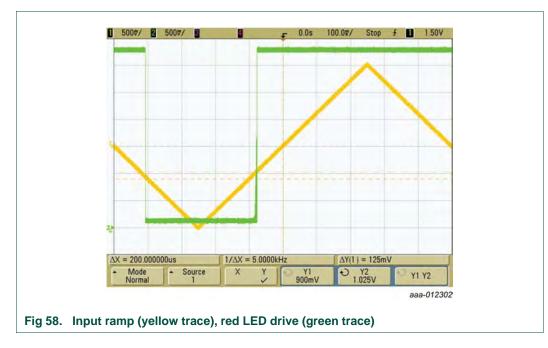

The input (IO0) is attenuated slightly by a resistor divider (R07 and R08), if the resulting voltage is lower than the threshold set by  $V_{IL}$ , the output of the comparator (IC1B) switches to near ground. This turns on the red LED (D01). Resistor (R08) applies positive feedback hysteresis (about 125 mV) to the comparator, shifting the trip point to a slightly higher voltage, to stop the circuit from oscillation around the switch point.

LED current is limited by resistors R05 and R09, which are selected to give approximately equal brightness to the green and red LED elements. See Figure 56.

The operation of the window circuit is shown by applying a ramp waveform, see <u>Figure 57</u> and <u>Figure 58</u>.

# UM10741

### Fm+ development kit OM13320

### 6.2.2 Push switches

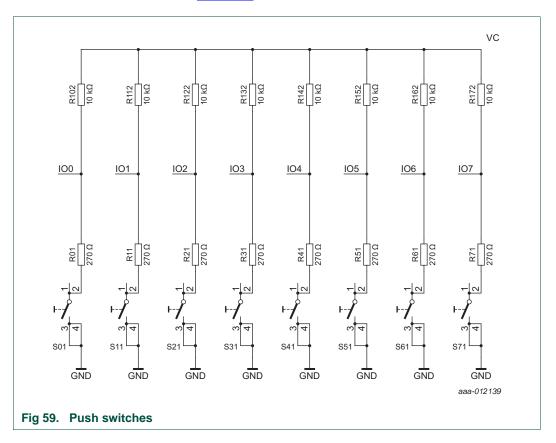

Each channel has a push switch (S01 through S71) that connects the appropriate IO pin to ground when pressed. Series resistors (R01 through R71) limit the current, in the event that the IO pin is being driven HIGH (by the connected GPIO device) when the push switch is closed. Each input is biased to VC (one-half the supply voltage), in the event that the IO pin is left open. This extinguishes both the green and red LEDs of that channel, preventing false readings. See Figure 59.

### 6.2.3 Bias circuit

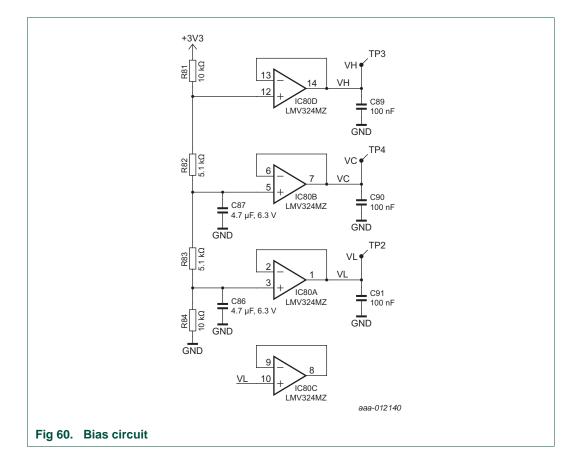

Each channel requires three reference voltages (VL, VC, and VH), from the bias circuit. A resistor divider chain (R01, R02, R03, and R04) divides the supply voltage to produce one-third (VL), one half (VC) and two-thirds (VH). Each value is buffered by an op amp (sections of IC80). Test points are provided as PCB pads for VH (high), VC (center), and VL (low). The fourth section of the quad op amp (IC80) is not used. Noise spikes on each bias supply are removed by capacitors (C89, C90, and C91), power supply variations are removed by capacitors (C86 and C87). See Figure 60.

### Fm+ development kit OM13320

### 6.2.4 Connectors

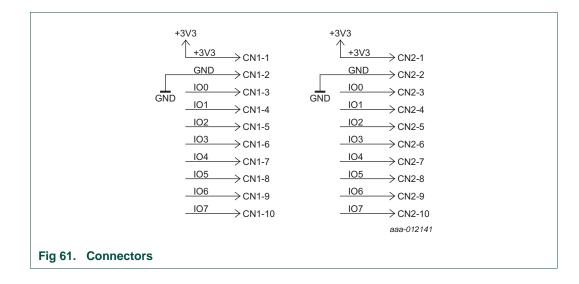

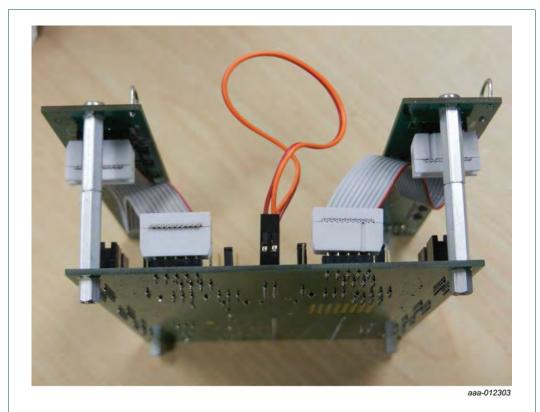

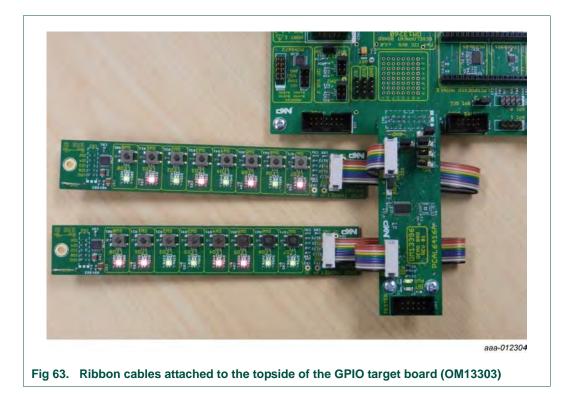

The GPIO Target Board (OM13303) is intended to be connected to the Fm+ Development Board (OM13260) (or other GPIO daughter cards) via a 10-pin ribbon cable. There are two identical connectors, one on each end of the GPIO Target Board to allow connection without blocking the push switches or the LEDs. See Figure 61, Figure 62 and Figure 63.

### Fm+ development kit OM13320

Fig 62. Ribbon cables attached to underside of the GPIO target board (OM13303)

UM10741

# 7. Bus buffer demo board (OM13398)

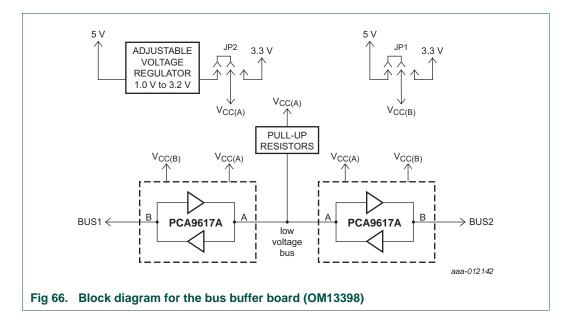

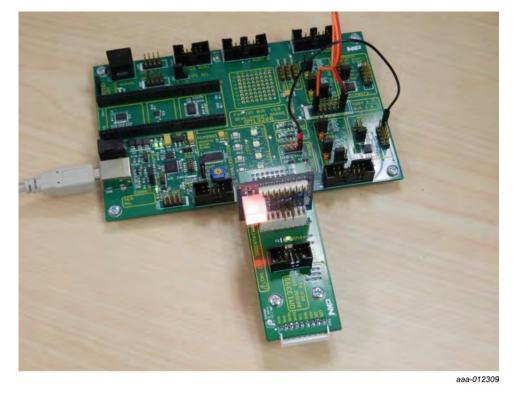

The Bus Buffer Board (OM13398) (supplied in the kit) provides a method to link both the I<sup>2</sup>C buses on the Fm+ Development Board (OM13260) by attachment to Port E, in place of the wire jumper used earlier (see <u>Section 5.6.1 "Linking both buses together (with a jumper)</u>". See Figure 64 and Figure 65.

Fig 64. Bus buffer board (OM13398)

© NXP B.V. 2014. All rights reserved.

### 7.1 Theory of operation

Two identical bus buffer devices are connected in series between the Bus1 and Bus2 segments on the Fm+ Development Board (OM13260). Each Bus Buffer has two identical channels, one for I<sup>2</sup>C clock (SCL) and the second for I<sup>2</sup>C data (SDA). Only one channel will be described in detail.

Each PCA9617A bus buffer device has two power supply connections,  $V_{CC(A)}$  and  $V_{CC(B)}$ , to allow voltage level shifting between one I<sup>2</sup>C-bus segment and another I<sup>2</sup>C-bus segment. Jumpers on the Bus Buffer Board (OM13398) select the voltage source of each of the two device power supplies. To demonstrate the voltage level translator ability the link between the two bus buffers is supplied from a variable voltage regulator, which in turn can be set by the user anywhere between 1.0 V and 3.2 V.

The pull-up resistor on the Low Voltage Bus section is selected by jumpers.

### 7.2 Circuit description

The schematic diagram has multiple sheets. For clarification, only fragments of the schematic are shown here. The full schematic should be downloaded if required. The following pages are divided in to several sections covering the Bus1 Bus Buffer, Bus2 Bus Buffer, Supply select jumpers, Adjustable Voltage Regulator, and Connectors. A block diagram will assist understanding. See Figure 66.

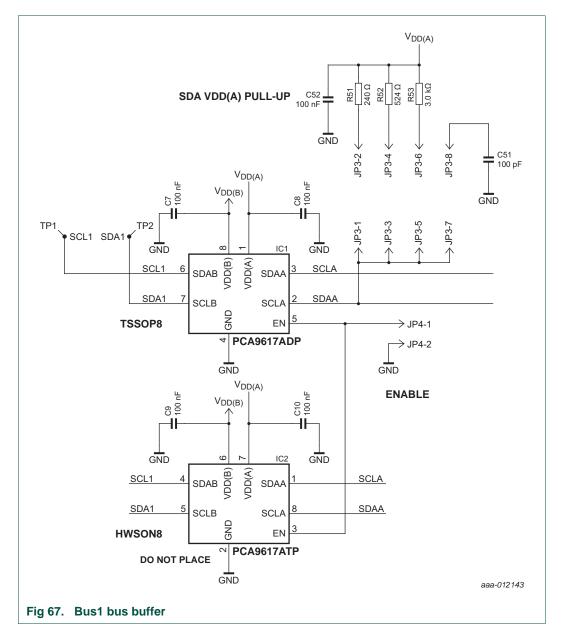

### 7.2.1 Bus1 bus buffer (PCA9617A)

I<sup>2</sup>C-bus signals from the Fm+ Development Board (OM13260), called SCL1 and SDA1, are applied to the high voltage or 'B' Side of IC1 (PCA9617A). The required pull-up resistors on this section of Bus1 are on the Fm+ Development Board (OM13260).

Signals on the low voltage or 'A' Side of IC1 are connected to a selection of pull-up resistors selected by either JP5 (for SCL) or JP3 (for SDA), and the low voltage or 'A' Side of the second PCA9617A, IC3.

Loading capacitors, C31 for SCL and C51 SDA, can be placed on the low voltage section of the bus. To accommodate two different footprints IC1 (TSSOP8) and IC2 (HWSON8) are connected in parallel, but only one part is installed. Installing JP4 disables the Bus Buffer. See Figure 67.

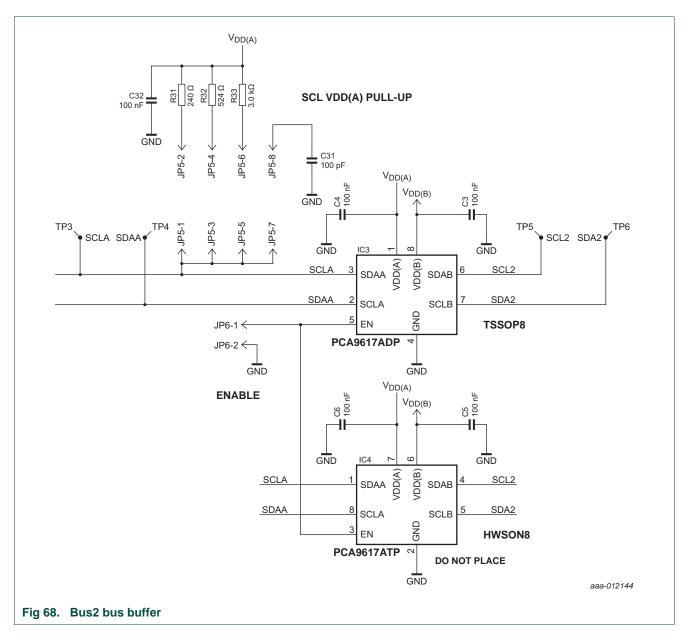

### 7.2.2 Bus2 bus buffer (PCA9617A)

I<sup>2</sup>C-bus signals on the low voltage bus are also connected to the A side of the second PCA9617A Bus Buffer device, IC3. To accommodate two different footprints, IC3 (TSSOP8) and IC4 (HWSON8) are connected in parallel, but only one device is installed. Installing JP6 disables the bus buffer. See Figure 68.

I<sup>2</sup>C-bus signals from the high voltage or 'B' side of IC3 (PCA9617A) are passed back to the Fm+ Development Board (OM13260). The required pull-up resistors on this section of Bus1 are on the Fm+ Development Board (OM13260).

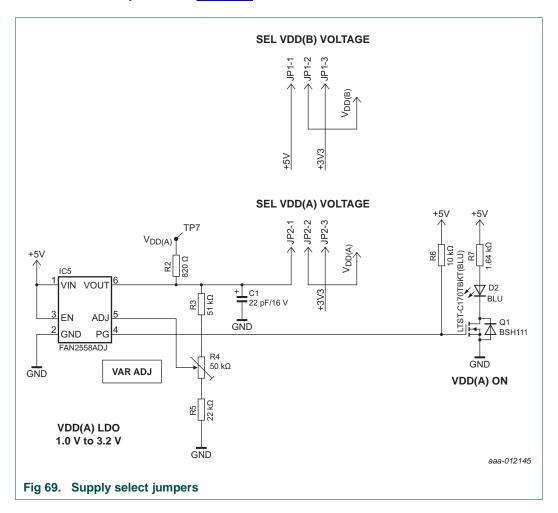

### 7.2.3 Supply select jumpers

The 'B Side' (high voltage side of the voltage level translator) of each PCA9617A can be either 3.3 V or 5 V as selected by JP1. The 'A Side' (low voltage side of the voltage level translator) of each PCA9617A can be either 3.3 V or a variable voltage between 1.0 V and 3.2 V as selected by JP2. See Figure 69.

### 7.2.4 Variable voltage regulator

The low voltage bus bias is generated by an LDO (Low Drop Out) voltage regulator, IC5. The output voltage is set by resistor divider R3, R4, and R5, and provides a range of 1.0 V to 3.2 V. The LDO provides a 'Power Good' signal, which is pulled HIGH by R6, and buffered by Q1. When the LDO is working correctly, the blue LED (D2) is turned ON. See Figure 69.

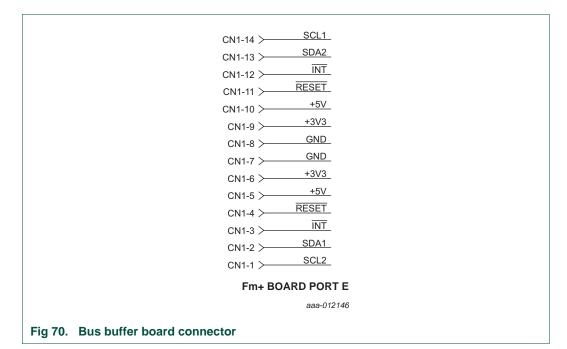

### 7.2.5 Connector

The connector on the Bus Buffer Board (OM13398) matches the Port E connector on the Fm+ Development Board (OM13260). See Figure 70 and Figure 71.

The signals are arranged to be symmetrical so that the Bus Buffer Board (OM13398) can be rotated 180°, causing the signals from the Fm+ Development Board (OM13260) to flow in the opposite direction. For example, from Bus1 to Bus2, or from Bus2 to Bus1 when the Bus Buffer Board (OM13398) is rotated in the Port E connector. See Figure 71. The ability to reverse the signal flow is necessary when examining different I<sup>2</sup>C buffers, or comparing one NXP device to a non-NXP device.

#### 8. Bridge board (OM13399)

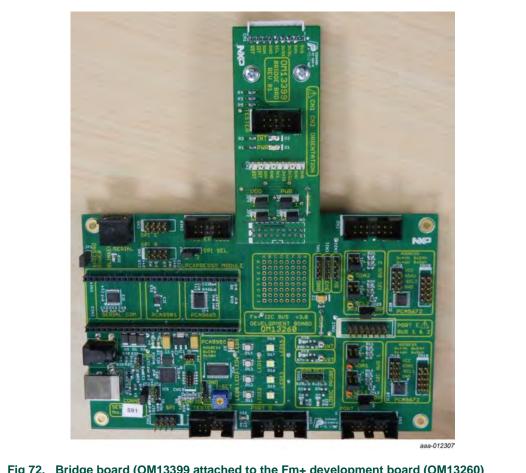

The Bridge Board (OM13399) (supplied in the kit) provides attachment of old style with a 9-pin, in-line, non-polarized connector NXP designed I<sup>2</sup>C demo boards to the Fm+ Development Board (OM13260). The Bridge Board (OM13399) can attach to any daughter card Port (A – D) inclusive. See Figure 72 and Figure 73.

### 8.1 Theory of operation

The Bridge Board is mostly a mechanical platform for the old style with a 9-pin, in-line, non-polarized connector of NXP designed I<sup>2</sup>C demo boards that use a non-polarized nine position connector. Previous NXP I<sup>2</sup>C demo boards were released with both vertical and horizontal mounting, and both male pins and female sockets. The Bridge Board (OM13399) therefore has both styles. There is also a 'Tester' connector that allows direct connection of the third-party tools (see Section 9). The old style with a 9-pin, in-line, non-polarized nine-circuit connector had only one I<sup>2</sup>C-bus, with SCL and SDA signals. The Fm+ Development Board Daughter Card ports have two I<sup>2</sup>C Buses (Bus1 and Bus2) signals. One or other I<sup>2</sup>C Bus can be selected by jumpers. The power source may also be selected by jumper.

### 8.2 Circuit description

The schematic diagram has a single sheet. For clarification, only fragments of the schematic are shown here. The full schematic should be downloaded if required. The circuit is simple.

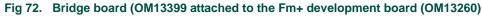

### 8.2.1 Fm+ development board (OM13260) connector (CN3)

The connector on the Bridge Board (OM13399) matches the Port connectors on the Fm+ Development Board (OM13260) See Figure 74. A Bridge Board (OM13399) can be attached to any Port A – Port D inclusive. It cannot be connected to Port E due to mechanical arrangement of the Port E connector.

The Fm+ Development Board has two separate I<sup>2</sup>C buses (Bus1 and Bus2) and one of these is selected by two jumpers, JP2 for SCL and JP3 for SDA.

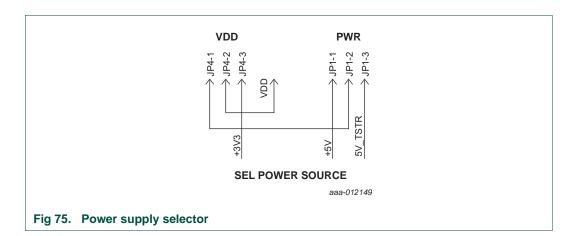

### 8.2.2 Power supply select (JP1 and JP4)

There are two power sources available to the Bridge Board (OM13399) depending upon whether it is connected to the Fm+ Development Board (OM13260) or powered by a third-party tool (see <u>Section 9</u>).

The Tester socket provides 5 V and the Fm+ Development Board (OM13260) provides both 3.3 V or 5 V. Jumper JP1 selects the source of the 5 V power. JP4 selects either 3.3 V or 5 V as needed.

**Remark:** When the Bridge Board (OM13399) is not attached to the Fm+ Development Board and powered by the Tester, the only option is 5 V.

### 8.2.3 9-position connectors (CN1 and CN2)

| $CN2-1 \leftarrow +5V$ $CN2-2 \leftarrow +5VSW$ $CN2-3 \leftarrow +3V3$ $CN2-3 \leftarrow +3V3SW$ $CN2-5 \leftarrow SCL$ $CN2-5 \leftarrow GND$ $CN2-6 \leftarrow GND$ $CN2-7 \leftarrow SDA$ | $CN1-1 \rightarrow +5V$ $CN1-2 \rightarrow +5VSW$ $CN1-3 \rightarrow +3V3$ $CN1-3 \rightarrow +3V3SW$ $CN1-4 \rightarrow +3V3SW$ $CN1-5 \rightarrow SCL$ $CN1-6 \rightarrow GND$ $CN1-7 \rightarrow SDA$ |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $CN2-8 \leftarrow INT \\ CN2-9 \leftarrow RESET \\ PPOS MALE HEADER$                                                                                                                          | CN1-8 > INT<br>CN1-9 > RESET<br>9POS FEMALE SOCKET                                                                                                                                                       |

| Fig 76. 9-position connectors (CN1 and CN2)                                                                                                                                                   | aaa-012150                                                                                                                                                                                               |

Two 9-position connectors are provided; both carry exactly the same signals. CN1 is female, CN2 is male.

**Remark:** These connectors are not polarized or keyed. Take care to make connection correctly.

UM10741

| CN4-10 ← GND                        |

|-------------------------------------|

| CN4-9 ←                             |

| CN4-8 ←                             |

| CN4-7 CN4-7                         |

| $CN4-6 \leftarrow \frac{5V_TSTR}{}$ |

| CN4-5 ←                             |

| CN4-4 <                             |

| CN4-3 ← SDA                         |

| CN4-2 <del>GND</del>                |

| CN4-1 ← SCL                         |

| I2C TESTER                          |

| aaa-012151                          |

| Fig 77. Tester connection (CN4)     |

8.2.4 Tester connector (CN4)

The 10-position  $(2 \times 5)$  shrouded header connector (CN4) mates with third-party tools (see Section 9). Only I<sup>2</sup>C-bus signals and available 5 V power are connected.

**Remark:** The Tester's bus signals are connected to the two 9-position connectors and, depending upon the position of JP2 and JP3, to the Fm+ Development Board Bus1 or Bus2. Take care to avoid double termination of the I<sup>2</sup>C buses.

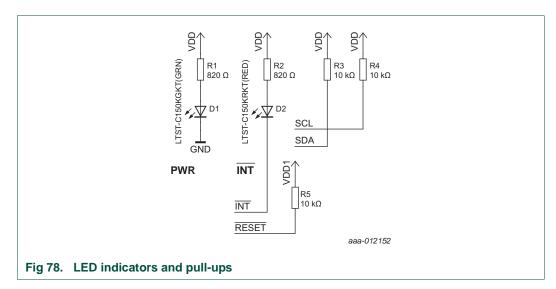

8.2.5 LED indicators and pull-ups

Two LEDs provide indication of power (D1, Green) and INT (interrupt) status (D2, Red). To prevent malfunction of the l<sup>2</sup>C-bus if the Bridge Board (OM13399) is used in manner that does not have pull-up on either SCL or SDA, there are weak pull-ups (R3, R4). These may be replaced with lower value resistors (or removed), as needed.

Fm+ development kit OM13320

### 8.3 Example using PCA9632 (OM13269)

Fig 79. Bridge board (OM13399) used to attach a PCA9632 (OM13269)

The Bridge Board (OM13399) (supplied in the kit) provides attachment of old style with a 9-pin, in-line, non-polarized connector NXP designed  $I^2C$  demo boards to the Fm+ Development Board (OM13260).

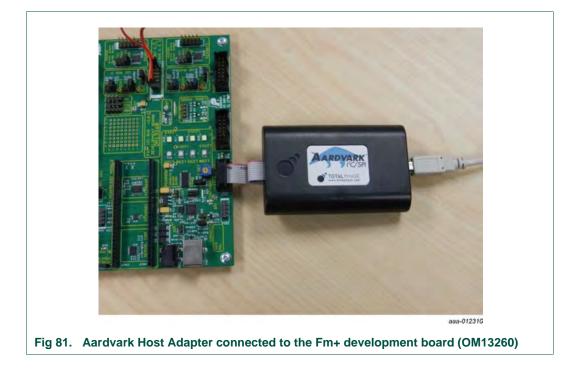

# 9. Third-party tools

Generation, inspection and logging of I<sup>2</sup>C-bus data is easily achieved with third-party development tools from a number of suppliers: SB Solutions, Inc. (<u>www.i2ctools.com</u>) and Total Phase (<u>www.totalphase.com</u>).

SB Solutions supplies a range of tools driven from USB and outputs to I<sup>2</sup>C and SPI. The user interface is very similar to the Fm+ Development Board GUI, and a DLL is provided for custom development. These tools are not supplied in the kit, and must be purchased directly from the vendor.

Total Phase supplies two tools called Aardvark (host adapter) and Beagle (bus logger) that connect directly to the Fm+ Development Board (OM13260). These tools are not supplied in the kit, and must be purchased directly from the vendor.

Fig 80. SB Solutions USB-to-I2C Pro connected to an Fm+ Development Board daughter card

# UM10741 Fm+ development kit OM13320

# **10. Abbreviations**

| Table 7.             | Abbreviations                |

|----------------------|------------------------------|

| Acronym              | Description                  |

| DLL                  | Dynamic Link Library         |

| EVM                  | Evaluation Module            |

| FET                  | Field-Effect Transistor      |

| Fm+                  | Fast-mode Plus               |

| GPIO                 | General Purpose Input/Output |

| GUI                  | Graphical User Interface     |

| HID                  | Human Interface Driver       |

| I <sup>2</sup> C-bus | Inter-Integrated Circuit-bus |

| I/O                  | Input/Output                 |

| ISP                  | In-System Programmable       |

| JTAG                 | Joint Test Action Group      |

| LDO                  | Low Drop-Out                 |

| LED                  | Light-Emitting Diode         |

| MCU                  | MicroController Unit         |

| OS                   | Operating System             |

| PC                   | Personal Computer            |

| PCB                  | Printed-Circuit Board        |

| RC                   | Resistor-Capacitor network   |

| RGB                  | Red/Green/Blue               |

| SPI                  | Serial Peripheral Interface  |

| SWD                  | Single Wire Debug            |

| USB                  | Universal Serial Port        |

# **11. References**

UM10785, "Fm+ Demo Board Software Installation Guide" — NXP Semiconductors; 25 February 2014; www.nxp.com/documents/user\_manual/UM10785.pdf

# 12. Legal information

### 12.1 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

## 12.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

### 12.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I<sup>2</sup>C-bus — logo is a trademark of NXP Semiconductors N.V.

**User manual**

# 13. Contents

| 1               | Introduction 3                                 |

|-----------------|------------------------------------------------|

| 2               | Key features 3                                 |

|                 | I <sup>2</sup> C-bus masters                   |

|                 | l <sup>2</sup> C-bus slaves                    |

|                 | Accessory sockets                              |

|                 | Other features4                                |

| 3               | Fm+ development kit quick tour                 |

| 3.1             | Kit contents                                   |

| 3.1.1           | Box contents                                   |

| 3.2             | Supplied PCB assemblies                        |

| 3.2.1           | Fm+ Development Board (OM13260) 6              |

| 3.2.2           | GPIO target board (OM13303) 7                  |

| 3.2.3           | PCA9617A bus buffer demo board                 |

|                 | (OM13398)                                      |

| 3.2.4           | Bridge board (OM13398) 8                       |

| 3.2.5           | Daughter cards (not supplied in the kit) 8     |

| 4               | First time setup: Fm+ development board kit    |

|                 | (OM13320)                                      |

| 4.1             | Before you begin 9                             |

| 4.2             | First time setup of the Fm+ development board  |

|                 | (OM13260)                                      |

| 4.3             | OM132680 jumpers 9                             |

| 4.4             | OM13260 Port E bypass                          |

| 4.5             | OM13260 mounting hardware                      |

| 4.6<br>4.7      | NXP firmware installation                      |

| 4.7<br>5        |                                                |

| <b>э</b><br>5.1 |                                                |

| 5.1<br>5.2      | ······································         |

| 5.2.1           | Circuit description                            |

| 5.2.1           | USB interface                                  |

| 5.3             | Bus one (Bus1)                                 |

| 5.3.1           | Bus1 master (MCU LPC1343)                      |

| 5.3.2           | Bus1 pull-up resistors                         |

| 5.3.3           | LED driver slave (PCA9955)                     |

| 5.3.4           | GPIO slave (PCA9672)                           |

| 5.4             | Bus two (Bus2)                                 |

| 5.4.1           | Bus2 master                                    |

|                 | (LPC Xpresso — MCU LPC1343) 25                 |

| 5.4.2           | Bus2 bus master (PCA9665) 27                   |

| 5.4.3           | Bus2 pull-up resistors                         |

| 5.5             | Daughter card ports 29                         |

| 5.6             | Port E 30                                      |

| 5.6.1           | Linking both buses together (with a jumper) 30 |

| 5.6.2           | Linking both buses together (with a bus buffer |

|                 | board) 31                                      |

| 5.7            | Tester connectors (for third-party tools)                     | 31       |

|----------------|---------------------------------------------------------------|----------|

| 5.8<br>5.9     | Serial communication port                                     | 32<br>34 |

| 5.9<br>5.10    | SPI ports                                                     | 34<br>35 |

| 5.11           | INT and RST indicators                                        | 36       |

| 5.12           | Prototype area                                                | 37       |

| 5.13           | LED blinker (PCA9901)                                         | 39       |

| 6              | GPIO target board (OM13303)                                   | 40       |

| 6.1            | Theory of operation                                           | 40       |

| 6.2            | Circuit description                                           | 41       |

| 6.2.1          | Window comparator                                             | 41       |

| 6.2.2          | Push switches                                                 | 43       |

| 6.2.3          | Bias circuit                                                  | 43       |

| 6.2.4          | Connectors.                                                   | 44       |

| 7              | Bus buffer demo board (OM13398)                               | 46       |

| 7.1            | Theory of operation                                           | 47       |

| 7.2            | Circuit description                                           | 47       |

| 7.2.1<br>7.2.2 | Bus1 bus buffer (PCA9617A)Bus2 bus buffer (PCA9617A)          | 48<br>49 |

| 7.2.2          | Supply select jumpers                                         | 49<br>50 |

| 7.2.4          | Variable voltage regulator                                    | 50       |

| 7.2.5          | Connector                                                     | 51       |

| 8              | Bridge board (OM13399)                                        | 52       |

| 8.1            | Theory of operation                                           | 53       |

| 8.2            | Circuit description                                           | 53       |

| 8.2.1          | Fm+ development board (OM13260)                               |          |

|                | connector (CN3).                                              | 53       |

| 8.2.2          | Power supply select (JP1 and JP4)                             | 54       |

| 8.2.3<br>8.2.4 | 9-position connectors (CN1 and CN2)<br>Tester connector (CN4) | 54<br>55 |

| 0.2.4<br>8.2.5 | LED indicators and pull-ups                                   | 55<br>55 |

| 8.3            | Example using PCA9632 (OM13269)                               | 56       |

| 9              | Third-party tools                                             | 57       |

| 10             | Abbreviations                                                 | 59       |

| 11             | References                                                    | 59       |

| 12             | Legal information                                             | 60       |

| 12.1           | Definitions                                                   | 60       |

| 12.2           | Disclaimers                                                   | 60       |

| 12.3           | Trademarks                                                    | 60       |

| 13             | Contents                                                      | 61       |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

### © NXP B.V. 2014.

#### All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 1 April 2014 Document identifier: UM10741