## **UG10199**

# NXP MPU Cortex-A Core Zephyr User Guide Rev. 2.0 — 29 July 2025

User guide

#### **Document information**

| Information | Content                                                                                                                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | UG10199, NXP MPUs, Cortex-A core, Zephyr User Guide, i.MX 8M Mini EVK, i.MX 8M Plus EVK, i.MX 8M Nano EVK, i.MX 93 EVK, and i.MX 95 EVK boards, Zephyr driver information, driver testing and examples |

| Abstract    | This document explains the hardware setup, use cases, and commands to run Zephyr on the supported NXP MPU Cortex A hardware platforms.                                                                 |

**NXP MPU Cortex-A Core Zephyr User Guide**

#### 1 Resources

This section describes the GitHub repositories and official documents to support Zephyr development.

## 1.1 Zephyr GitHub repositories

Table 1. GitHub Repo for Zephyr

| Name    | Repo                                          | Branch |

|---------|-----------------------------------------------|--------|

| Zephyr  | https://github.com/zephyrproject-rtos/zephyr  | main   |

| hal_nxp | https://github.com/zephyrproject-rtos/hal_nxp | master |

## 1.2 Zephyr official documents

The official Zephyr documents are available on the URL: <a href="https://docs.zephyrproject.org/latest/">https://docs.zephyrproject.org/latest/</a>

See the <u>Introduction to Zephyr</u> for a high-level overview. To start developing Zephyr applications, refer to the Zephyr <u>Getting Started Guide</u>. Refer to <u>Release-Management</u> for official Zephyr release milestone dates.

**NXP MPU Cortex-A Core Zephyr User Guide**

## 2 Zephyr development

Refer to **Getting Started Guide** to:

- Set up a command-line Zephyr development environment on Ubuntu, Mac OS, or Windows (instructions for other Linux distributions are discussed in Install Linux Host Dependencies).

- Get the source code.

- Build, flash, and run a sample application.

**NXP MPU Cortex-A Core Zephyr User Guide**

## 3 Zephyr kernel

#### 3.1 Hardware Model V2

After Zephyr v3.6 release, the Zephyr kernel transitions to the Hardware Model V2. This new model overhauls the way both SoCs and boards are named and defined and adds support for the important features. The main features of the Hardware Model V2 are listed below:

- Support for multi-core, multi-arch AMP (Asymmetrical Multi Processing) SoCs

- · Support for multi-SoC boards

- Support for reusing the SoC and board Kconfig trees outside the Zephyr build system

- Support for advanced use cases with Sysbuild (System build)

- · Removal of all existing arbitrary and inconsistent uses of Kconfig and folder names

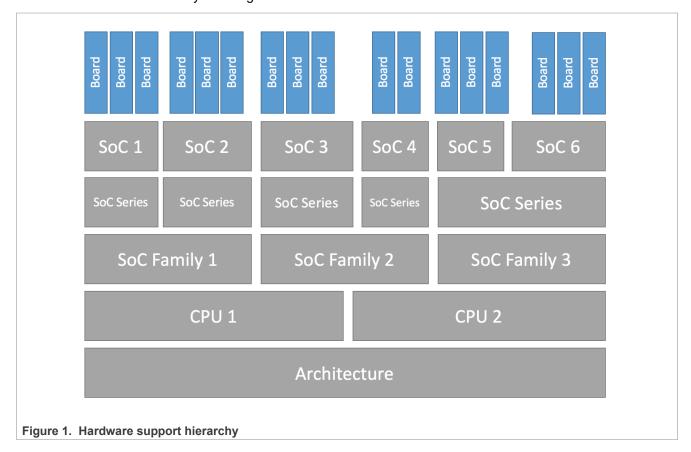

Zephyr supports the following hardware support hierarchy, which has several levels. The levels are listed starting from the most specific to the least specific:

- · A board, which has one or more

- SoC, each of which optionally belong to an

- SoC series, which in turn may optionally belong to an

- · SoC family. Each SoC has one or more

- CPU cluster, each containing one or more

- CPU core, of a particular

- · architecture

You can visualize the hierarchy in the figure below:

**NXP MPU Cortex-A Core Zephyr User Guide**

Refer to **Zephyr documentation** for more details.

#### Important:

- In this document, "**HWMV1**" refers to Hardware Model V1 supported in Zephyr release v3.6 and previous releases.

- "HWMV2" refers to Hardware Model V2 supported after Zephyr release v3.6.

.

**NXP MPU Cortex-A Core Zephyr User Guide**

## 4 NXP MPUs supported in Zephyr

#### 4.1 i.MX 93

#### 4.1.1 Overview

NXP provides the i.MX 93 family of processors that are power-optimized for smart home, building control, contactless HMI, IoT edge, automotive, and industrial applications.

The i.MX 93 processor includes the powerful dual Arm<sup>™</sup> Cortex-A55 processors with speeds up to 1.7 GHz integrated with a NPU that accelerates the machine learning inference. A general-purpose Arm<sup>™</sup> Cortex<sup>™</sup>-M33 core running up to 250 MHz provides for real-time and low-power processing. Robust control networks are possible via a CAN-FD interface. Also, dual 1 Gbit/s Ethernet controllers, one supporting Time Sensitive Networking (TSN), drive gateway applications with low latency.

The i.MX 93 automotive qualified part is useful for applications such as:

- Driver monitoring system (DMS)

- · Cost optimized gateway

- · General purpose compute

Refer to NXP official website for more details: i.MX 93 Applications Processors Family | NXP Semiconductors

#### 4.1.2 Zephyr SoCs and board

From Zephyr 3.7 release, hardware model v1 (HWMV1) is updated to hardware model v2 (HWMV2).

#### Table 2. HWMV2

| Parameter                         | Directory/File Name    |

|-----------------------------------|------------------------|

| SoC source code directory         | soc/nxp/imx/imx9/      |

| Board source code directory       | boards/nxp/imx93_evk/  |

| Supported board name and variants | imx93_evk/mimx9352/a55 |

#### Table 3. HWMV1

| Parameter                         | Directory/File Name      |

|-----------------------------------|--------------------------|

| SoC source code directory         | soc/arm64/nxp_imx/mimx9/ |

| Board source code directory       | boards/arm64/mimx93_evk/ |

| Supported board name and variants | mimx93_evk_a55           |

#### 4.1.3 Peripheral drivers

Table 4. Peripheral drivers on i.MX 93

| Peripheral       | Driver      | Reference                      |

|------------------|-------------|--------------------------------|

| GIC              | GIC v3      | 5.3 Interrupt-Controller - GIC |

| Clock            | ССМ         | 5.7 Clock – CCM Rev2           |

| IOMUX Controller | Pinctrl IMX | 5.4 IOMUX – pinctrl_imx        |

| UART             | LPUART      | 5.2 UART - LPUART              |

#### **NXP MPU Cortex-A Core Zephyr User Guide**

Table 4. Peripheral drivers on i.MX 93...continued

| Peripheral      | Driver | Reference            |

|-----------------|--------|----------------------|

| GPIO            | rgpio  | 5.11 GPIO - RGPIO    |

| I2C             | LPI2C  | 5.14 I2C - LPI2C     |

| TPM Counter     | TPM    | 5.10 Counter - TPM   |

| Ethernet - ENET | ENET   | 5.15 Ethernet - ENET |

#### 4.1.4 Building Zephyr

Take samples/hello world application as example:

#### HWMV2:

```

west build -p always -b imx93_evk/mimx9352/a55 samples/hello_world/

```

#### HWMV1:

```

west build -p always -b mimx93_evk_a55 samples/hello_world/

```

Then Zephyr binary image "zephyr.bin" and elf image "zephyr.elf" can be located in the zephyr/build/zephyr/ directory.

#### 4.1.5 Running Zephyr on the i.MX 93 board

Zephyr on Cortex-A Core can be booted up or stopped on a specified Cortex-A Core by using the U-Boot commands or remoteproc under Linux.

#### 4.1.5.1 Board setup and software preparation (i.MX 93 EVK)

To run Zephyr, prepare the i.MX 93 EVK board using the steps below:

#### 1. UART Console Setup

Connect USB debug connector J1401 to the PC. The PC enumerates four COM ports when the USB cable is plugged into J1401. For example, on a Linux host, the four COM ports could be  $/\text{dev}/\text{ttyUSB0} \sim /\text{dev}/\text{ttyUSB3}$ . If multiple USB serial cables are plugged into the same PC, the ID of tty USB device might be different. Therefore, users must check the kernel log after i.MX 93 EVK debug cable is plugged into the PC. For example, the following log shows that the COM ports should be  $/\text{dev}/\text{ttyUSB0} \sim /\text{dev}/\text{ttyUSB3}$ .

```

linux:~$ sudo dmesg | tail

[272709.527874] usb 3-2.1.2: FTDI USB Serial Device converter now attached to

ttyUSB0

[272709.528196] ftdi_sio 3-2.1.2:1.1: FTDI USB Serial Device converter

detected

[272709.528266] usb 3-2.1.2: Detected FT4232H

[272709.528582] usb 3-2.1.2: FTDI USB Serial Device converter now attached to

ttyUSB1

[272709.528888] ftdi_sio 3-2.1.2:1.2: FTDI USB Serial Device converter

detected

[272709.528957] usb 3-2.1.2: Detected FT4232H

[272709.528957] usb 3-2.1.2: FTDI USB Serial Device converter now attached to

ttyUSB2

```

**NXP MPU Cortex-A Core Zephyr User Guide**

```

[272709.529451] ftdi_sio 3-2.1.2:1.3: FTDI USB Serial Device converter detected [272709.529514] usb 3-2.1.2: Detected FT4232H [272709.529780] usb 3-2.1.2: FTDI USB Serial Device converter now attached to ttyUSB3

```

The third port (it is /dev/ttyUSB2 in the above example) is used for U-Boot and Linux, and the fourth port (it is /dev/ttyUSB3 in the above example) is used for Zephyr debug console by default. Developers can use minicom, Putty, Tera Term, Xshell, or other terminal tools to open these two UART consoles. The settings used are the **115200** Baud rate, **8 bit** data bits, **1** stop bits, and **none** parity.

2. Deploying the pre-built SD card image

Zephyr on Cortex-A Core can be booted up or stopped on specified Cortex-A Core by using the U-Boot commands or remoteproc under Linux. U-Boot commands and remoteproc to start or stop Cortex-A Core Zephyr are supported in Real-time Edge software release v3.0 and late releases (<a href="https://www.nxp.com/rtedge">https://www.nxp.com/rtedge</a>). Therefore, a quick method to setup the software environment on i.MX 93 EVK is to deploy the prebuild image (.wic image) to an SD card and boot from it directly.

- 3. Follow the following steps to prepare an SD/MMC card to boot up an i.MX board using a Linux host machine.

- 4. Download latest Real-time Edge release pre-build image for the EVK board from <a href="https://www.nxp.com/rtedge">https://www.nxp.com/rtedge</a>

| Release and Documentation                                                                                                                                                                                                                                                                               | <b>Build Sources</b>                           | Supported Platforms/Pre-<br>Built Binary                                                                                                                                                                                                                              | What's New                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Real Time Edge Software v3.0  Release Date: Dec 2024  Documentation  Real-time Edge Software User Guide  Real-Time Edge Yocto Project User's Guide  Real-time Edge Software Release Notes  GenAVB/TSN Stack Evaluation User Guide  Harpoon User's Guide  iMXSULL EVK GenAVB/TSN Rework Application Note | See README (20n instructions for each release. | IMX6ULI4X14EVK IMX8MM-LPDDR4-EVK IMX8DXLBO-LPDDR4-EVK IMX91-IXII-LPDDR4-EVK IMX91-9X9-LPDDR4-QSB IMX93-9X9-LPDDR4-QSB IMX93-14X14-LPDDR4X-EVK IMX95-15X15-LPDDR4X-EVK IMX95-15X15-LPDDR4X-EVK IMX95-19X19-LPDDR5-EVK LS1028ARDB LS1043ARDB LS1046ARDB LX2160ARDB-REV2 | Real-time System Preempt-RT Linux 6.6.36-rt35(tag If-6.6.36-rt-2.1.0) Baremetal (U-Boot 2024.04) RTOS on Cortex-A core Uprev: Zephyr v3.7, FreeRTOS kernel V11.0.1 RTOS with Jailhouse Harpoon 3.2 Heterogeneous Multicore Framework Unified lifecycle management Linux remoteproc start/stop U-Boot cpu disable/status Enhanced ram console with dumping tools Heterogeneous Multi-Soc Framework Linux DSA: device driver of DSA control interface TSN configuration: CB/Qci/Qbv  NETC DSA switch configuration on I.MX RT1180 |

5. Then a zip file "Real-time\_Edge\_vx.x\_IMX93EVK.zip" (x.x is replaced with release version) is downloaded, extract the .wic file named "nxp-image-real-time-edge-imx93evk.rootfs.wic" from the path "Real-time\_Edge\_vx.x\_IMX93EVK/real-time-edge/nxp-image-real-time-edge-imx93evk.rootfs.wic.zst" in the zip file.

The SD card image (with the extension .wic) contains U-Boot, the Linux image and device trees, and the rootfs for a 4 GB SD card. The image can be installed on the SD card with one command if flexibility is not required. Carry out the following command to copy the SD card image to the SD/MMC card. Change sdx below to match the one used by the SD card.

```

$ sudo dd if=<image name>.wic of=/dev/sdx bs=1M && sync

```

The entire contents of the SD card are replaced. If the SD card is larger than 4 GB, the additional space is not accessible.

6. Then, insert the SD card back to the EVK board. Configure the EVK board to boot from SD card by switching SW1301[3:0] to be "0010".

**NXP MPU Cortex-A Core Zephyr User Guide**

Power up the board and locate the TF-A and U-Boot log from the third port (it is /dev/ttyUSB2 in the above example).

#### 4.1.5.2 Booting Zephyr by using U-Boot commands1

Multiple U-Boot commands can be used to start or stop Zephyr on the Cortex-A core.

#### 4.1.5.2.1 "cpu" command

Following is the help information of the U-Boot cpu command:

```

u-boot=> cpu

cpu - Multiprocessor CPU boot manipulation and release

```

#### Usage:

- cpu <num> reset Resets cpu <num>

- cpu status Displays the status of all cpus

- cpu <num> status Displays the status of cpu <num>

- cpu <num> disable Disables the status of cpu <num>

- cpu <num> release <addr> [args] Releases cpu <num> at <addr> with [args]

Except the "cpu <num> reset" command, all other cpu commands have been implemented on i.MX 8M Mini platform.

In general, U-Boot runs on the master Core (Core0) of Cortex-A cores. Therefore, to start RTOS on any other slave Cortex-A core (the Cores except Core0) from the specified memory address, use the command below:

```

"cpu <num> release <addr> [args]"

```

For this purpose, load the RTOS binary images into the corresponding memory space, and use the "cpu <num> disable" command to power off any slave core that runs RTOS. Use the commands "cpu status" or "cpu <num>" status to check the status (running or power off) for all or the specified Cortex-A cores.

#### 4.1.5.2.2 "go" command

The following is the help information of the U-Boot go command:

```

U-Boot=> go

```

go - starts the application at address 'addr'

#### Usage:

```

go addr [arg ...]

```

- starts the application at address 'addr'

Passing 'arg' as arguments

The "go" command can be used to start the application or RTOS running on the master Core (Core0). The impact is not returned back to the U-Boot command line.

In summary, you can use U-Boot command "go" to boot the RTOS from Core0 or use U-Boot command "cpu" to boot or power off the RTOS running on the other Cortex-A cores except Core0.

**NXP MPU Cortex-A Core Zephyr User Guide**

#### 4.1.5.2.3 Running the Zephyr Application on i.MX 93 EVK

The below example shows how to run the hello world examples on the i.MX 93 EVK board.

- 1. Power up the i.MX 93 EVK board and stop at the U-Boot command line.

- 2. Deploy Zephyr binary image "zephyr.bin" to the board.

There are multiple methods can be used to deploy the zephyr.bin to the board, select one the below methods:

- 3. Download the image into memory from tftp server:

```

u-boot=> tftp 0xd0000000 zephyr.bin

```

4. Or copy the image to SD Card by using Linux host PC:

There are two partitions in the SD Card if .wic is deployed on the SD Card:

- The first one is the FAT partition, which is used to store Linux image and dtb files.

- The second one is the Linux partition to be uses for the Linux Root file system.

Copy the Zephyr binary image "zephyr.bin" to the first FAT partition of the SD card by using Linux host PC. Then, plug the card into the board, power up the board, and stop at U-Boot command line. Then, load the image from the SD card into memory by using the following U-Boot command:

```

u-boot=> fatload mmc 1:1 0xd0000000 zephyr.bin;

```

Or download the image into memory by using serial port

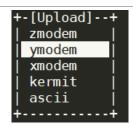

5. For example, load the binary file over serial line in ymodem mode, execute the following command under U-Boot:

```

u-boot=> loady 0xD0000000

```

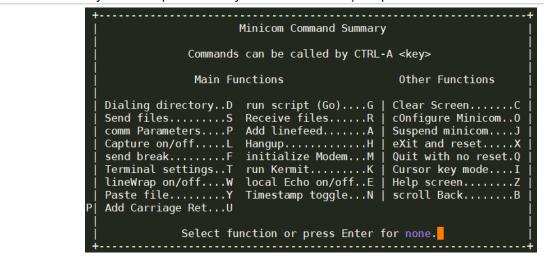

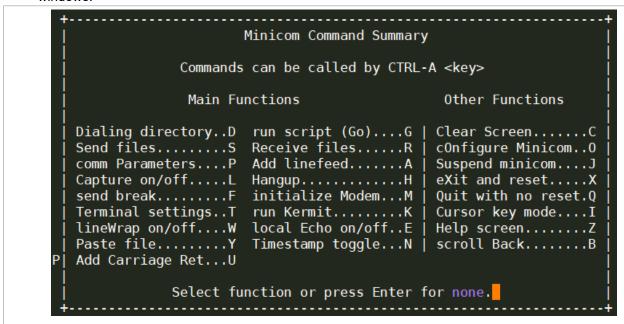

Then, send the binary file from console software in host PC. The steps are different for different console software. Here, take minicom as an example: Use the quick key "**ctrl + A + Z**" (pressed down and hold "ctrl" key and then press the key "**A**" and "**Z**" in turn) to open the command window.

```

Minicom Command Summary

Commands can be called by CTRL-A <key>

Main Functions

Other Functions

Clear Screen.....C

Dialing directory..D run script (Go)....G |

Send files...... Receive files.....R

cOnfigure Minicom...0

comm Parameters....P Add linefeed.....A

Suspend minicom....J

Capture on/off.....L Hangup.....H

eXit and reset....X

send break.....F

initialize Modem...M

Quit with no reset.Q

Terminal settings..T

run Kermit.....K

Cursor key mode....I

lineWrap on/off....W local Echo on/off..E

Help screen.....Z

Paste file....Y

Timestamp toggle...N | scroll Back.....B

Add Carriage Ret...U

Select function or press Enter for none.

```

Figure 3. Minicom Command Summary

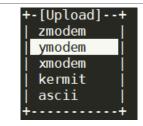

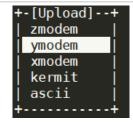

Then press "S" to select the "Send Files" command:

**NXP MPU Cortex-A Core Zephyr User Guide**

Figure 4. Select ymodem

Select ymodem, then select or input the path and name of zephyr.bin.

```

-----[Select one or more files for upload]-----

Directory: /root

. . ]

.cache]

.config]

.local]

.ssh]

[snap]

.Xauthority

.bash history +--

|No file selected - enter filename:

.bashrc

> /tftpboot/imx93/zephyr.bin

.lesshst

.minirc.dfl

.openocd_history

.profile

.sudo_as_admin_successful

(Escape to exit, Space to tag)

```

Figure 5. Select or input the path and name of zephyr.bin

Then zephyr.bin is downloaded to the memory through the serial port:

```

From the section of t

```

Figure 6. Download the zephyr.bin file

6. Then kick zephyr.bin to the Cortex-A55 Core1:

```

u-boot=> dcache flush;

icache flush;

cpu 1 release 0xd0000000

```

Or kick the zephyr.bin to the Cortex-A55 Core0:

```

u-boot=> dcache flush;

icache flush;

go 0xd0000000

```

- 7. The UART console of Zephyr now displays the Zephyr booting log.

- 8. If needed, use the following command to poweroff the RTOS running on Core1 (the first Core is Core0):

```

u-boot=> cpu 1 disable

```

#### 4.1.5.3 Booting Zephyr by using Linux RemoteProc

Remoteproc (Remote Processor Framework) under Linux is another Cortex-A core Zephyr RTOS management tool in addition to the U-Boot commands in U-Boot. Using remoteproc can dynamically start or stop Zephyr

**NXP MPU Cortex-A Core Zephyr User Guide**

under Linux. The limitation of this Cortex-A core Zephyr life cycle management method is that Linux must be running on at least single Cortex-A Core in order to manage Zephyr running on any of the other Cortex-A cores.

Remoteproc is used to control the remote processors that might run different instances of operation system. For example, it can be used for power on, loading firmware, or switching off the power of the remote processor. For SMP Linux which it runs on multiple Cortex-A Cores, each Cortex-A Core can be used as a remote processor, and can use remoteproc to bring up or bring down another RTOS instance on it. In order to run another RTOS on it, remoteproc first removes this Cortex-A Core from SMP Linux by using a CPU hotplug. Then, brings it to be down. It then brings it up again with a new RTOS instance to run it. Remoteproc can also bring this CPU core running RTOS to be down and then plug it back to SMP Linux by using CPU hotplug.

#### • Linux Device Tree Configuration:

In order to use remoteproc to manage life cycle on Cortex-A Core, you must add device nodes in Linux dts. For example, the following dts nodes are defined in <code>imx93-rproc-ca55.dtsi</code> (provided in Real-time Edge Linux kernel: <a href="https://github.com/nxp-real-time-edge-sw/real-time-edge-linux">https://github.com/nxp-real-time-edge-sw/real-time-edge-linux</a>). This file defines single remoteproc instances, it use fsl, cpus-bits defines CPU core bitmask to specify which CPU core(s) can be managed by this instance. The memory-region specifies the reserved memory space used by RTOS to be run on this instance.

```

ca55_1: remoteproc-ca55-1 {

compatible = "fsl,imx-rproc-psci"; /* bitmask:0b10, assign A55 Core 1 */

fsl,cpus-bits = <0x2>;

memory-region = <&rtos_ca55_reserved>;

};

```

#### Hardware Resource Allocation between RTOS and Linux

In order to run a flexible AMP system with Multiple RTOS and Linux running together on the single SoC simultaneously, the hardware resources need to be allocated to different OS carefully to avoid conflicts, the hardware resources include memory and peripherals. Refer to  ${\tt imx93-11x11-evk-multicore-rtos.dts}$  in Real-time Edge Linux (<a href="https://github.com/nxp-real-time-edge-sw/real-time-edge-linux">https://github.com/nxp-real-time-edge-sw/real-time-edge-linux</a>) as an example, the memory used by RTOS need to be added to reserved-memory in Linux dts, and Linux dts nodes UART4 should be disabled as it is used as RTOS debug console.

#### • GIC Configuration to run multiple RTOS on Cortex-A Cores

When running multiple OSes on different Cortex-A Cores on one platform, you must avoid GIC being reconfigured. GIC reconfiguration might crash the OS that has already been started. To achieve this step, configure the following:

- For Zephyr, enable "CONFIG GIC SAFE CONFIG=y".

- For the Linux kernel, enable "CONFIG GIC GENTLE CONFIG=y".

#### Using remoteproc to start or stop RTOS on Cortex-A Core

1. **Start Linux** In order to run RTOS, must use a device tree which is enabled remoteproc and has compatible resource allocation between RTOS and Linux. In Real-time Edge Linux, "imx93-11x11-evk-multicorertos.dtb" can be used to run the Zephyr hello world application.

To do this, when U-Boot is executing, stop at the U-Boot prompt with a terminal emulator connected to the serial port and execute the following commands:

```

u-boot=> setenv fdtfile imx93-11x11-evk-multicore-rtos.dtb

u-boot=> setenv mmcargs $mmcargs clk_ignore_unused

u-boot=> run bsp_bootcmd

```

2. **Using RemoteProc to start or stop Zephyr** When Linux boots up, log in Linux. Then use "scp" or other methods to download or copy zephyr.elf to the directory: /lib/firmware/

The remoteproc sys portal is available at the following directory:

/sys/devices/platform/remoteproc-ca55-1/remoteproc/remoteproc0

UG10199

12 / 82

**NXP MPU Cortex-A Core Zephyr User Guide**

3. Then, use the following command to start Zephyr:

Zephyr log will display on the Zephyr UART console. If needed, use the following command to stop RTOS running on Core1:

```

root@imx93evk:~# echo stop > /sys/devices/platform/remoteproc-ca55-1/

remoteproc/remoteproc0/state

```

Cortex-A Core dynamic allocation between Linux and the RTOS

Before running RTOS by using remoteproc, all Cortex-A Cores are used by the SMP Linux kernel by default. After running RTOS on the specified Cortex-A Core by using remoteproc, these Cortex-A core(s) are hot removed from the SMP Linux kernel and RTOS runs on them. After using the remoteproc <code>stop</code> command to stop the RTOS running on Cortex-A Core, these CPU cores once used by RTOS are hot added back to the SMP Linux kernel. Use the following command to check which CPU Core is used by the SMP Linux kernel currently:

root@imx93evk:~# cat /proc/cpuinfo

**NXP MPU Cortex-A Core Zephyr User Guide**

#### 4.2 i.MX 8M Plus

#### 4.2.1 Overview

The i.MX 8M Plus family focuses on machine learning and vision, advanced multimedia, and industrial automation with high reliability. It is built to meet the needs of Smart Home, Building, City and Industry 4.0 applications.

- Powerful quad or dual Arm Cortex-A53 processor with a Neural Processing Unit (NPU) operating at up to 2.3 TOPS.

- Dual image signal processors (ISP) and two camera inputs for an effective advanced vision system.

- The multimedia capabilities include video encode (including h.265) and decode, 3D/2D graphic acceleration, and multiple audio and voice functionalities.

- Real-time control with Cortex-M7. Robust control networks supported by dual CAN FD and dual Gigabit Ethernet with Time Sensitive Networking (TSN).

- · High industrial reliability with DRAM inline ECC.

Refer to NXP Official website for more details: i.MX 8M Plus | Cortex-A53/M7 | NXP Semiconductors

#### 4.2.2 Zephyr SoC and Board

From Zephyr 3.7 release, Zephyr SoC and Board have changed from hardware model v1 (HWMV1) to hardware model v2(HWMV2).

#### Table 5. HWMV2:

| Parameter                   | Path                                                   |

|-----------------------------|--------------------------------------------------------|

| SoC source code directory   | soc/nxp/imx/imx8m/                                     |

| Board source code directory | boards/nxp/imx8mp_evk/                                 |

|                             | imx8mp_evk/mimx8ml8/a53<br>imx8mp_evk/mimx8ml8/a53/smp |

#### Table 6. HWMV1

| Parameter                         | Parameter                          |

|-----------------------------------|------------------------------------|

| SoC source code directory         | soc/arm64/nxp_imx/mimx8m/          |

| Board source code directory       | boards/arm64/mimx8mp_evk/          |

| Supported board name and variants | mimx8mp_evk_a53mimx8mp_evk_a53_smp |

#### 4.2.3 Peripheral drivers

Table 7. Peripheral drivers on i.MX 8M Plus

| Table 11 Comprise and Comprise |             |                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------------|

| Peripheral                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Driver      | Reference                      |

| GIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | GIC v3      | 5.3 Interrupt-Controller - GIC |

| Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ССМ         | 5.6 Clock – CCM                |

| IOMUX Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Pinctrl IMX | 5.4 IOMUX – pinctrl_imx        |

| UART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IUART       | 5.1 UART - IUART               |

| GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | IGPIO       | <u>5.12</u> GPIO - IGPIO       |

#### **NXP MPU Cortex-A Core Zephyr User Guide**

Table 7. Peripheral drivers on i.MX 8M Plus...continued

| Peripheral      | Driver | Reference              |

|-----------------|--------|------------------------|

| I2C             | II2C   | <u>5.13</u> I2C - II2C |

| TPM Counter     | GPT    | 5.9 Counter - GPT      |

| Ethernet - ENET | ENET   | 5.15 Ethernet - ENET   |

#### 4.2.4 Building Zephyr application

Take the samples/hello world application as an example:

#### HWMV2:

```

west build -p always -b imx8mp_evk/mimx8ml8/a53 samples/hello_world/

```

#### HWMV1:

```

west build -p always -b mimx8mp_evk_a53 samples/hello_world/

```

Then Zephyr binary image "zephyr.bin" and elf image "zephyr.elf" can be located in the zephyr/build/zephyr/ directory.

#### 4.2.5 Running Zephyr application on the i.MX 8M Plus board

Zephyr on Cortex-A Core can be booted up or stopped on specified Cortex-A Core by using the U-Boot commands or remoteproc under Linux.

#### 4.2.5.1 Board setup and software preparation (i.MX 8M Plus)

Prepare the i.MX 8M Plus EVK board to run Zephyr:

1. **UART Console Setup** Connect USB debug connector J23 to PC, PC enumerates four COM ports when the USB cable is plugged into J23. For example on Linux host, the four COM ports could be /dev/ttyUSB0 ~ /dev/ttyUSB3, the ID of a ttyUSB device could be different if multiple USB serial cables are plugged into the same PC. Therefore, you can check the kernel log after the i.MX EVK debug cable is plugged into the PC. For example, the following log shows the COM ports should be /dev/ttyUSB0 ~ /dev/ttyUSB3.

```

linux:~$ sudo dmesq | tail

[272709.527874] usb 3-2.1.2: FTDI USB Serial Device converter now attached to

ttyUSB0

[272709.528196] ftdi sio 3-2.1.2:1.1: FTDI USB Serial Device converter

[272709.528266] usb 3-2.1.2: Detected FT4232H

[272709.528582] usb 3-2.1.2: FTDI USB Serial Device converter now attached to

ttyUSB1

[272709.528888] ftdi sio 3-2.1.2:1.2: FTDI USB Serial Device converter

detected

[272709.528957] usb 3-2.1.2: Detected FT4232H

[272709.529217] usb 3-2.1.2: FTDI USB Serial Device converter now attached to

ttyUSB2

[272709.529451] ftdi sio 3-2.1.2:1.3: FTDI USB Serial Device converter

detected

[272709.529514] usb 3-2.1.2: Detected FT4232H

[272709.529780] usb 3-2.1.2: FTDI USB Serial Device converter now attached to

ttyUSB3

```

**NXP MPU Cortex-A Core Zephyr User Guide**

The third port (it is /dev/ttyUSB2 in the above example) is used for U-Boot and Linux. The fourth port (it is /dev/ttyUSB3 in the above example) is used for Zephyr debug console by default. Developers can use minicom, Putty, Tera Term, Xshell, or other terminal tools to open these two UART consoles with the 115200 Baud rate, 8-bit data bits, 1 stop bit, and none parity.

- 2. **Deploying the pre-built SD card image** Zephyr on Cortex-A Core can be booted up or stopped on specified Cortex-A Core by using the U-Boot commands or remoteproc under Linux. U-Boot commands and remoteproc to start or stop Cortex-A Core Zephyr are supported in Real-time Edge software release in v3.0 and late releases (<a href="https://www.nxp.com/rtedge">https://www.nxp.com/rtedge</a>), so a quick method to setup software environment on i.MX 8M Plus EVK is to deploy the pre-build image (.wic image) to the SD card and boot from it directly.

- 3. Follow the following steps to prepare an SD/MMC card to boot up an i.MX board using a Linux host machine.

- a. Download latest Real-time Edge release pre-build image for the EVK board from <a href="https://www.nxp.com/rtedge">https://www.nxp.com/rtedge</a>.

| Release and Documentation                                                                                                                                                                                                                                                                                  | <b>Build Sources</b>                           | Supported Platforms/Pre-<br>Built Binary                                                                                                                                                                                                                                                  | What's New                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Real Time Edge Software v3.0  Release Date: Dec 2024  Documentation  Real-time Edge Software User Guide Real-Time Edge Yocto Project User's Guide Real-time Edge Software Release Notes Guide GenAVB/TSN Stack Evaluation User Guide Harpoon User's Guide  I.MX6ULL EVK GenAVB/TSN Rework Application Note | See README L'on instructions for each release. | IMX6ULI14X14EVK IMX8MM-LPDDR4-EVK IMX8DXLB0-LPDDR4-EVK IMX91-11X11-LPDDR4-EVK IMX91-9X9-LPDDR4-QSB IMX9MP-LPDDR4-QSB IMX93-9X9-LPDDR4-QSB IMX93-14X14-LPDDR4X-EVK IMX93-15X15-LPDDR4X-EVK IMX95-15X15-LPDDR4X-EVK IMX95-19X19-LPDDR5-EVK LS1028ARDB LS1043ARDB LS1046ARDB LX2160ARDB-REV2 | Real-time System Preempt-RT Linux 6.6.36-rt35(tag If-6.6.36-rt-2.1.0) Baremetal (U-Boot 2024.04) RTOS on Cortex-A core Uprev: Zephyr v3.7, FreeRTOS kernel V11.0 RTOS with Jailhouse Harpoon 3.2 Heterogeneous Multicore Framework Unified lifecycle management Linux remoteproc start/stop U-Boot cpu disable/status Enhanced ram console with dumping tool Heterogeneous Multi-SoC Framework Linux DSA: device driver of DSA control interface TSN configuration: CB/Qci/Qbv RTTI BO OTSN switch configuration on i.MX RT1180 OTSN configuration: CB/Qci/Qbv |

Then a zip file "Real-time\_Edge\_vx.x\_IMX8MP-LPDDR4-EVK.zip" (x.x is replaced with release version) is downloaded. Extract the .wic file named "nxp-image-real-time-edge-imx8mp-lpddr4-evk. rootfs.wic" from the path "Real-time\_Edge\_vx.x\_IMX8MP-LPDDR4-EVK/real-time-edge/nxp-image-real-time-edge-imx8mp-lpddr4-evk.rootfs.wic.zst" in the zip file.

The SD card image (with the extension .wic) contains U-Boot, the Linux image and device trees, and the rootfs for a 4 GB SD card. The image can be installed on the SD card with one command if flexibility is not required. Carry out the following command to copy the SD card image to the SD/MMC card. Change sdx below to match the one used by the SD card.

```

$ sudo dd if=<image name>.wic of=/dev/sdx bs=1M && sync

```

The entire contents of the SD card are replaced. If the SD card is larger than 4 GB, the additional space is not accessible. Then, insert the SD card back to the EVK board and change the EVK board to boot from SD card by switching SW4[1:4] to be "0011".

4. Power up the board and you can locate the TF-A and U-Boot log from the third port (it is /dev/ttyUSB2 in the above example).

#### 4.2.5.2 Booting Zephyr by using U-Boot commands1

Multiple U-Boot commands can be used to start or stop Zephyr on the Cortex-A core.

UG10199

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

**NXP MPU Cortex-A Core Zephyr User Guide**

#### 4.2.5.2.1 "cpu" command

Following is the help information of the U-Boot cpu command:

```

u-boot=> cpu

```

cpu - Multiprocessor CPU boot manipulation and release

#### Usage:

- cpu <num> reset Resets cpu <num>

- cpu status Displays the status of all cpus

- cpu <num> status Displays the status of cpu <num>

- cpu <num> disable Disables the status of cpu <num>

- cpu <num> release <addr> [args] Releases cpu <num> at <addr> with [args]

Except the "cpu <num> reset" command, all other cpu commands have been implemented on i.MX 8M Mini platform.

In general, U-Boot runs on the master Core (Core0) of Cortex-A cores. Therefore, to start RTOS on any other slave Cortex-A core (the Cores except Core0) from the specified memory address, use the command below:

```

"cpu <num> release <addr> [args]"

```

For this purpose, load the RTOS binary images into the corresponding memory space, and use the "cpu <num> disable" command to power off any slave core that runs RTOS. Use the commands "cpu status" or "cpu <num>" status to check the status (running or power off) for all or the specified Cortex-A cores.

#### 4.2.5.2.2 "go" command

The following is the help information of the U-Boot go command:

```

U-Boot=> qo

```

go - starts the application at address 'addr'

#### Usage:

```

go addr [arg ...]

```

- starts the application at address 'addr'

Passing 'arg' as arguments

The "go" command can be used to start the application or RTOS running on the master Core (Core0). The impact is not returned back to the U-Boot command line.

In summary, you can use U-Boot command "go" to boot the RTOS from Core0 or use U-Boot command "cpu" to boot or power off the RTOS running on the other Cortex-A cores except Core0.

#### 4.2.5.2.3 Running the Zephyr application on i.MX 8M Plus EVK

The below example shows how to run the hello world examples on the i.MX 8M Plus board.

- 1. Power up the i.MX 8M Plus EVK board and stop at the U-Boot command line.

- 2. Deploy Zephyr binary image "zephyr.bin" to the board.

**NXP MPU Cortex-A Core Zephyr User Guide**

There are multiple methods can be used to deploy the <code>zephyr.bin</code> to the board, select one the below methods:

a. Download the image into memory from tftp server:

```

u-boot=> tftp 0xc0000000 zephyr.bin

```

- b. **Or** copy the image to SD Card by using Linux host PC:

- There are two partitions in the SD Card if .wic is deployed on the SD Card.

- The first one is the FAT partition, which is used to store Linux image and dtb files.

- The second one is the Linux partition to be used for the Linux Root file system.

Copy the Zephyr binary image "zephyr.bin" to the first FAT partition of the SD card by using Linux host PC. Then, plug the card into the board. Now, power up the board and stop at U-Boot command line. Then, load the image from the SD card into memory by using the following U-Boot command:

```

u-boot=> fatload mmc 1:1 0xc0000000 zephyr.bin;

```

c. Or download the image into memory by using serial port

For example, to load the binary file over a serial line in ymodem mode, execute the following command under U-Boot:

```

u-boot=> loady 0xc0000000

```

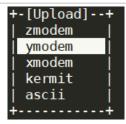

Then, send the binary file from console software in the host PC. Different steps for different console software. Here, take minicom as an example: Use the quick key "ctrl + A + Z" (pressed down and hold the "ctrl" key and then press the key "A" and "Z" in turn) to open the command window.

Figure 8. Minicom Command Summary

Then press "S" to select the "Send Files" command:

Figure 9. Select ymodem

Select **ymodem**, then select or input the path and name of zephyr.bin.

**NXP MPU Cortex-A Core Zephyr User Guide**

```

-----[Select one or more files for upload]------

Directory: /root

[...]

[.cache]

[.config]

[.local]

[.ssh]

[snap]

.Xauthority

.bash_history

|No file selected - enter filename:

bashrc

> /tftpboot/imx8mp/zephyr.bin

.lesshst

.minirc.dfl

.openocd history

.profile

.sudo as admin successful

(Escape to exit, Space to tag)

```

Then zephyr.bin is downloaded to the memory through the serial port:

```

+----------[ymodem upload - Press CTRL-C to quit]----------+

|Sending: zephyr.bin

|Bytes Sent: 37120 BPS:2854 |

|Sending: |

|Ymodem sectors/kbytes sent: 0/ 0k |

|Transfer complete |

| READY: press any key to continue...

```

Figure 11. Download the zephyr.bin file

3. Then kick zephyr.bin to the Cortex-A53 Core3:

Figure 10. Select or input the path and name of zephyr.bin <tbd>

```

u-boot=> dcache flush;

icache flush;

cpu 3 release 0xc0000000

```

#### Or kick the zephyr.bin to the Cortex-A53 Core0:

```

u-boot=> dcache flush;

icache flush;

go 0xc0000000

```

- 4. The UART console of Zephyr now displays the Zephyr booting log.

- 5. If needed, use the following command to power off the RTOS running on Core3 (the first Core is Core0):

```

u-boot=> cpu 3 disable

```

#### 4.2.5.3 Booting Zephyr by using Linux RemoteProc

Remoteproc (Remote Processor Framework) under Linux is another Cortex-A Core Zephyr RTOS management tool under Linux. Apart from the U-Boot commands in U-Boot, using remoteproc can dynamically start or stop Zephyr under Linux. To manage Zephyr running on any of the other Cortex-A Cores, Linux must run on at least single Cortex-A Core. This is the limitation of the Remoteproc life cycle management method.

Remoteproc under Linux can be used to control remote processors on which different instances of the operating system are running. For example, it can be used to control the power on, load firmware, or power off of these processors.

For SMP Linux, which runs on multiple Cortex-A cores, each Cortex-A core can be used as a remote processor. In such as case, remoteproc can be used to bring up or bring down another RTOS instance on SMP Linux. To

**NXP MPU Cortex-A Core Zephyr User Guide**

run another RTOS on it, remoteproc firstly removes this Cortex-A Core from SMP Linux by using a CPU hotplug and brings it down. Then, it brings up Cortex-A Core again with a new RTOS instance to run it. Remoteproc can also bring this CPU Core running RTOS to be down and then plug it back to SMP Linux by using a CPU hotplug.

#### Linux Device Tree Configuration

To use remoteproc to manage the life cycle on Cortex-A Core, you must add device nodes in Linux dts. Real-time Edge Linux kernel: <a href="https://github.com/nxp-real-time-edge-sw/real-time-edge-linux">https://github.com/nxp-real-time-edge-sw/real-time-edge-linux</a>) defines four remoteproc instances, For example, the following dts nodes are defined in <a href="https://www.ncproc-ca53.dtsi.lt.uses">https://www.ncproc-ca53.dtsi.lt.uses</a> 'fsl, <a href="https://cpus-bits'</a> to define CPU core bitmask to specify the CPU core(s) that the instance can manage. The 'memory-region' specifies the reserved memory space used by RTOS to be run on this instance.

```

ca53 1: remoteproc-ca53-1 {

compatible = "fsl,imx-rproc-psci";

/* bitmask:0b0010, assign A53 Core 1 */

fsl,cpus-bits = <0x2>;

memory-region = <&rtos ca53 reserved>;

};

ca53 2: remoteproc-ca53-2 {

compatible = "fsl,imx-rproc-psci";

/* bitmask:0b0100, assign A53 Core 2 */

fsl,cpus-bits = <0x4>;

memory-region = <&rtos ca53 reserved>;

};

ca53 3: remoteproc-ca53-3 {

compatible = "fsl,imx-rproc-psci";

/* bitmask:0b1000, assign A53 Core 3 */

fsl,cpus-bits = <0x8>;

memory-region = <&rtos ca53 reserved>;

ca53 2 3: remoteproc-ca53-2-3 {

compatible = "fsl,imx-rproc-psci";

/* bitmask:0b1100, assign A53 Core 2 and Core 3 */

fsl,cpus-bits = <0xc>;

memory-region = <&rtos ca53 reserved>;

};

```

The fourth remoteproc instance "ca53\_2\_3" uses two CPU Core: Core2 and Core3, so it can used to run an SMP RTOS on these two CPU cores. As remoteproc instance "ca53\_3" and "ca53\_2\_3" both use CPU core Core3, so these two instances cannot run simultaneously.

#### Hardware Resource Allocation between RTOS and Linux

To run a flexible AMP system with multiple RTOSes and Linux running together on a single SoC simultaneously, certain guidelines must be followed. The hardware resources including memory and peripherals must be allocated to different OSes carefully to avoid conflicts.

Refer to "imx8mp-evk-multicore-rtos.dts" in Real-time Edge Linux (<a href="https://github.com/nxp-real-time-edge-sw/real-time-edge-linux">https://github.com/nxp-real-time-edge-sw/real-time-edge-linux</a>) as an example. For this use case, the memory used by RTOS must be added to the reserved-memory in Linux dts, and Linux dts nodes UART4 must be disabled as it is used as an RTOS debug console.

- GIC Configuration to run multiple RTOS on Cortex-A Cores When running multiple OSes on different Cortex-A Cores on one platform, you must avoid GIC being reconfigured. GIC reconfiguration might crash the OS that has already been started. To achieve this step, configure the following:

- For Zephyr, enable "CONFIG GIC SAFE CONFIG=y".

- For the Linux kernel, enable "CONFIG GIC GENTLE\_CONFIG=y".

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

**NXP MPU Cortex-A Core Zephyr User Guide**

- Using remoteproc to start or stop RTOS on Cortex-A Core: Use the following steps to start or stop RTOS by using remoteproc:

- 1. **Start Linux** To run RTOS, users must use a device tree that has remoteproc enabled and has compatible resource allocation between RTOS and Linux.

- 2. Running Zephyr: In Real-time Edge Linux, "imx8mp-evk-multicore-rtos.dtb" can be used to run the Zephyr hello\_world application. During U-Boot execution, stop at the U-Boot prompt using a terminal emulator connected to the serial port and run the following commands:

```

u-boot=> setenv fdtfile imx8mp-evk-multicore-rtos.dtb

u-boot=> setenv mmcargs $mmcargs clk_ignore_unused

u-boot=> run bsp_bootcmd

```

3. **Using RemoteProc to start or stop Zephyr**: When Linux boots up, log in to Linux. Then use "scp" or any other method to download or copy <code>zephyr.elf</code> to directory: <code>/lib/firmware/</code> The following remoteproc sys portals are available in the following directories:

```

/sys/devices/platform/remoteproc-ca53-1/remoteproc/remoteproc0/

/sys/devices/platform/remoteproc-ca53-2/remoteproc/remoteproc1/

/sys/devices/platform/remoteproc-ca53-3/remoteproc/remoteproc2/

/sys/devices/platform/remoteproc-ca53-2-3/remoteproc/remoteproc3/

```

**Note:** The remoteproc portal instance depends on the device tree configuration used and changes accordingly. Therefore, use the name under each remoteproc instance portal to check the instance that must be used.

4. Then, use the following command to start Zephyr:

```

root@imx8mp-lpddr4-evk:~# echo zephyr.elf > /sys/devices/platform/

remoteproc-ca53-3/remoteproc/remoteproc2/firmware

root@imx8mp-lpddr4-evk:~# echo start > /sys/devices/platform/remoteproc-ca53-3/remoteproc/remoteproc2/state

```

Then, the Zephyr log is displayed on the Zephyr UART console. If needed, use the following command to stop RTOS running on Core1:

```

root@imx8mp-lpddr4-evk:~# echo stop > /sys/devices/platform/remoteproc-

ca53-3/remoteproc/remoteproc2/state

```

5. Cortex-A core dynamically allocated between Linux and RTOS Before running RTOS by using remoteproc, the SMP Linux kernel by default uses all Cortex-A Cores. After running RTOS on the specified Cortex-A Core by using remoteproc, these Cortex-A core(s) are hot removed from SMP Linux kernel and RTOS is run on them. After using the remoteproc stop command to stop the RTOS running on Cortex-A Core, these CPU cores once used by RTOS are hot added back to SMP Linux kernel. Users can use the following command to identify the CPU Core that is being used by SMP Linux kernel currently:

```

root@imx8mp-lpddr4-evk:~# cat /proc/cpuinfo

```

**NXP MPU Cortex-A Core Zephyr User Guide**

#### 4.3 i.MX 8M Mini

#### 4.3.1 Overview

NXP's i.MX 8M Mini applications processor demonstrates the latest video and audio experience by combining state-of-the-art media-specific features with high-performance processing while keeping the design optimized for lowest power consumption.

The i.MX 8M Mini family of processors features advanced implementation of a quad Arm Cortex-A53 core, which operates at speeds of up to 1.6 GHz. A general-purpose Cortex-M4 400 MHz core processor is used for low-power processing. The DRAM controller supports 32-bit/16-bit LPDDR4, DDR4, and DDR3L memories. A wide range of audio interfaces are available, including I2S, AC97, TDM, and S/PDIF. There are a number of other interfaces for connecting peripherals, such as USB, PCIe, and Ethernet.

Refer to NXP Official website for more details: <u>i.MX 8M Mini | Arm Cortex A53 | Cortex M4 | NXP Semiconductors</u>

#### 4.3.2 Zephyr SoC and Board

From Zephyr 3.7 release, it changed from hardware model v1 (HWMV1) to hardware model v2(HWMV2).

Table 8. HWMV2

| Parameter                         | Path                        |

|-----------------------------------|-----------------------------|

| SoC source code directory         | soc/nxp/imx/imx8m/          |

| Board source code directory       | boards/nxp/imx8mm_evk/      |

| Supported board name and variants | imx8mm_evk/mimx8mm6/a53     |

|                                   | imx8mm_evk/mimx8mm6/a53/smp |

#### Table 9. HWMV1

| Parameter                         | Path                                    |

|-----------------------------------|-----------------------------------------|

| SoC source code directory         | soc/arm64/nxp_imx/mimx8m/               |

| Board source code directory       | boards/arm64/mimx8mm_evk/               |

| Supported board name and variants | mimx8mm_evk_a53     mimx8mm_evk_a53_smp |

#### 4.3.3 Peripheral drivers

Table 10. Peripheral drivers on i.MX 8M Mini

| Peripheral       | Driver      | Reference                      |

|------------------|-------------|--------------------------------|

| GIC              | GIC v3      | 5.3 Interrupt-Controller - GIC |

| Clock            | ССМ         | 5.6 Clock – CCM                |

| IOMUX Controller | Pinctrl IMX | 5.4 IOMUX – pinctrl_imx        |

| UART             | IUART       | 5.1 UART - IUART               |

| GPIO             | IGPIO       | 5.12 GPIO - IGPIO              |

| I2C              | II2C        | 5.13 I2C - II2C                |

| TPM Counter      | GPT         | 5.9 Counter - GPT              |

**NXP MPU Cortex-A Core Zephyr User Guide**

Table 10. Peripheral drivers on i.MX 8M Mini...continued

| Peripheral      | Driver | Reference            |

|-----------------|--------|----------------------|

| Ethernet - ENET | ENET   | 5.15 Ethernet - ENET |

#### 4.3.4 Building the Zephyr application on i.MX 8M Mini

Take the samples/hello world application as an example.

#### HWMV2:

```

west build -p always -b imx8mm_evk/mimx8mm6/a53 samples/hello_world/

```

#### HWMV1:

```

west build -p always -b mimx8mm_evk_a53 samples/hello_world/

```

Then, Zephyr binary image "zephyr.bin" and elf image "zephyr.elf" can be located in the zephyr/build/zephyr/directory.

#### 4.3.5 Running Zephyr on i.MX 8M Mini EVK board

Zephyr on Cortex-A core can be booted up or stopped on a specified Cortex-A core by using the U-Boot commands or remoteproc under Linux.

#### 4.3.5.1 Board setup and software preparation (i.MX 8M Mini EVK)

Prepare the i.MX 8M Mini EVK board to run Zephyr:

1. UART console setup: Connect USB debug connector J901 to the PC. The PC enumerates two COM ports when the USB cable is plugged into J901. For example on Linux host, the two COM ports could be / dev/ttyUSB0 ~ /dev/ttyUSB1, the ID of ttyUSB device could be changed if multiple USB serial cables are pluged into the same PC, so could check the kernel log after i.MX EVK debug cable is pluged into the PC, for example, the following log shows the COM ports must be /dev/ttyUSB0 ~ /dev/ttyUSB1.

```

linux:~$ sudo dmesg | tail

[525744.711621] usb 3-2.2: New USB device found, idVendor=0403,

idProduct=6010, bcdDevice= 5.00

[525744.711640] usb 3-2.2: New USB device strings: Mfr=1, Product=2,

SerialNumber=0

[525744.711646] usb 3-2.2: Product: Dual RS232

[525744.711652] usb 3-2.2: Manufacturer: FTDI

[525744.723483] ftdi_sio 3-2.2:1.0: FTDI USB Serial Device converter detected

[525744.723590] usb 3-2.2: Detected FT2232C/D

[525744.724076] usb 3-2.2: FTDI USB Serial Device converter now attached to

ttyUSB0

[525744.724621] ftdi_sio 3-2.2:1.1: FTDI USB Serial Device converter detected

[525744.724705] usb 3-2.2: Detected FT2232C/D

[525744.725187] usb 3-2.2: FTDI USB Serial Device converter now attached to

ttyUSB1

```

The second COM port (it is /dev/ttyUSB1 in above example) is used for U-Boot and Linux, and the first COM port (it is /dev/ttyUSB0 in above example) is used for Zephyr debug console by default. Developers can use minicom, Putty, Tera Term, Xshell, or other terminal tools to open these two UART consoles with the 115200 Baud rate, 8bit data bits, 1 stop bits and none parity.

2. **Deploying the pre-built SD card image** Zephyr on Cortex-A Core can be booted up or stopped on specified Cortex-A Core by using the U-Boot commands or remoteproc under Linux. U-Boot commands and remoteproc to start or stop Cortex-A Core Zephyr are supported in Real-time Edge software release in v3.0

**NXP MPU Cortex-A Core Zephyr User Guide**

and late releases (<a href="https://www.nxp.com/rtedge">https://www.nxp.com/rtedge</a>), so a quick method to setup software environment on i.MX 8M Mini EVK is to deploy the pre-build image (.wic image) to SD card and boot from it directly.

- 3. Follow the following steps to prepare an SD/MMC card to boot up an i.MX board using a Linux host machine.

- 4. Download latest Real-time Edge release pre-build image for the EVK board from <a href="https://www.nxp.com/rtedge">https://www.nxp.com/rtedge</a>

| Release and Documentation                                                                                                                                                                                                                                                                                | <b>Build Sources</b>                           | Supported Platforms/Pre-<br>Built Binary                                                                                                                                                                                                                                                    | What's New                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Real Time Edge Software v3.0  Release Date: Dec 2024  Documentation  Real-time Edge Software User Guide  Real-Time Edge Yocto Project User's Guide  Real-time Edge Software Release Notes  GenAVB/TSN Stack Evaluation User Guide  Harpoon User's Guide  i.MXGULL EVK GenAVB/TSN Rework Application Note | See README & on instructions for each release. | IMX6ULL14X14EVK  IMX8MM-LPDDR4-EVK  IMX8DXLB0-LPDDR4-EVK  IMX91-IIX11-LPDDR4-EVK  IMX91-9X9-LPDDR4-QSB  IMX9MP-LPDDR4-EVK  IMX93-9X9-LPDDR4-QSB  IMX93-14X14-LPDDR4X-EVK  IMX95-15X15-LPDDR4X-EVK  IMX95-15X15-LPDDR4X-EVK  IMX95-19X19-LPDDR5-EVK  LS1028ARDB  LS1045ARDB  LX2160ARDB-REV2 | Real-time System Preempt-RT Linux 6.6.36-rt35(tag If-6.6.36-rt-2.1.0) Baremetal (U-Boot 2024.04) RTOS on Cortex-A core Uprev: Zephyr v3.7, FreeRTOS kernel V11.0.1 RTOS with Jailhouse Harpoon 3.2 Heterogeneous Multicore Framework Unified lifecycle management Linux remoteproc start/stop U-Boot cpu disable/status Enhanced ram console with dumping tools Heterogeneous Multi-SoC Framework Linux DSA: device driver of DSA control interface TSN configuration: CB/Qci/Qbv NETC DSA switch configuration on i.MX RT180  OTSN configuration: CB/Qci/Qbv REal-time Networking |

- 5. Then a zip file "Real-time\_Edge\_vx.x\_IMX8MM-LPDDR4-EVK.zip" (x.x is replaced with release version) is downloaded. Extract the .wic file named "nxp-image-real-time-edge-imx8mm-lpddr4-

- evk.rootfs.wic" from the path "Real-time\_Edge\_vx.x\_IMX8MM-LPDDR4-EVK/real-time-edge/nxp-image-real-time-edge-imx8mm-lpddr4-evk.rootfs.wic.zst" in the zip file.

6. The SD card image (with the extension .wic) contains U-Boot, the Linux image and device trees, and the

- 6. The SD card image (with the extension .wic) contains U-Boot, the Linux image and device trees, and the rootfs for a 4 GB SD card. The image can be installed on the SD card with one command if flexibility is not required. Run the following command to copy the SD card image to the SD/MMC card. Change sdx in the below command to match the one used by the SD card.

```

\ sudo dd if=<image name>.wic of=/dev/sdx bs=1M && sync

```

The entire contents of the SD card are replaced. If the SD card is larger than 4 GB, the additional space is not accessible.

7. Then insert SD card back to the EVK board, and change the EVK board to boot from SD card by switching SW4[1:4] to be "0011". Power up the board and then you can locate the TF-A and U-Boot log from the third port (it is /dev/ttyUSB2 in the above example).

#### 4.3.5.2 Booting Zephyr by using U-Boot commands1

Multiple U-Boot commands can be used to start or stop Zephyr on the Cortex-A core.

#### 4.3.5.2.1 "cpu" command

Following is the help information of the U-Boot cpu command:

u-boot=> cpu

cpu - Multiprocessor CPU boot manipulation and release

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

**NXP MPU Cortex-A Core Zephyr User Guide**

#### Usage:

- cpu <num> reset Resets cpu <num>

- cpu status Displays the status of all cpus

- cpu <num> status Displays the status of cpu <num>

- cpu <num> disable Disables the status of cpu <num>

- cpu <num> release <addr> [args] Releases cpu <num> at <addr> with [args]

Except the "cpu <num> reset" command, all other cpu commands have been implemented on i.MX 8M Mini platform.

In general, U-Boot runs on the master Core (Core0) of Cortex-A cores. Therefore, to start RTOS on any other slave Cortex-A core (the Cores except Core0) from the specified memory address, use the command below:

```

"cpu <num> release <addr> [args]"

```

For this purpose, load the RTOS binary images into the corresponding memory space, and use the "cpu <num> disable" command to power off any slave core that runs RTOS. Use the commands "cpu status" or "cpu <num>" status to check the status (running or power off) for all or the specified Cortex-A cores.

#### 4.3.5.2.2 "go" command

The following is the help information of the U-Boot go command:

```

U-Boot=> go

```

go - starts the application at address 'addr'

#### Usage:

```

go addr [arg ...]

```

- starts the application at address 'addr'

Passing 'arg' as arguments

The "go" command can be used to start the application or RTOS running on the master Core (Core0). The impact is not returned back to the U-Boot command line.

In summary, you can use U-Boot command "go" to boot the RTOS from Core0 or use U-Boot command "cpu" to boot or power off the RTOS running on the other Cortex-A cores except Core0.

#### 4.3.5.2.3 Running Zephyr application on i.MX 8M Mini EVK

Use the steps below to run the Zephyr application on the i.MX 8M Mini EVK board.

- 1. Power up the i.MX 8M Mini EVK board and stop at the U-Boot command line.

- 2. Deploy the Zephyr binary image "zephyr.bin" to the board. There are multiple methods that can be used to deploy zephyr.bin to the board. Select one of the below methods:

- · Download the image into memory from the tftp server:

```

u-boot=> tftp 0x93c00000 zephyr.bin

```

**NXP MPU Cortex-A Core Zephyr User Guide**

- Or copy the image to an SD card by using a Linux host PC.

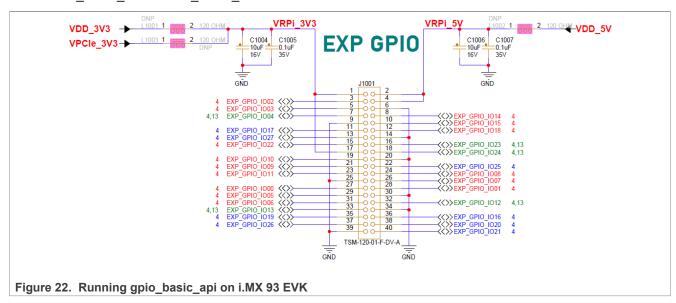

- 3. There are two partitions in the SD card if the .wic is deployed on the SD Card. The first one is the FAT partition, which is used to store the Linux Image and dtb files. The second partition is the Linux partition used for the Linux Root file system.