## MC92520 ATM Cell Processor User's Manual

MC92520UM/D Rev. 0, 12/2000

DigitalDNA and Mfax are trademarks of Motorola, Inc.

Information in this document is provided solely to enable system and software implementers to use Motorola microprocessors. There are no express or implied copyright licenses granted hereunder to design or fabricate Motorola integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (\(\tilde{\text{M}}\) are registered trademarks of Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

#### How to reach us:

**USA/EUROPE/Locations Not Listed:** Motorola Literature Distribution; P.O. Box 5405, Denver, Colorado 80217. 1–303–675–2140 or 1–800–441–2447

**JAPAN:** Motorola Japan Ltd.; SPS, Technical Information Center, 3–20–1, Minami–Azabu. Minato–ku, Tokyo 106–8573 Japan. 81–3–3440–3569

ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong. 852–26668334

Technical Information Center: 1-800-521-6274

HOME PAGE: http://www.motorola.com/semiconductors

Document Comments: FAX (512) 895-2638, Attn: RISC Applications Engineering

World Wide Web Addresses: http://www.motorola.com/PowerPC

http://www.motorola.com/NetComm http://www.motorola.com/ColdFire

| 1   | Introduction                  |

|-----|-------------------------------|

| 2   | Functional Description        |

| 3   | System Operation              |

| 4   | External Interfaces           |

| 5   | Data Path Operation           |

| 6   | Protocol Support              |

| 7   | Programming Model             |

| 8   | Test Operation                |

| 9   | Product Specifications        |

| А   | UPC/NPC Design                |

| В   | Maintenance Slot Calculations |

| С   | VC Bundling                   |

| D   | Applications                  |

| Е   | BSDL Codes                    |

| IND | Index                         |

|     |                               |

| NO |                               |

|----|-------------------------------|

|    | Introduction                  |

| 2  | Functional Description        |

| 3  | System Operation              |

| 4  | External Interfaces           |

| 5  | Data Path Operation           |

| 6  | Protocol Support              |

| 7  | Programming Model             |

| 8  | Test Operation                |

| 9  | Product Specifications        |

| А  | UPC/NPC Design                |

| В  | Maintenance Slot Calculations |

| С  | VC Bundling                   |

| D  | Applications                  |

| Е  | BSDL Codes                    |

|    |                               |

IND

Index

| Paragraph<br>Number | Title Pa<br>Numb                   |      |

|---------------------|------------------------------------|------|

|                     | About This Book                    |      |

|                     | Audience                           | xxix |

|                     | Organization                       | xxix |

|                     | Additional Reading                 | .xxx |

|                     | Conventions                        | xxxi |

|                     | Acronyms and Abbreviationsx        | xxii |

|                     | Chapter 1                          |      |

|                     | Introduction                       |      |

| 1.1                 | ATM Networks                       | 1-1  |

| 1.2                 | MC92520 Applications               | 1-3  |

| 1.2.1               | ATM Network Line Card              | 1-3  |

| 1.2.2               | ATM Network Access Multiplexer     | 1-4  |

| 1.3                 | MC92520 Block Diagram              | 1-5  |

| 1.4                 | MC92520 Features                   |      |

| 1.4.1               | Ingress Features                   |      |

| 1.4.2               | Egress Features                    |      |

| 1.5                 | The MC92520 Versus the MC92501     |      |

| 1.6                 | The MC92510 Versus the MC92520     | 1-9  |

|                     | Chapter 2                          |      |

|                     | Functional Description             |      |

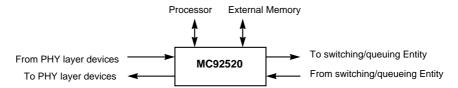

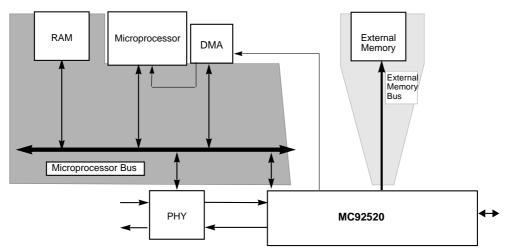

| 2.1                 | System Environment                 | 2-1  |

| 2.2                 | MC92520 Functional Description     |      |

| 2.2.1               | Ingress Cell Flow                  | 2-3  |

| 2.2.2               | Egress Cell Flow                   | 2-4  |

| 2.2.3               | Other Functions                    | 2-4  |

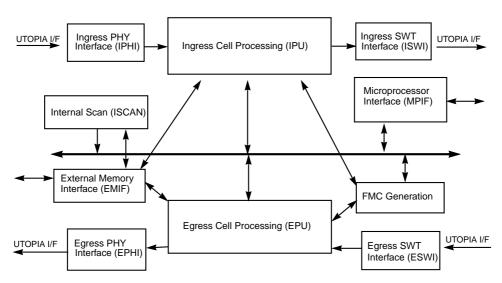

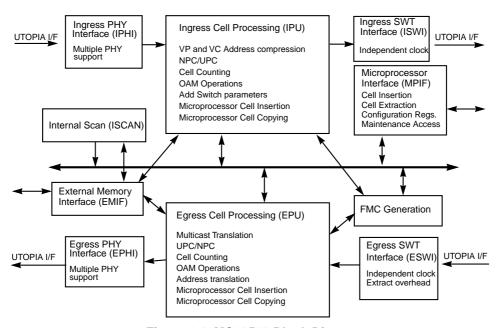

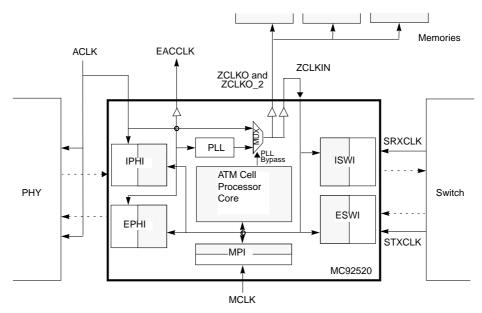

| 2.3                 | MC92520 Block Diagram              |      |

| 2.3.1               | Ingress PHY Interface (IPHI)       |      |

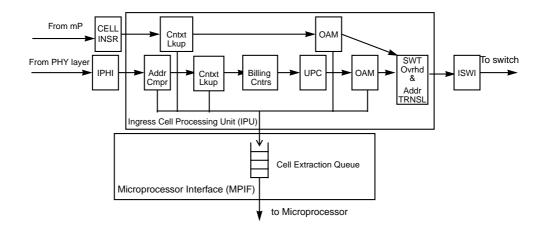

| 2.3.2               | Ingress Cell Processing Unit (IPU) |      |

| 2.3.3               | Ingress Switch Interface (ISWI)    |      |

| 2.3.4               | Egress Switch Interface (ESWI)     | 2-7  |

| Paragraph<br>Number | Title                                          | Page<br>Number |

|---------------------|------------------------------------------------|----------------|

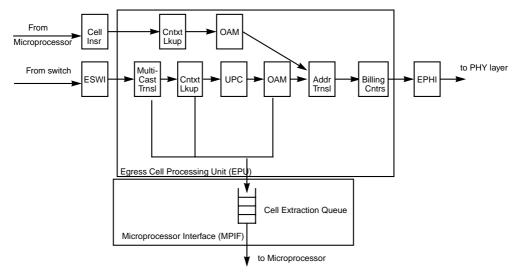

| 2.3.5               | Egress Cell Processing Unit (EPU)              | 2-7            |

| 2.3.6               | Egress PHY Interface (EPHI)                    |                |

| 2.3.7               | External Memory Interface (EMIF)               |                |

| 2.3.8               | Microprocessor Interface (MPIF)                | 2-8            |

| 2.3.9               | Internal Scan (ISCAN)                          |                |

| 2.3.10              | FMC Generation                                 | 2-8            |

|                     | Chapter 3<br>System Operation                  |                |

| 2.1                 |                                                | 2.1            |

| 3.1                 | Setup Mode                                     |                |

| 3.1.1               | Configuring the Phase-Locked Loop (PLL)        |                |

| 3.1.2               | Programming the Configuration Registers        |                |

| 3.1.3               | Initializing External Memory                   |                |

| 3.1.4               | Configuring External Memory Maintenance Slots  |                |

| 3.1.5               | Writing the Enter Operate Mode Register (EOMR) |                |

| 3.2                 | Operate Mode                                   |                |

| 3.2.1               | External Memory Maintenance                    |                |

| 3.2.1.1             | Periodic External Memory Maintenance           |                |

| 3.2.2<br>3.2.2.1    | External Memory Access                         |                |

| 3.2.2.1.1           | Maintenance Slot Access                        |                |

| 3.2.2.1.1           | External Memory Request (EMREQ) FIFO           |                |

| 3.2.2.1.2           | External Memory Read Access Requests           |                |

| 3.2.2.1.4           | External Memory Write Access Requests          |                |

| 3.2.2.1.5           | External Memory Access Errors and Interrupts   |                |

| 3.2.2.2             | Indirect Memory Access                         |                |

| 3.2.2.2.1           | Write Access                                   |                |

| 3.2.2.2.2           | Read Access                                    |                |

| 3.2.3               | Cell Insertion And Extraction                  |                |

| 3.2.3.1             | Cell Insertion                                 |                |

| 3.2.3.2             | Cell Extraction                                | -              |

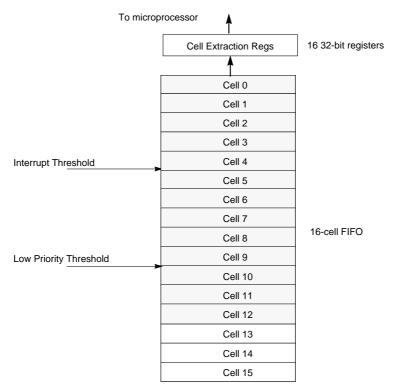

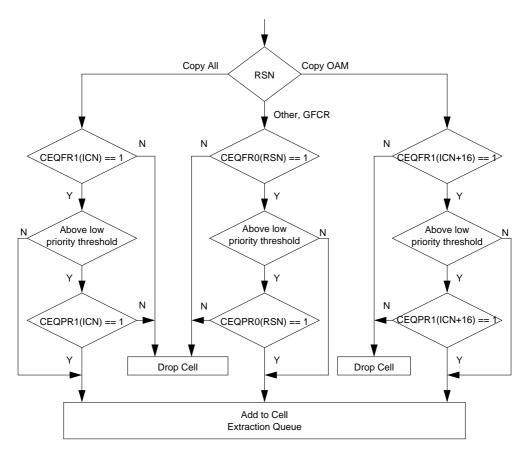

| 3.2.3.2.1           | Cell Extraction Queue                          |                |

| 3.2.3.2.2           | Cell Extraction Registers                      |                |

| 3.3                 | PHY-Side Interface Operation                   |                |

| 3.3.1               | PHY-Side Interface Considerations              |                |

| 3.3.1.1             | Multiple PHY Devices                           |                |

| 3.3.1.2             | Per-PHY FIFOs                                  |                |

| 3.3.1.3             | Total Cell FIFO Depth                          |                |

| 3.3.1.4             | Head-Of-Line Blocking                          |                |

| 3.3.2               | PHY-Side Interface Configuration Options       |                |

| 3.3.2.1             | Single- and Multi-PHY Support                  | 3-21           |

| Paragraph<br>Number | Title                                                              | Page<br>Number |

|---------------------|--------------------------------------------------------------------|----------------|

| 3.3.2.1.1           | Single-PHY Configuration                                           | 3-21           |

| 3.3.2.1.2           | Multi-PHY Configuration                                            | 3-22           |

| 3.3.2.1.3           | Multi-PHY Operation                                                |                |

| 3.3.2.2             | Single- and Multi-FIFO Support                                     | 3-23           |

| 3.3.2.2.1           | Single-FIFO Configuration                                          | 3-23           |

| 3.3.2.2.2           | Multi-FIFO Configuration                                           | 3-24           |

| 3.3.2.2.3           | Guidelines                                                         | 3-24           |

| 3.3.2.3             | HOL Blocking Detection and Prevention                              | 3-24           |

| 3.3.2.3.1           | Configuration                                                      | 3-25           |

| 3.3.2.3.2           | Operation                                                          |                |

| 3.3.2.3.3           | Guidelines                                                         | 3-26           |

| 3.4                 | Switch-Side Interface Operation                                    | 3-26           |

| 3.4.1               | Switch-Side Interface Considerations                               | 3-26           |

| 3.4.1.1             | Cell Scheduling                                                    | 3-26           |

| 3.4.1.2             | Supporting a Multi-PHY Interface on the Switch-Side                | 3-27           |

| 3.4.1.3             | Failure Detection and Recovery                                     |                |

| 3.4.2               | Switch-Side Interface Configuration Options                        |                |

| 3.4.2.1             | Switch-Side Single-PHY Interface Support                           | 3-29           |

| 3.4.2.1.1           | Configuration                                                      | 3-29           |

| 3.4.2.1.2           | Guidelines                                                         | 3-29           |

| 3.4.2.2             | Switch-Side Multi-PHY Interface Support                            | 3-29           |

| 3.4.2.2.1           | Configuration                                                      | 3-30           |

| 3.4.2.2.2           | Operation                                                          | 3-31           |

| 3.4.2.2.3           | Egress FIFO Depth                                                  | 3-32           |

| 3.4.2.2.4           | Guidelines                                                         |                |

|                     | Chapter 4                                                          |                |

|                     | External Interfaces                                                |                |

| 4.1                 | Clocks and Reset                                                   | 4-1            |

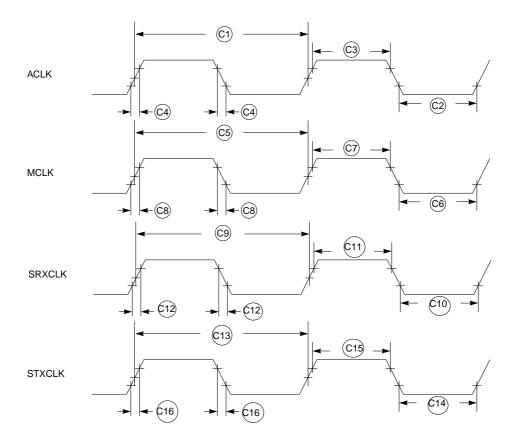

| 4.1.1               | Clocks                                                             |                |

| 4.1.1.1             | Datapath Clocks (ACLK, SRXCLK, and STXCLK)                         |                |

| 4.1.1.2             | External Memory and Cell Processing Clocks (ZCLKO, ZCl ZCLKIN) 4-2 | LKO_2, and     |

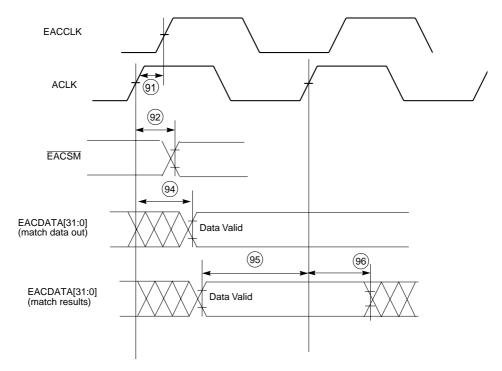

| 4.1.1.3             | External Address Compression Clock (EACCLK)                        | 4-3            |

| 4.1.1.4             | Microprocessor Clock (MCLK)                                        | 4-4            |

| 4.1.2               | Reset                                                              | 4-4            |

| 4.2                 | PHY Interfaces                                                     |                |

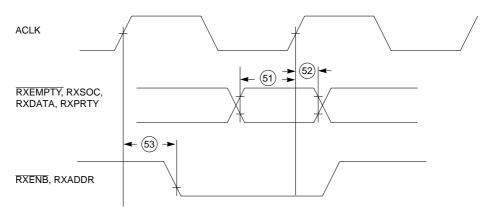

| 4.2.1               | Single-PHY Receive Interface (Ingress)                             |                |

| 4.2.1.1             | Octet- or Word-Level Handshake                                     | 4-7            |

| 4.2.1.2             | Cell-Level Handshake                                               | 4-8            |

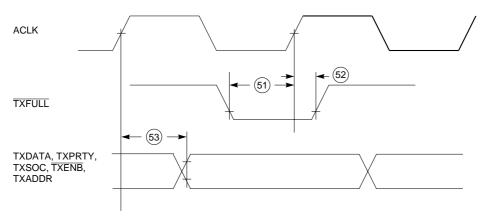

| 4.2.2               | Single-PHY Transmit Interface (Egress)                             | 4-10           |

| Paragraph<br>Number | Title                                         | Page<br>Number |

|---------------------|-----------------------------------------------|----------------|

| 4.2.2.1             | Octet/Word-Level Handshake                    |                |

| 4.2.2.2             | Cell-Level Handshake                          |                |

| 4.2.3               | Multi-PHY Receive Interface (Ingress)         | 4-14           |

| 4.2.4               | Multi-PHY Transmit Interface (Egress)         | 4-17           |

| 4.3                 | Switch Interface                              |                |

| 4.3.1               | Receive Interface (Ingress)                   | 4-20           |

| 4.3.2               | Transmit Interface (Egress)                   |                |

| 4.3.2.1             | Single-PHY Interface                          | 4-23           |

| 4.3.2.2             | Multi-PHY Interface                           | 4-24           |

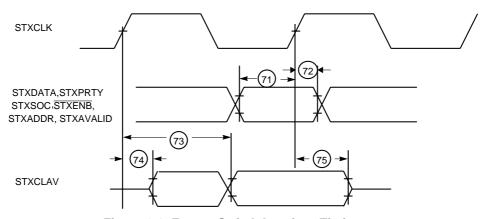

| 4.4                 | External Memory Interface                     | 4-26           |

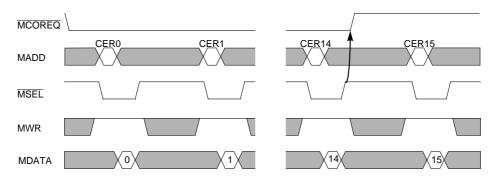

| 4.4.1               | EM Chip Enables                               | 4-26           |

| 4.4.2               | EM Interface                                  |                |

| 4.4.3               | External Address Compression Device Interface | 4-27           |

| 4.5                 | Microprocessor Interface                      |                |

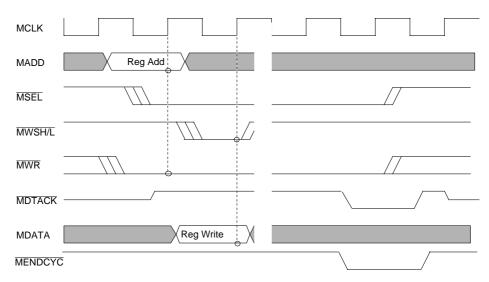

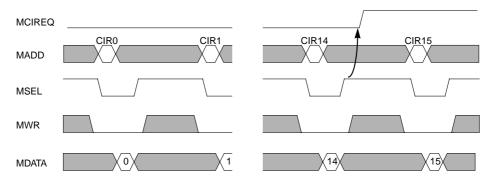

| 4.5.1               | Processor Read and Write Operations           | 4-28           |

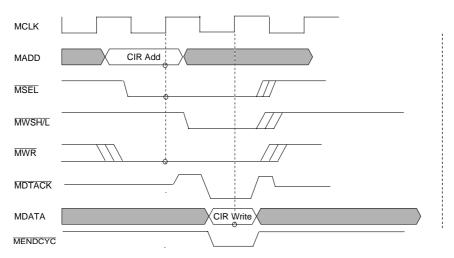

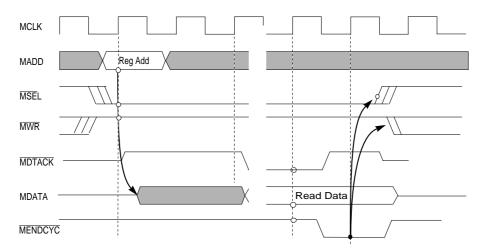

| 4.5.1.1             | Processor Read Operations                     | 4-29           |

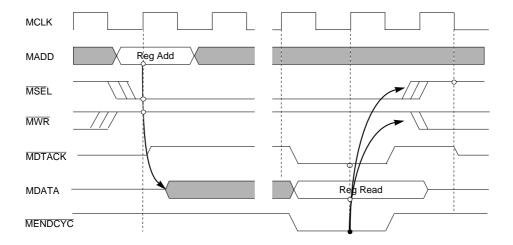

| 4.5.1.1.1           | General Register Read                         | 4-30           |

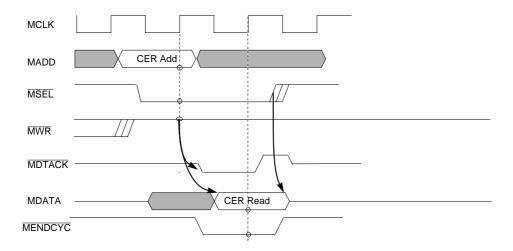

| 4.5.1.1.2           | Cell Extraction Register Read                 | 4-30           |

| 4.5.1.2             | Processor Write Operations                    | 4-31           |

| 4.5.1.2.1           | General Register Write                        | 4-31           |

| 4.5.1.2.2           | Cell Insertion Register Write                 | 4-32           |

| 4.5.1.3             | Use of MENDCYC in Processor Operations        | 4-33           |

| 4.5.2               | DMA Device Support                            | 4-34           |

| 4.5.2.1             | Cell Extraction with DMA Support              | 4-34           |

| 4.5.2.2             | Cell Insertion with DMA Support               | 4-35           |

|                     | Chapter 5 Data Path Operation                 |                |

| 5.1                 | Ingress Data Path Operation                   | 5_1            |

| 5.1.1               | Assembling Cells                              |                |

| 5.1.2               | Compressing Addresses                         |                |

| 5.1.2.1             | Address Compression Options                   |                |

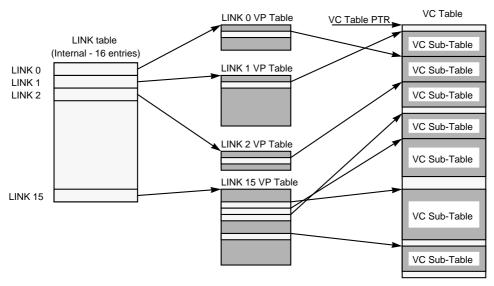

| 5.1.2.2             | VPI/VCI Table Lookup                          |                |

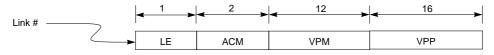

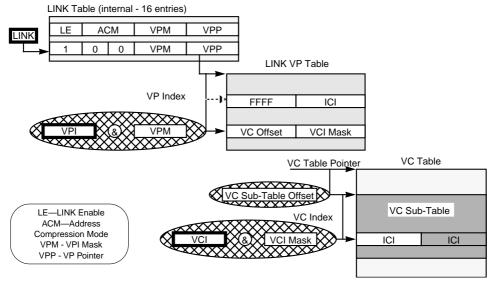

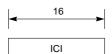

| 5.1.2.2.1           | Link Table                                    |                |

| 5.1.2.2.2           | VP Table                                      |                |

| 5.1.2.2.3           | VC Table                                      |                |

| 5.1.2.3             | VPI-only Table Lookup                         |                |

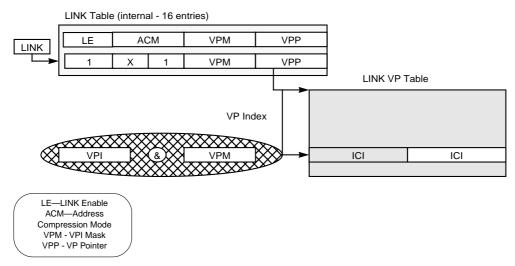

| 5.1.2.4             | External Address Compression                  |                |

| 5.1.2.4.1           | EAC Write Structure                           |                |

| 5.1.2.4.2           | EAC Read Structure                            |                |

| 5.1.2.4.3           | External Address Compression with VPI Lookup  |                |

| Paragraph<br>Number | Title                                          | Page<br>Number |

|---------------------|------------------------------------------------|----------------|

| 5.1.2.4.4           | VPI Lookup Disable                             | 5-12           |

| 5.1.3               | Performing Context Table Lookups               | 5-12           |

| 5.1.4               | Incrementing Connection and Link Cell Counters | 5-12           |

| 5.1.5               | Performing UPC/NPC Processing                  |                |

| 5.1.6               | Inserting Cells in the Ingress Flow            | 5-13           |

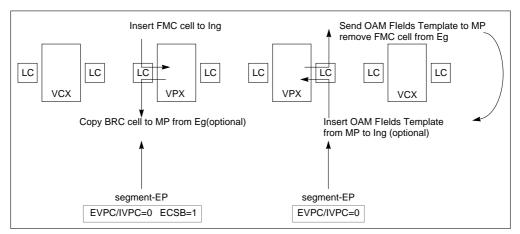

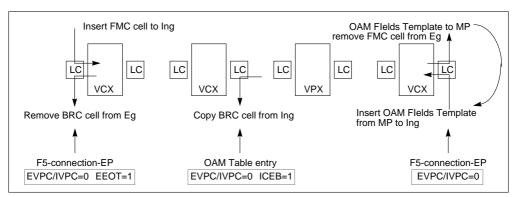

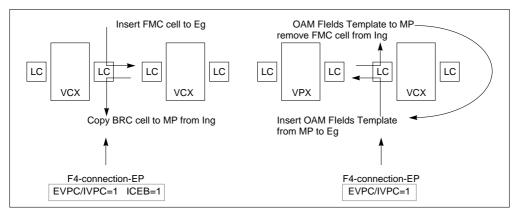

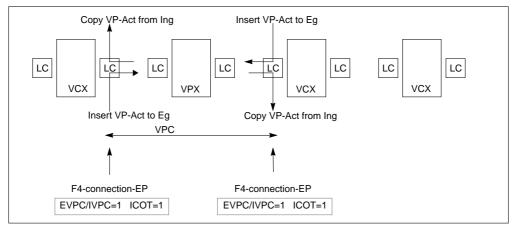

| 5.1.7               | OAM Processing                                 | 5-14           |

| 5.1.8               | Adding Switch Overhead Information             | 5-15           |

| 5.1.9               | Performing Address Translation                 | 5-18           |

| 5.1.10              | Transferring Cells to the Switch               | 5-18           |

| 5.2                 | Egress Data Path Operation                     | 5-19           |

| 5.2.1               | Transferring Cells from the Switch             |                |

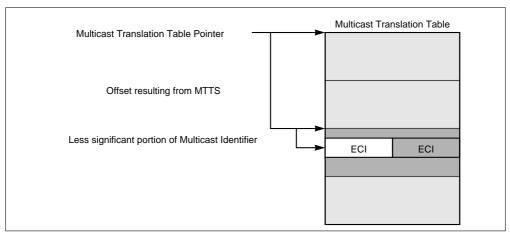

| 5.2.2               | Multicast Identifier Translation               |                |

| 5.2.3               | Inserting Cells into the Egress Flow           | 5-27           |

| 5.2.4               | Performing Context Table Lookups               | 5-28           |

| 5.2.5               | Performing UPC/NPC Processing                  | 5-29           |

| 5.2.6               | Performing OAM Processing                      | 5-29           |

| 5.2.7               | Translating Addresses                          |                |

| 5.2.8               | Incrementing Connection and Cell Counters      | 5-30           |

| 5.2.9               | Transmitting Cells to the Physical Layer       | 5-30           |

|                     | Chapter 6 Protocol Support                     |                |

| 6.1                 | Traditional UPC/NPC Support                    | 6-1            |

| 6.1.1               | Cell-Based UPC                                 |                |

| 6.1.2               | Packet-Based UPC                               |                |

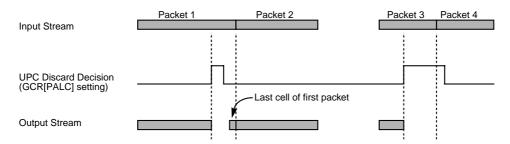

| 6.1.2.1             | Partial Packet Discard (PPD)                   | 6-3            |

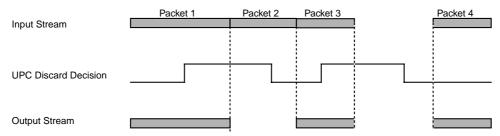

| 6.1.2.2             | Early Packet Discard (EPD)                     |                |

| 6.1.2.3             | Limited Early Packet Discard (Limited EPD)     |                |

| 6.1.3               | Selective Discard Support                      | 6-6            |

| 6.2                 | CLP Bit Management and Transparency Support    | 6-6            |

| 6.2.1               | CLP Bit Management for Simple Switch Fabrics   |                |

| 6.2.2               | CLP Bit Management for Frame-Based Connections | 6-9            |

| 6.3                 | Guaranteed Frame Rate (GFR) Support            | 6-11           |

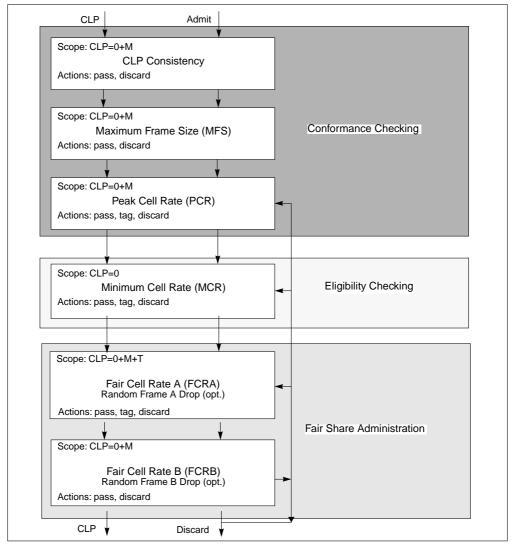

| 6.3.1               | GFR Policing and Fair Share Administration     | 6-12           |

| 6.3.1.1             | Global GFR Configurations                      | 6-14           |

| 6.3.1.2             | Cell Loss Priority (CLP) Consistency           | 6-15           |

| 6.3.1.3             | Maximum Frame Size (MFS)                       |                |

| 6.3.1.4             | Peak Cell Rate (PCR)                           | 6-16           |

| 6.3.1.5             | Minimum Cell Rate (MCR)                        |                |

| 6.3.1.6             | Fair Cell Rate (FCR)                           | 6-18           |

| 6.3.1.7             | FCR Administration                             | 6-19           |

| Paragraph<br>Number | Title                                                   | Page<br>Number |

|---------------------|---------------------------------------------------------|----------------|

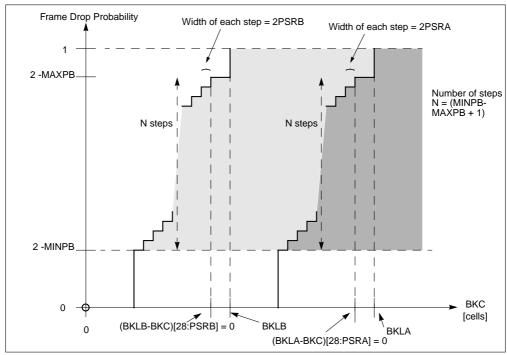

| 6.3.1.8             | Congestion Avoidance Through Random Frame Drop (RFD)    | 6-20           |

| 6.3.1.8.1           | GFR and TCP/IP Congestion                               | 6-21           |

| 6.3.1.8.2           | RFD Configuration Overview                              |                |

| 6.3.1.8.3           | Configuration of RFD Probability Function Limits        |                |

| 6.3.1.8.4           | Configuration of the RFD Probability Function           |                |

| 6.3.1.8.5           | Understanding RFD from the Implementation Standpoint    | 6-23           |

| 6.3.2               | GFR Configuration Examples                              | 6-24           |

| 6.3.2.1             | GFR Conformance and Eligibility Filter                  | 6-24           |

| 6.3.2.2             | GFR Support for a Switch Fabric That is Not Frame-Aware |                |

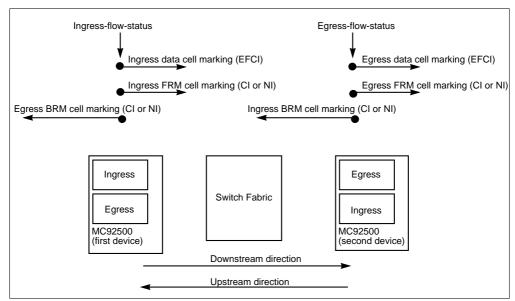

| 6.4                 | Available Bit-Rate Support                              |                |

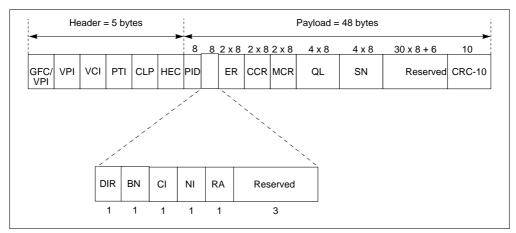

| 6.4.1               | Resource Management (RM) Cell Definition                | 6-31           |

| 6.4.2               | Cell Marking (CI, NI, PTI)                              | 6-33           |

| 6.4.2.1             | Sources for Ingress Flow Status                         |                |

| 6.4.2.2             | Sources for Egress Flow Status                          |                |

| 6.4.2.3             | MC92520 Actions in the Ingress Direction                |                |

| 6.4.2.4             | MC92520 Actions in the Egress Direction                 |                |

| 6.4.2.5             | Cell Marking Examples                                   |                |

| 6.4.3               | Ingress Switch Parameters Hooks                         |                |

| 6.4.4               | Egress Reset EFCI                                       |                |

| 6.5                 | Operations and Maintenance (OAM) Support                |                |

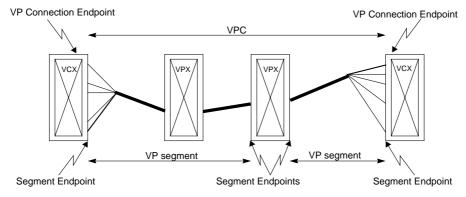

| 6.5.1               | General Concepts and Definitions                        |                |

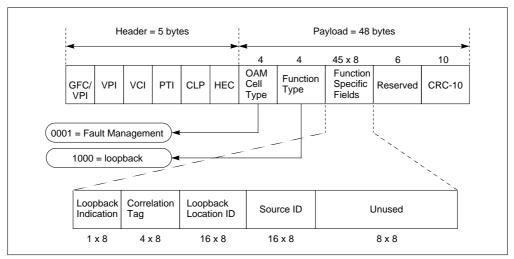

| 6.5.1.1             | OAM Cell Header Definition                              |                |

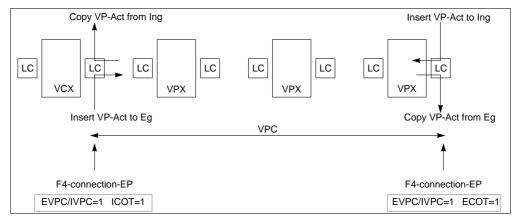

| 6.5.1.2             | Virtual Path (F4) Flow Mechanism                        | 6-47           |

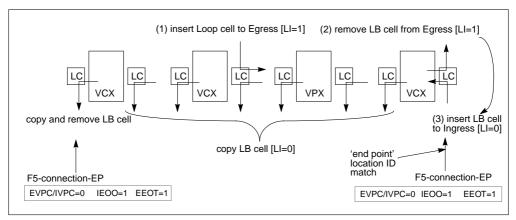

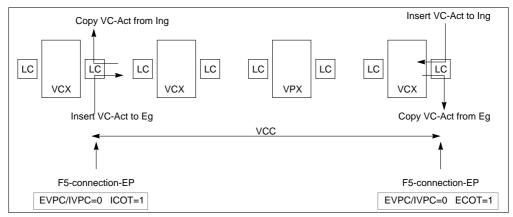

| 6.5.1.3             | Virtual Channel (F5) Flow Mechanism                     |                |

| 6.5.1.4             | OAM Cell and Function Types                             |                |

| 6.5.2               | Internal Scan                                           | 6-48           |

| 6.5.3               | Generic OAM Support                                     |                |

| 6.5.3.1             | Illegal OAM Cells                                       |                |

| 6.5.3.2             | Other OAM Cells                                         | 6-51           |

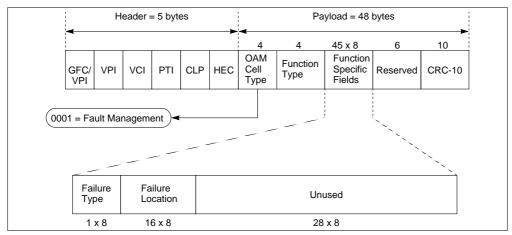

| 6.5.4               | Fault Management                                        | 6-51           |

| 6.5.4.1             | Alarm Surveillance                                      | 6-51           |

| 6.5.4.1.1           | Alarm Indication Signal Cells                           | 6-52           |

| 6.5.4.1.2           | Remote Defect Indicator Cells                           |                |

| 6.5.4.1.3           | Continuity Check Cells                                  |                |

| 6.5.4.2             | Failure Localization and Testing                        | 6-58           |

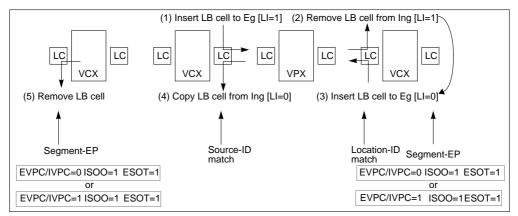

| 6.5.4.2.1           | Loopback Cell Format                                    |                |

| 6.5.4.2.2           | Loopback Cell Processing                                |                |

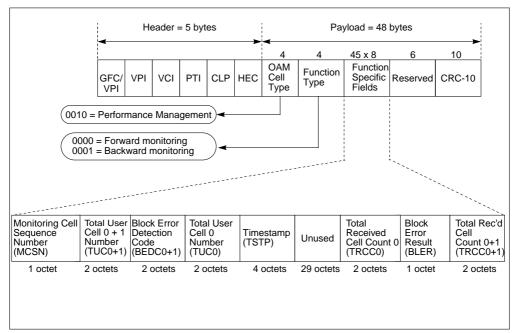

| 6.5.5               | Performance Management                                  |                |

| 6.5.5.1             | Performance Management Cell Format                      |                |

| 6.5.6               | Performance Monitoring                                  |                |

| 6.5.7               | Activation/Deactivation OAM Cells                       |                |

**Paragraph** Page Title Number Number Chapter 7 **Programming Model** 7.1 7.1.1 7.1.1.1 7.1.1.2 7.1.2 7.1.2.1 7.1.3 7.1.4 Status Reporting Registers 7-7 7.1.4.1 7.1.4.1.1 7.1.4.2 7.1.4.3 7.1.4.4 External Memory Maintenance Slot Read Access Result (EMRSLT)..... 7-13 7.1.4.5 7.1.4.6 7.1.4.7 7.1.4.8 7.1.5 7.1.5.1 7.1.5.2 7.1.5.3 7.1.5.4 7.1.5.5 7.1.5.6 7.1.5.7 7.1.5.8 7.1.5.9 7.1.5.10 7.1.5.11 7.1.5.12 7.1.5.13 7.1.5.14 7.1.5.15 7.1.5.16 Egress Billing Counters Table Pointer Register (EBCTP)...... 7-24 7.1.5.17 7.1.5.18 7.1.5.19 7.1.5.20 7.1.5.21 7.1.5.22

| Paragraph<br>Number | Title                                                        | Page<br>Number |

|---------------------|--------------------------------------------------------------|----------------|

| 7.1.5.23            | Indirect External Memory Access Data Register (IADR)         |                |

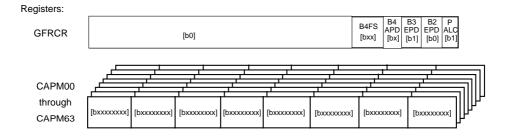

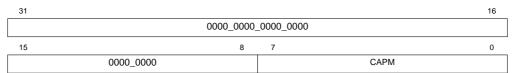

| 7.1.5.24            | Cell Arrival Period Multiplier Registers 0 - 63 (CAPMnn)     |                |

| 7.1.6               | Configuration Registers                                      |                |

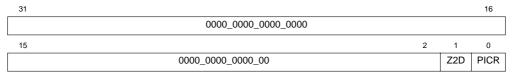

| 7.1.6.1             | PLL Range Register (PLLRR)                                   |                |

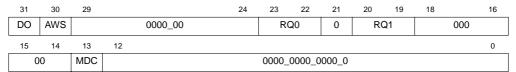

| 7.1.6.2             | Microprocessor Configuration Register (MPCONR)               |                |

| 7.1.6.3             | Ingress PHY Configuration Register (IPHCR)                   | 7-29           |

| 7.1.6.4             | Egress PHY Configuration Register (EPHCR)                    |                |

| 7.1.6.5             | Ingress Switch Interface Configuration Register (ISWCR)      |                |

| 7.1.6.6             | Egress Switch Interface Configuration Register (ESWCR)       |                |

| 7.1.6.7             | Egress Switch Interface Configuration Register 1 (ESWCR1)    |                |

| 7.1.6.8             | Egress Switch Overhead Information Register 0 (ESOIR0)       |                |

| 7.1.6.9             | Egress Switch Overhead Information Register 1 (ESOIR1)       |                |

| 7.1.6.10            | UNI Register (UNIR)                                          |                |

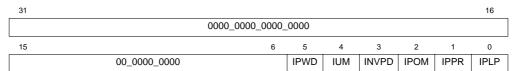

| 7.1.6.11            | Ingress Processing Configuration Register (IPCR)             |                |

| 7.1.6.12            | Egress Processing Configuration Register (EPCR)              |                |

| 7.1.6.13            | Egress Multicast Configuration Register (EMCR)               |                |

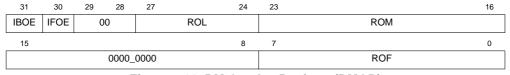

| 7.1.6.14            | ATMC CFB Configuration Register (ACR)                        |                |

| 7.1.6.15            | General Configuration Register (GCR)                         |                |

| 7.1.6.16            | Context Parameters Table Pointer Register (CPTP)             |                |

| 7.1.6.17            | OAM Table Pointer Register (OTP)                             |                |

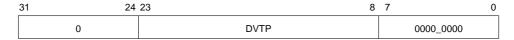

| 7.1.6.18            | Dump Vector Table Pointer Register (DVTP)                    |                |

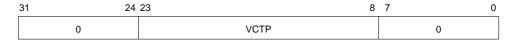

| 7.1.6.19            | VC Table Pointer Register (VCTP)                             |                |

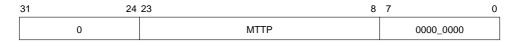

| 7.1.6.20            | Multicast Translation Table Pointer Register (MTTP)          |                |

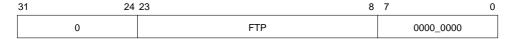

| 7.1.6.21            | Flags Table Pointer Register (FTP)                           |                |

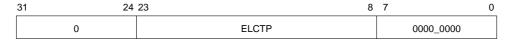

| 7.1.6.22            | Egress Link Counters Table Pointer Register (ELCTP)          |                |

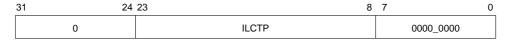

| 7.1.6.23            | Ingress Link Counters Table Pointer Register (ILCTP)         |                |

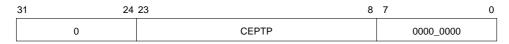

| 7.1.6.24            | Context Parameters Extension Table Pointer Register (CPETP). |                |

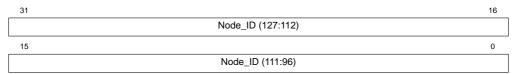

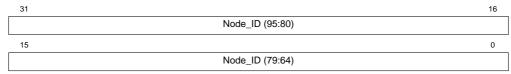

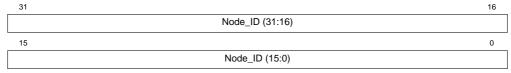

| 7.1.6.25            | Node ID Register 0 (ND0)                                     |                |

| 7.1.6.26            | Node ID Register 1 (ND1)                                     |                |

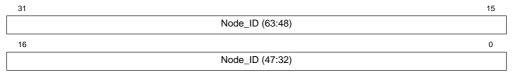

| 7.1.6.27            | Node ID Register 2 (ND2)                                     |                |

| 7.1.6.28            | Node ID Register 3 (ND3)                                     |                |

| 7.1.6.29            | Ingress VCI Copy Register (IVCR)                             |                |

| 7.1.6.30            | Egress VCI Copy Register (EVCR)                              |                |

| 7.1.6.31            | Ingress VCI Remove Register (IVRR)                           |                |

| 7.1.6.32            | Egress VCI Remove Register (EVRR)                            |                |

| 7.1.6.33            | Performance Monitoring Exclusion Register (PMER)             |                |

| 7.1.6.34            | RM Overlay Register (RMOR)                                   |                |

| 7.1.6.35            | CLP Transparency Overlay Register (CTOR)                     |                |

| 7.1.6.36            | Egress Overhead Manipulation Register (EGOMR)                |                |

| 7.1.6.37            | GFR Configuration Register (GFRCR)                           |                |

| 7.1.7               | Pseudo-Registers                                             |                |

| 7.1.7.1             | Software Reset Register (SRR)                                |                |

| 7.1.7.2             | Start Scan Register (SSR)                                    | /-56           |

| Paragraph<br>Number | Title                                                | Page<br>Number |

|---------------------|------------------------------------------------------|----------------|

| 7.1.7.3             | Enter Operate Mode Register (EOMR)                   |                |

| 7.1.8               | External Memory Accesses                             | 7-56           |

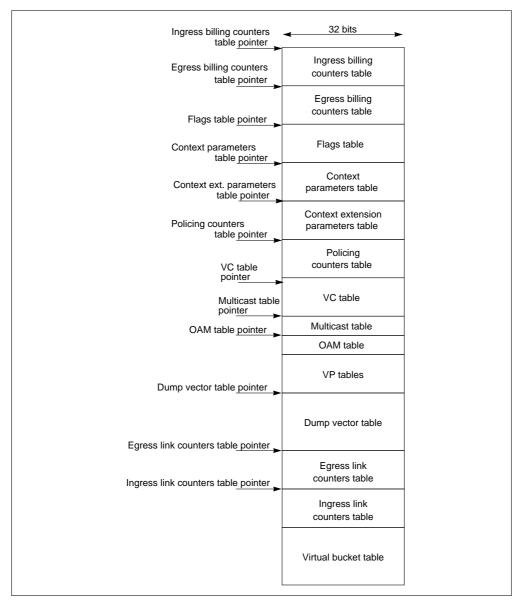

| 7.2                 | External Memory Description                          | 7-57           |

| 7.2.1               | Memory Partitioning                                  | 7-57           |

| 7.2.2               | Memory Allocation                                    | 7-61           |

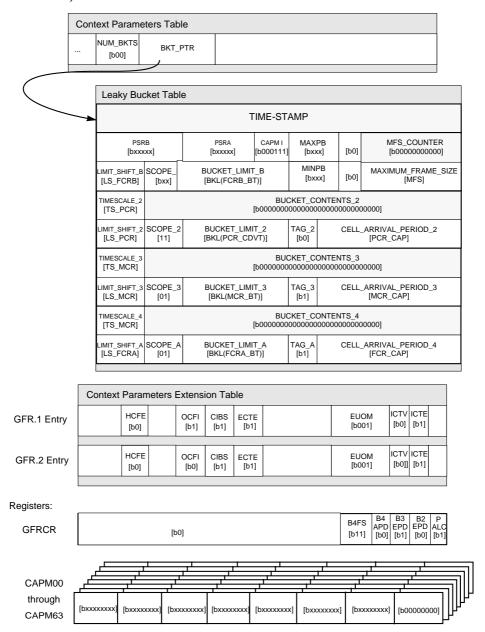

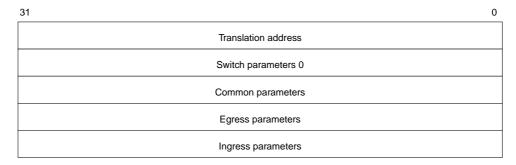

| 7.2.3               | Context Parameters Table                             | 7-64           |

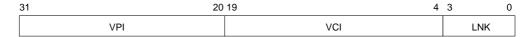

| 7.2.3.1             | Egress Translation Address                           | 7-65           |

| 7.2.3.2             | Ingress Translation Address                          | 7-65           |

| 7.2.3.3             | Switch Parameters                                    | 7-66           |

| 7.2.3.4             | Common Parameters                                    | 7-66           |

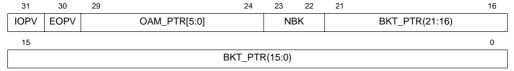

| 7.2.3.5             | Egress Parameters                                    | 7-67           |

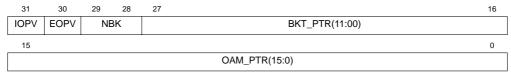

| 7.2.3.6             | Ingress Parameters                                   | 7-69           |

| 7.2.4               | Ingress Billing Counters Table                       | 7-71           |

| 7.2.5               | Egress Billing Counters Table                        | 7-73           |

| 7.2.6               | Policing Counters Table                              | 7-76           |

| 7.2.7               | Flags Table                                          | 7-77           |

| 7.2.8               | VP Table                                             | 7-79           |

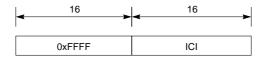

| 7.2.8.1             | VP Table Record without VC Table Lookup              | 7-79           |

| 7.2.8.2             | VP Table Record with VC Table Lookup                 | 7-79           |

| 7.2.9               | VC Table                                             |                |

| 7.2.10              | Multicast Translation Table                          | 7-81           |

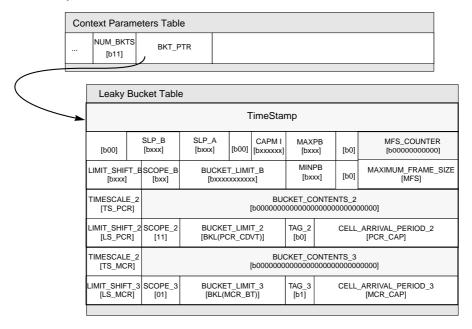

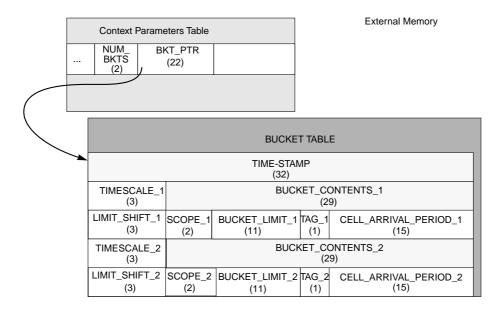

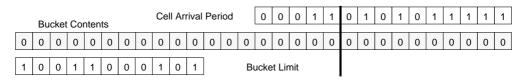

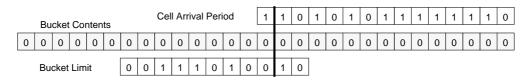

| 7.2.11              | Buckets Record                                       |                |

| 7.2.11.1            | Bucket Entries for One Connection                    | 7-82           |

| 7.2.11.2            | Bucket Information                                   | 7-82           |

| 7.2.11.2.1          | GFR Policing Not Selected                            | 7-82           |

| 7.2.11.2.2          | GFR Policing Selected                                | 7-83           |

| 7.2.12              | OAM Table                                            | 7-86           |

| 7.2.13              | Dump Vector Table                                    | 7-88           |

| 7.2.14              | Ingress Link Counters Table                          | 7-90           |

| 7.2.15              | Egress Link Counters Table                           | 7-90           |

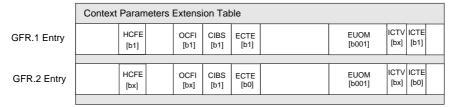

| 7.2.16              | Context Parameters Extension Table                   | 7-91           |

| 7.3                 | Data Structures                                      | 7-97           |

| 7.3.1               | Inserted Cell Structure                              | 7-97           |

| 7.3.1.1             | Cell Descriptor                                      | 7-98           |

| 7.3.1.2             | Connection Descriptor                                | 7-100          |

| 7.3.1.3             | ATM Cell Header                                      | 7-101          |

| 7.3.1.4             | Inserted OAM Fields Template                         |                |

| 7.3.2               | Extracted Cell Structure                             | 7-103          |

| 7.3.2.1             | Cell Indication                                      |                |

| 7.3.2.1.1           | User/OAM Cell Indication                             |                |

| 7.3.2.1.2           | Egress Multicast Translation Failure Cell Indication |                |

| 7.3.2.1.3           | Error Cell Indication                                | 7-105          |

| 7.3.2.1.4           | Short Report Indication                              | 7-106          |

| Paragraph<br>Number | Title                                                                   | Page<br>Number |

|---------------------|-------------------------------------------------------------------------|----------------|

| 7.3.2.1.5           | OAM Fields Template Indication                                          | 7-106          |

| 7.3.2.2             | Connection Indication                                                   | 7-107          |

| 7.3.2.3             | Time-Stamp                                                              | 7-108          |

| 7.3.2.4             | ATM Cell Header                                                         | 7-108          |

| 7.3.2.5             | Extracted OAM Fields Template                                           | 7-109          |

| 7.3.3               | General Fields                                                          | 7-110          |

| 7.3.3.1             | Cell Name Field                                                         | 7-110          |

| 7.3.3.2             | Reason Field                                                            | 7-110          |

|                     | Chapter 8 Test Operation                                                |                |

|                     |                                                                         |                |

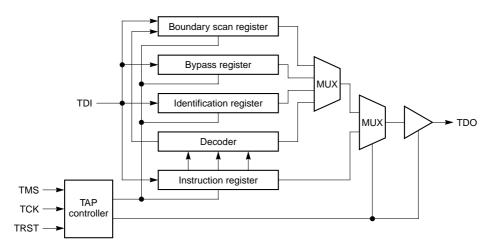

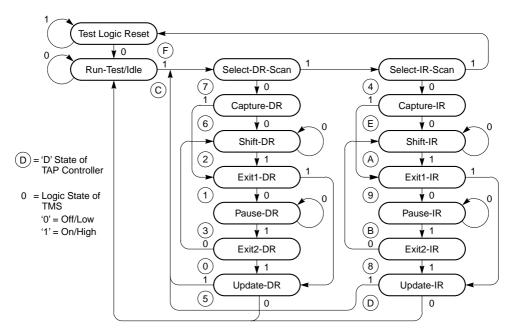

| 8.1                 | JTAG Overview                                                           | 8-1            |

| 8.1.1               | Functional Blocks                                                       | 8-2            |

| 8.1.1.1             | TAP Controller                                                          | 8-2            |

| 8.1.1.2             | Instruction Register                                                    | 8-3            |

| 8.1.1.3             | Device Identification Register                                          | 8-3            |

| 8.1.1.4             | Bypass Register                                                         | 8-4            |

| 8.1.1.5             | Boundary Scan Register                                                  | 8-4            |

| 8.1.2               | JTAG Instruction Support                                                | 8-4            |

| 8.1.3               | Boundary Scan Register Path                                             | 8-5            |

|                     | Chapter 9 Product Specifications                                        |                |

| 0.1                 |                                                                         | 0.1            |

| 9.1                 | Introduction                                                            |                |

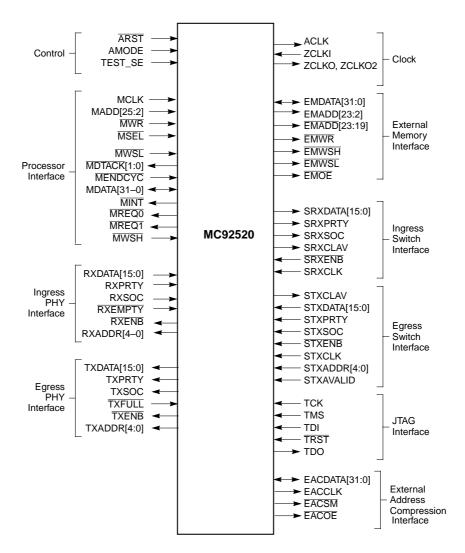

| 9.2                 | Signal Description                                                      |                |

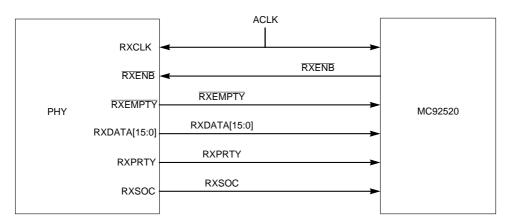

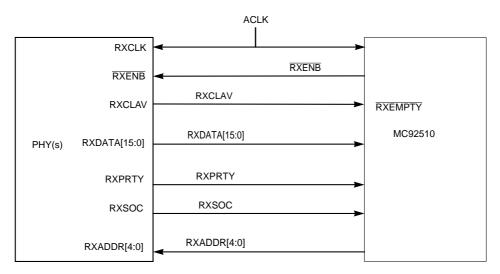

| 9.2.1               | Ingress PHY Signals                                                     |                |

| 9.2.2               | Egress PHY Signals                                                      |                |

| 9.2.3               | Ingress Switch Interface Signals                                        |                |

| 9.2.4               | Egress Switch Interface Signals                                         |                |

| 9.2.5<br>9.2.6      | External Memory Signals  External Address Compression Interface Signals |                |

| 9.2.7               | Control Signals                                                         |                |

| 9.2.7               | Microprocessor Signals (MP)                                             |                |

| 9.2.8.1             | DMA Requests                                                            |                |

| 9.2.9               | PLL Signals                                                             |                |

| 9.2.10              | Test Signals                                                            |                |

| 9.2.10              | Electrical and Physical Characteristics                                 |                |

| 9.3.1               | Recommended Operating Conditions                                        |                |

| 9.3.2               | Absolute Maximum Ratings                                                |                |

| 9.3.3               | DC Electrical Characteristics                                           |                |

| ,                   | De Licenten Characteristics                                             |                |

| Paragraph<br>Number | Title                                         | Page<br>Number |

|---------------------|-----------------------------------------------|----------------|

| 9.3.4               | Clocks                                        | 9-13           |

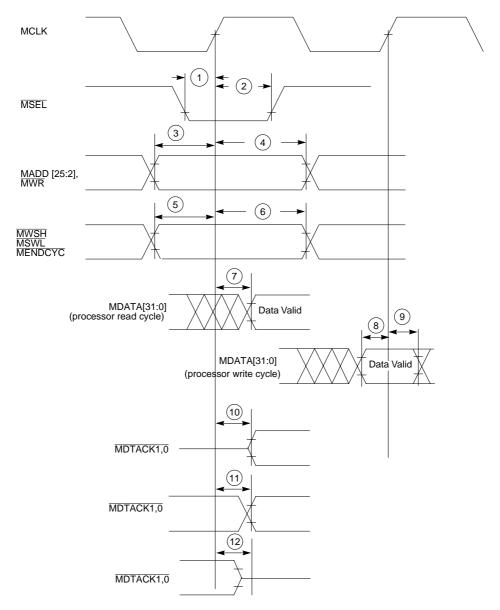

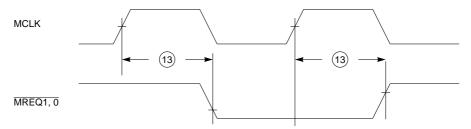

| 9.3.5               | Microprocessor Interface Timing               | 9-15           |

| 9.3.6               | PHY Interface Timing                          | 9-18           |

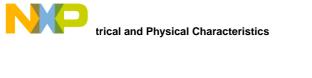

| 9.3.7               | Ingress Switch Interface Timing               | 9-19           |

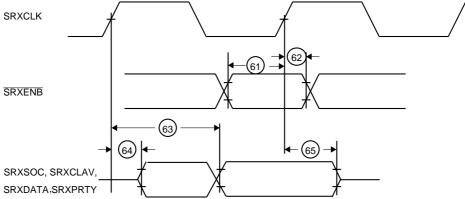

| 9.3.8               | Egress Switch Interface Timing                | 9-20           |

| 9.3.9               | External Memory Interface Timing              | 9-21           |

| 9.3.10              | External Address Compression Interface Timing | 9-23           |

| 9.4                 | Ordering Information                          | 9-24           |

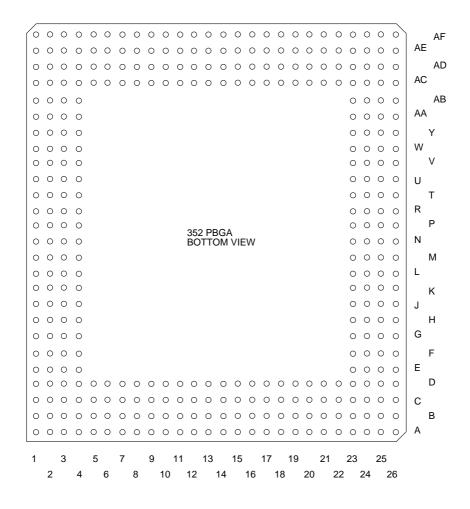

| 9.5                 | Mechanical Data                               | 9-24           |

| 9.5.1               | Pin Assignments                               | 9-25           |

| 9.5.2               | Package Dimensions                            | 9-28           |

|                     | Appendix A<br>UPC/NPC Design                  |                |

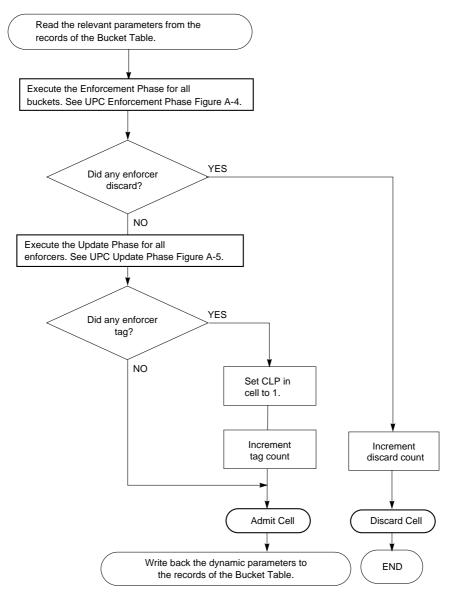

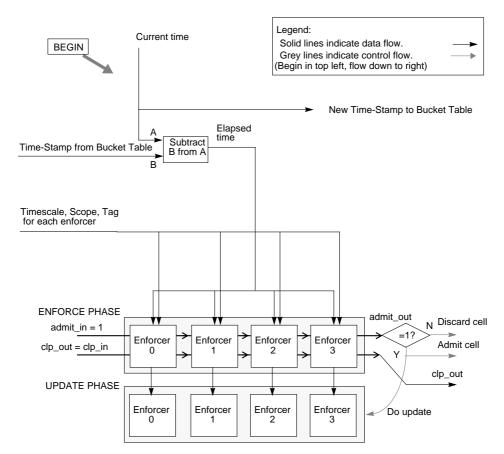

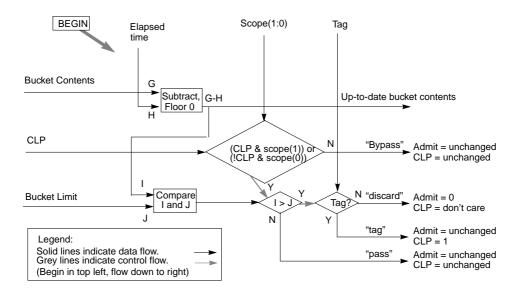

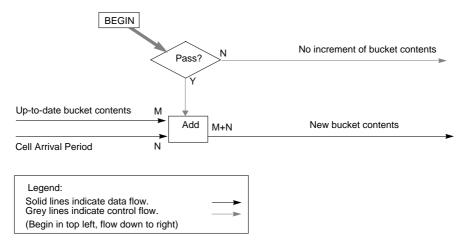

| A.1                 | Time-Stamped Leaky Time Bucket                | A-1            |

| A.2                 | Multi-Enforcer UPC/NPC                        | A-2            |

| A.3                 | Data Structure                                | A-3            |

| A.3.1               | Detailed Flowchart                            | A-4            |

| A.4                 | Control/Data Flowcharts                       | A-5            |

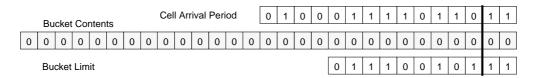

| A.5                 | Bucket Parameter Encoding                     | A-8            |

| A.5.1               | Cell Arrival Computation Example              | A-10           |

| A.5.2               | Bucket Limit Encoding                         |                |

| A.6                 | UPC Parameter Calculations                    |                |

| A.6.1               | Example A                                     | A-11           |

| A.6.2               | Example B                                     | A-12           |

| A.7                 | Bellcore Cell Relay Service Parameters        | A-13           |

|                     | Appendix B Maintenance Slot Calculations      |                |

| B.1                 | Maintenance Slot Equations                    | D 15           |

| B.2                 | Maintenance Time Slot Example 1               |                |

| B.3                 | Maintenance Time Slot Example 2               |                |

| B.4                 | Maintenance Slot Parameters                   |                |

| D. <del>4</del>     | Maintenance Slot I arameters                  | Б-10           |

|                     | Appendix C<br>VC Bundling                     |                |

| C.1                 | VP-VC Boundary                                |                |

| C.1.1               | Bundling VCs into a VP                        |                |

| C.1.2               | Separating a VP into VCs                      | C-2            |

| Paragraph<br>Number | Title                                       | Page<br>Number |

|---------------------|---------------------------------------------|----------------|

| C.2                 | F4-Level OAM Processing at a VP/VC Boundary | C-3            |

| C.3                 | Continuity Check                            |                |

| C.3.1               | OAM Block Test                              | C-3            |

| C.4                 | F5-Level OAM Processing at a VP/VC Boundary | C-3            |

| C.5                 | Reserved VCI Values                         | C-4            |

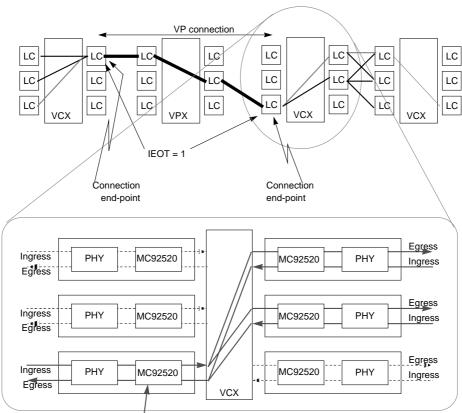

|                     | Appendix D<br>MC92520 Applications          |                |

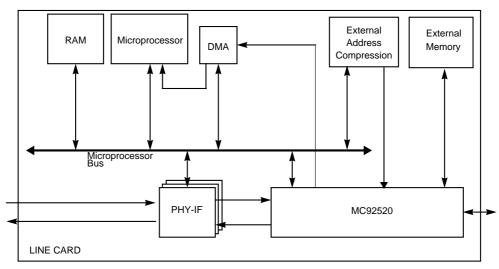

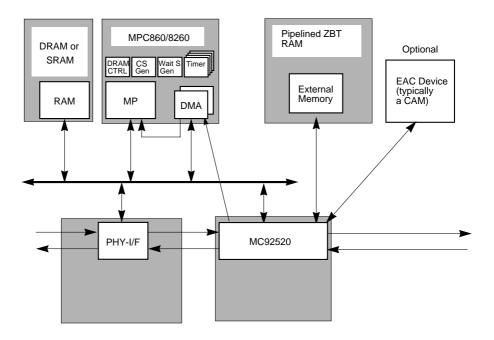

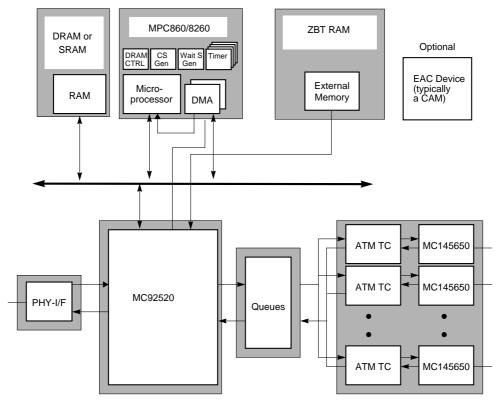

| D.1                 | Standard Architecture                       | D-1            |

| D.1.1               | MC92520/MC92510                             | D-2            |

| D.1.2               | PHY                                         | D-2            |

| D.1.3               | Line Card Microprocessor                    | D-2            |

| D.1.4               | External Memory                             |                |

| D.1.5               | External Address Compression CAM            | D-3            |

| D.1.6               | Microprocessor RAM                          |                |

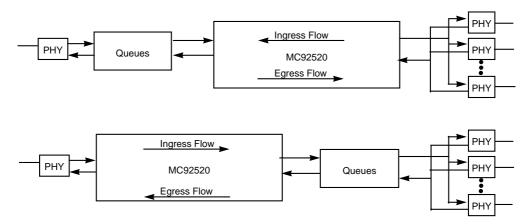

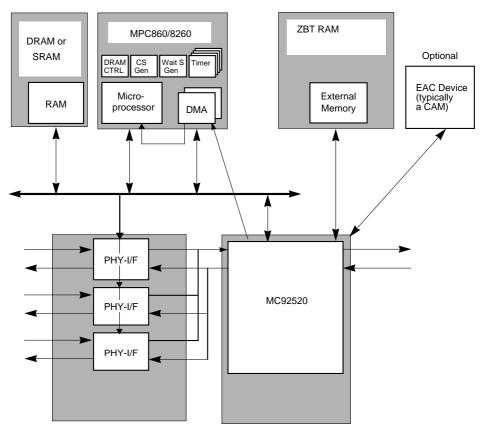

| D.2                 | Multiple PHY Architecture                   |                |

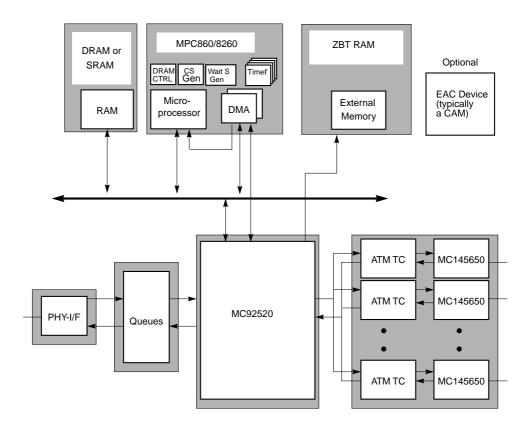

| D.3                 | DSLAM Access Network Architectures          | D-4            |

Appendix E BSDL Code

Index

| r Title                                                    | Page<br>Number                |

|------------------------------------------------------------|-------------------------------|

|                                                            |                               |

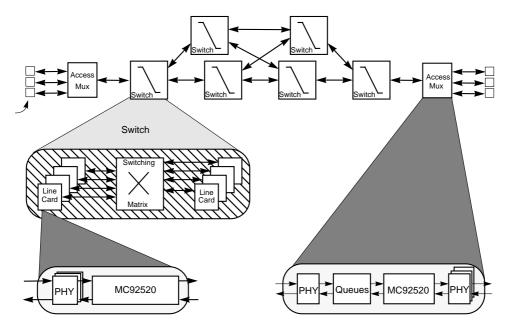

| Typical ATM Network Structure                              | 1-2                           |

| Typical ATM Line Card Application                          | 1-3                           |

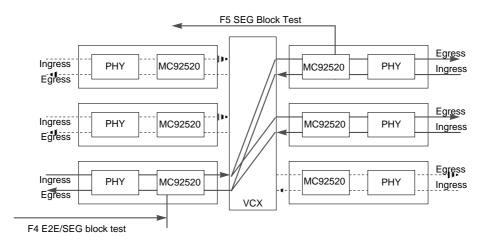

| MC92520 Network Access Multiplexer Design Examples         |                               |

| MC92520 Block Diagram                                      | 1-5                           |

| ATMC Schematic Interface                                   | 2-1                           |

| MC92520 in Operate Mode                                    | 2-2                           |

| MC92520 Block Diagram                                      | 2-5                           |

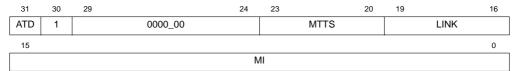

| External Memory Read Request Control Word                  | 3-9                           |

| Cell Extraction Queue                                      | 3-16                          |

| Cell Extraction Queue Filtering                            | 3-17                          |

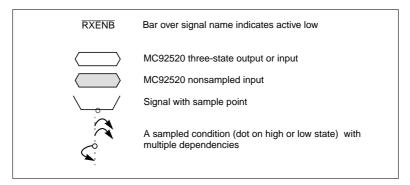

| Timing Diagram Legend                                      | 4-1                           |

| MC92520 Clock Configuration                                | 4-2                           |

| MC92520 Single-PHY Receive Interface                       | 4-6                           |

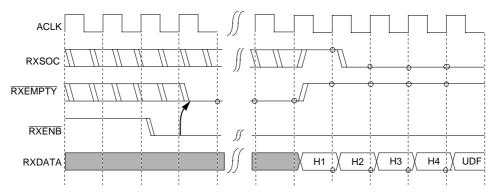

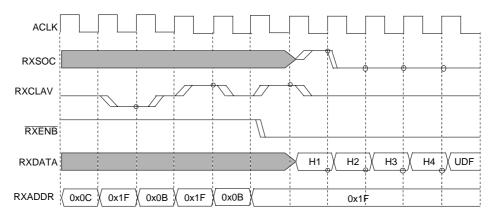

| MC92520 Receive Timing—End of Cell                         | 4-6                           |

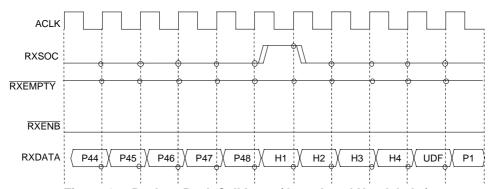

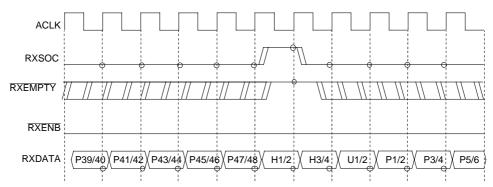

| Start of Cell—MC92520 Empty (Octet-Level Handshake)        | 4-7                           |

|                                                            |                               |

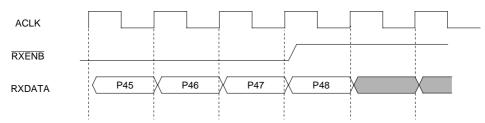

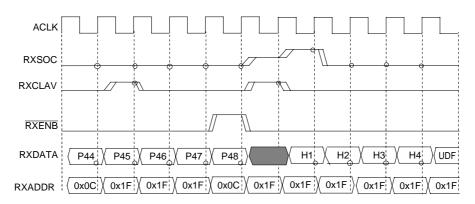

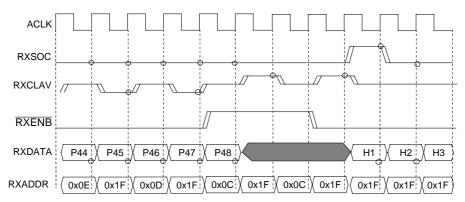

| Back-to-Back Cell Input (Octet-Level Handshake)            |                               |

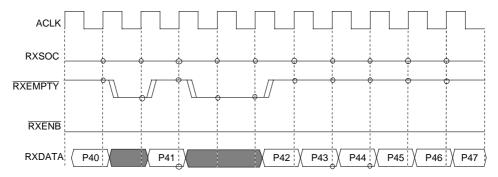

| Response to RXEMPTY Assertion (Octet-Level Handshake)      | 4-8                           |

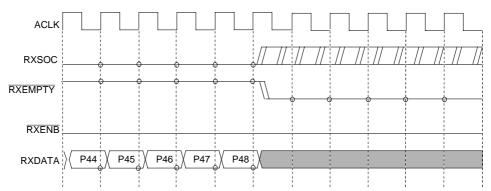

| Start of Cell—MC92520 Empty (Cell-Level Handshake)         | 4-9                           |

| End of Cell—PHY Empty (Cell-Level Handshake)               | 4-9                           |

| Back to Back Cell Input (Cell-Level Interface)             |                               |

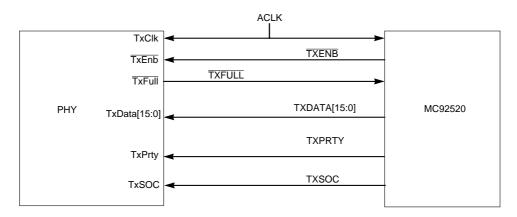

| MC92520 Single-PHY Transmit Interface                      | 4-10                          |

| MC92520 Transmit Timing—MC92520 is Empty                   | 4-11                          |

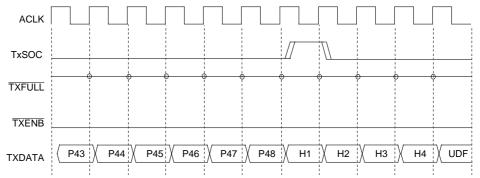

| Start of Cell (Octet-Level Handshake)                      | 4-12                          |

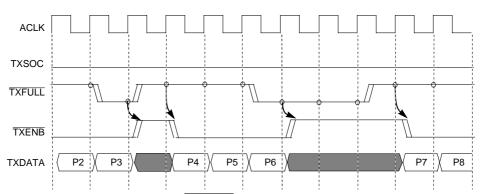

| Back-to-Back Cell Output (Octet-Level Handshake)           | 4-12                          |

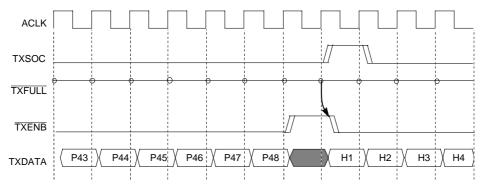

| Response to TXFULL Assertion (Octet-Level Handshake)       | 4-13                          |

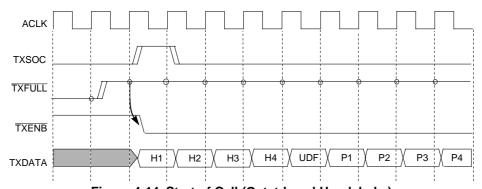

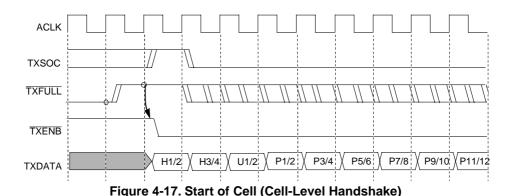

| Start of Cell (Cell-Level Handshake)                       | 4-13                          |

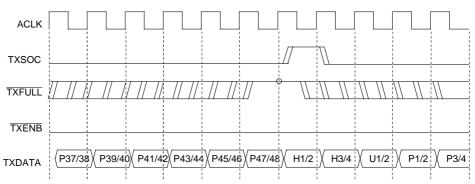

| Back-to-Back Cell Output (Cell-Level Handshake)            | 4-14                          |

| MC92520 Multi-PHY Receive Interface                        |                               |

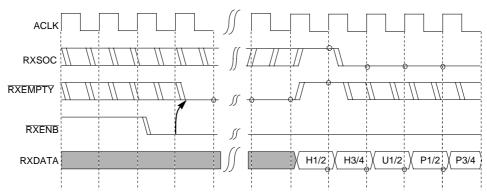

| Poll PHYs, Select PHY, and Start Reading a Cell            | 4-16                          |

| Polls the PHYs While Transferring a Cell                   | 4-16                          |

| The MC92520 Reads Cells from the Same PHY                  |                               |

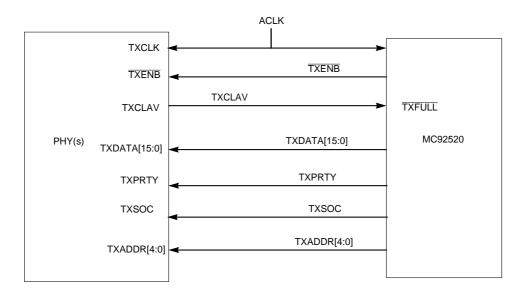

| MC92520 Multi-PHY Transmit Interface                       |                               |

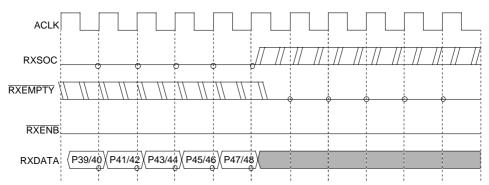

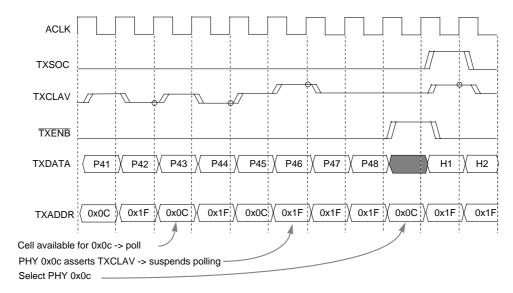

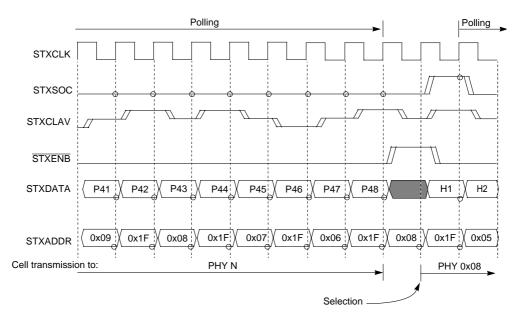

| MC92520 Transmit Timing—Single-FIFO Polling                |                               |

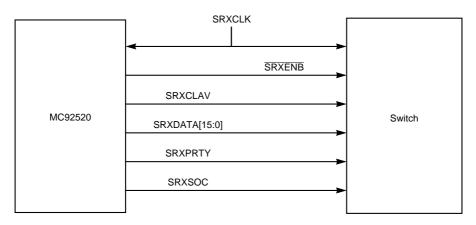

| MC92520 Switch Receive Interface                           |                               |

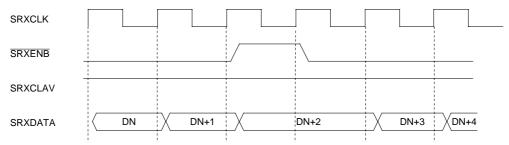

| Receive Timing without Tri-state—Effect of SRXENB Negation |                               |

|                                                            | Typical ATM Network Structure |

| Figure<br>Number | Title                                                           | Page<br>Number |

|------------------|-----------------------------------------------------------------|----------------|

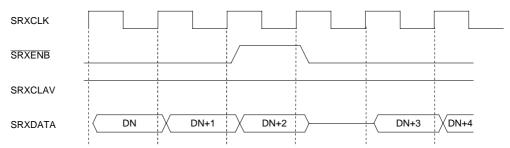

| 4-27             | Receive Timing with Tri-state—Effect of SRXENB Negation         | 4-21           |

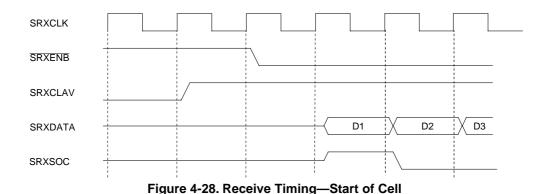

| 4-28             | Receive Timing—Start of Cell                                    |                |

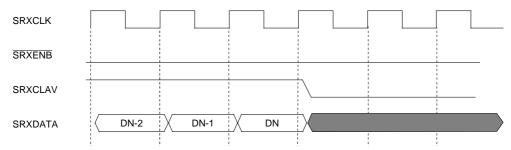

| 4-29             | Receive Timing—End of Cell                                      |                |

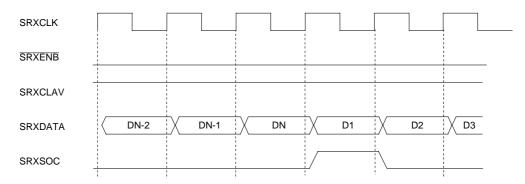

| 4-30             | Receive Timing—Back-to-Back Cell Transfers                      | 4-22           |

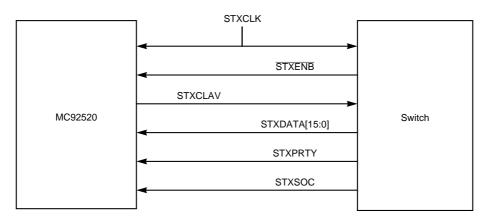

| 4-31             | MC92520 Single-PHY Switch Transmit Interface                    | 4-23           |

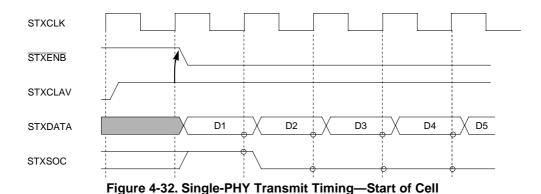

| 4-32             | Single-PHY Transmit Timing—Start of Cell                        |                |

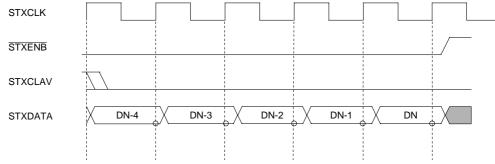

| 4-33             | Single-PHY Transmit Timing (End of Cell)                        |                |

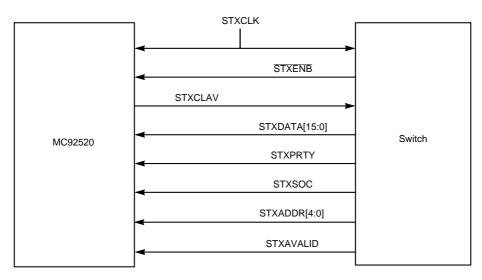

| 4-34             | MC92520 Multi-PHY Switch Transmit Interface                     |                |

| 4-35             | Polling Phase and Selection Phase                               |                |

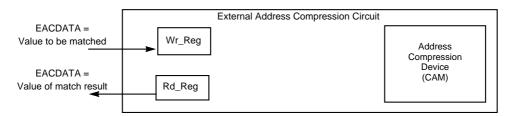

| 4-36             | Example Implementation of External Address Compression          |                |

| 4-37             | MC92520 Register Read Timing                                    |                |

| 4-38             | Cell Extraction Register Read Timing                            |                |

| 4-39             | MC92520 Register Write Timing                                   | 4-32           |

| 4-40             | Cell Insertion Register Write Timing with AWS Set               |                |

| 4-41             | MC92520 MENDCYC Extending a Processor Operation                 |                |

| 4-42             | DMA Device Support on Cell Extraction Register                  |                |

| 4-43             | DMA Device Support on Cell Insertion Register                   |                |

| 5-1              | Ingress Data Path                                               |                |

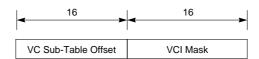

| 5-2              | Address Compression Tables                                      |                |

| 5-3              | Link Table Logical Structure                                    |                |

| 5-4              | Full Table Lookup Scheme                                        |                |

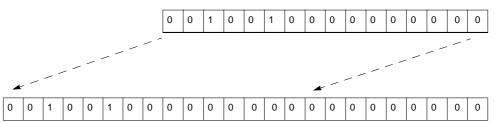

| 5-5              | Deriving Address of Link VP Table                               |                |

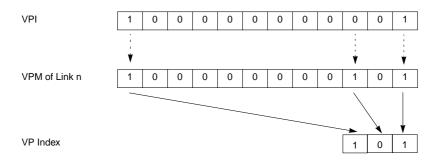

| 5-6              | Deriving the VP Index                                           |                |

| 5-7              | VP Table Record Logical Structure for VP Switching              |                |

| 5-8              | VP Table Record Logical Structure as Pointer to VC Table        |                |

| 5-9              | VC Table Record Logical Structure                               |                |

| 5-10             | Address Compression with VPI-only Table Lookup                  | 5-10           |

| 5-11             | External Address Compression Events                             |                |

| 5-12             | EAC Write (Request) Structure                                   |                |

| 5-13             | EAC Read (Response) Structure                                   |                |

| 5-14             | Data Structure with No HEC/UDF (ISHF=00)                        |                |

| 5-15             | Data Structure with HEC/UDF = 0 (ISHF = 10)                     | 5-17           |

| 5-16             | Data Structure with HEC Octet from Switch Parameter (ISHF = 11) |                |

| 5-17             | Data Structure with UDF Word from Switch Parameters (ISHF = 11) |                |

| 5-18             | Egress Data Path                                                | 5-19           |

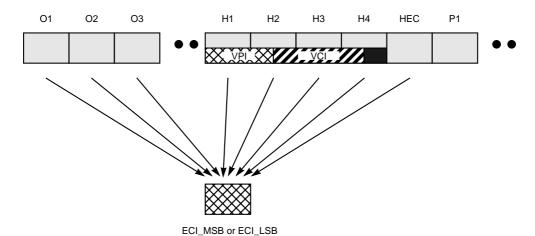

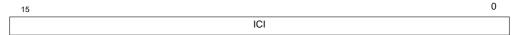

| 5-19             | ECI Extraction from Switch Cell Data Structure                  | 5-21           |

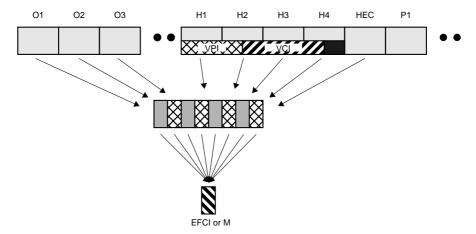

| 5-20             | EFCI and M Extraction from Switch Cell Data Structure           |                |

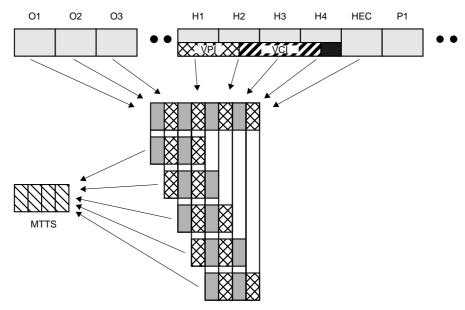

| 5-21             | MTTS Extraction from Switch Cell Data Structure                 | 5-23           |

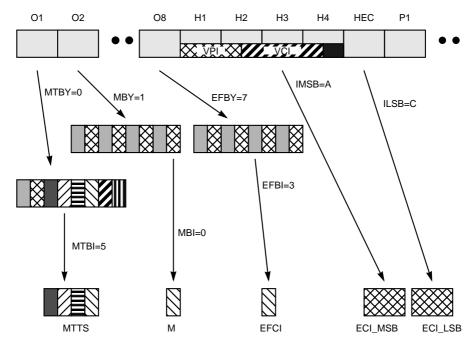

| 5-22             | Overhead Extraction Example                                     | 5-24           |

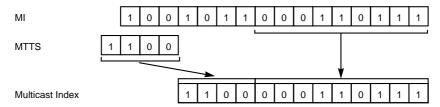

| 5-23             | Multicast Derivation Example                                    |                |

| 5-24             | Multicast Translation                                           |                |

| 6-1              | PPD Algorithm Example                                           |                |

| 6-2              | EPD Algorithm Example                                           | 6-5            |

|                  |                                                                 |                |

| Figure<br>Number | . Title                                                              | Page<br>Number |

|------------------|----------------------------------------------------------------------|----------------|

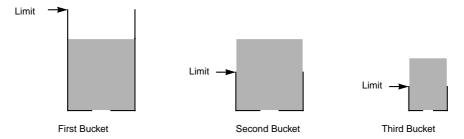

| 6-3              | Three Bucket Example                                                 | 6-5            |

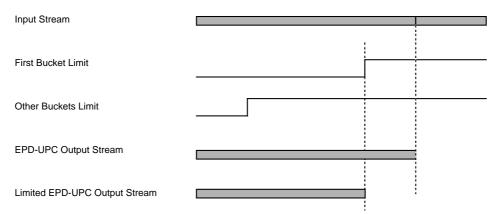

| 6-4              | Comparison of EPD vs. Limited EPD                                    |                |

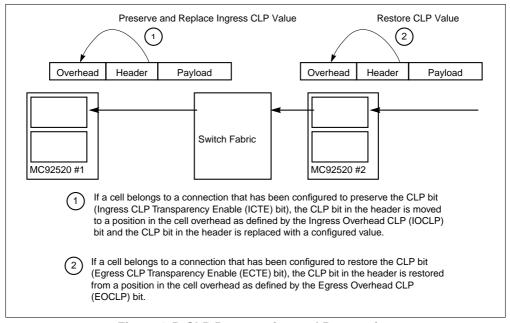

| 6-5              | CLP Preservation and Restoration                                     |                |

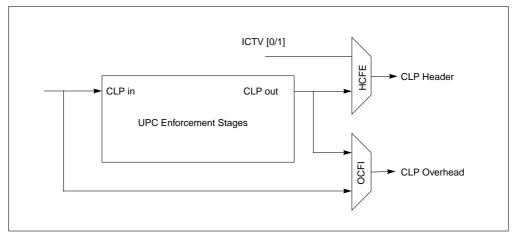

| 6-6              | CLP Selection for Preservation and Replacement                       |                |

| 6-7              | GFR UPC Enforcement Stages                                           |                |

| 6-8              | Random Frame Drop (RFD) Probability Functions                        | 6-22           |

| 6-9              | GFR Conformance and Eligibility Filter                               | 6-25           |

| 6-10             | GFR Conformance/Eligibility Filter and Fair Cell Rate Administration |                |

| 6-11             | RM Cell Fields                                                       |                |

| 6-12             | MC92520 to Switch Connections                                        | 6-33           |

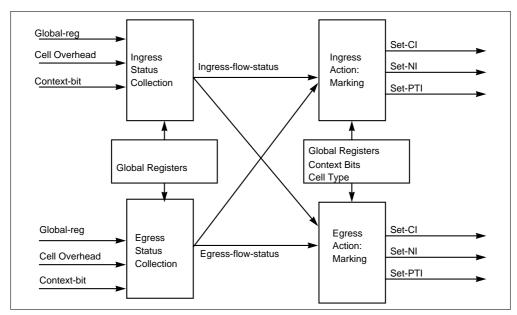

| 6-13             | MC92520 Marking Scheme                                               | 6-34           |

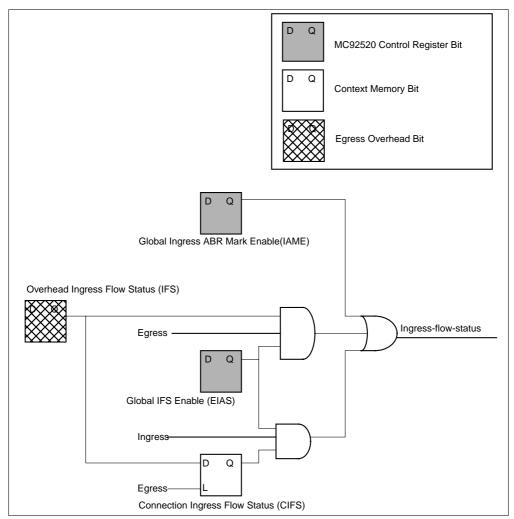

| 6-14             | Ingress-Flow-Status Logic                                            | 6-36           |

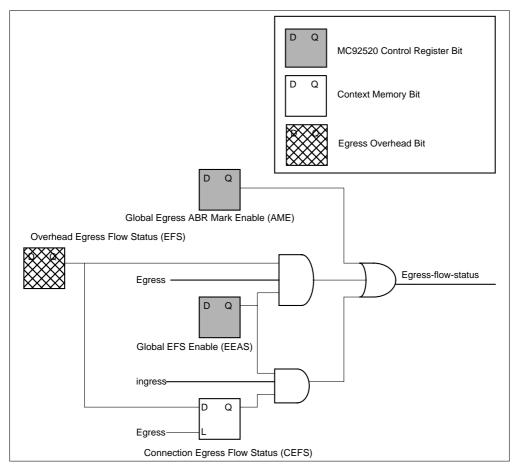

| 6-15             | Egress-Flow-Status Logic                                             | 6-38           |

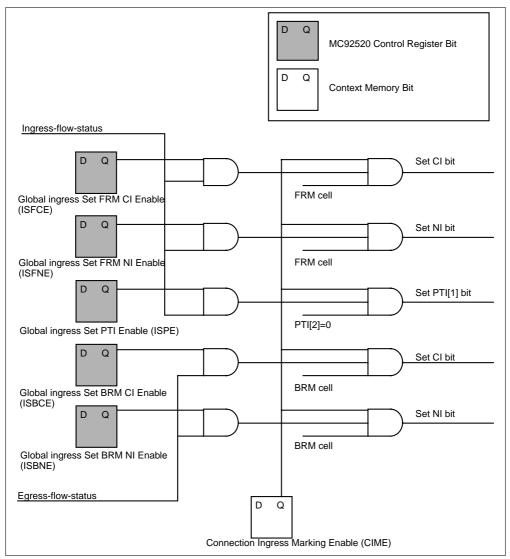

| 6-16             | Ingress Direction Actions                                            | 6-39           |

| 6-17             | Egress Direction Actions                                             | 6-41           |

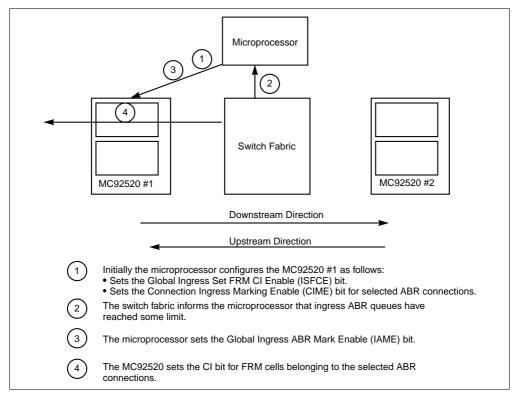

| 6-18             | Marking CI Bits of Ingress FRM Cells                                 |                |

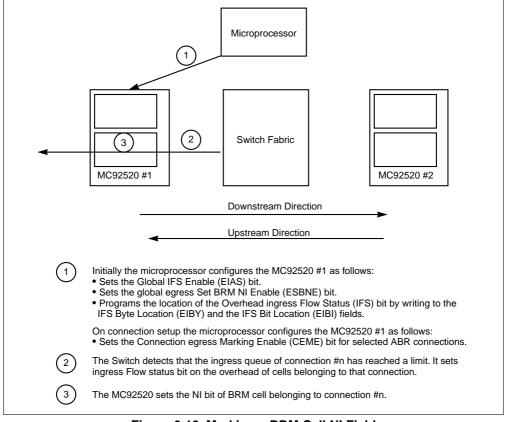

| 6-19             | Marking a BRM Cell NI Field                                          | 6-43           |

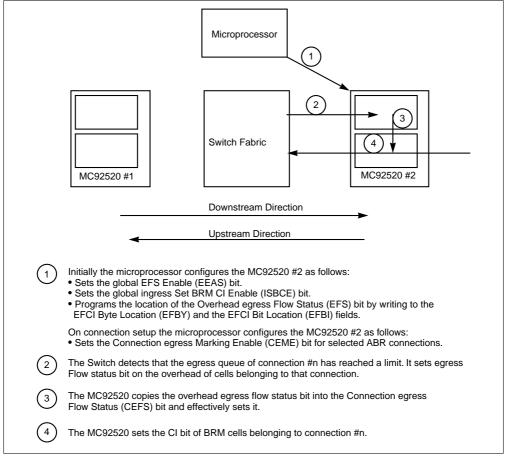

| 6-20             | Marking the CI Bit for All Ingress BRM Cells for a Connection        | 6-44           |

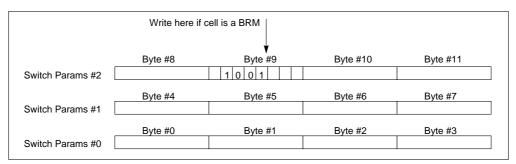

| 6-21             | Ingress Switch Parameter Example                                     | 6-45           |

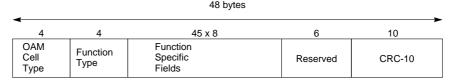

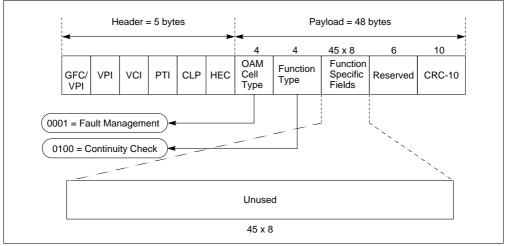

| 6-22             | OAM Cell Payload Structure                                           | 6-48           |

| 6-23             | Visibility of VCCs at the End Points of VPCs                         | 6-50           |

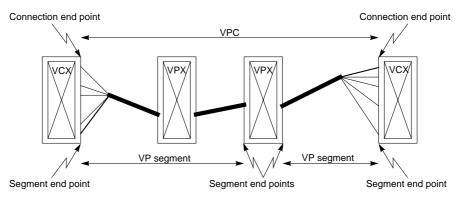

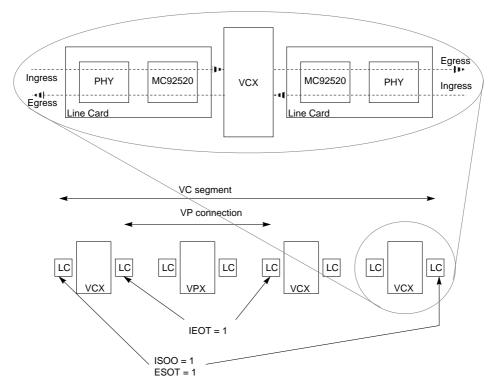

| 6-24             | Example of VP Connection / VC Segment                                | 6-50           |

| 6-25             | AIS/RDI Fault Management Cell                                        | 6-52           |

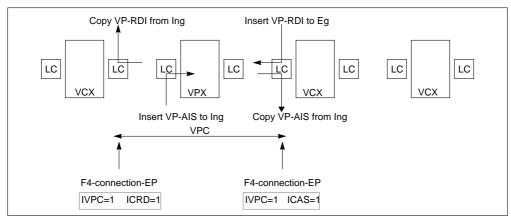

| 6-26             | F4 AIS/RDI Flows for a VPC Internal to the Network                   | 6-55           |

| 6-27             | F4 AIS/RDI Flows for a VPC that Crosses the UNI                      | 6-56           |

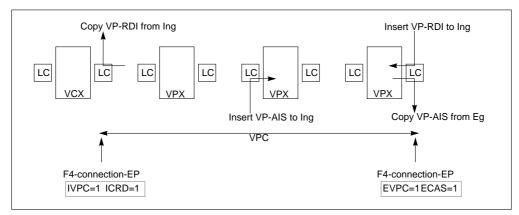

| 6-28             | F5 AIS/RDI Flows                                                     | 6-56           |

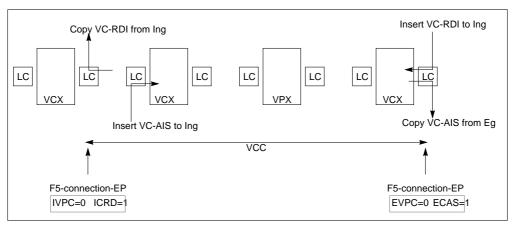

| 6-29             | Continuity Check Fault Management Cell                               | 6-57           |

| 6-30             | OAM Loopback Cell                                                    | 6-59           |

| 6-31             | Loopback Not at End Point                                            | 6-60           |

| 6-32             | Loopback at End Point of VCC                                         | 6-61           |

| 6-33             | Performance Management Cell                                          | 6-62           |

| 6-34             | Performance Management Block Test on a VPC Segment                   | 6-66           |

| 6-35             | Performance Management Block Test on a VCC                           |                |

| 6-36             | F4 PM Block Test on a VPC Internal to the Network                    | 6-67           |

| 6-37             | F4 PM Block Test on a VPC that Crosses the UNI                       | 6-68           |

| 6-38             | F4 OAM Flow for a VPC Internal to the Network                        | 6-69           |

| 6-39             | F4 OAM Flow for a VPC that Crosses the UNI                           | 6-69           |

| 6-40             | F5 OAM Flow                                                          | 6-70           |

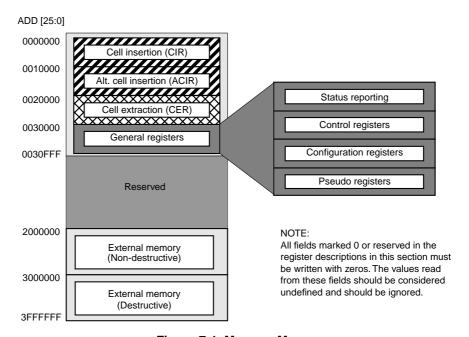

| 7-1              | Memory Map                                                           | 7-2            |

| 7-2              | Cell Insertion Register Addresses                                    |                |

| 7-3              | Cell Extraction Register Addresses                                   |                |

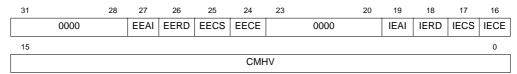

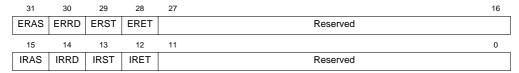

| 7-4              | Interrupt Register (IR) Fields                                       | 7-7            |

| 7-5              | Interrupt Mask Register (IMR)                                        | 7-10           |

| Figure<br>Number | Title                                                         | Page<br>Number |

|------------------|---------------------------------------------------------------|----------------|

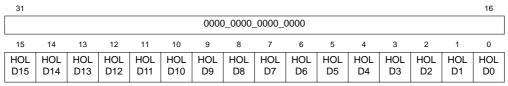

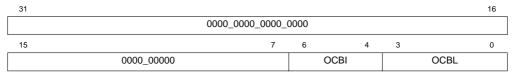

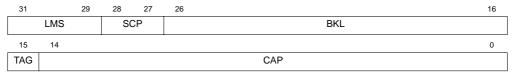

| 7-6              | HOL Blocking Status Register (HOLDSR)                         | 7-12           |

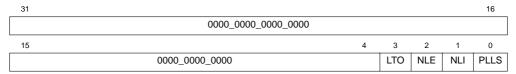

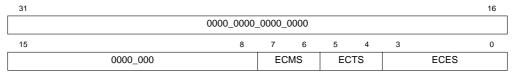

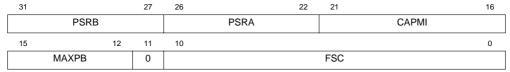

| 7-7              | PLL Status Register (PLLSR)                                   |                |

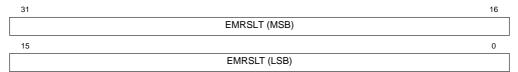

| 7-8              | EM Maintenance Slot Read Access Result (EMRSLT) Fields        | 7-13           |

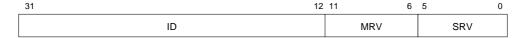

| 7-9              | Revision Register (RR)                                        |                |

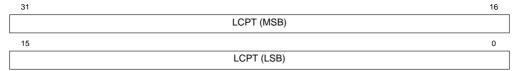

| 7-10             | Last Cell Processing Time Register (LCPTR) Fields             |                |

| 7-11             | ATMC CFB Revision Register (ARR)                              | 7-14           |

| 7-12             | PLL Control Register (PLLCR)                                  |                |

| 7-13             | Microprocessor Control Register (MPCTLR) Fields               | 7-15           |

| 7-14             | Maintenance Control Register (MACTLR)                         |                |

| 7-15             | Cell Extraction Queue Filtering Register 0 (CEQFR0) Fields    |                |

| 7-16             | Cell Extraction Queue Filtering Register 1 (CEQFR1)           | 7-17           |

| 7-17             | Cell Extraction Queue Priority Register 0 (CEQPR0) Fields     | 7-17           |

| 7-18             | Cell Extraction Queue 000 1 (CEQPR1)                          | 7-18           |

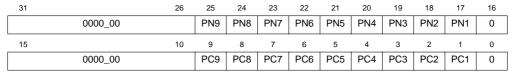

| 7-19             | Ingress Insertion Leaky Bucket Register (IILB)                | 7-18           |

| 7-20             | Ingress Insertion Bucket Fill Register (IIBF)                 | 7-19           |

| 7-21             | Egress Insertion Leaky Bucket Register (EILB)                 | 7-19           |

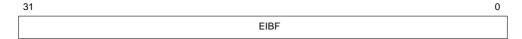

| 7-22             | Egress Insertion Bucket Fill Register (EIBF)                  | 7-20           |

| 7-23             | Internal Scan Register (ISCR)                                 | 7-20           |

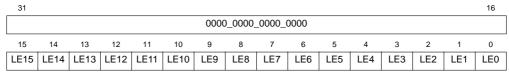

| 7-24             | Ingress Link Register (ILNKn)                                 |                |

| 7-25             | Egress Link Enable Register (ELER)                            | 7-22           |

| 7-26             | Egress Link Register (ELNKn)                                  | 7-23           |

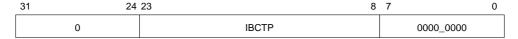

| 7-27             | Ingress Billing Counters Table Pointer (IBCTP) Fields         | 7-24           |

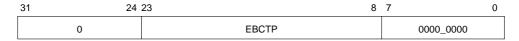

| 7-28             | Egress Billing Counters Table Pointer (EBCTP) Fields          | 7-24           |

| 7-29             | Policing Counters Table Pointer (PCTP) Fields                 | 7-25           |

| 7-30             | CLTMR Fields                                                  |                |

| 7-31             | Ingress Processing Control Register (IPLR)                    | 7-25           |

| 7-32             | Egress Processing Control Register (EPLR)                     | 7-26           |

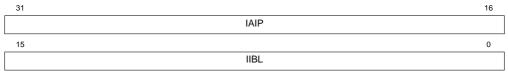

| 7-33             | Indirect External Memory Access Address Register (IAAR)       |                |

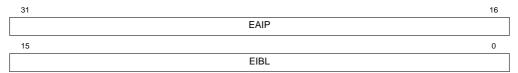

| 7-34             | Cell Arrival Period Multiplier (CAPMnn) Fields                | 7-27           |

| 7-35             | PLL Range Register (PLLRR)                                    |                |

| 7-36             | Microprocessor Configuration Register (MPCONR)                | 7-28           |

| 7-37             | Ingress PHY Configuration Register (IPHCR)                    |                |

| 7-38             | Egress PHY Configuration Register (EPHCR)                     | 7-30           |

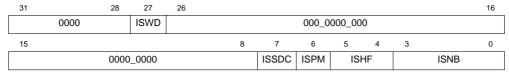

| 7-39             | Ingress Switch Interface Configuration Register (ISWCR)       | 7-32           |

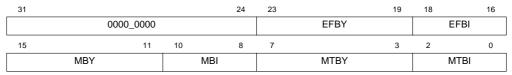

| 7-40             | Egress Switch Interface Configuration Register (ESWCR)        |                |

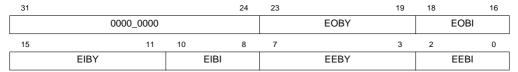

| 7-41             | Egress Switch Interface Configuration Register 1(ESWCR1)      | 7-36           |

| 7-42             | Egress Switch Overhead Information Register 0 (ESOIR0)        | 7-37           |

| 7-43             | Egress Switch Overhead Information Register 1 (ESOIR1) Fields | 7-38           |

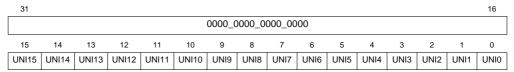

| 7-44             | UNI Register (UNIR)                                           | 7-38           |

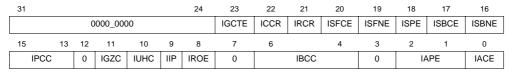

| 7-45             | Ingress Processing Configuration Register (IPCR)              | 7-39           |

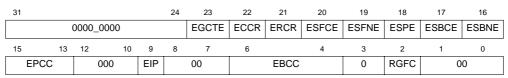

| 7-46             | Egress Processing Configuration Register (EPCR)               |                |

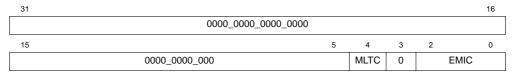

| 7-47             | Egress Multicast Configuration Register (EMCR)                |                |

| 7-48             | ATMC CFB Configuration Register (ACR)                         | 7-43           |

| Figure<br>Number | Title                                                              | Page<br>Number |

|------------------|--------------------------------------------------------------------|----------------|

| 7-49             | General Configuration Register (GCR)                               | 7-45           |

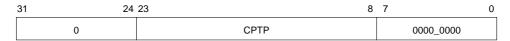

| 7-50             | Context Parameters Table Pointer (CPTP) Fields                     | 7-46           |

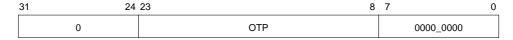

| 7-51             | OAM Table Pointer (OTP) Register Fields                            | 7-46           |

| 7-52             | Dump Vector Table Pointer (DVTP) Register Fields                   | 7-46           |

| 7-53             | VC Table Pointer (VCTP) Register Fields                            | 7-47           |

| 7-54             | Multicast Translation Table Pointer (MTTP) Register Fields         |                |

| 7-55             | Flags Table Pointer (FTP) Register Fields                          | 7-47           |

| 7-56             | Egress Link Counters Table Pointer (ELCTP) Register Fields         |                |

| 7-57             | Ingress Link Counters Table Pointer (ILCTP) Register Fields        |                |

| 7-58             | Context Parameters Extension Table Pointer (CPETP) Register Fields |                |

| 7-59             | Node ID Register 0 (ND0) Fields                                    |                |

| 7-60             | Node ID Register 1 (ND1) Fields                                    |                |

| 7-61             | Node ID Register 2 (ND2) Fields                                    |                |

| 7-62             | Node ID Register 3 (ND3) Fields                                    |                |

| 7-63             | Ingress VCI Copy Register (IVCR)                                   |                |

| 7-64             | Egress VCI Copy Register (EVCR)                                    |                |

| 7-65             | Ingress VCI Remove Register (IVRR)                                 |                |

| 7-66             | Egress VCI Remove Register (EVRR)                                  |                |

| 7-67             | Performance Monitoring Exclusive Register (PMER)                   |                |

| 7-68             | RM Overlay Register (RMOR)                                         |                |

| 7-69             | CLP Transparency Overlay Register (CTOR)                           |                |

| 7-70             | Egress Overhead Manipulation Register (EGOMR)                      |                |

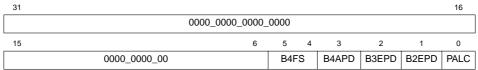

| 7-71             | GFR Configuration Register (GFRCR)                                 |                |

| 7-72             | External Memory Partitioning                                       |                |

| 7-73             | Context Parameters Table Record (Full Configuration)               |                |

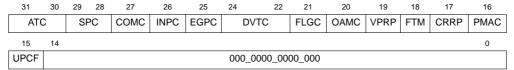

| 7-74             | Context Parameters Table Record (ATC=01, SPC=01)                   |                |

| 7-75             | Egress Translation Address Long Word                               |                |

| 7-76             | Ingress Address Translation Long Word                              |                |

| 7-77             | Common Parameters Long Word Fields (PMAC = 0)                      |                |

| 7-78             | Common Parameters Long Word Fields (PMAC = 1)                      |                |

| 7-79             | Egress Parameters Long Word Fields                                 |                |

| 7-80             | Ingress Parameters Long Word Fields                                |                |

| 7-81             | Ingress Counters (Full Configuration—IBCC = 001)                   |                |

| 7-82             | Ingress Counters (Single OAM Configuration—IBCC = 011)             |                |

| 7-83             | Ingress Counters (Single OAM Configuration—IBCC = 010)             |                |

| 7-84             | Ingress Counters (No CLP Distinction Configuration—IBCC = 100)     |                |

| 7-85             | Ingress Counters (No OAM Distinction Configuration—IBCC = 101)     |                |

| 7-86             | Ingress Counters (Single Counter Configuration—IBCC = 110)         |                |

| 7-87             | Egress Counters (Full Configuration—EBCC = 001)                    |                |

| 7-88             | Egress Counters (Single OAM Configuration—EBCC = 011)              |                |

| 7-89             | Egress Counters (Single OAM Configuration—EBCC = 010)              |                |

| 7-90             | Egress Counters (No CLP Distinction Configuration—EBCC = 100)      |                |

| 7-91             | Egress Counters (No OAM Distinction Configuration—EBCC = 101)      |                |

| Figure<br>Number           | Title                                                                                                                               | Page<br>Number |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 7-92                       |                                                                                                                                     |                |

| 7-92<br>7-93               | Egress Counters (Single Counter Configuration—EBCC = 110)                                                                           |                |

| 7-93<br>7-94               | Policing Counters (Full Configuration—PCC = 001)                                                                                    |                |

| 7-9 <del>4</del><br>7-95   | Policing Counters (No CLP Distinction Configuration—PCC = 010)                                                                      |                |

| 7-93<br>7-96               | Policing Counters (No CLP Distinction Configuration—PCC = 011)                                                                      |                |

| 7-90<br>7-97               | Policing Counters (Only Discard Counter Configuration—PCC=101)                                                                      | 7-11           |

| 7-97<br>7-98               | Flags Table Fields                                                                                                                  |                |

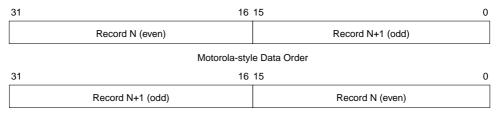

| 7-98<br>7-99               | Arrangement of 16-Bit Records in External Memory                                                                                    |                |

| 7-99<br>7-100              | VP Table Structure                                                                                                                  |                |

| 7-100<br>7-101             | VP Table Structure                                                                                                                  |                |

| 7-101                      | VP Table Record Fields with VP Switching                                                                                            |                |

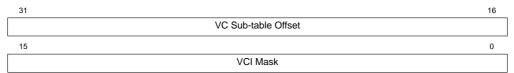

| 7-102<br>7-103             | VC Record Structure                                                                                                                 |                |

| 7-103<br>7-104             | Multicast Translation Table Record Structure                                                                                        |                |

| 7-10 <del>4</del><br>7-105 | Bucket Entries.                                                                                                                     |                |

| 7-105<br>7-106             | Bucket Information Word 1, 3, 5, and 7 Fields - GFR Policing Not Selected                                                           |                |

| 7-100<br>7-107             | Bucket Information Word 2, 4, 6, and 8 Fields - GFR Policing Not Selected                                                           |                |

| 7-107<br>7-108             | Bucket Information Word 2, 4, 0, and 8 Fields - GFR Policing Not Selected  Bucket Information Word 1 Fields - GFR Policing Selected |                |

| 7-108<br>7-109             | Bucket Information Word 2 Fields - GFR Policing Selected                                                                            |                |

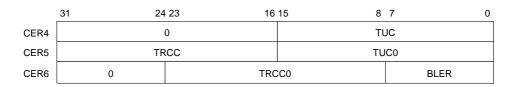

| 7-109<br>7-110             | OAM Table Record                                                                                                                    |                |

| 7-110<br>7-111             | Control Bits.                                                                                                                       |                |

| 7-111                      | Dump Vector Table Egress Long Word Fields                                                                                           |                |

| 7-112                      | Dump Vector Table Ingress Long Word Fields                                                                                          |                |

| 7-113                      | Ingress Link Counter Record                                                                                                         |                |

| 7-115                      | Egress Link Counter Record                                                                                                          |                |

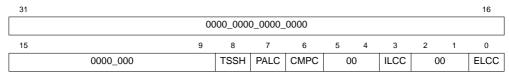

| 7-116                      | Parameter Extension Word Fields (PMAC = 1 and UPCF = 0)                                                                             |                |

| 7-117                      | Parameter Extension Word Fields (PMAC = 1 and UPCF = 1)                                                                             |                |

| 7-118                      | Parameter Extension Word Fields (PMAC = 0 and UPCF = 0)                                                                             |                |

| 7-119                      | Parameter Extension Word Fields (PMAC = 0 and UPCF = 1)                                                                             |                |

| 7-120                      | Inserted Cell Structure                                                                                                             |                |

| 7-121                      | Cell Descriptor Format I                                                                                                            |                |

| 7-122                      | Cell Descriptor Format II                                                                                                           |                |

| 7-123                      | Cell Descriptor Format III                                                                                                          |                |

| 7-124                      | Cell Descriptor Format IV                                                                                                           |                |

| 7-125                      | Cell Descriptor Format V                                                                                                            | 7-100          |

| 7-126                      | Connection Descriptor Structure                                                                                                     | 7-101          |

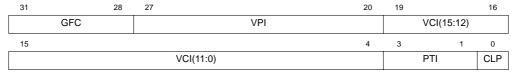

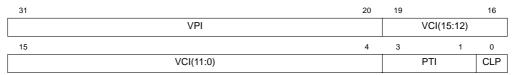

| 7-127                      | Inserted Cell ATM Cell Header Fields (UNI)                                                                                          | 7-101          |

| 7-128                      | Inserted Cell ATM Cell Header Fields (NNI)                                                                                          | 7-101          |

| 7-129                      | Inserted BRC Fields Template                                                                                                        | 7-102          |

| 7-130                      | Extracted Cell Structure                                                                                                            | 7-103          |