# User Guide

C-WARE SOFTWARE TOOLSET TUTORIAL WORKBOOK

C-WARE SOFTWARE TOOLSET VERSION 2.2

CSTTW-UG/D Rev 00

# C-Ware Software Toolset Tutorial Workbook

C-WARE SOFTWARE TOOLSET, VERSION 2.2

**Copyright** © **2003 Motorola, Inc.** All rights reserved. No part of this documentation may be reproduced in any form or by any means or used to make any derivative work (such as translation, transformation, or adaptation) without written permission from Motorola.

Motorola reserves the right to revise this documentation and to make changes in content from time to time without obligation on the part of Motorola to provide notification of such revision or change.

Motorola provides this documentation without warranty, term, or condition of any kind, either implied or expressed, including, but not limited to, the implied warranties, terms or conditions of merchantability, satisfactory quality, and fitness for a particular purpose. Motorola may make improvements or changes in the product(s) and/or the program(s) described in this documentation at any time.

C-3e, C-5, C-5e, C-Port, C-Ware, Q-3, and Q-5 are all trademarks of C-Port, a Motorola Company. Motorola and the stylized Motorola logo are registered in the US Patent & Trademark Office. All other product or service names are the property of their respective owners.

Lesson 1

LESSON 2

# **CONTENTS**

| About This Guide                                  |    |

|---------------------------------------------------|----|

| Guide Overview                                    | 9  |

| Using PDF Documents                               | 10 |

| Guide Conventions                                 | 11 |

| References to CST Pathnames                       | 12 |

| Revision History                                  | 13 |

| Related Product Documentation                     | 14 |

| Workbook Overview                                 |    |

| Overview                                          | 17 |

| Lessons                                           | 17 |

| Lessons in This Workbook                          | 18 |

| CST High-Level Directories                        | 18 |

| Building C-5 Applications From Programs           | 18 |

| Simulating the Execution of C-5 Programs          | 19 |

| Debugging C-5 RC Programs                         | 19 |

| Generating Simulated Ingress Traffic              | 20 |

| Post-Processing Simulated Egress Traffic          | 20 |

| Programming the C-5 Serial Data Processors        | 21 |

| Modifying the Gigabit Ethernet Switch Application | 21 |

| CST Helpful Hints                                 | 22 |

| Referring to CST Directory Pathnames              | 22 |

| Windows NT™ File Completion                       | 23 |

| Setting the CST Environment Variables             | 23 |

| Text Editors                                      | 24 |

| Examining the Toolset's Top-Level Directories     |    |

| Goals                                             | 25 |

| Prerequisites                                     | 25 |

LESSON 3

Lesson 4

| Top-Level Directory Contents                                     |  |

|------------------------------------------------------------------|--|

| alliance\                                                        |  |

| apps\                                                            |  |

| bin\                                                             |  |

| contrib\                                                         |  |

| diags\                                                           |  |

| Documentation\                                                   |  |

| drivers\                                                         |  |

| libperl\                                                         |  |

| mingw\                                                           |  |

| services\                                                        |  |

| Tools\                                                           |  |

| Summary                                                          |  |

| Exercises                                                        |  |

| Prerequisites                                                    |  |

| Source Files Correspond to Network Processor Embedded Processors |  |

| Automated Building of Packages                                   |  |

| More About Package Files and Build Target Variants               |  |

| Compiling the Application's Programs                             |  |

| XPRC Programs                                                    |  |

| CPRC Programs                                                    |  |

| Microcode Programs                                               |  |

| Dependency Checking                                              |  |

|                                                                  |  |

| Summary                                                          |  |

| Exercises                                                        |  |

| Building Programs That Perform Offline Support for Applications  |  |

| · ·                                                              |  |

| Goals                                                            |  |

#### CONTENTS

| Components and Capabilities of the C-Ware Simulation Environment  | 46 |

|-------------------------------------------------------------------|----|

| Starting the Simulator                                            | 46 |

| Using the cwsim.exe Wrapper                                       | 46 |

| Starting a Simulator Explicitly                                   | 47 |

| Automatic Use of the Configuration File and/or Command Input File | 47 |

| Featured Capabilities of the C-Ware Simulator                     |    |

| Awareness of CST Build System Environment Variables               |    |

| Interactive Simulator Control                                     |    |

| Support for Simulated Ingress and Egress Traffic                  |    |

| Supported by Pattern Generation Tools                             |    |

| Modeling the C-Port Q-5 Traffic Management Coprocessor            | 50 |

| Modeling the C-Port M-5 Channel Adapter                           |    |

| Preloading Executables in XP, CP, SDPs, and FP                    |    |

| Preloading a Saved State of the NP's Table Lookup Unit            |    |

| Preloading a Saved State of the NP's Buffer Management Unit       |    |

| Starting the C-Ware Debugger Within the Simulator                 |    |

| Running Simulations Under Control of CWIPA Performance Analyzer   |    |

| Supporting External Loopback for SDPs and the Fabric Processor    |    |

| Other CSE Components and Capabilities                             |    |

| Simulating PCI Bus Transactions To/From the Network Processor     |    |

| Providing Blocking TCP Clients and Servers to External Processes  |    |

| Supporting Nonblocking I/O for Socket Interfaces                  |    |

| System Simulations That Are Supported                             |    |

| Understanding Simulator Commands                                  |    |

| Navigating Among Simulated NP Components                          |    |

| Running Simulations                                               |    |

| Simulator Configuration File                                      |    |

| Command Input File                                                |    |

| Preprocessing Configuration and Command Input Files               |    |

| Obtaining Information About NP Components                         |    |

| Component Tracing                                                 |    |

| ksPrintf() Diagnostic Messages                                    |    |

| Application-Defined Tracing                                       |    |

| Viewing the Simulator's Performance-Related Counters              |    |

| Summary                                                           |    |

| Exercises                                                         | 71 |

| Lesson 5 | Debugging XPRC and CPRC Programs                                 |                |

|----------|------------------------------------------------------------------|----------------|

|          | Goals                                                            |                |

|          | Featured Capabilities of the C-Ware Debugger                     |                |

|          | Starting the Debugger                                            |                |

|          | Starting Within a C-Ware Simulator Session                       |                |

|          | Starting Outside a Simulator Session 7                           |                |

|          | Establishing Debugger Interoperation With the Simulator 7        |                |

|          | Operating the Debugger                                           |                |

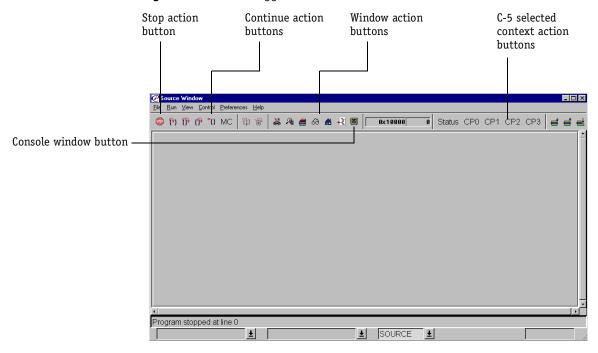

|          | Debugger Control of a Simulator Session                          | 30             |

|          | Targeting an RC or Shared CPRC Cluster                           | 30             |

|          | Opening the Debugger's Console Window                            | 31             |

|          | Setting Breakpoints 8                                            | 32             |

|          | Using the Button Bar                                             | 32             |

|          | Using a Console Window Command                                   | 32             |

|          | Viewing Information About Breakpoints 8                          | 32             |

|          | Setting a Thread-Specific Breakpoint                             | 3              |

|          | Setting a Temporary Breakpoint                                   | 3              |

|          | Encountering a Breakpoint                                        | 34             |

|          | Continue Program Execution                                       | 34             |

|          | Additional Topics                                                | 35             |

|          | Targeting a New RC Program in the Same Simulator Session         |                |

|          | Distinguishing RC Program Instances in Shared IMEM               |                |

|          | Viewing CPRC Thread Numbers 8                                    |                |

|          | Changing Focus to One CPRC Within the Cluster                    |                |

|          | Each Variable has Distinct Addresses in Cluster's DMEM Resources |                |

|          | Summary                                                          |                |

|          | Exercises                                                        |                |

| LESSON 6 | Generating Simulated Ingress Traffic                             |                |

|          | Goals                                                            | }9             |

|          | Overview                                                         | }9             |

|          | pg Scripts 9                                                     | <del>)</del> 0 |

|          | Pattern-Producing Scripts                                        | <del>)</del> 0 |

|          | General                                                          | <del>)</del> 0 |

|          | Protocole                                                        | nΩ             |

Fabric Port

91

API Scripts

91

|          | Ethernet Framer Scripts                             |       |

|----------|-----------------------------------------------------|-------|

|          | 100Mb Ethernet/IP Example                           |       |

|          | PPP Over SONET Example                              |       |

|          | Pattern Files                                       |       |

|          | Pattern File Format                                 |       |

|          | Benefits                                            |       |

|          | Exercises                                           |       |

| LESSON 7 | Post-Processing Simulated Egress Traffic            |       |

|          | Goals                                               | 99    |

|          | Overview                                            | 99    |

|          | Trace Files                                         | . 100 |

|          | Generating the Trace Files                          | . 100 |

|          | Analyzing the Trace Files                           | . 101 |

|          | Exercises                                           | . 103 |

| Lesson 8 | Programming the NP Serial Data Processors  Overview | 104   |

|          | SDP Architecture Overview                           |       |

|          | Common SDP Architecture                             |       |

|          | Common Microsequencer Architecture                  |       |

|          | Microsequencer Components                           |       |

|          | Payload In bus/Payload bus                          |       |

|          | Payload Out/P_bus                                   |       |

|          | A-Bus                                               |       |

|          | B-Bus                                               |       |

|          | ALU                                                 |       |

|          | Internal Registers (Iregs)                          |       |

|          | Content Addressable Memory (CAM)                    |       |

|          | Cyclic Redundancy (CRC) Block                       |       |

|          | Creg Address                                        |       |

|          | Microsequencer Inputs and Outputs                   |       |

|          | Aids to SDP Programming                             |       |

|          | Microcode Language                                  |       |

|          | Other Considerations                                |       |

|          | Creg Address Timing                                 |       |

|          | ALU Testing                                         |       |

|          |                                                     |       |

Lesson 9

| B-bus                                                    |     |

|----------------------------------------------------------|-----|

| P-bus                                                    |     |

| Microcode Symbols                                        |     |

| Visibility of SDPs in the C-Ware Simulator               | 114 |

| Microcode Messaging                                      | 114 |

| SDP Tracing                                              |     |

| Trace Level 1                                            |     |

| Trace Level 2                                            |     |

| Trace Level 3                                            |     |

| Analyzing SDP Performance                                | 123 |

| Trace Level 1                                            | 124 |

| Trace Level 2                                            | 124 |

| SDP Microcode Examples                                   | 127 |

| 'gmiiRxBit' Code Example                                 | 127 |

| 'RxByte' Code Example                                    | 134 |

|                                                          |     |

| Modifying the Gigabit Ethernet Switch Application        |     |

| Overview                                                 |     |

| Application Overview                                     |     |

| Specific Functional Changes                              |     |

| Building the Application                                 |     |

| Setting Up the Simulation Environment                    |     |

| Running the Unmodified Application Under Simulation      |     |

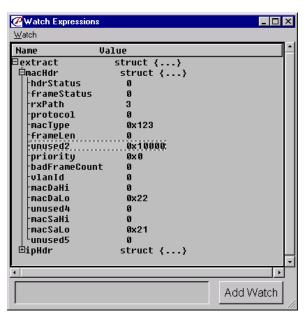

| Identifying a Discrepancy in Egress Data                 |     |

| Correcting the Discrepancy                               | 155 |

| Modifying the Transmit Microcode                         |     |

| Modifying the Receive Microcode                          | 165 |

| Verifying the Modifications                              | 168 |

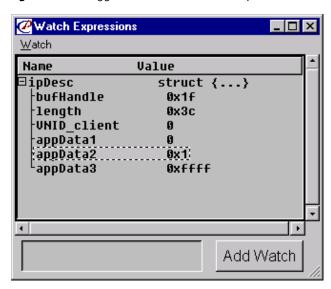

| Modying the Receive-Side and Transmit-Side CPRC Programs | 171 |

| Receive-Side CPRC Program Modifications                  | 171 |

| Transmit-Side CPRC Program Modifications                 | 177 |

# ABOUT THIS GUIDE

#### **Guide Overview**

This *C-Ware Software Toolset Tutorial Workbook* offers intensive instruction on how to use the Toolset to develop, debug, and tune C-Port NP-target application software.

This workbook is intended for new users of the CST who wish to quickly gain hands-on experience using CST software development tools.

This Workbook is divided into chapter-like sections called *lessons*. Each lesson assists the reader in learning a new set of skills for working with the CST.

This workbook contains nine chapters, which cover the following topics:

- Lesson 1 describes the structure of the lessons and provides details about the contents

of each lesson.

- Lesson 2 describes the structure of the CST Toolset and identifies the locations of the CST tools and components.

- Lesson 3 provides instruction on the building of C-Ware applications.

- Lesson 4 describes the features of the C-Ware Simulation Environment (CSE) and provides instruction on its use.

- Lesson 5 describes the features of the C-Ware Debugger and provides instruction on its use.

- Lesson 6 describes the purpose and use of pattern files and pattern generation scripts.

- Lesson 7 describes the purpose of trace files and provides instruction on the use of the **printTrace.pl** script to filter trace files.

- Lesson 8 provides instruction on programming the Serial Data Processors (SDPs).

- Lesson 9 provides instruction on how to modify and debug the Gigabit Ethernet Switch (**gbeSwitch**) application.

# **Using PDF Documents**

Electronic documents are provided as PDF files. Open and view them using the Adobe® Acrobat® Reader application, version 3.0 or later. If necessary, download the Acrobat Reader from the Adobe Systems, Inc. web site:

#### http://www.adobe.com/prodindex/acrobat/readstep.html

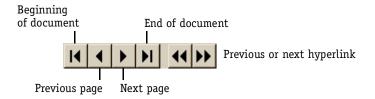

PDF files offer several ways for moving among the document's pages, as follows:

- To move quickly from section to section within the document, use the *Acrobat* bookmarks that appear on the left side of the Acrobat Reader window. The bookmarks provide an expandable 'outline' view of the document's contents. To display the document's Acrobat bookmarks, press the 'Display both bookmarks and page' button on the Acrobat Reader tool bar.

- To move to the referenced page of an entry in the document's Contents or Index, click on the entry itself, each of which is "hot linked."

- To follow a cross-reference to a heading, figure, or table, click the blue text.

- To move to the beginning or end of the document, to move page by page within the document, or to navigate among the pages you displayed by clicking on hyperlinks, use the Acrobat Reader navigation buttons shown in this figure:

Table 1 summarizes how to navigate within an electronic document.

**Table 1** Navigating Within a PDF Document

| TO NAVIGATE THIS WAY                                                     | CLICK THIS                                               |

|--------------------------------------------------------------------------|----------------------------------------------------------|

| Move from section to section within the document.                        | A bookmark on the left side of the Acrobat Reader window |

| Move to an entry in the document's Contents or Index.                    | The entry itself                                         |

| Follow a cross-reference (highlighted in blue text).                     | The cross-reference text                                 |

| Move page by page.                                                       | The appropriate Acrobat Reader navigation buttons        |

| Move to the beginning or end of the document.                            | The appropriate Acrobat Reader navigation buttons        |

| Move backward or forward among a series of hyperlinks you have selected. | The appropriate Acrobat Reader navigation buttons        |

## **Guide Conventions**

The following visual elements are used throughout this guide, where applicable:

This icon and text designates information of special note.

**Warning:** This icon and text indicate a potentially dangerous procedure. Instructions contained in the warnings must be followed.

**Warning:** This icon and text indicate a procedure where the reader must take precautions regarding laser light.

This icon and text indicate the possibility of electrostatic discharge (ESD) in a procedure that requires the reader to take the proper ESD precautions.

# References to CST Pathnames

You typically install the C-Ware Software Toolset (CST) on your development workstation in a directory path suggested by the installation procedure, such as:

- C:\C-Port\Cstx.y\ (on Windows NT)

- /usr/yourlogin/C-Port/Cstx.y/ (on Sun SPARC Solaris)

or:

/usr/cport/C-Port/Cstx.y/

or:

/opt/C-Port/Cstx.y/

where 'x' is a major version number and 'y' is a minor (or intermediate) version number.

You typically install each CST version under some directory path ...\C-Port\Cstx.y\. However, the user can install the CST in any directory on the development workstation. The user can also install more than one CST version on the same workstation.

Therefore, to refer to installed CST directories, we use pathnames that are relative to the ...\C-Port\Cstx.y\ path, which is the "root" of a given CST installation.

For example, the apps\gbeSwitch\ directory path refers to the location of the Gigabit Ethernet Switch application that is installed as part of the CST. The full path of this directory on a Windows NT system might be C:\C-Port\Cst2.2\apps\gbeSwitch\, so this convention is convenience for shortening the pathname.

Other top-level directories that are installed as part of the CST include **bin\**, **diags\**, **Documentation\**, **services\**, and so on. These directories are described in the *C-Ware Software Toolset Getting Started Guide* document, which is part of the CST documentation set.

# **Revision History**

Table 2 provides details about changes made for each revision of this guide.

Table 2

C-Ware Software Toolset Tutorial Workbook Revision History

| REVISION DATE    | CST REVISION | CDS REVISION | CHANGES           |

|------------------|--------------|--------------|-------------------|

| February 4, 2003 | 2.2          | 2.0          | Original version. |

# Related Product Documentation

Table 3 lists the user and reference documentation for the C-Port silicon, C-Ware Development System, and the C-Ware Software Toolset.

Table 3

C-Port Silicon and CST Documentation Set

| DOCUMENT<br>SUBJECT              | DOCUMENT NAME                                                | PURPOSE                                                                                                                                                           | DOCUMENT ID                                                  |

|----------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Processor<br>Information         | C-5 Network Processor Architecture Guide                     | Describes the full architecture of the C-5 network processor.                                                                                                     | C5NPARCH-RM                                                  |

|                                  | C-5 Network Processor Data Sheet                             | Describes hardware design specifications for the C-5 network processor.                                                                                           | C5NPDATA-DS                                                  |

|                                  | C-5e/C-3e Network Processor Architecture<br>Guide            | Describes the full architecture of the C-5e and C-3e network processors.                                                                                          | C53C3EARCH-RM                                                |

|                                  | C-5e Network Processor Data Sheet                            | Describes hardware design specifications for the C-5e network processor.                                                                                          | C5ENPDATA-DS                                                 |

|                                  | M-5 Channel Adapter Architecture Guide                       | Describes the full architecture of the M-5 channel adapter.                                                                                                       | M5CAARCH-RM                                                  |

|                                  | Q-5/Q-3 Traffic Management Coprocessor<br>Architecture Guide | Describes the full architecture of the Q-5 and Q-3 traffic management coprocessors.                                                                               | Q5Q3ARCH-RM                                                  |

| Hardware<br>Development          | C-Ware Development System Getting Started<br>Guide           | Describes installation of the CDS.                                                                                                                                | CDS20GSG-UG                                                  |

| Tools                            | C-Ware Development System User Guide                         | Describes operation of the CDS.                                                                                                                                   | CDS20UG-UG                                                   |

| Software<br>Development<br>Tools | C-Ware Software Toolset Getting Started Guide                | Describes how to quickly become acquainted with the CST's software development tools for a given CST platform.                                                    | CSTGSGW-UG<br>(Windows)<br>CSTGSGS-UG<br>(Sun SPARC Solaris) |

|                                  | C-Ware Application Building Guide                            | Describes tools to build executable programs for the C-Port network processors or simulators.                                                                     | CSTABG-UG                                                    |

|                                  | C-Ware Debugger User Guide                                   | Describes the GNU-based tool for debugging software running on either the C-Port network processorsor simulators.                                                 | CSTDBGUG-UG                                                  |

|                                  | C-Ware Integrated Performance Analyzer User<br>Guide         | Describes use of theIntegrated Performance<br>Analyzer tool for gathering performance<br>metrics of a C-Port NP-based application<br>running under the simulator. | CSTIPAUG-UG                                                  |

|                                  | C-Ware Simulation Environment User Guide                     | Describes how to configure and run a simulation of a C-Port NP-based application using simulator tools.                                                           | CSTSIMUG-UG                                                  |

**Table 3** C-Port Silicon and CST Documentation Set (continued)

| DOCUMENT<br>SUBJECT        | DOCUMENT NAME                                                | PURPOSE                                                                                                                                                             | DOCUMENT ID |

|----------------------------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Application<br>Development | C-Ware Application Design Guide                              | Describes design guidelines and trade-offs for implementing new C-Port NP-based communications applications.                                                        | CSTAPDG-UG  |

|                            | C-Ware API User Guide                                        | Describes the subsystems and services that make up the C-Ware Applications Programming Interface (API) for C-Port NP-based communications applications.             | CSTAPIUG-UG |

|                            | C-Ware Host Application Programming Guide                    | Describes the CST software infrastructure and APIs that support host based communications applications.                                                             | CSTHAPG-UG  |

|                            | C-Ware Microcode Programming Guide                           | Describes programming the C-Port network processor's Serial Data Processors and Fabric Processor.                                                                   | CSTMCPG-UG  |

|                            | C-Ware Q-5 TMC API User Guide                                | Provides a reference for the Q-5 Traffic<br>Management Coprocessor (TMC) API. This<br>guide includes a discussion and example of<br>creating a scheduler hierarchy. | CSTQ5API-UG |

| Other<br>Documents         | Answers to FAQs About C-Ware Software<br>Toolset Version 2.0 | Describes how the directory architecture provided in C-Ware Software Toolset Version 2.0 differs from previous CST releases.                                        | CSTOAFAQ-UG |

|                            | Build System Conventions                                     | Describes the key features of the C-Ware Software Toolset's provided environment for building software.                                                             | CSTOBSC-UG  |

|                            | C-Ware Software Toolset Application Guidelines               | Describes the criteria for how software components comply with the C-Ware Software Toolset's provided environment for building software.                            | CSTOCAG-UG  |

# WORKBOOK OVERVIEW

#### **Overview**

The C-Ware Software Toolset (CST) contains a powerful set of software development tools, simulation and performance analysis tools, and sample C-Ware Application Library reference applications that can greatly increase your capability to develop applications for the C-Port family of network processors.

This Tutorial Workbook offers intensive instruction on how to use the Toolset to develop, debug, and tune C-Port NP-target application software.

This Workbook assumes that you are already familiar with the architecture and features of Motorola's C-Port family of network processors.

#### Lessons

This Workbook is divided into chapter-like sections called *lessons*. Each lesson assists the reader in learning a new set of skills for working with the CST.

Each lesson presents the following:

- Goal The purpose of the lesson; that is, which skills you will learn.

- Prerequisites The knowledge and skills you should bring before performing this lesson.

- **Modules** A combination of knowledge to learn and steps to follow in order to learn a new skill. Each lesson can present one or more modules.

- Summary A restatement of the purpose of the lesson, how each module in the

lesson support the purpose of the lesson, and an explanation of how the new skills you

learned in this lesson relate to previously learned skills and to other skills you can learn

later in the Workbook.

- **Exercises** One or more suggested questions to answer, or suggested procedures to follow, that refresh and reinforce the reader's knowledge of the skills presented in this lesson.

#### **Lessons in This Workbook**

This Workbook presents the following lessons.

## CST High-Level Directories

This lesson presents how the CST's high-level directories and files are organized. Included informational topics are:

- Purpose and contents of all CST high-level directories

- Locations of CST directories that contain C-Ware applications (apps\) and components (apps\components\), tools (bin\), and CST product documentation (Documentation\)

- Organization of the CST documentation set

- Locations of directories from which to run CST-supplied applications under the C-Ware Simulation Environment

- How the CST's apps\application\ subdirectories support the CST's build system conventions

- Locations of CST diagnostics programs for the C-5 NP

# **Building C-5 Applications From Programs**

This lesson shows how to build a C-5 NP-targeted application package from a C-Ware application's individual programs, including these modules:

- Building the application's package

- Building the application's XPRC and CPRC programs and microprograms

- Performing dependency checking when building the application

- Building programs that perform offline support for C-Ware applications, such as table building

# Simulating the Execution of C-5 Programs

This lesson presents how to use the C-Ware Simulation Environment as a "target" for running your C-Ware applications, including these modules:

- Learning Simulator command primitives

- Identifying the simulated C-5 NP components

- Running simulations using the C-Ware Simulation Environment and C-Ware Simulator tool

- Purpose of the configuration file (config) and command input file (sim.in)

- Preprocessing the Simulator's configuration and command input files

- How the Simulator supports C-5 NP component tracing

- Generating diagnostic and trace messages during a simulation

## Debugging C-5 RC Programs

This lesson shows how to use the C-Ware Debugger, which is a custom implementation of the GNU **qdb** tool, to debug your C-5 applications, including these modules:

- Understanding high-level Debugger features

- Starting the Debugger, from within the C-5 Simulator or from outside the Simulator

- Understanding how the Debugger interoperates with the Simulator

- Operating the Debugger, including targeting an RC program, setting breakpoints, stepping through code, and distinguishing the contexts of execution for a program in a CP cluster

- Changing the target of a debugging session from one RC to another

# Generating Simulated Ingress Traffic

This lesson shows how to use the CST-provided set of Perl language "pattern generation" (or "pg") scripts to produce simulated ingress traffic data. You configure the Simulator to input this data to your C-Ware application as it runs under the C-Ware Simulation Environment, Included modules are:

- Description of all "pg" scripts: pattern-producing, API scripts, and Ethernet framer scripts

- Generating pattern files using "pg" scripts, with 100Mb Ethernet/IP and PPP over SONET examples

- Review of "pattern file" format

- Complementarity of using "pg" scripts and the **printTrace.pl** tool (for post-processing egress pattern files from running applications under simulation)

(An "ingress pattern file" is a representation of a stream of simulated ingress data traffic from a C-Ware application that ran under the Simulator.)

# Post-Processing Simulated Egress Traffic

This lesson shows how to use the **printTrace.pl** tool to filter an egress pattern file into a format that presents ATM cell data and payload, or Ethernet packet data and payload, in human-readable format. Included modules are:

- Purpose of "trace files"

- Analyzing trace files

- Examining sample output from the printTrace.pl tool

(An "egress pattern file" is a representation of a stream of simulated egress data traffic from a C-Ware application that ran under the Simulator.)

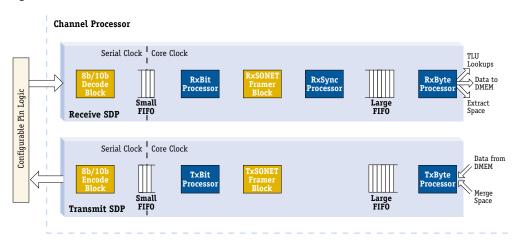

# Programming the C-5 Serial Data Processors

This lesson presents how to use the powerful features of the C-5 NP Channel Processor's Serial Data Processor (SDP) microsequencers to support detailed application requirements. This lesson also presents techniques for debugging SDP microcode programs within applications that run under the C-Ware Simulator. Included modules are:

- Overview of SDP architecture

- Overview of the common microsequencer architecture

- Overview of nine SDP microsequencers

- Overview of SDP microsequencer inputs and outputs

- Aids to SDP microcode programming

- Visibility of SDP state in the C-Ware Simulator, including microcode messaging and SDP tracing

- Analyzing SDP performance

- Examining SDP microcode source code

# Modifying the Gigabit Ethernet Switch Application

This lesson walks you through several specific steps for making a basic modification to the CST's Gigabit Ethernet Switch (**gbeSwitch**) application.

In this extended exercise, you modify both microcode and CPRC program code to implement a rearrangement of header bytes in a series of Ethernet frames that pass through the C-Ware Simulator as configured to model the C-5 NP Version D0 device.

## **CST Helpful Hints**

This section presents helpful hints for using the features of the CST.

#### Referring to CST Directory Pathnames

You typically install the CST in a default directory path provided by the installation procedure, such as:

- C:\C-Port\Cst2.2\ (on Windows NT)

- /usr/C-Port/Cst2.2/ (on Sun SPARC Solaris)

However, the user can install the CST in any directory on the system. The user can also install more than one CST version on the same system. You typically install those versions under the ...\C-Port\Cstx.x\ path.

To refer to CST directories in this guide, we use a relative pathname to refer to a "top-level" CST directory—that is, a directory path that is relative to the ...\C-Port\Cstx.x\ path. The CST's top-level directories typically contain subdirectories as well.

For example, we use the **apps\gbeSwitch\** directory path to refer to the location of the Gigabit Ethernet Switch application that is included in the CST. The full path of this directory on a Windows NT system might be **C:\C-Port\Cst2.2\apps\gbeSwitch\**, so shortening the path by this convention is convenient.

Other top-level directories that are installed as part of the CST include **bin**\, **Documentation**\, **diags**\, **services**\, and so on. These directories are described in "Top-Level Directory Contents" on page 25.

# Windows NT™ File Completion

In the Windows NT registry, you can define a keyboard key to perform "filename completion" for commands typed at the DOS shell prompt. This is a helpful feature because it allows you to avoid retyping long filenames and directory names, as found in the CST software development environment.

To enable the "filename completion" feature at the DOS command prompt:

- 1 From the Window desktop, click the 'Start' menu and select 'run...', then type 'regedit' as the command to perform. This opens the Windows registry edit (program name is **regedit**) program.

- 2 Press **Ctrl+F** to open the Registry Edit tool's Find dialog box.

- **3** In this dialog, search for the registry key 'CompletionChar'.

- **4** Edit the value of this registry key to be '9'. This enables use of the **Tab** key on the keyboard for filename completion inside the DOS shell.

## Setting the CST Environment Variables

You might have the need to install more than one version of the CST on your workstation. For instance, this might be required while you port your application from one CST version to another.

To support users who develop C-Ware based applications using more than one CST version, the CST defines and uses operating system environment variables that allow CST tools to differentiate among the directories of different CST installations.

The CST provides the **sv.bat** script (**sv.[c]sh** script on Sun Solaris<sup>™</sup>) in its **bin\** directory to set the environment variables used by CST program-building tools. In this Workbook there are instructions on how to use **sv.bat** from a DOS shell to set these variables.

To use a shell other than the DOS shell (such as the *bash* shell for Windows), you can put the set of environment variables that the **sv.bat** script sets in your shell initialization script (such as the **.bashrc** file for the *bash* shell).

If you prefer to use the DOS shell (as demonstrated in this Workbook), you must run the **sv.bat** script as the first command in each new DOS shell window that you open using CST program-building tools.

The syntax for calling the **sv.bat** program is as follows:

D:\C-Port\Cst2.2\bin> sv

Use this command if there is only one installation of the CST on your workstation, or if the most recent CST installation is the one that you are presently using.

If you have multiple CST installations on your workstation and you want to use a CST version other than the most recently installed version, then invoke **sv** with the path to the other installation:

D:\cd \C-Port\Cst2.0\bin> echo %CPORT%

D:\C-Port\Cst2.0\bin> sv d:\c-port\cst2.0

Details about using the **sv.bat** script are found in the C-Ware Software Toolset Getting Started Guide, which is part of the CST documentation set.

#### **Text Editors**

As you work with the CST's software development tools, you will open many text files for viewing and modification.

Though Windows NT includes text editors such as Microsoft Word<sup>TM</sup> and Microsoft WordPad<sup>TM</sup>, these are not necessarily the most effective editors for ASCII text.

We recommend that you install your favorite programmer's text editor on your workstation. Many users prefer *GNU Emacs, Epsilon*, or *vi* for text editing.

# EXAMINING THE TOOLSET'S TOP-LEVEL DIRECTORIES

#### Goals

In this lesson you will learn:

- The purposes of each top-level directory provided by the C-Ware Software Toolset (CST)

- How to identify the locations of CST tools, C-Ware Application Library software, CST services software, C-Ware diagnostics software, and the CST documentation set.

# **Prerequisites**

To perform this lesson's exercises, you should have access to a workstation on which the CST Version 2.2 product has been installed.

# Top-Level Directory Contents

The CST contains a number of tools, software applications, and a set of documentation that helps you develop systems based on the C-Port family of network processors.

This section describes the organization of the software in the CST, as well as where to find the tools, documentation, and applications that will be required for software development.

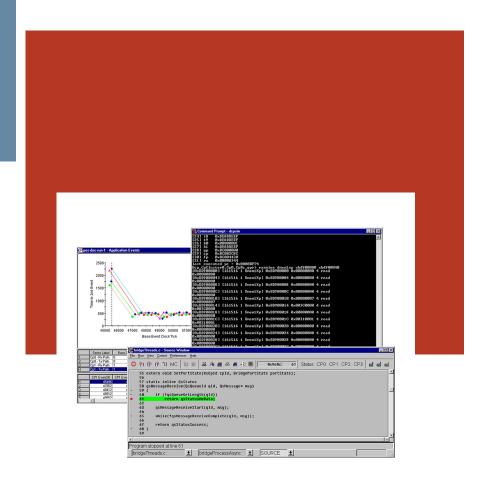

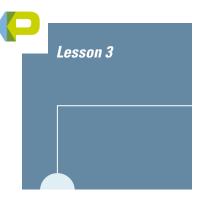

Figure 1 on page 26 depicts the workflow for using the CST's software development tools to build and work with a C-Ware application.

**CST Binary code** CST Source code **ISV Software OEM** Third party code Source **C-Ware Applications** Host Processor **Applications** Library Code Extended GNU-based optimizing C compiler C-Ware API Full function, SDP microcode C-Ware performance-accurate, C-Ware Microcode customization tools high-speed Compiler Tools simulation environment C-Ware Traffic User Test Script Simulation Post Tool **Environment** Processing Graphical performance C-Ware C-Ware Extended GNU-based monitoring tool Debugger Performance debugger Analyzer

Figure 1 User Workflow for CST Tools and Applications

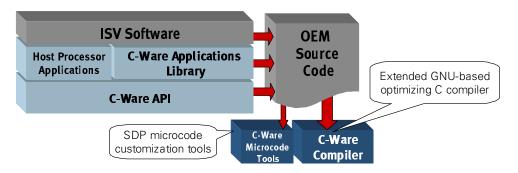

Under your CST installation's "root" directory, which is typically a path such as **C:\C-Port\Cst**x.x\, there are a set of top-level directories shown in Figure 2 on page 27.

Your CST installation's top-level directories might include the 'patch1' directory, which indicates that a *patch release* was also installed on this workstation after a giver CST product version was installed. A patch release updates only certain files in an existing CST installation on your workstation. Its directory contains its own **README** file and installation script.

#### alliance\

This directory contains software that allows a C-Ware based application to work with products provided by third-party vendors. This is software is provided, documented, tested, and supported by members of Motorola's Smart Networks Alliance Program. See the *CST Release Notes* document for a description of this software.

C-Port — Cst2. 2 🕀 🦳 alliance Software supporting third-party products Complete C-Port NP-based applications apps bin Software build tools and utilities contrib Useful sample software 🗻 diags Diagnostic software for C-Port NPs Documentation CST product documentation set drivers Host processor driver software and other drivers libperl Perl language support 📄 mingw GNU C compiler for Windows NT services C-Ware API software (C-Port NPs and host processor) 🛅 Tools Microcode assembler, other simulation tools

Figure 2 CST Version 2.2 Installation's Top-Level Directories (Windows NT Platform)

#### apps\

This directory contains all software for a set of C-Ware Application Library applications supported by Motorola in this CST release. Most of these applications demonstrate software that implements a Layer 3 or higher protocol on the C-Port family of network processors and support chips. Other applications implement tests that demonstrate basic functional capabilities of the C-5 Network Processor, such as the software found in the CST's apps\hostDmaTest\ directory.

Each application supports the C-5 NP and/or the C-5e/C-3e NP, either on actual hardware or under the C-Ware Simulator or both.

Each application's software is contained in its own subdirectory under **apps**\. Each application's directory contains these subdirectories:

chip\np\ — Contains subdirectories that contain all source code, organized by build target, as explained in the *Build System Conventions* document (apps\doc\Build\_System.pdf).

Under each .\chip\np\ directory subtree, find the application's main XPRC and CPRC programs under the relevant "terminal" (or end node) .\src\ subdirectory — that is, the .\chip\np\cprc\src\ and .\chip\np\xprc\src\ directories. The terminal .\src\

directory might be found directly under the .\chip\np\xprc\ directory or under a build target-specific subdirectory such as .\chip\np\xprc\c5\ or .\chip\np\cprc\cxe\.

The source file names for XPRC and CPRC main programs can depend on how the application uses the network processor's Channel Processors. Look for files with names such as **cpMain.c** (versus **xpMain.c**), **cpMainRx.c** (versus **cpMainTx.c**), **atmCpMain.c** (versus **atmRxMain.c** or **atmTxMain.c**), and so on. C-Ware applications that use a multi-phase (that is, overlaid) RC program might use both the source file names **xpMain.c** and **xpMainInit.c** to implement the two programs phases.

- **doc**\ Contains documentation about the application, typically including:

- A formatted user guide about the application's architecture and functionality

- A **README** file that summarizes the pertinent information about building the application

- **inc**\— Contains C language header (\*.h) files used to build the application that are common to all *build targets* for this application.

For a C-Ware-compliant application, a build target specifies a combination of chip architecture, chip product, chip generation (or version), chip processor, chip revision, runtime environment, and runtime configuration. These terms are defined and explained in the Build System Conventions document (apps\doc\Build System.pdf).

- offline\ (Provided only for certain C-Ware Application Library applications)

Contains software that is used to specify, create, and populate routing tables in a manner that uses a minimum of network processor cycles. This software reduces the number of cycles performed early in the application when run under the C-Ware Simulator. For a given application, see the file apps\application\doc\Readme for the details about using offline table building (if available).

- **run\** Contains files that allow you to build the entire application and to run the built application under simulation. That is, this directory contains:

- The top-level Makefile for building the application

- The package description file (that is, \*.dsc) for specifying the content of the application's package file

- The pair of \*.expected and \*.out files used for this application's installation acceptance test

- The C-Ware Simulator configuration and (optional) default command input file provided by the application developer.

Also contains the subdirectories (under .\bin\) that organize for each build target the network processor RC and SDP executable files (that is, \*.dcp and \*.sdp) and application package file (that is, \*.pkg) that result from building the application.

Also contains subdirectories (.\inPatterns\) and .\outPatterns\) that organize the files that contain representation of simulated ingress and egress traffic data. The application developer has provided these files to use (or to capture) when running this application under the C-Ware Simulator.

Also contains these subdirectories:

- deps\ Collects makefile dependency information produced by the make tool during application builds. Used by programmer-friendly text editors.

- lib\ Collects library (\*.a) files produced by the make tool during application builds.

- obj\ Collects object (\*.o) files produced by the make tool during application builds.

The apps\ directory also contains a .\components\ subdirectory that contains the software for each of a set of reusable components that are (or can be) used to build the C-Ware Application Library applications. Each .\components\ subdirectory contains its own subdirectories for building that component; these subdirectories (that is, the .\doc\, .\inc\, .\offline\, .\run\, and .\chip\np\ directories) are organized identically to C-Ware applications.

#### bin\

This directory contains most of the tools necessary to develop and build applications for the C-Port family of network processors, including running the C-Ware Simulator, and debugging and analyzing applications. You shouldn't need to modify the contents of this directory.

The **bin**\ directory must also contain a **license.db** file that is required for running the C-Ware Simulator. This license file can be obtained from your Motorola representative.

#### contrib\

This directory contains a range of software components, from complete applications to bits of source code. These components might have been created by Motorola or by third-party sources. *These applications and components are not supported by Motorola* but are deemed useful to developers of C-Ware applications. Any application provided here has minimal documentation.

The **contrib\archive\** directory contains previously released C-Ware Application Library applications that are *not supported by Motorola* in this CST release. Any application provided here has minimal documentation.

## diags\

This directory contains the environment for building a large set of diagnostics programs for testing particular C-Port network processor components. Building each diagnostic results in a C-Ware package file that can be packloaded into an actual C-Port network processor device or loaded into the C-Ware Simulator.

Building and running these diagnostics is described in the *C-Ware Development System User Guide* document.

#### **Documentation**\

This directory contains the entire CST documentation set, provided in Adobe Acrobat PDF file format for either online reading or offline printing.

We recommend that CST users first read the *CST Release Notes* document found in this directory. Included in the *Release Notes* is information on features that have been added, removed, or modified in this CST version.

The **Documentation**\ directory also contains the **C-Ware\_Start.html** file, which is an HTML page with hyperlinks to each item of CST product documentation, which are categorized as listed in Table 1 on page 31.

#### drivers\

This directory contains the software for "device driver" software to be incorporated into a host processor application program or host operating system (such as the Wind River Systems VxWorks real-time operating system). One important driver software object, the C-5 Device Driver, is described in the *C-Ware Host Application Programming Guide* document.

#### libper/\

This directory contains software for Perl language support for Windows NT.

## mingw\

This directory contains a version of the GNU C compiler (**gcc**) that produces applications that run under Windows NT. Used by the CST's Microcode Assembler tool.

**Table 1** Organization of the CST Documentation Set

| TYPE OF DOCUMENT        | NAME OF DOCUMENT                                                                   |

|-------------------------|------------------------------------------------------------------------------------|

| Release Notes           | C-Ware Software Toolset Release Notes                                              |

| Application Development | C-Ware Application Design Guide                                                    |

|                         | C-Ware API User Guide                                                              |

|                         | C-Ware Host Application Programming User Guide                                     |

|                         | C-Ware Microcode Programming Guide                                                 |

| Applications and        | AAL-5 SAR Application Guide                                                        |

| Components              | AAL-5 SAR to Gigabit Ethernet Switch Application Guide                             |

|                         | ATM Cell Switch Application Guide                                                  |

|                         | ···                                                                                |

| Development Tools       | C-Ware Application Building Guide                                                  |

|                         | C-Ware Debugger User Guide                                                         |

|                         | C-Ware Development System Getting Started Guide                                    |

|                         | C-Ware Development System User Guide                                               |

|                         | C-Ware Performance Analyzer User Guide                                             |

|                         | C-Ware Simulation Environment User Guide                                           |

|                         | C-Ware Software Toolset Getting Started Guide                                      |

| Other Documents         | Answers to Frequently Asked Questions About C-Ware Software<br>Toolset Version 2.0 |

|                         | Build System Conventions                                                           |

|                         | C-Ware Software Toolset Application Guidelines                                     |

|                         |                                                                                    |

#### services\

This directory contains all of the C-Ware application programming interface (API) code, including host-resident API code. The C-Ware API routines are described in the *C-Ware APIs User Guide* document and the *C-Ware Host Application Programming Guide*.

This directory's .\inc\ subdirectory contains all the public header files for the C-Ware APIs.

In the subdirectory under **services**\ for a given set of API services (such as .\buffer\ or .\queue\ or .\table\), look for Host API code under its .\host\ subdirectory.

The organization of the directory subtrees under **services**\ parallels that for the C-Ware Application Library applications provided under the CST's **apps\** directory. For more information, see the *Build System Conventions* document (**apps\doc\Build\_System.pdf**).

#### Tools\

This directory contains several software objects, some of which support the use of the C-Ware Simulator in a multiple C-Port network processor scenario. See the *C-Ware Simulation Environment User Guide* for more information about using this software.

This directory's .\common\ subdirectory contains other subdirectories that contain software used to perform multiple C-Port network processor system simulations.

This directory's .\pcisim\ subdirectory contains software for simulating a PCI bridge.

Under this directory's .\uasm\ subdirectory are the libraries used by the CST's Microcode Assembler tool.

# **Summary**

In this lesson you learned the purposes of each top-level directory provided by the C-Ware Software Toolset (CST).

In subsequent lessons you will use this knowledge to quickly identify the locations of CST tools, C-Ware Application Library software, CST services software, C-Ware diagnostics software, and the CST documentation set.

# **BUILDING C-WARE APPLICATIONS**

#### Goals

In this lesson you will learn:

- How the C-Ware Software Toolset's (CST) build system tools support building executable programs from these source files:

- C language programs for the network processor's Executive Processor (XP) and Channel Processor (CP)

- C language-like microcode programs for the network processor's Serial Data Processors (SDPs) and Fabric Processor FDPs

- How the CST provides automated building of a C-Ware application's software

- What a C-Ware package file is and how it is built from compiled Executive Processor RISC Core (XPRC) and Channel Processor RISC Core (CPRC) programs and from SDP/FDp microprograms

- What a build target variant is, and how the CST's apps\ subdirectories segregate an

application's compilation products by build target variants

- How the organization of the CST's **apps\** subdirectories support the CST build system

- How the CST's build system provides automatic dependency checking

- How some CST-supplied C-Ware applications provide "offline" programs for running the application more conveniently under the C-Ware Simulator

# **Prerequisites**

You should already be familiar with the organization and purposes of the CST's top-level directories.

To perform this lesson's exercises, you should have access to a workstation on which the CST Version 2.2 product has been installed.

# Source Files Correspond to Network Processor Embedded Processors

The C-5 Network Processor (NP) has a number of embedded RISC cores (RCs)—one Executive Processor RISC Core (XPRC) and 16 Channel Processor RISC Cores (CPRCs). In addition, each Channel Processor (CP) includes a microcode programmable Serial Data Processor (SDP, with both a set of ingress microsequences and blocks and a set of egress microsequencers and blocks). The C-5 NP also includes an embedded Fabric Processor (FP) whose Fabric Data Processors (FDPs), one for ingress and another for egress, are microcode programmable.

Each of these programmable entities can run a different software program. For example, there will be different software that runs in the XPRC, CPRCs, Channel Processor SDPs, and Fabric Processor FDPs.

The C-Ware Software Toolset (CST) allows you to use C language (and C language-like) source files for all these software programs and provides build tools to produce executable image files for each programmable entity.

Figure 3 Source Code Packaging

# Automated Building of Packages

This CST product provides complete automation of the program building activity. Each C-Ware Application Library application can be built using one high-level makefile, found in the file **apps**\application\run\Makefile. This makefile produces a package file for the application.

A package file (that is, \*.pkg) contains a concatenation of the application's executable images. Each image is downloaded into the C-5 NP processors when the chip is booted. When the C-5 NP device is installed in a C-Ware Development System (CDS), the use can "packload" the package file into the NP, or the package file can be declared in a configuration file (config) for loading into the C-Ware Simulator for application simulation.

To produce this package file, this makefile uses other makefiles to build an XPRC program executable (that is, a MIPS-like ELF file), some number of CPRC program executables (that is, MIPS-like ELF files), some number of Channel Processor SDP microprogram executables (that is, CAM contents, WCS contents, and so on), and Fabric Processor FDP microprogram executables. The software components used to build these executables are placed under the appropriate subdirectories found under the application's apps\application\chip\np\ directory.

When the network processor is taken out of reset, it is loaded with the contents of a package file. Or, when you start the C-Ware Simulator, you typically configure it to load a package file that is specified in a Simulator configuration file (**config**). Under software control (typically in an "init phase" program that is loaded first into the XPRC), the package's contents are loaded and distributed to the appropriate C-5 NP embedded processors, memories, and so on.

The application's makefile leaves the package file in a "build target variant" subdirectory of the **apps**\application\**run**\ directory. See the section "More About Package Files and Build Target Variants" that follows.

After you have set this command shell process's build target variant *environment variables*, described in the next section, you typically enter only one command to build the application:

C:\C-Port\...\application\run> make all

For a list of all makefile arguments (and their purposes) supported by an application's top-level **Makefile**, see the **Readme** file found in the application's .\doc\ subdirectory.

# More About Package Files and Build Target Variants

The application's package file is the ultimate product of using the **make** tool against the application's top-level makefile. The package file is typically placed in the specified build target variant's directory—that is, the **apps**\application\run\bin\variant\ directory.

The application's *build target variant* is an identifier that segregates different builds of the application based on different combinations of several parameters that relate to the application's execution target—that is, whether the package is loaded into:

- A host processor or a C-Port network processor

- If a C-Port network processor, which C-Port network processor device

- If a C-Port network processor, which version of that device

- If a C-Port network processor, whether an actual NP device or the Simulator

- Whether the package was built for debugging or production use

The exact design of the CST's build target variant scheme is described in the CST's Build System Conventions document.

The CST build system's makefiles depend on a set of environment variables for specifying the build target variant. Use the command scripts found in the **bin\configure\** to set these variables for a given build target variant. Alternatively, you can specify the build target variant for the next build on the **make** command line, as follows:

C:\C-Port\...\gbeSwitch\run\> make REV=c5-d0-sim-debug

Of course, set (or specify) the appropriate build target variant for the **apps**\application\run\ subdirectory where you issue the make command.

The CST provides the **dcpPackage** tool for creating a package from a set of MIPS-like ELF images for the XPRC and CPRC, SDP images, FP images, and so on. Find the **dcpPackage** tool in the CST's **bin\** directory.

All makefiles that build the executable components of a C-5 NP application are set up to build their respective images and to use **dcpPackage** to produce a C-5 NP package file.

Using the dcpPackage tool and specifying the contents of a package description file are discussed in the CST's C-Ware Application Building Guide document.

# Compiling the Application's Programs

The application's top-level makefile automatically rebuilds each constituent program or microprogram with a dependency whose instance has changed.

You typically build C language programs to run on the XPRC or CPRCs. C language-like source files are used to express microcode programs for the Channel Processors' SDPs and Fabric Processor's FDPs.

The C language programs and the microcode programs use different compilation steps, as described in the following sections.

Notice these important facts about each application's programs and their compilation products:

- Source code that is common to the application's XPRC and CPRC programs is typically located under a subdirectory named apps\application\chip\np\src\ and/or apps\application\chip\np\inc\.

- The compilation products of the application's programs, as binaries and like the

application's package file, are left in subdirectories that are segregated under build

target variants. That is, each application has its own apps\application\run\obj\variant\

and apps\application\run\lib\variant\ subdirectory trees.

# **XPRC Programs**

Source code that is unique to the application's XPRC program is typically located under a subdirectory named **apps**\application\chip\np\xprc\src\.

The object files (\*.o) and library files (\*.a) that result from a build are typically placed in the apps\application\run\obj\variant\xprc\ and apps\application\run\lib\variant\xprc\ directories, respectively.

The application's XPRC executable file (\*.dcp) and its corresponding map file (\*.map) are typically placed in the apps\application\run\bin\variant\ directory.

Note that the application typically uses a naming convention for the XPRC executable that includes the application identifier and the suffix "Xp", such as **gbeSwitchXp.dcp**.

#### **CPRC Programs**

Source code that is unique to the application's CPRC program(s) is typically located under a subdirectory named **apps**\application\chip\np\cprc\src\.

Notice that some applications will require more than one CP program, when different Channel Processors (CPs) on the C-5 NP are used for different purposes.

For example, in one application some CPs are dedicated to processing ingress traffic and others to egress traffic; in a different application certain CPs in the same CP cluster might process ingress traffic in a tightly synchronized manner, while other CPs in another CP cluster that also process ingress traffic do not explicitly cooperate with each other or with other clusters. In these cases you should expect to find (or to provide) different CP programs and their source files should follow a naming convention that distinguishes their respective roles.

The object files (\*.o) and library files (\*.o) that result from a build are typically placed in the apps\application\run\obj\variant\cprc\ and apps\application\run\lib\variant\cprc\ directories, respectively.

The application's CPRC executable file(s) (\*.dcp) and its corresponding map file (\*.map) are typically placed in the apps\application\run\bin\variant\ directory.

Note that the application typically uses a naming convention for the CPRC executable(s) that includes the application identifier and the suffix "Cp", such as **oc3SarQCp.dcp** in the AAL-5 SAR application.

For an application that uses different CPs to handle different protocols, look for (or provide) a naming convention that distinguishes the executable files, such as **enetCp.dcp**, **gbeRxCp.dcp**, **gbeTxCp.dcp**, and **posCp.dcp** in the Packet Over SONET to Gigabit Ethernet Switch application.

# Microcode Programs

Microcode programs (or *microprograms*) that are targeted to run on the Channel Processor SDPs or on the Fabric Processor's FDPs are typically located under a subdirectory named **apps**\application\chip\np\sdp\src\.

There is a distinct microprogram for each SDP microprocessor or FDP microprocessor that participates in the application's processing of ingress and egress traffic. Notice the naming conventions that each C-Ware Application Library application uses to differentiate its SDP and FDP microprograms.

SDP and FDP microprograms are built in a different fashion from XPRC and CPRC programs. Specifically, the output of compilation of microcode is a binary file that

contains writable control store (WCS) and CAM contents. In contrast, the output of a program for one of the RCs is a binary file in MIPS-like ELF format.

The compilation for SDP microprograms happens in two phases:

- 1 Compilation of the program by the C-Ware Microcode Assembler (which is actually a C compiler) to verify syntax and generation of an executable that is native to the development workstation (that is, Windows NT or Sun SPARC Solaris).

- **2** Execution of that workstation-native executable to produce a binary image of the SDP's or FDP's WCS and CAM contents that become included in the application's package file.

By default, the CST's Microcode Assembler suppresses output of all build-time messages except error messages. The only information echoed to standard output is the execution of the executable that produces the WCS and CAM contents.

A by-product of every microprogram build is a log file (\*.log) that lists all output produced by the Microcode Assembler. This file is placed in the directory where the microcode executable file is written. The log file lists:

- The names and offsets of each label defined in the microprogram

- The compiled form of all CAM contents

- The number of CAM entries that were compiled

- The number of microcode instructions used in the program and the percentage of the WCS that the program uses

- The ID number of each general purpose register for the target SDP/FDP microprocessor that was not used.

# **Dependency Checking**

An important task of a build system for software development is to ensure that, when producing an executable image, the object files are up to date with respect to the other object files in the application — especially those that share structures in header files. The CST provides this feature automatically by specifying *dependency checking* in each Makefile that builds an executable file.

The CST-supplied **cport-apps-rules.mk** and **cport-rules.mk** files contain the support for dependency checking. No changes are required to application makefiles in order to utilize this CST build system feature, as long as these two make include files are included.

The build system automatically generates dependency information for all files that are included in the build on a per-variant basis. It does this by putting the dependency information in the subdirectories under the application's .\run\deps\ subdirectory.

The following directory tree shows where the dependency information is stored:

```

application\

chip\

np\

cprc\

c5\

...

doc\

host\

offline\

run\

deps\

c5-d0-sim-debug\

cprc\

xprc\

sdp\

fdp\

...

```

The first time you build the application, certain directories (those shown above in boldface) are populated with the dependency checking information, so that subsequent builds require only a rebuild of the source files when a dependent file has changed (such as a header file).

The dependency check information is contained in files named \*.d in the appropriate directory.

### Building Programs That Perform Offline Support for Applications

Some C-Ware Application Library applications offer software that performs "offline" functionality, such as software that builds a utility (or other code that will be built into the application) for specifying the static contents for the application's routing tables. You can use this software to reduce the number of network processor cycles used early in the application's execution when run under simulation. This feature is not provided for all C-Ware Application Library applications.

Notice whether each CST-provided application provides an .\offline\ subdirectory. If so, move to a subdirectory of .\offline\ that contains its own Makefile. Use the make tool to execute that makefile to build the application's offline software.

The procedures for building and using the application's offline software are described in the application's **Readme** file—that is, the **apps**\application\doc\Readme file.

### **Summary**

In this lesson you were introduced to how the source files for a C-Ware application are organized and to the CST's build system commands. You were also introduced to the notion of a build target variant and learned that the CST's implementation of build target variants depends upon a set of environment variables. You also examined the CST directory scheme that supports building C-Ware applications for C-Port network processors.

You will use this knowledge in subsequent lessons to navigate an application's directory tree to setup a simulation and debugging environment for working with a C-Ware application.

You will also use this knowledge in a later lesson as you rebuild a new version of the CST-supplied Gigabit Ethernet Switch application that you have modified.

#### **Exercises**

The following exercises help you become familiar with the CST's program building tools for C-Ware applications.

Locate the "c5e-a1-sim-debug" build target variant for the Gigabit Ethernet Switch application and rebuild its application package.

C:\C-Port\...\gbeSwitch\run\> make REV=c5e-a1-sim-debug

Follow the directions given in the file apps\gbeSwitch\doc\Readme to build the Gigabit Ethernet Switch application's offline table building code.

```

// Set the build target variant first, for subsequent make commands

C:\C-Port\...\qbeSwitch\offline\cxe\>

C:\C-Port\...\bin\configure\c5e-a1-sim-debug.bat

// Build the tables.exe executable file

C:\C-Port\...\gbeSwitch\offline\cxe\> make REV=c5e

//Run tables.exe to produce the files tle_writes.h and Tlu.state

C:\C-Port\...\gbeSwitch\offline\cxe\> tables.exe

// Use this tle_writes.h file to replace the same file found in

// ...\apps\gbeSwitch\chip\np\xprc\cxe\inc\

C:\C-Port\...\gbeSwitch\offline\cxe\>

copy tle_write.h ..\..\chip\np\xprc\cxe\inc\

// Build the Gigabit Ethernet Switch application again

C:\C-Port\...\gbeSwitch\run> make

// (The next run of this application under the C-Ware Simulator uses

// the table data specified in the file

// ...\apps\gbeSwitch\offline\cxe\tables.c.)

```

# SIMULATING THE EXECUTION OF A C-WARE APPLICATION

#### Goals

In this lesson you will learn:

- That the key components of the C-Ware Simulation Environment (CSE) are the C-Ware Simulator (bin\cwsim.exe), the pattern generation Perl scripts (bin\pg\*.pl), the bin\printTrace.pl tool for filtering pattern files into a human-readable format, and other CST-provided software objects that support certain kinds of "system" simulations

- What are the featured capabilities of the C-Ware Simulation Environment (CSE)

- How to start and stop the C-Ware Simulator

- How to direct the C-Ware Simulator at start-up to emulate a particular C-Port network processor (NP)

- The purpose of the contents of the Simulator's configuration file and command input file

- How commands in the Simulator's command input file are performed

- How preprocessor commands alter the flow of execution of a Simulator command input file

- How to halt the Simulator interactively

- What are the typically used Simulator commands

- How to navigate the Simulator's model of a C-Port NP's components

- How to direct the Simulator to produce "trace" information about the state of a C-Port NP's embedded components

- How to view performance-related counters that are maintained by the Simulator

- What are the alternative Simulator techniques for viewing application-generated messages during a simulation session

### **Prerequisites**

Before attempting this lesson, you should already be familiar with the following:

- The purposes of the C-Ware Software Toolset's (CST) top-level directories

- The organization of a C-Ware application's subdirectory tree

- How to build a particular variant of a C-Ware Application

To perform this lesson's exercises, you should have access to a workstation on which the CST Version 2.2 product has been installed.

#### Components and Capabilities of the C-Ware Simulation Environment