# S32K Microcontroller Family Technical Deep Dive

Juan Romero and Philip Pesses

Automotive Microcontrollers and Processors

June 2019 | Session #AMF-AUT-T3623

SECURE CONNECTIONS FOR A SMARTER WORLD

# Agenda

- S32K Product Family Overview

- S32K1 Technical Capabilities

- -SoC Benefits, SW, Tools, Solutions

- Technical Resources

# NXP – Supplier of Choice for Advanced Processing

### Powertrain & Vehicle Dynamics

VDS (Vehicle Dynamics & Safety)

#### Chassis, Safety, Torque and Energy Management

- Long term innovator in chassis and powertrain control

- Significant growth in safety as autonomous control drives robust fault tolerant systems

#### Body & Comfort

#### **GPIS**

(General Purpose & Integrated Solutions)

### Body Electronics Edge Nodes

- Broadest portfolio of integrated MCU+HV mixed-signal solutions

- Application specific software solutions

#### **Driver Replacement**

#### ADAS

(Advanced Driver Assistance Systems)

#### Connectivity

C&S (Connectivity & Security)

#### Networking

### DN

(Digital Networking)

#### Infotainment

#### i.MX

(Multimedia and General Purpose Applications Processor)

#### Radar, LIDAR, Vision Sensor Fusion

- #1 in radar processing

- Comprehensive radar, vision and central processing portfolio

### Vehicle Network Processing

(Gateways, Domain Controllers)

- #1 in vehicle networking and security

- End-to-end portfolio of networking devices

### Advanced Processing Solutions

- High-performance Multicore Arm® SOCs for Edge Compute

- Virtualized, Secure, Solutions with Application Specific Acceleration

#### Infotainment, Reconfigurable Cluster, Telematics, V2X, Driver Awareness

- #1 in Infotainment & Reconfigurable Cluster

- Scalable multimedia solution with audio DSP, VMCU, safety camera/display/audio, hardware virtualization, vision acceleration

# S32K Target Apps: Truly General Purpose

# General Purpose and Integrated Solutions

MPC56xxB – GP 32bit

S12 – GP 16bit

S08 - GP 8bit

KEA

arm

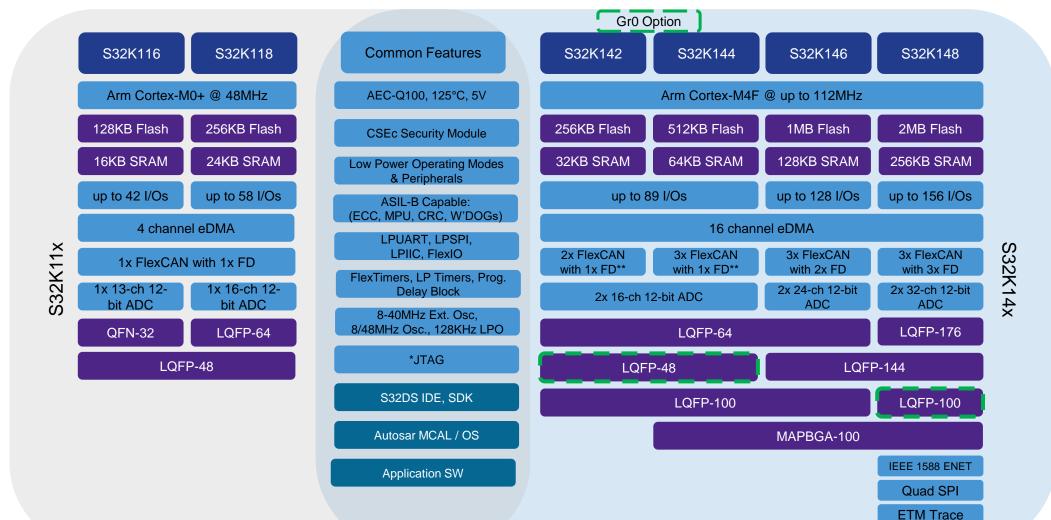

### S32K14x and S32K11x Features

2x SAI

### S32K – Future Proof

### **Superior Performance**

- High speed ARM Cortex-M4F

CPU with DSP functionality

- IEEE-754 HW floating point unit without SW overhead

- Harvard architecture accelerates data handling

- 16 bit instruction set (THUMB

2) → ~31% reduced memory usage

- Combined D/I cache for direct execution

- Concurrent, low latency bus accesses over crossbar

- Parallel DMA operation

- Dedicated EEPROM to support read while write

### Highest Energy Efficiency

- Low leakage technology (C90TFS)

- Multiple low power modes

- Internal oscillators e.g. 48MHz 1.3%

- Best in class STOP current: 25-40uA (device depended)

### Communications, Safety, Security

- CAN with Flexible Datarate (FD) option according to ISO/CD 11898-1

- HW motor control support (BLDC/PMSM)

- ISO26262 compliance (ASIL-B)

- Communication protocol emulation module (FlexIO)

- HW security engine (SHE+ compliant)

- Ethernet AVB support:

100Mbit/s Ethernet + IEEE

1588 Time Stamping + Audio

(I2S)

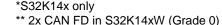

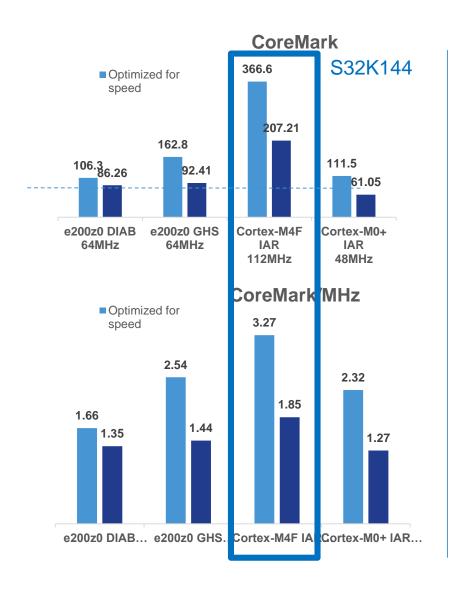

# S32K Superior Performance & Code Density

- Higher speed leads to better cache efficency

- More space for application code

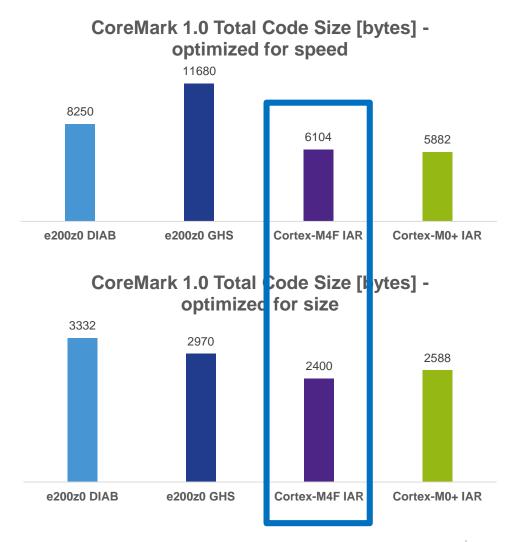

# S32K1: Superior Low Power MCU Optimized for SW

### Optimized system solution:

- Reduce average power

- Sleep as much as possible

- Minimize RUN execution

- Simplify power mode transitions

- Only switch on silicon portions

- Completely power gate unused portions in many power modes

- Only clock what is required

- Optimize clock signal switching mechanism

- Reduce number of clocked lines

- Avoid wasting power in clock edges

- Employ intelligent autonomous operation

- Switch on CPU and clock tree as little as possible

ALL modules maintained in ALL modes

ALL memory maintained in ALL modes

ALL I/O maintained in ALL modes

ALL I/O can wake up the MCU

Clock gating

Clock tree management

Peripheral grouping

Autonomous peripherals

e.g. DMA, RTC, ADC, LPUART

# S32K1 Low Power Performance Snapshot

|         | Ta (C)    | VLPS (uA) | VLPR (mA) | Stop 1 (mA) | Run (mA)* |

|---------|-----------|-----------|-----------|-------------|-----------|

| S32K116 | 25 (typ)  | 26        | 1.05      | 6.3         | 20.3      |

| S32K118 | 25 (typ)  | 27        | 1.15      | 6.4         | 21.8      |

| S32K142 | 25 (typ)  | 29        | 1.17      | 6.4         | 37.5      |

| S32K144 | 25 (typ)  | 29.8      | 1.48      | 7           | 39.6      |

|         | 105 (typ) | 256       | 1.8       | 7.8         | 40.5      |

|         | 125 (max) | 1960      | 3.18      | 12.9        | 46.8      |

| S32K146 | 25 (typ)  | 37        | 1.57      | 8           | 47.6      |

| S32K148 | 25 (typ)  | 38        | 2.17      | 8.5         | 57.7      |

- All memory and all registers and all I/O are always maintained in all modes

- All I/Os can wake up the MCU

- Parameters of multiple use cases provided in Datasheet

# **Energy-saving Peripherals**

Intelligent peripherals increasing time in sleep modes with no CPU intervention for reduced power consumption.

| Peripheral                        | Low Power Functionality                                                                                                                                                                                                                        |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DMA                               | Allows energy-saving peripherals (ex. ADC, UART and Timer/PWM) to trigger asynchronous DMA request in STOP/VLPS modes to perform DMA transfer and return to current power mode with no CPU intervention                                        |

| LPUART                            | Supports asynchronous transmit and receive operations to the bus clock supporting communication down to STOP/VLPS modes. Configurable receiver baud rate oversampling ratio from 4x to 32x allowing higher baud rates with lower clock sources |

| LPSPI                             | Supports slave mode address match wake-up function and first message capture down to STOP/VLPS modes                                                                                                                                           |

| I2C                               | Supports multiple address match wake-up function down to STOP/VLPS modes                                                                                                                                                                       |

| FTM<br>(Timer/PWM)                | Supports 16-bit timer input capture, output compare and PWM functions down to STOP/VLPS modes                                                                                                                                                  |

| LPTMR<br>(Timer/Pulse<br>Counter) | Supports 16-bit timer and pulse counter functions in all power modes                                                                                                                                                                           |

| RTC                               | Supports 32-bit seconds counter with seconds interrupt and programmable alarm in all power modes with include temperature and voltage compensation                                                                                             |

| ADC                               | Supports triggered single conversions in multiple result registers down to STOP/VLPS modes with hardware averaging and automatic compare modes                                                                                                 |

| CMP (Analog<br>Comparator)        | Supports threshold crossing detection in all power modes along with a triggered compare mode for lower average power compares                                                                                                                  |

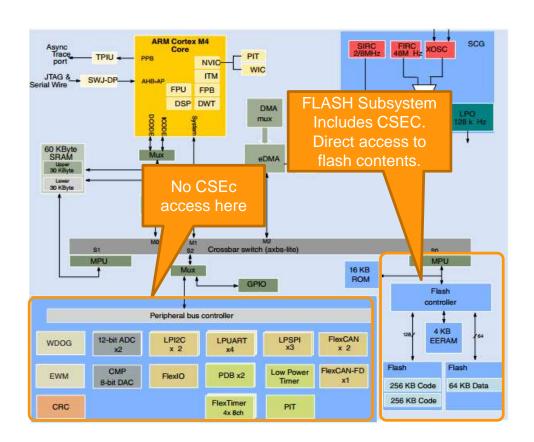

# **CSEc Security Block Diagram**

### Supports SHE Functionality

- Secure key storage: CSEc includes

17 or 20 user keys, SHE requires 10

- AES-128 encryption/decryption

- AES-128 Cypher-based Message Authentication Code (CMAC) calculation and authentication

- True and Pseudo random number generation

- User configurable Secure Boot Mode (Sequential, Strict, or Parallel Boot)

# **Security Use Cases**

### In-Vehicle Security

- Immobilizer / Component Protection

- Mileage Protection

- Secure Boot and Chain of Trust

- Secure Communication

- Digital Rights Management (DRM) e.g. BMS in EV

### Connected Vehicle Security

- Android application download

- DRM for content download/streaming

- Remote ECU firmware update

- Black-box for due government or insurance

NXP is the #1 solution provider HW + SW

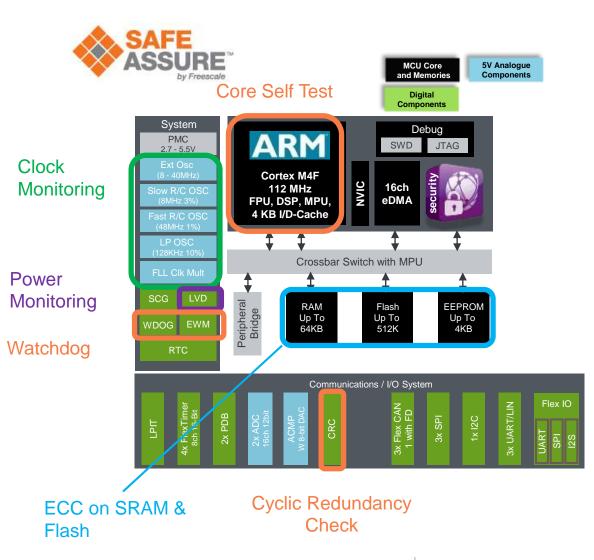

# **ASIL-B Functional Safety**

- Safety Hardware

- Power supplies

- Clocks generation

- Core platform (core, DMA, cache ...)

- Busses XBAR

- Memories NVM, SRAM

- Safety Process

- ISO 26262 development process

- Safety Support

- FMEDA

- Safety manual

- Technical support

- Safety Software

- S32K core self-test SW

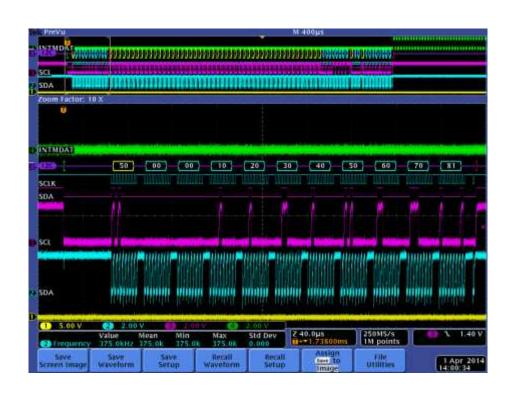

# S32K FlexIO Peripheral Capabilities

- FlexIO = Flexible Input and Output peripheral

- Programmable logic for complex output waveform generation

- Emulation of standard communication interfaces:

- UART, SPI, I2C, I2S, LCD RGB, PWM, LIN, etc.

- Low CPU overhead

- DMA support

- Drivers available

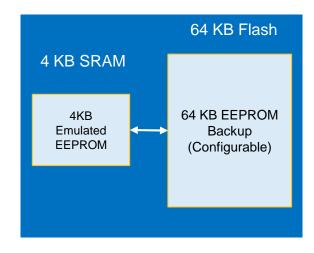

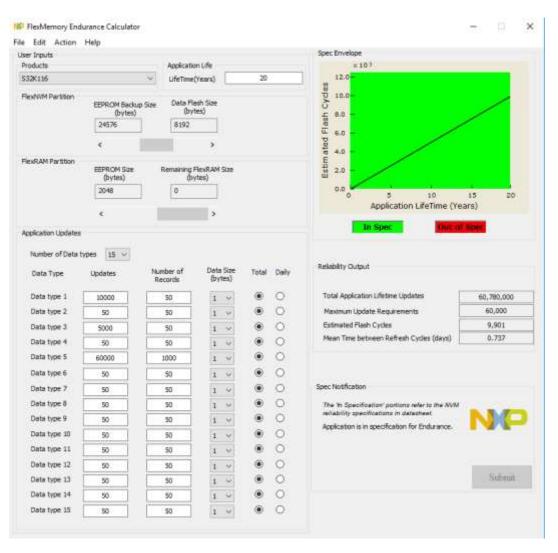

### FlexNVM – EEPROM Emulation

- Seen as RAM (read and write) from the user perspective → easy!

- Flash block in the background with a robust and proven record management methodology → Easy to use for customers

- With appropriate tools to evaluate endurance and data retention

#### **EEE Data**

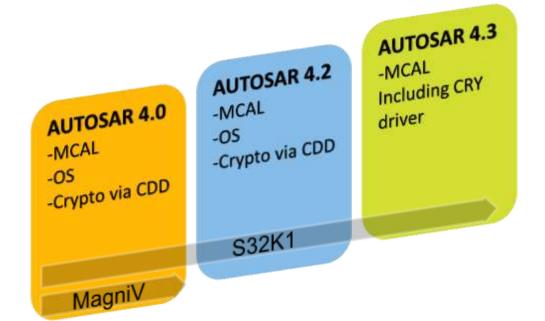

AUTOSAR Offering – The Most Complete/Supported

Ecosystem

- Supporting multiple versions

- Across entire portfolio

- Unmatched flexibility for choosing tools

- New ARCCORE Starter Kit

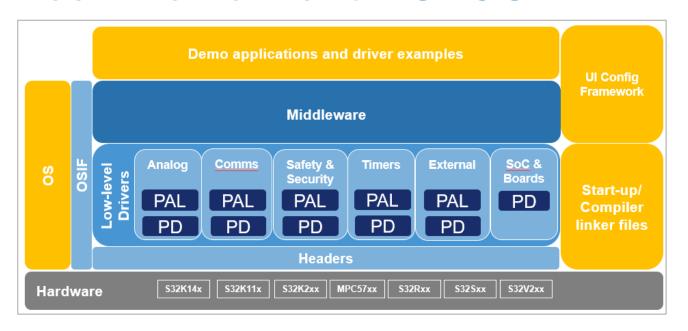

### S32 SDK Solution – The Best Alternative to AUTOSAR

### Highlights and Features

- Integrated Non-AUTOSAR Production-Grade SDK

- Contains a wide range of examples and demos

- Graphical-based Configuration

- Integrated with S32 Design Studio and other IDEs

- Layered Software Architecture

- Documented Source Code and Examples

- FreeRTOS integration

- Multiple MCU architectures and platforms supported with single codebase and consolidated releases.

- Middleware support:

- LIN stack, System basis chip, TCP/IP, Math and motor control, Core self test (safety)

### Multiple IDE integration:

S32 Design Studio, ARM Keil MDK

### Premium compiler support:

GHS, IAR, DIAB, GCC, ARM C

### Quality Level:

QM (A-SPICE L3 compliant)

### S32 Design Studio IDE – Graphical Configuration Environment

- 1. Create a new S32DS IDE New Project Wizard

- Select MCU and target package

- 2. Select Compiler

- GCC or 3<sup>rd</sup> party Premium Compiler (IAR and GHS)

- 3. Select Integration NXP tools

- Processor Expert

- Pin Mux Tool

- Device Configuration

- SDK Configuration

- Bootloader

- FreeMASTER Embedded

- 4. Select Software Integration

- S32K SDK Integrated with-in the tools

- KEA SDK Integrated with-in the tools

- Automotive Math and Motor Control Libraries (AMMCLib)

### Motor control System Solutions

**NXP GPIS MOTOR CONTROL SOLUTION** demonstrates the capability and advantages of NXP MCUs for wide variety of automotive motor control applications with three-phase PMSM and BLDC motors.

#### **MOTOR CONTROL ENABLEMENT – EASY OF USE SOLUTION**

- Modular SW Motor control library AMMCLib and MC Frameworks

- Scalable HW Motor control development kits

- Powerful Tools FreeMASTER, MCAT, MBDT, S32 DS

- Technical expertise Motor control know-how, IEEE publications, Patents

High Power – 3/6phase 48V / 150 Amps Motor type: BLDC, PMSM, ACIM

Phase number: 3/6 phase Voltage: 12 / 24 / 48 V

Current sensor: Single, dual, triple shunt Position sensor: Encoder, Hall, Resolver

Fault detection: over current, over voltage,

under voltage protection

Communication: CAN (FD), LIN

#### **NXP Tools and Ecosystem**

S32 Design Studio

FreeMASTER with MCAT

Advanced Math & Motor Control Library

Model-Based Design Toolbox

#### **VALUE PROPOSITION**

- Easy to use

- Easy to customize for wide variety of MC applications

- Reduce Time-to-Market by rapid application development

- Easy getting started & fine-tuning

- Highly optimized algorithms for basic and complex MC applications

- Recognized Centre of Excellence for motor control in automotive

# System Solutions – Released Already

#### **ISELED Driver**

- High-speed communication for creating dynamic lighting effects

- ISELED Driver for S32K

- Using FlexIO and SPI

- SDK and Autosar

### Touch Sense Reference Design

- 1D Touch Library

- SDK and Autosar

- Single chip solution for automotive TS.

- Suitable for up to 10 electrodes

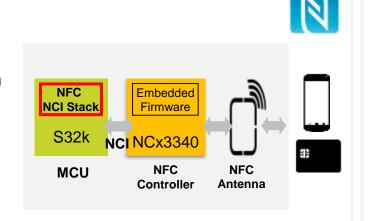

#### **NFC Stack**

- Interface between MCU and NFC controller

- Specified by NFC Forum

- Eases integration of NFC controllers

- SDK and Autosar

### **BMS** Reference Design

Turnkey solution for Safety Applications up to ASIL-C 4 NXP Devices:

- S32K144

- KEA

- SBC

- Battery Cell Management

### Additional S32K Demos and Ref. Designs

Secure CAN-FD Diagnostics (S32K + UJA1169)

Flex I/O (S32K EVBs emulating comms protocols)

CAN-FD vs. CAN CSEc vs. S/w (S32K + TFT-LCD)

Low Power Demo (S32K + LP Shield)

CAN authentication (S32K EVBs + TFT-LCDs)

Injector driver demo (S32K + PT2000)

Door Handle (S32K + MagniV + NFC)

Motorcycle ABS (S32K + SB0400)

**BLDC Motor** Control (S32K + GD3000)

DC Motor Control (S32K + HB2001)

**GPIS** Applications Resources

Engage in good technical discussions

- S32K / S12+MagniV

- > 1000 technical threads created during 2018.

Training solution for Automotive Edge Nodes.

Application of Automotive Automotive Automotive Automotive Edge Nodes.

Application of Automotive Automotive

Train yourself and customers:

- Training materials in <u>nxp.com/s32k →</u>

Training

- > 20 technical trainings posted in 2017.

Develop applications and customers. App notes posted on

- S32k / KEA

- MagniV / S12

22 Application notes posted on nxp.com/s32k

Demos/Ref. designs

Accelerate you developments.

- Contact us for additional information

- > 15 S32K1xx/MagniV demos/ref. designs available.

# Summary – S32K Product Line

### **Broad applications**

- Automotive MCU for general purpose applications

- Accelerates

automotive

software design

### Benefits to you

- Future proof

- Minimize complexity

- Maximize R&D efficiency

### Ready to go

- Rich set of collaterals & solutions available today

- Product Longevity program

# SECURE CONNECTIONS FOR A SMARTER WORLD