# SL2ICS2001DW/V1D

# I-CODE SLI Label IC bumped wafer specification on UV-tape

Rev. 3.0 — 5 February 2008

Product data sheet addendum

# 1. General description

This specification describes the electrical, physical and dimensional properties of Au-bumped sawn wafers on FFC with UV-tape of I-CODE SLI Label ICs on an NXP C075EE process and is the base for delivery of tested I-CODE SLI Label ICs.

## 2. Ordering information

#### Table 1. Ordering information

| Type number      | Package |                                     |                |  |  |

|------------------|---------|-------------------------------------|----------------|--|--|

|                  | Name    | Description                         | Odering code   |  |  |

| SL2ICS2001DW/V1D | -       | Bumped die on sawn wafer on UV-tape | 9352 795 61005 |  |  |

# 3. Mechanical specification

### 3.1 Wafer

• Diameter: 8"

• Thickness: 150 μm ± 15 μm

### 3.2 Wafer backside

Material: Si

Treatment: ground and stress release

• Roughness: R<sub>a</sub> max. 0.5 μm

R<sub>t</sub> max. 5 μm

## 3.3 Chip dimensions

Chip size: 900 x 780 μm²

Scribe lines: 80 / 80 μm

#### 3.4 Passivation

Type: sandwich structure

Material: PSG / Nitride (on top)

Thickness: 500 nm / 600 nm

**PUBLIC**

### 3.5 Au bump

Bump material: > 99.9 % pure Au

Bump hardness: 35 – 80 HV 0.005

Bump shear strength: > 70 MPa

Bump height: 18 μm

· Bump height uniformity:

- within a die:  $\pm 2 \mu m$ - within a wafer:  $\pm 3 \mu m$ - wafer to wafer:  $\pm 4 \mu m$ • Bump flatness:  $\pm 1.5 \mu m$

· Bump size:

- LA, LB

92 x 92 μm²

- VSS¹, TESTIO¹

62 x 62 μm²

• Pad size (unbumped):

LA, LB 78 x 78 μm²

VSS¹, TESTIO¹ 48 x 48 μm²

• Bump size variation:  $\pm 5 \mu m$

Under bump metallization: sputtered TiW

### 3.6 Fail die identification

Every die is electrically tested according to data sheet. Identification of chips with electrical parameters not conform with the data sheet is done by inking and wafer mapping (all dies at wafer periphery are identified as 'FAIL').

The ink information refers to unsawn wafers. At sawn wafers (on FFC) additional ICs are marked as 'FAIL' in the wafer map if damaged during the sawing process. These ICs will not be inked.

#### 3.6.1 Wafer mapping

Wafer mapping for failed die information is available on floppy-disk.

Format: IBIS format

2 of 9

<sup>1.</sup> Pad VSS and TESTIO are disconnected when wafer is sawn

PUBLIC

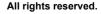

# 4. Chip orientation and bondpad locations

**PUBLIC**

# 5. Limiting values

Table 2. Limiting values[1][2]

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                 | Parameter                      | Conditions |     | Min | Max  | Unit               |

|------------------------|--------------------------------|------------|-----|-----|------|--------------------|

| $T_{stg}$              | Storage temperature range      |            |     | -55 | +140 | °C                 |

| Tj                     | Junction temperature           |            |     | -55 | +140 | °C                 |

| $V_{ESD}$              | ESD voltage immunity           |            | [3] | -   | ±2   | $kV_{peak}$        |

| I <sub>max LA-LB</sub> | Maximum input peak current     |            |     | -   | ±60  | mA <sub>peak</sub> |

| T <sub>jop</sub>       | Operating junction temperature |            |     | -25 | +85  | °C                 |

| I <sub>LA-LB</sub>     | Input current                  |            | [4] | -   | 30   | $mA_{rms}$         |

- [1] Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any conditions other than those described in the Operating Conditions and Electrical Characteristics section of this specification is not implied.

- [2] This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maxima.

- [3] MIL-STD-883D, Method 3015.7, Human body model

- [4] The voltage between LA and LB is limited by the on-chip voltage limitation circuitry (corresponding to parameter I<sub>LA-LB</sub>)

PUBLIC

## 6. Characteristics

#### 6.1 Electrical characteristics

Table 3. Characteristics [1]

| Symbol                   | Parameter                                         | Conditions                                        |            | Min    | Тур    | Max    | Unit      |

|--------------------------|---------------------------------------------------|---------------------------------------------------|------------|--------|--------|--------|-----------|

| T <sub>jop</sub> = -25 t | o 85°C                                            |                                                   |            |        |        |        |           |

| $V_{LA\text{-}LB}$       | Minimum supply voltage for READ/WRITE/EAS         |                                                   |            | ±2.5   | ±2.6   | ±2.9   | $V_{rms}$ |

| f <sub>op</sub>          | Operating frequency                               |                                                   | [2]        | 13.553 | 13.560 | 13.567 | MHz       |

| C <sub>res</sub>         | Input capacitance between LA – LB                 | $V_{LA-LB} = 2 V_{rms}$                           | [3]        | 22.3   | 23.5   | 24.7   | pF        |

| P <sub>min</sub>         | Minimum operating supply power                    |                                                   | <u>[4]</u> | -      | 280    | -      | μW        |

| m                        | Modulation of RF voltage for demodulator response | $m = \frac{V_{max} - V_{min}}{V_{max} + V_{min}}$ | <u>[5]</u> | -      | -      | -      | %         |

| t <sub>P sm</sub>        | Modulation pulse length of RF voltage             |                                                   | <u>[5]</u> | -      | -      | -      | μS        |

| t <sub>D</sub>           | Demodulator response time                         | $m \geq 10$ %, $100$ %                            | [5]        | -      | -      | -      | μS        |

| R <sub>mod</sub>         | Load modulation                                   |                                                   | [5]        | -      | -      | -      | Ω         |

| t <sub>ret</sub>         | EEPROM Data retention                             | $T_{amb} \le 55  ^{\circ}C$                       |            | 10     | -      | -      | Years     |

| n <sub>write</sub>       | EEPROM Write endurance                            |                                                   |            | 100000 | -      | -      | Cycles    |

<sup>[1]</sup> Typical ratings are not guaranteed. These values listed are at room temperature.

# 7. Final wafertest specification

• Mininum yield per wafer: 30 % of 35416 potential good dies.

• Minimum yield per lot: 30 %

5 of 9

<sup>[2]</sup> Bandwidth limitation (±7 kHz) according to ISM band regulations.

<sup>[3]</sup> Measured with an HP4285A LCR meter at 13.56 MHz.

<sup>[4]</sup> Including losses in resonant capacitor and rectifier.

<sup>[5]</sup> Refer to ISO/IEC 15693-2 and 15693-3 including pulse shapes and tolerances; proper coil design assumed.

**PUBLIC**

# 8. Hints for label IC encapsulation

### 8.1 Protection against visible light

As a result of the ultra low power design of the I-CODE SLI Label IC some analogue circuits on the chip are light sensitive. This means that common sun light can impact the operation of the label if the chip is not protected against visible light radiation.

Measurements have shown that a radiation of  $E_{max} = 60 \text{ W/m}^2$  (spectrum: 400 to 1000 nm) causes a reduced operating range of the plain chip.

Measurements of direct sunlight in summer deliver values up to 260 W/m<sup>2</sup>.

To ensure proper operation an expected minimum radiation reduction factor of approx. 9  $(2 \times 260/60 = 8.7)$  must be provided by the encapsulation. That means special care has to be taken to ensure a sufficient light protection of the I-CODE SLI Label IC (e.g. non translucent encapsulation or underfiller, ...) according to application requirements.

### 8.2 Protection against UV light

An EEPROM memory, as it is also used in the I-CODE SLI Label IC, has some principle sensitivity to UV light (applies to EEPROM-technology in general).

Thus strong UV exposure in the production of inlets/labels has to be avoided. UV protection has to be ensured using appropriate assembly methods.

### 8.3 Resistance to x-rays

X-ray exposure on comparable NXP ICs (with even smaller feature size) caused neither a long term influence on the behaviour of the ICs nor on the data retention of the EEPROMs.

#### 9. References

- Data sheet "I-CODE SLI Label IC, functional specification"

- Data sheet "General specification for 8" wafer"

- Data sheet "General quality specification"

- Application note "I-CODE coil design guide"

- Application note "Specification of the IBIS wafermap"

- Application note "Handling and processing of sawn wafers on UV dicing tape"

PUBLIC

# 10. Revision history

### Table 4. Revision history

| Document ID | Release date                        | Data sheet status  | Change notice | Supersedes |

|-------------|-------------------------------------|--------------------|---------------|------------|

| 150030      | 5 February 2008                     | Product data sheet | -             | -          |

|             | <ul> <li>Initial version</li> </ul> |                    |               |            |

PUBLIC

# 11. Legal information

#### 11.1 Data sheet status

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions"

- The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

#### 11.2 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

#### 11.3 Disclaimers

**General** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected

to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.

Terms and conditions of sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

### 11.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I-CODE — is a trademark of NXP B.V.

#### 12. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

# SL2ICS2001DW/V1D

## I-CODE SLI Label IC bumped wafer specification on UV-tape

PUBLIC

# 13. Tables

| Table 1. | Ordering information              | Table 3. | Characteristics [1] | 5 |

|----------|-----------------------------------|----------|---------------------|---|

| Table 2. | Limiting values <sup>[1][2]</sup> | Table 4. | Revision history    | 7 |

# 14. Figures

Fig 1. Chip orientation and bondpad locations......3

# 15. Contents

| 1     | General description                    | 1 |

|-------|----------------------------------------|---|

| 2     | Ordering information                   | 1 |

| 3     | Mechanical specification               | 1 |

| 3.1   | Wafer                                  |   |

| 3.2   | Wafer backside                         |   |

| 3.3   | Chip dimensions                        |   |

| 3.4   | Passivation                            |   |

| 3.5   | Au bump                                |   |

| 3.6   | Fail die identification                |   |

| 3.6.1 | Wafer mapping                          | 2 |

| 4     | Chip orientation and bondpad locations | 3 |

| 5     | Limiting values                        | 4 |

| 6     | Characteristics                        | 5 |

| 6.1   | Electrical characteristics             | 5 |

| 7     | Final wafertest specification          | 5 |

| 8     | Hints for label IC encapsulation       | 6 |

| 8.1   | Protection against visible light       |   |

| 8.2   | Protection against UV light            |   |

| 8.3   | Resistance to x-rays                   | 6 |

| 8.3   | Resistance to x-rays                   | 6 |

| 9     | References                             | 6 |

| 10    | Revision history                       | 7 |

| 11    | Legal information                      | 8 |

| 11.1  | Data sheet status                      | 8 |

| 11.2  | Definitions                            | 8 |

| 11.3  | Disclaimers                            | 8 |

| 11.4  | Trademarks                             | 8 |

| 12    | Contact information                    | 8 |

| 13    | Tables                                 | 9 |

| 14    | Figures                                | 9 |

| 15    | Contents                               | 9 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.