# AN12207 SCI2C Protocol Specification Rev. 1.6 — 11 June 2018

**Application Note**

#### **Document information**

| Info     | Content                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Keywords | I <sup>2</sup> C-bus, Smart Card, APDU mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Abstract | This document contains the definition of a Smart Card I <sup>2</sup> C (SCI2C)<br>Protocol using an Inter-IC (I <sup>2</sup> C) based physical interface and data link<br>layer, a SMBus based network layer and bus protocol as well as a<br>mapping layer to convey ISO/IEC 7816-4 based communication.<br>It defines a model where the terminal (Reader/writer) is mapped to an I <sup>2</sup> C<br>master device and the card is mapped to an I <sup>2</sup> C slave device. It allows for<br>control and data communication between the communication partners<br>and provides a mapping of the so-called Application Protocol Data Units.<br>It supports microcontroller driven smart cards with full featured operating<br>systems supporting APDUs (Application Protocol Data Units) operating in<br>an I <sup>2</sup> C-bus environment. |  |

#### **Revision history**

| Rev | Date     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.6 | 20180611 | Editorial updates, no content change                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1.5 | 20170131 | Correct note in chapter 13.10.3 / Figure 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1.4 | 20151217 | Add additional recommendation for cold reset<br>See chapter 4.2, 11.1 and 13.4                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1.3 | 20141008 | Fix some minor mistake in figures and examples;<br>add parameter FWI <sub>DEF</sub><br>add definition of Protocol Binding Confirmation code ( <u>Table 14</u> )<br>correct definition for protocol exception trigger in chapter <u>13.9</u><br>corrections/clarification in chapters <u>13.10.3</u> and <u>13.10.4</u><br>adding chapter <u>24"I2C address (Informative)</u> "<br>correct Maximum Data Bytes (Slave to Master) <u>Table 9</u><br>correct Maximum Data Bytes (Master to Slave) <u>Table 11</u> |

| 1.2 | 20120426 | Correction of CDB <sub>SM,MAX</sub> values;<br>update of value definition table (CDB, t <sub>CMDG</sub> , t <sub>PDE</sub> );<br>removal of slave NACK requirement on wrong EDCCB;<br>clean-up of missing references                                                                                                                                                                                                                                                                                          |

| 1.1 | 20100929 | Add list of abbreviations; add some missing requirements; fix some mistakes in figures and<br>in the examples; add a bus clear procedure; change text on how to split payload streams<br>into chunks; switch from CRC to LRC based error detection code; switch to a different<br>block splitting; add status command; add missing requirement for the communication<br>speed data element; add frame waiting time parameter as new low level data element                                                    |

| 1.0 | 20100624 | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

# **Contact information**

For additional information, please visit: <u>http://www.nxp.com</u>

# 1. Introduction

## 1.1 Scope

The scope of this document covers the definition of a Smart Card I2C (SCIIC) Protocol using an Inter-IC (I2C) based physical interface and data link layer, a SMBus based network layer and bus protocol as well as a mapping layer to convey [7816-4] based communication.

## 1.2 Audience

This document is intended for the use of manufacturers wanting to implement a master device or a slave device supporting SCIIC.

# **1.3 Applicable Document and References**

The following documents contain provisions that are referenced in this specification. The latest version including all published amendments applies unless a publication data is explicitly stated.

| [7816-3]  | ISO/IEC 7816-3: "Identification cards - Integrated circuit cards<br>– Card with contacts – Electrical interface and transmission<br>protocols",<br>Third edition 2006-11-01                                                 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [7816-4]  | ISO/IEC 7816-4: "Identification cards - Integrated circuit cards<br>- Organization, security and commands for interchange",<br>Second edition 2005-01-15                                                                    |

| [7816-10] | ISO/IEC 7816-10: "Identification cards - Integrated circuit(s) cards with contacts – Electronic signals and answer to reset for synchronous cards", Third edition 2003-11-01                                                |

| [8825-1]  | ISO/IEC 8825-1: "Information technology — ASN.1 encoding<br>rules: Specification of Basic Encoding Rules (BER), Canonical<br>Encoding Rules (CER) and Distinguished Encoding Rules<br>(DER) ",<br>Fourth edition 2008-12-15 |

| [13239]   | ISO/IEC 13239: "Information technology —<br>Telecommunications and information exchange between<br>systems — High-level data link control (HDLC) procedures",<br>Third edition 2002-07-15                                   |

| [I2C-bus] | UM10204 - I <sup>2</sup> C-bus specification and user manual,<br>Rev. 03, 19 June 2007,<br>NXP Semiconductors,<br>http://ics.nxp.com/support/documents/interface/pdf/i2c.bus.sp<br>ecification.pdf                          |

| [PMBUS-1] | Power System Management Protocol Specification,<br>Part I – General Requirements, Transport and Electrical<br>Interface,<br>Revision 1.1, 5 February 2007,<br>SMI Forum<br>http://pmbus.org/specs.html                      |

| [PMBUS-2] | Power System Management Protocol Specification,<br>Part II – Command Language,<br>Revision 1.1, 5 February 2007,<br>SMI Forum<br>http://pmbus.org/specs.html |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [RFC2119] | Key words for use in RFCs to Indicate Requirement Levels, March 1997                                                                                         |

| [SMBUS]   | System Management Bus Specification,<br>Version 2.0 August 3 <sup>rd</sup> 2000,<br>SBS Implementers Forum,<br><u>http://www.sbs-forum.org/specs/</u>        |

# **1.4 Notational Conventions**

## 1.4.1 Notations

The following notations apply to this document:

| Notation Description |                                                                        |

|----------------------|------------------------------------------------------------------------|

| XYh                  | Hexadecimal notation.                                                  |

|                      | Values expressed in hexadecimal form are followed by a lower case "h". |

|                      | For example, 27509 decimal is expressed in hexadecimal as 6B75h.       |

| XYb                  | Binary notation.                                                       |

|                      | Values expressed in binary form are followed by a lower case "b".      |

|                      | For example, 82h hexadecimal is expressed in binary as 10000010b.      |

| хх                   | More than one value possible.                                          |

| -                    | Bit position that is not relevant for the definition of the element.   |

#### Table 1 Notational Conventions

#### 1.4.2 Bit numbering

The bit numbering applied in this document is b0 to b7. The bit b0 refers to the least significant bit of a byte and b7 to the most significant bit of a byte.

I.e. a value of 10000000b is a byte (eight bits in size) where the '1' is the most significant bit b7.

#### 1.4.3 Reserved for Future Use

An entity transmitting bytes or bits defined as RFU (Reserved for Future Use) SHALL set these bytes or bits to the value indicated, or to zero if no value is given.

An entity receiving bytes or bits defined as RFU SHALL disregard these bytes or bits and SHALL keep the same interpretation of any other field of the whole response, unless explicitly stated otherwise.

Note: An entity transmitting bytes or bits defined as Any Value may set these bytes or bits to any specific value. How to process bytes or bits received that are defined as Any Value is out of scope of this specification, where not explicitly stated otherwise.

#### 1.4.4 Drawings

The I<sup>2</sup>C-bus and SMBus packet drawings as used within this specification follow the definitions as made in [SMBUS].

#### 1.4.5 Logic Levels

A logic '0' on the SCL and SDA lines are called LOW and a logic '1' is called HIGH within this specification.

#### 1.4.6 TLV data object

This specification is using simple TLV (Tag Length Value) data objects to encode some of the information being exchanged between slave device and master device. The encoding used follows the definition of BER-TLVs (Basic Encoding Rules-TLV) as defined within [7816-4] and [8825-1].

A TLV data object consists of two to three fields:

Tag field (REQUIRED)

- Length field (REQUIRED)

- Value field (OPTIONAL)

#### 1.4.6.1 Tag field of a TLV data object

The tag field consists of a single byte encoding the tag type and number. For an encoding compatibility with [7816-4] and [8825-1] the bits b6 and b7 SHALL both be set to 1b to indicate a tag in private class and bit b5 SHALL be set to 0b to indicate a primitive encoding of the data object.

#### 1.4.6.2 Length field of a TLV data object

The length field consists of a single byte encoding a number N in the range from 0 to 127. The length field content in the range from 128 to 255 is RFU.

#### 1.4.6.3 Value field of a TLV data object

The value field consists of N bytes encoding the value information of the tag. The value field is not present in case the length field contains an N equal to 0.

# 1.5 Special Word Usage

The key words "MUST", "MUST NOT", "REQUIRED", "SHALL", "SHALL NOT", "SHOULD", "SHOULD NOT", "RECOMMENDED", "MAY", and "OPTIONAL" in this document are to be interpreted as described in [RFC2119].

## **1.6 Abbreviations**

This chapter provides an overview of the abbreviations as used in this document.

| AIDApplication IDentifierAPDUApplication Protocol Data UnitASCIIAmerican Standard Code for Information InterchangeATRAnswer To ResetBERBasic Encoding RulesBRBit RateB UFBUFferCDBCommand Data ByteCLACLAss |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASCIIAmerican Standard Code for Information InterchangeATRAnswer To ResetBERBasic Encoding RulesBRBit RateB UFBUFferCDBCommand Data Byte                                                                    |

| ATRAnswer To ResetBERBasic Encoding RulesBRBit RateB UFBUFferCDBCommand Data Byte                                                                                                                           |

| BERBasic Encoding RulesBRBit RateB UFBUFferCDBCommand Data Byte                                                                                                                                             |

| BRBit RateB UFBUFferCDBCommand Data Byte                                                                                                                                                                    |

| B UFBUFferCDBCommand Data Byte                                                                                                                                                                              |

| CDB Command Data Byte                                                                                                                                                                                       |

| ,                                                                                                                                                                                                           |

| CLA CLAss                                                                                                                                                                                                   |

|                                                                                                                                                                                                             |

| CMD CoMmanD                                                                                                                                                                                                 |

| CRC Cyclic Redundancy Chec                                                                                                                                                                                  |

| C-APDU Command-APDU                                                                                                                                                                                         |

| DEF DEFault                                                                                                                                                                                                 |

| EDC Error Detection Code                                                                                                                                                                                    |

| EDCCB Error Detection Code Control Byte                                                                                                                                                                     |

| FWI Frame Waiting Integer                                                                                                                                                                                   |

| HDLC High-level Data Link Control                                                                                                                                                                           |

| IEC International Electrotechnical Commission                                                                                                                                                               |

| INIT INITial                                                                                                                                                                                                |

| INS INStruction                                                                                                                                                                                             |

| ISO International Organization for Standardization                                                                                                                                                          |

| I/O Input/Output                                                                                                                                                                                            |

| Abbreviation<br>LEN<br>LRC<br>MAX<br>MD<br>MDPV<br>MDPVMA<br>MDPVMI<br>MS<br>N<br>P1<br>P2<br>PBS<br>PCB<br>PC<br>PBS<br>PCB<br>PC<br>PBS<br>PCB<br>PC<br>PBS<br>PCB<br>PC<br>PBS<br>PCB<br>PC<br>PBS<br>PCB<br>PC<br>PBS<br>PCB<br>PC<br>PBS<br>PCB<br>PC<br>PBS<br>PCB<br>PC<br>PBS<br>PCB<br>PC<br>PBS<br>PCB<br>PC<br>PD<br>PE<br>PE<br>PEC<br>PWRSAV<br>RATR<br>RFU<br>RST<br>RATR<br>RFU<br>SS<br>SADDR<br>SS<br>SCI2C<br>SCL<br>SDA<br>SDPV<br>SDPVMA | LENgth<br>Longitudinal Redundancy Code<br>MAXimum<br>Master Delay<br>Master Device Protocol Version<br>Master Device Protocol Version MAjor<br>Master Device Protocol Version Minor<br>Master Device Protocol Version Minor<br>Master to Slave<br>Number<br>Parameter Slave<br>Number<br>Parameter 1<br>Parameter 2<br>Protocol Binding Selection<br>Protocol Control Byte<br>Power Down<br>Parameter Exchange<br>Packet Error Code<br>PoWeR SAVing<br>Read Answer To Reset<br>Reserved for Future Use<br>ReSeT<br>Response-APDU<br>Tag Length Value<br>Slave<br>Slave ADDRess<br>Smart Battery System<br>Smart Card Inter-IC<br>Serial Clock Line<br>Serial Data Line<br>Slave Device Protocol Version |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCI2C                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Smart Card Inter-IC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SDA<br>SDPV                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Serial Data Line<br>Slave Device Protocol Version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

#### **Table 2 Abbreviations**

# 2. Overview

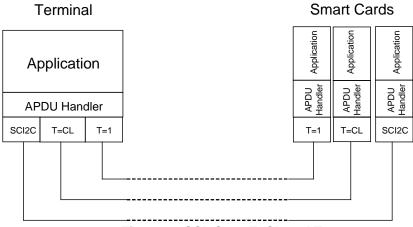

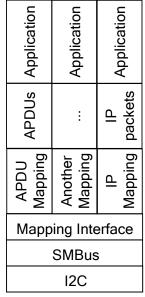

This document contains the definition of a Smart Card I<sup>2</sup>C (SCIIC) Protocol using an Inter-IC (I<sup>2</sup>C) based physical interface and data link layer, a SMBus based network layer and bus protocol as well as a mapping layer to convey [7816-4] based communication.

It defines a model where the terminal (Reader/writer) is mapped to an I<sup>2</sup>C master device and the card is mapped to an I<sup>2</sup>C slave device. It allows for control and data communication between the communication partners and provides a mapping of the so called Application Protocol Data Units.

The combination of above allows for control and data exchange between the communication partners and provides a mapping of the so called APDUs (Application Protocol Data Units, see [7816-4]). It supports microcontroller driven smart cards with full featured operating systems supporting APDUs operating in an I<sup>2</sup>C-bus environment (see [I2C-bus]).

The protocol defined in this document allows a smart card to operate besides slaves on a single bus with the support for multi-slave and multi-master as well.

The content of this document is not to be confused with memory cards compatible with [7816-10] and is also not related to document of manufactures that do map functionality of synchronous cards to specific defined APDUs to access them in an abstract way.

The informative chapters at the end of this specification, declared by the term informative in brackets after the chapter title, are for information only and do in no way overrule any definitions.

# 3. Signals

This chapter defines the electrical signals to be supported by a master device and a slave device compliant to this specification.

The following signals SHALL be supported:

- SCL serial clock line

- SDA serial data line

The following signal MAY be supported by a slave device:

- RST\_N reset signal input

- Note: This specification does not contain the assignment of signals to specific pins of a package. This is left to the device and package related specification of a product.

# 4. **Operating Conditions**

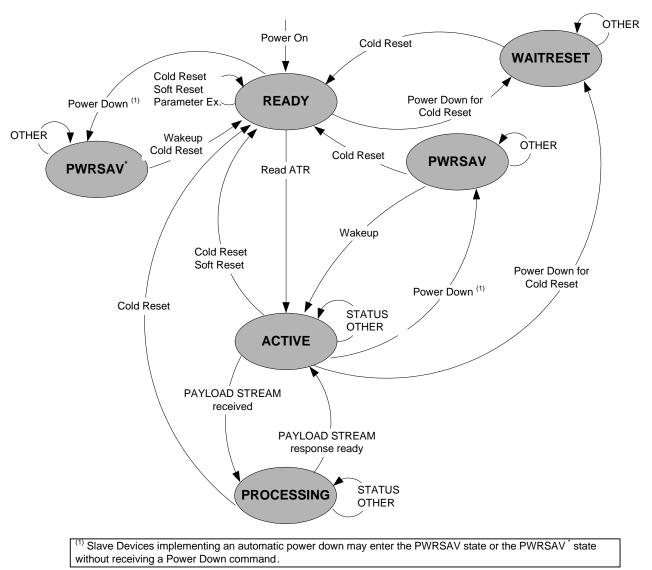

This chapter describes the basic operation conditions as well as the state changes based on the commands received. The state machine of the slave device is provided in chapter 18.

#### 4.1 Power On

The slave device SHALL enter the READY state when supply is applied and the RST\_N signal is set to high state. In case the RST\_N signal is set to low state when supply is applied the slave device will only enter the READY state after the end of the sequence as defined in chapter <u>13.4</u>.

# 4.2 Reset

The slave device SHALL support means to be reset without the need to disconnect the power supply. A reset is used by the master device to reset all non-persistent states inside the slave device. There are two kinds of resets defined:

- Cold Reset (RECOMMENDED) and

- Soft Reset (REQUIRED)

The Cold Reset is issued by a sequence as defined in chapter <u>13.4</u>.

The Soft Reset is issued by a command as defined in chapter <u>13.5</u>.

The Cold Reset sequence as well as the Soft Reset command SHALL reset all nonpersistent information inside the slave device and it SHALL switch the slave device into its READY state.

Note: In case of exceptional processing or a failure to recover from communication issues the slave SHALL be reset using a Cold Reset or a power cycle.

# 4.3 Power Saving

The slave device SHALL support means to switch to a power saving mode. This specification allows for devices to implicitly switch to a PWRSAV (PoWeR SAVing) state but it also defines two special commands to enable the PWRSAV state:

- Power Down and

- Power Down for Cold Reset

The Power Down command puts the device into the PWRSAV state when the slave device is in ACTIVE state or it puts the device into the PWRSAV<sup>\*</sup> state when the slave device is in READY state. From there the slave device awaits a Wakeup command to switch back to its original state before entering the power saving mode. The Power Down command as well as the PWRSAV state and the PWRSAV<sup>\*</sup> state SHALL NOT reset non-persistent states inside the slave device.

The Power Down for Reset command puts the device into the WAITRESET state. From there the slave device will only react on a Cold Reset.

The Power Down commands are defined in chapter  $\underline{13.1}$  and chapter  $\underline{13.2}$  and the Wakeup command is defined in chapter  $\underline{13.3}$ .

# 5. I<sup>2</sup>C-bus

The I<sup>2</sup>C-bus as referred within this document is defined in [I2C-bus].

The SCL and SDA signals created by the master device SHALL be compliant with the input voltage definitions of [I2C-bus].

The SCL and SDA signals created by the slave device MAY be compliant with the input and voltage definitions of [I2C-bus].

The master device SHALL support a 7-bit slave addressing.

The master device MAY apply a bus clear as defined in [I2C-bus] and it SHALL only use the bus clear in case it detects the unlikely event where the SDA signal is stuck LOW creating a bus jam.

The slave device SHALL support a 7-bit addressing.

Note: There are no requirements for a slave device to be fully compliant to the input and voltage definitions of [I2C-bus] to allow slave devices with generic I/O driver capabilities to comply with this specification. It's left to the system implementation or system integrator to identify required and suitable combinations of master devices and slave devices based on the design of the bus, the routing of the signals and the combination of devices hooked on the bus.

# 6. SMBus

# 6.1 Generic Requirements

The SMBus (System Management Bus) as referred within this document refers to [SMBUS]. The definitions in this chapter specify options to be supported and possible constraints compared to [SMBUS].

The master device SHALL support the clock low extension as specified in [SMBUS].

The slave device MAY use the clock low extension as specified in [SMBUS] in case it can't support the speed of the master device at certain times.

The PEC (Packet Error Code) as specified in [SMBUS] SHALL NOT be used.

The slave device MAY NOT support the SMBus host notifies protocol as specified in [SMBUS].

The slave device SHALL acknowledge its own address if not otherwise stated in this specification.

The slave device MAY NOT support the address resolution proposal as specified in [SMBUS].

The slave device MAY NOT support the SMBSUS signal as specified in [SMBUS].

The slave device MAY NOT support the SMBALERT signal as specified in [SMBUS].

- Note: Even though the PEC is not supported the integrity of higher layer data exchanged is taken care of via an error detection code specified in this specification.

- Note: There are no requirements for a slave device to be fully compliant to the input and voltage definitions of [SMBUS] to allow slave devices with generic I/O driver capabilities to comply with this specification. It's left to the system implementation or system integrator to identify required and suitable combinations of master devices and slave devices based on the design of the bus, the routing of the signals and the combination of devices hooked on the bus.

# 7. PMBus

The PMBus (Power Management Bus) as referred within this document refers to [PMBUS-1] and [PMBUS-2]. The definitions in this chapter specify options to be supported and possible constraints compared to [PMBUS-1] and [PMBUS-2].

The master device as specified in this specification is not compliant to [PMBUS-1] and [PMBUS-2] even though it's be possible to implement a master device supporting both specifications.

The slave device as specified in this specification is not compliant to [PMBUS-1] and [PMBUS-2]. Anyhow most of the definitions in [PMBUS-1] are taken from [SMBUS] and therefore do not differ a lot.

In general, the maximum amount of data bytes within a SMBus packet, as defined within this specification, is compliant to the definitions made in [PMBUS-1].

The command code values as used for the activation of a slave device according to this specification are not compliant to PMBus but they are not overlapping existing commands as defined within [PMBUS-2].

Note: The commands Wakeup, SoftReset as well as Read Answer to Reset do all use command codes declared as Reserved within [PMBUS-2] and therefore a detection and separation of slave devices implementing this specification vs. implementing the PMBus specifications is possible.

# 8. Slave Address Assignment

The default address of a slave device compliant to this specification SHALL be within range of SADDR (Slave ADDRess, see chapter <u>21</u>).

The slave device MAY be configurable to use another slave address. The means to configure the actual used slave address is out of scope of this specification.

The slave device SHALL acknowledge addresses provided by the master devices matching its own assigned address if not otherwise specified in this document.

The slave device SHALL NOT acknowledge addresses provided by the master device not matching the address assigned to it.

Master devices compliant to this specification SHALL address slave devices compliant to this specification only by using the single address the slave device is configured to respond at.

# 9. Communication Speed

The master device SHALL support byte level clock stretching and it MAY support bit level clock stretching.

The master device SHALL use an initial maximum communication speed of BR<sub>INIT</sub> (Bit Rate INITial, see chapter <u>21</u>) in case it does not support bit level clock stretching.

The slave device SHALL only use byte level clock stretching when being addressed by the master device using a communication speed of up to BR<sub>S,MAX</sub>.

The slave device SHALL be able to slow down the bit rate by using bit level clock stretching when being addressed by the master device using a communication speed above BR<sub>S,MAX</sub>.

Note: The initial maximum communication speed may be limited by restrictions of other slave devices on the same bus.

# **10. Timing Requirements**

# **10.1 Command Delay Time**

The master device SHALL wait at least  $t_{CMDG}$  (time, ComManD Guard, see chapter 21) between two commands issued on the bus. This time SHALL be the time between the end of a Stop Condition of a previous command and the start of the Start Condition of a following command.

The slave device SHALL be able to receive a next command within  $t_{CMDG}$  after the end of a Stop Condition of a previous command if not otherwise stated within this specification.

Note: The Command Delay Time does not apply for a single command using a Repeated Start Condition.

# **11. Bus Error conditions**

## 11.1 Bus Jam

A bus jam describes a condition where either SCL or SDA or both SCL and SDA stay low continuously.

Note: In case of SCL stay LOW, the slave SHALL be reset using a Cold Reset.

## 11.2 No Address Acknowledgement

NoAddrAck (No Address Acknowledgement) is a condition where the slave device does not acknowledge a slave address sent by the master device.

#### 11.3 No Data Acknowledge

NoDataAck (No Data Acknowledgement) is a condition where either the slave device does not acknowledge a byte sent by the master device or where the master device does not acknowledge a byte sent by the slave device.

# 12. Bus Packets

The master device and the slave device SHALL implement the following SMBus packets:

- Quick command

- Send byte

- Block write

- Block read

The packets listed above SHALL be implemented in compliance with [SMBUS] if not otherwise stated in this specification.

The master device SHALL use the above packets when addressing a slave device compliant to this specification.

The master device SHALL NOT combine the above packets using repeated start conditions when addressing a slave device compliant to this specification.

The master device SHALL indicate the data direction by a single bit following the slave address.

The master SHALL indicate a master to slave data direction by setting the bit to 0b (Wr) and a slave to master data direction by setting the bit to 1b (Rd).

The command code definition as contained in [SMBUS] is used by this specification to exchange protocol related information called PCB (Protocol Control Byte). For the use of a PCB, which is needed in both directions, this specification extends the definitions thereof (see chapter 12.2 and chapter 12.4).

The following chapters define the used SMBus packets in full detail. The representation used for the figures equals the one used in [SMBUS]. It describes the data on the SCL line in a timeline where the first field shown (most top left in the figures) is the first data sent and the last field shown (most bottom right in the figures) is the last data sent. The number above a field defines the number of data bits of the field when sent. The number below a field defines the logical level of the SDA signal at that time.

Note: Even though this specification extends [SMBUS] to exchange a PCB in both directions the coding of the packet format as such has not been changed. This

has been kept to allow hosts using an SMBus compliant master device to exchange commands according to this specification as well. As a result of the decision to stay backwards compatible the data exchange capabilities between the master device and a slave device is asymmetrical. A master device can send one byte more to the slave in a single command compared to the number of bytes a slave can return in a single command.

Note: A repeated start condition is to be used by the master device for the Block read packet only. The slave device does not recognize bus packets when combined using repeated start conditions.

# 12.1 Quick Command

The following figure shows the format of the Quick command packet:

| 1 | 7     | 1     | 1 | 1 |

|---|-------|-------|---|---|

| S | SADDR | Rd/Wr | Α | Ρ |

Figure 1 Quick command packet

Note: This specification uses the read indication and the write indication of the Quick packet to code a command. This is done to ease the protocol implementation and to optimize the amount of data exchanged.

# 12.2 Send Byte

The following figure shows the format of the Send byte packet:

| 1 | 7     | 1  | 1 | 8   | 1 | 1 |

|---|-------|----|---|-----|---|---|

| S | SADDR | Wr | А | PCB | А | Ρ |

Figure 2 Send byte packet

Note: Devices according to this specification exchange a PCB within the single byte contained within the Send byte whereas [SMBUS] specifies a generic data byte.

# 12.3 Block write

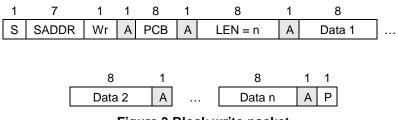

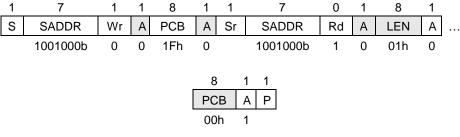

The following figure shows the format of the Block write packet:

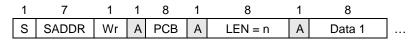

Figure 3 Block write packet

The field LEN within the Block write encodes the number of data bytes being sent by the master device to the slave device.

The master device SHALL be able to send any number from 0 up to and including  $CDB_{MS,DEF}$  (Command Data Bytes, Master to Slave, DEFault, see chapter <u>21</u>) data bytes in a Block write packet to a slave device.

The master device SHALL be able to detect that the slave device does not acknowledge one of the bytes within a packet and in such case of an unexpected not acknowledge the master device SHALL raise a Protocol Exception.

The master device SHALL create a Stop Condition to indicate the end of a write transfer.

The slave device SHALL be able to retrieve any number from 0 up to and including CDB<sub>MS,DEF</sub> data bytes in a Block write packet from a master device.

The slave device SHALL acknowledge all bytes received from the master device.

The slave device SHALL be able to detect a mismatch of data bytes received within the Block write packet compared to the LEN byte as contained within the packet and in such case of a mismatch the slave device SHALL raise a Protocol Exception (see chapter 14.2).

# 12.4 Block read

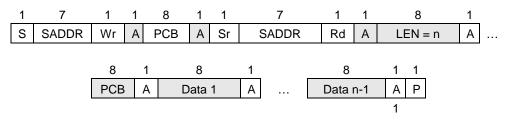

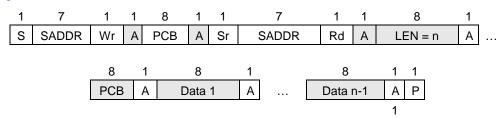

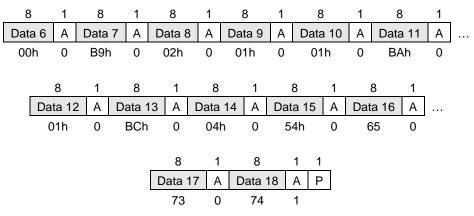

The following figure shows the format of the Block read packet:

#### Figure 4 Block read packet

The field LEN within the Block read encodes the number of data bytes + 1 being received by the master device to the slave device.

The master device SHALL be able to retrieve any number from 0 up to and including  $CDB_{SM,DEF}$  (Command Data Bytes, Slave to Master, DEFault, see chapter <u>21</u>) data bytes in a Block read packet from a slave device.

The master device SHALL acknowledge all bytes read from the slave device except for the last byte, which the master device SHALL NOT acknowledge to indicate the end of the read transfer.

The slave device SHALL be able to return any number from 0 up to and including CDB<sub>SM,DEF</sub> data bytes in a Block read packet to a slave device.

The slave device SHALL be able to detect that the master device does not acknowledge one of the bytes within a packet and in such case of an unexpected not acknowledge the slave device SHALL raise a Protocol Exception.

The slave device SHALL be able to detect that the master device acknowledges also the last byte and in such case of an unexpected acknowledge the slave device SHALL raise a Protocol Exception.

The master device SHALL be able to detect a mismatch of data bytes received within the Block read packet compared to the LEN byte as contained within the packet and in case of a mismatch the master device SHALL raise a Protocol Exception (see chapter 14.2).

In case the master device receives a PCB from the slave device indicating an exception (see chapter <u>14.1.1</u>) the master device SHALL raise a Protocol Exception.

Note: The PCB field returned by the slave device is included in the LEN variable. As a result of that the LEN is set to 1 even though no actual data bytes are being returned by the slave device. Assuming CDB<sub>SM,DEF</sub> to be 31 and the maximum 31 data bytes are actually returned by the slave device the LEN field has a value of 32.

- Note: Slave devices according to this specification return a PCB next to the byte(s) whereas [SMBUS] only specifies data bytes to be returned.

- Note: The last byte as used above means the last byte according to the LEN field indicated by the slave device. The master device is expected to read exactly the amount of bytes as indicated by the slave device. Anyhow the master device may not read all bytes

# 13. Commands

This chapter defines command set being used. These commands are constructed based on the bus packets as defined in chapter <u>12</u>.

The following commands are defined:

- Power Down

- Power Down for Cold Reset

- Wakeup

- Cold Reset

- Soft Reset

- Read Answer to Reset

- Parameter Exchange

- Protocol Binding Selection

- Status

- Data Exchange

- Master to Slave Data Transmission

- Slave to Master data Transmission

The following chapters specify the commands in full detail.

Note: Cold Reset is not a command being constructed based on a bus packet but based on the RST\_N signal.

## 13.1 Power Down

The Power Down command SHALL be based on the Quick command packet and SHALL contain the data direction bit set to 0b (Wr) (see chapter <u>12.1</u>).

The master device MAY NOT implement the Power Down command.

The master device MAY at any time issue the Power Down command.

The master device SHALL only assume the slave device to have entered the PWRSAV state in case the Power Down command has been acknowledged.

The master device SHALL do NRETRY,PD (number of retries power down) attempts to put the device into the PWRSAV state in case the slave does not acknowledge its slave address before raising a Protocol Error. This retry limit SHALL NOT apply in the case that the previous command was the last command of a chain of Master to Slave Data Transmission commands.

The slave device SHALL be able to receive a Power Down command when its current state is the READY state and when its current state is the ACTIVE state.

On reception of a Power Down command the slave device SHALL change its state to PWRSAV when its current state is the ACTIVE state and it SHALL change its state to PWRSAV<sup>\*</sup> when its current state is the READY state.

The slave device SHALL have entered the PWRSAV state or the PWRSAV<sup>\*</sup> state (its power saving modes) within a time  $t_{PDE}$  (time, Power Down Enter see chapter <u>21</u>) after it has received the Stop Condition of the Power Down command.

- Note: Acknowledged as used above means in this case that the slave device has acknowledged the address byte.

- Note: The slave device MAY implement an automatic power down by entering the PWRSAV state after a defined time of no communication when its current state is the ACTIVE state.

- Note: The slave device MAY implement an automatic power down by entering the PWRSAV\* state after a defined time of no communication when its current state is the READY state.

# **13.2 Power Down for Cold Reset**

The Power Down for Cold Reset command SHALL be based on the Quick command packet and SHALL contain the data direction bit set to 1b (Rd) (see chapter <u>12.1</u>).

The master device MAY implement the Power Down for Cold Reset command.

The master device MAY at any time issue the Power Down for Cold Reset command to slave devices supporting the command.

The master device SHALL only assume the slave device to have entered the PWRSAV state in case the Power Down for Cold Reset command has been acknowledged.

The master device SHALL do NRETRY,PDCR (number of retries power down for cold reset) attempts to put the device into the PWRSAV state in case the slave does not acknowledge its slave address before raising a Protocol Error. This retry limit SHALL NOT apply in the case that the previous command was the last command of a chain of Master to Slave Data Transmission commands.

The slave device SHALL implement the Power Down for Cold Reset command when supporting the Cold Reset sequence.

In case the slave device supports the Power Down for Cold Reset command it SHALL be able to receive a Power Down for Cold Reset command when its current state is the READY state and when its current state is the ACTIVE state.

On reception of a Power Down for Cold Reset command the slave device SHALL change its state to WAITRESET when its current state is the ACTIVE state or its current state is the READY state.

The slave device SHALL have entered the PWRSAV state within a time  $t_{PDE}$  (time, Power Down Enter, see chapter <u>21</u>)) after it has received the Stop Condition of the command and it SHALL only leave the PWRSAV state when detecting a Cold Reset.

- Note: Acknowledged as used above means in this case that the slave device has acknowledged the address byte.

- Note: The slave device does not react on communication on the bus anymore after the Power Down for Cold Reset command.

Note: This command may be used to put a slave device implementing the l<sup>2</sup>C-bus in software to stay in the PWRSAV state while a master communicates with other slave devices on the same bus.

# 13.3 Wakeup

The Wakeup command SHALL be based on the Send Byte packet.

The master device MAY NOT implement the Wakeup command.

The master device MAY at any time issue the Wakeup command.

The PCB contained SHALL have a value in accordance with Table 3.

| Value   | Meaning                        |

|---------|--------------------------------|

| 001111b | Protocol Data – Wakeup command |

Table 3 Wakeup – PCB Master to Slave

The bits b0 to b5 set to 001111b indicate the Wakeup command.

The bits b6 and b7 of the PCB of the Wakeup command are RFU.

The master device SHALL issue a Stop Condition to conclude the command and release the bus, without sending the following PCB, in case the slave device does not acknowledge its slave address within the command.

The master device SHALL always assume the slave device to have left the PWRSAV state and being ready to receive command again even if during the Wakeup command a NoAddrAck error occurred.

The master device SHALL send the next command to the slave device no later than  $t_{WNCMD}$  (time, Wakeup Next ComManD, see chapter <u>21</u>) after the end of Stop Condition of the Wakeup command.

In case the Wakeup command ends in a NoAddrAck and the command following the Wakeup command end in a NoAddrAck or NoDataAck the master device SHALL do  $N_{RETRY,W}$  (Number of RETRY Wakeup) attempts to wake up the slave device from the PWRSAV state before raising a Protocol Error.

The slave device SHALL be able to receive a Wakeup command when its current state is the READY state, when its current state is the ACTIVE state as well as when its current state is the PWRSAV state.

The slave device SHALL change its state back to the state being in before entering the PWRSAV state.

The slave device SHALL be ready to be addressed by the master device within  $t_{CMDG}$  after the end of the Stop Condition of the Wakeup command.

Note: A NoAddrAck error may be caused by slave devices that are not able to actually decode correctly a wakeup command while being in the PWRSAV state but they indeed need to wake up based on state changes of bus signals and then are able to detect the next command issued on the bus. In principle such different behavior of acknowledgement could be used by the

master device to differentiate or even identify different slave device implementations.

# 13.4 Cold Reset

It is RECOMMENDED the master device supports the Cold Reset sequence in cases of exceptional processing or to recover from communication issues.

The master device MAY at any time issue a Cold Reset sequence to slave devices supporting the RST\_N signal.

The Cold Reset sequence is issued by a master device having access to the RST\_N signal input of the slave device by pulling the RST\_N signal to low state for at least  $t_{RSTL}$  (time, ReSeT Low, see chapter <u>21</u>) and then releasing to high state again afterwards.

The master device SHALL wait at least  $t_{RSTG}$  (time, ReSeT Guard, see chapter 21) after releasing the RST\_N signal input of the salve device to high state before sending any other command on the bus.

The master device SHALL send the Read Answer to Reset as next command after a Cold Reset sequence to the slave device and only after successful execution of the Read Answer to Reset command the master device SHALL assume the slave device has reset all its non-persistent information.

The slave device SHALL implement the Cold Reset sequence when supporting a RST\_N reset signal input.

In case the slave device supports the Cold Reset sequence the slave device SHALL at any time be able to react on a Cold Reset sequence.

On reception of a Cold Reset sequence the slave device SHALL change its state to the READY state.

The slave device SHALL be ready to receive the next command within a time of  $t_{RSTG}$  after the master device has released the RST\_N signal to high state.

Note: A Cold Reset is sometimes also called Power-on Reset.

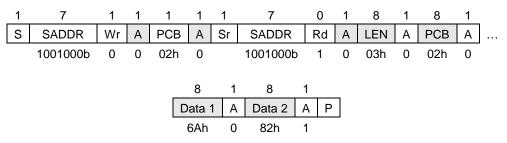

# 13.5 Soft Reset

The Soft Reset command SHALL be based on the Read block packet.

The master device MAY NOT implement the Soft Reset command.

The master device MAY at any time issue the Soft Reset command.

The PCB contained SHALL have a value in accordance with Table 4.

| l | Value   | Meaning                            |

|---|---------|------------------------------------|

|   | 011111b | Protocol Data - Soft Reset command |

#### Table 4 Soft Reset – PCB Master to Slave

The bits b0 to b5 set to 011111b indicate the Soft Reset command.

The bits b6 and b7 of the PCB of the Soft Reset command are RFU.

The master device SHALL NOT assume the slave device to have successfully executed a soft reset after the Soft Reset command has been acknowledged.

The master device SHALL wait at least  $t_{RSTG}$  (see chapter <u>21</u>) after the end of the Stop Condition of the Soft Reset command before sending any other command on the bus.

The master device SHALL send the Read Answer to Reset as next command after a Soft Reset command to the slave device and only after successful execution of the Read Answer to Reset command the master device SHALL assume the slave device has reset all its non-persistent information.

The master device SHALL do N<sub>RETRY,SRST</sub> (number of retries soft reset) attempts to reset the slave device in case the slave does not acknowledge its slave address before raising a Protocol Error. This retry limit SHALL NOT apply in the case that the previous command was the last command of a chain of Master to Slave Data Transmission commands.

The slave device SHALL be able to receive a Soft Reset command when its current state is the READY as well as when its current state is the ACTIVE state.

The slave device SHALL change its state to the READY state when receiving a Soft Reset command and its current state is either the READY or the ACTIVE state.

The PCB returned by the slave device SHALL have a value in accordance with Table 5.

| Value     | Meaning |

|-----------|---------|

| d0000000b | RFU     |

Table 5 Soft Reset – PCB Slave to Master

The bits b0 to b7 of the PCB returned by the slave device are RFU.

The slave device SHALL NOT return any data bytes within the command (except the PCB itself). The slave device SHALL set the LEN field to 01h accordingly.

The slave device SHALL be ready to receive the next command within a time of  $t_{RSTG}$  (see chapter <u>21</u>) after the end of the Stop Condition of the Soft Reset command.

Note: Acknowledged as used above means in this case that the slave device has acknowledged the address byte as well as the single data byte of the Soft Reset command.

# 13.6 Read Answer to Reset

The Read Answer to Reset command SHALL be based on the Read block packet.

The master device SHALL issue the Read Answer to Reset command to check if the slave device is in READY state and to read the slave device information contained therein.

The PCB sent by the master device SHALL have a value in accordance with <u>Table 6</u>.

| Value   | Meaning                                      |

|---------|----------------------------------------------|

| 101111b | Protocol Data – Read Answer to Reset command |

## Table 6 Read Answer to Reset – PCB Master to Slave

The bits b0 to b5 set to 101111b indicate the Read Answer to Reset command.

The bits b6 and b7 of the PCB send by the master device are RFU.

The master device SHALL do  $N_{RETRY,RATR}$  (number of retries read answer to reset) attempts in case the slave does not acknowledge its slave address before raising a Protocol Error. This retry SHALL include a retry of the previous sequence or command in case it was a Cold Reset, Soft Reset or Wakeup. The retry limit SHALL NOT apply in the case that the previous command was the last command of a chain of Master to Slave Data Transmission commands.

The slave device SHALL only acknowledge the command when in READY state.

© NXP B.V. 2018. All rights reserved

The slave device SHALL change state to the ACTIVE state when receiving a Read Answer to Reset command and its current state is the READY state.

The PCB returned by the slave device SHALL have a value in accordance with Table 7.

| Value     | Meaning |

|-----------|---------|

| d0000000b | RFU     |

#### Table 7 Read Answer to Reset – PCB Slave to Master

The bits b0 to b7 of the PCB returned by the slave device are RFU.

The slave device SHALL return its Answer to Reset data within the data field of the command in accordance with the definition in chapter  $\underline{15}$ .

A maximum of CDB<sub>ATS,MAX</sub> (Command Data Bytes, Answer To Reset, MAXimum) are allowed to be returned as data bytes by the slave device.

The master device SHALL only apply and use the information returned by the slave device within its Answer to Reset data for commands following the Read Answer to Reset command.

## **13.7 Parameter Exchange**

The Parameter Exchange command SHALL be based on the Read block packet.

The master device MAY NOT implement the Parameter Exchange command.

The master device MAY issue the Parameter Exchange command to either indicate the support of number of data bytes in a Master to Slave Data Transmission command above CDBI<sub>SM,DEF</sub> or to check for number of data bytes in a Slave to Master Data Transmission command above CDBI<sub>MS,DEF</sub> supported by the slave device.

The master device SHALL preferably issue the Parameter Exchange command after the Read Answer to Reset command and before any other command.

The PCB sent by the master device SHALL have a value in accordance with Table 8.

| Value   | Meaning                                    |

|---------|--------------------------------------------|

| 111111b | Protocol Data – Parameter Exchange command |

| YYb     | YYb codes CDBI <sub>SM,MAX</sub>           |

#### Table 8 Parameter Exchange – PCB Master to Slave

The bits b0 to b5 set to 111111b of the PCB send by the master device indicate the Parameter Exchange command.

The bits b6 and b7 of the PCB send by the master device code the CDBI<sub>SM,MAX</sub> (Command Data Bytes Integer, Slave to Master, MAXimum) value. Based on the announced CDBI<sub>SM,MAX</sub> value the slave device MAY send up to CDB<sub>SM,MAX</sub> (Command Data Bytes, Slave to Master, MAXimum) bytes according to <u>Table 9</u> within following Block read packet.

| CDBI <sub>SM,MAX</sub> | <b>СDВ</b> <sub>SM,MAX</sub> |

|------------------------|------------------------------|

| 00b                    | 29                           |

| 01b                    | 61                           |

| 10b                    | 125                          |

| 11b                    | 253                          |

Table 9 Maximum Data Bytes – Slave to Master

The CDB<sub>SM,MAX</sub> as indicated via its CDBI<sub>SM,MAX</sub> by the master device overrides the CDB<sub>SM,DEF</sub> within the slave device. The overwrite stays valid until the slave device enters the READY state.

The master device SHALL be able to receive CDB<sub>SM,MAX</sub> data bytes in a Slave to Master Data Transmission command as indicated by the CDBI<sub>SM,MAX</sub> sent in the Parameter Exchange command.

The master device SHALL do N<sub>RETRY,PE</sub> (number of retries parameter exchange) attempts in case the slave does not acknowledge its slave address before raising a Protocol Error.

The slave device SHALL only acknowledge the command when in ACTIVE state.

The slave device SHALL NOT change its state when receiving a Parameter Exchange command.

The PCB returned by the slave device SHALL have a value in accordance with Table 10.

| Value | Meaning                                                            |

|-------|--------------------------------------------------------------------|

| ZZb   | ZZb codes CDBI <sub>MS,MAX</sub>                                   |

| NNb   | NNb codes the bitwise negated $\text{CDBI}_{\text{MS},\text{MAX}}$ |

| YYb   | YYb codes CDBISM,MAX confirmation                                  |

#### Table 10 Parameter Exchange – PCB Slave to Master

The bits b0 and b1 of the PCB returned by the slave device are RFU.

The bits b2 and b3 of the PCB returned by the slave device code the CDBI<sub>MS,MAX</sub> (Command Data Bytes Integer, Master to Slave, MAXimum) value. Based on the announced CDBI<sub>MS,MAX</sub> value the master device MAY send up to CDB<sub>MS,MAX</sub> (Command Data Bytes, Master to Slave, MAXimum) bytes according to <u>Table 11</u> within following Block write packet.

| <b>CDBI</b> <sub>MS,MAX</sub> | CDB <sub>MS,MAX</sub> |

|-------------------------------|-----------------------|

| 00b                           | 32                    |

| 01b                           | 64                    |

| 10b                           | 128                   |

| 11b                           | 253                   |

Table 11 Maximum Data Bytes – Master to Slave

The bits b4 and b5 of the PCB returned by the slave device code the bitwise negated  $\text{CDB}_{\text{MS,MAX}}$  value.

The bits b6 and b7 of the PCB returned by the slave device code the CDBI<sub>SM,MAX</sub> confirmation containing the acknowledgement of the CDBI<sub>SM,MAX</sub> received from the master device.

The value of the CDBI<sub>SM,MAX</sub> confirmation returned by the slave device SHALL have the same value as the CDBI<sub>SM,MAX</sub> in the PCB send by the master device.

The slave device SHALL NOT return any data bytes within the command (except the PCB itself). The slave device SHALL set the LEN field to 01h accordingly.

The slave device SHALL be able to receive  $CDB_{MS,MAX}$  data bytes in a Master to Slave Data Transmission command as indicated by the  $CDBI_{MS,MAX}$  returned in the Parameter Exchange command.

The CDB<sub>MS,MAX</sub> as indicated via its CDBI<sub>MS,MAX</sub> by the slave overrides the CDB<sub>MS,DEF</sub> in the master device. The overwrite stays valid until the master device issues a Power Down for Cold Reset, a Cold Reset or a Soft Reset command to the slave device.

The master device SHALL detect a mismatch between the CDBI<sub>SM,MAX</sub> and the CDBI<sub>SM,MAX</sub> confirmation and issue a Protocol Error in case of a mismatch (see chapter 14.2).

The master device SHALL bitwise negate one of the CDBI<sub>MS,MAX</sub> values received, it SHALL compare the result of the calculation with the other value received, it SHALL detect a mismatch between the resulting values CDBI<sub>MS,MAX</sub> and the bitwise negated CDBI<sub>MS,MAX</sub> and it SHALL issue a Protocol Error in case of a mismatch (see chapter 14.2).

After the Parameter Exchange command the master device MAY send up to CDB<sub>MS,MAX</sub> data bytes in a Data Transmission command.

After the Parameter Exchange command the slave device MAY return up to CDB<sub>SM,MAX</sub> data bytes in a Slave to Master Data Transmission command.

- Note: The CDBI<sub>SM,MAX</sub> is confirmed back by the slave device to allow the master device to detect communication errors during the exchange of the information.

- Note: The CDBI<sub>MS,MAX</sub> is transferred as bitwise negated value as well to allow the master device to detect communication errors.

- Note: It's strongly proposed to implement the Protocol Exchange command in case the master device is I2C compliant and supports a CDBI<sub>MS</sub> above CDBI<sub>MS,DEF</sub> as this will allow for an improved performance of the data exchange in case of an high amount of data bytes is to be exchanged.

# 13.8 Protocol Binding Selection

The Protocol Binding Selection command SHALL be based on the Read block packet.

The master device MAY NOT implement the Protocol Binding Selection command.

The master device SHALL only issue the Protocol Binding Selection command to change the protocol binding to another protocol binding then the default one indicated by the slave device (see chapter 15.2.2).

The PCB sent by the master device SHALL have a value in accordance with Table 12.

| Value | Meaning                                            |  |

|-------|----------------------------------------------------|--|

| 0011b | Protocol Data – Protocol Binding Selection command |  |

| ҮҮҮҮb | YYYYb codes the protocol binding request           |  |

#### Table 12 Protocol Binding Selection – PCB Master to Slave

The bits b0 to b3 set to 0011b indicate the Protocol Binding Selection command.

The bits b4 to b7 of the PCB send by the master device code the protocol binding request containing specific protocol binding to be selected (details see <u>Table 14</u>).

The master device SHALL do N<sub>RETRY,PBS</sub> (number of retries protocol binding selection) attempts in case the slave does not acknowledge its slave address before raising a Protocol Error.

The slave device SHALL only acknowledge the command when in ACTIVE state.

The slave device SHALL NOT change its state when receiving a Protocol binding Selection command.

The PCB returned by the slave device SHALL have a value in accordance with Table 13.

| Value | Meaning                                       |  |

|-------|-----------------------------------------------|--|

| YYYYb | YYYYb codes the protocol binding confirmation |  |

#### Table 13 Protocol Binding Selection – PCB Slave to Master

The bits b4 to b7 of the PCB returned by the slave device code the protocol binding confirmation containing the acknowledgement of the protocol binding (details see <u>Table 14</u>).

| Value YYYY | Selected protocol                                                                                 |

|------------|---------------------------------------------------------------------------------------------------|

| 0000       | protocol indicated with bit 0 of Support protocol bindings element in the ATR (section $15.2.1$ ) |

| 0001       | protocol indicated with bit 1 of Support protocol bindings element in the ATR (section $15.2.1$ ) |

| 0010       | protocol indicated with bit 2 of Support protocol bindings element in the ATR (section $15.2.1$ ) |

| 0011       | protocol indicated with bit 3 of Support protocol bindings element in the ATR (section $15.2.1$ ) |

| 0100       | protocol indicated with bit 4 of Support protocol bindings element in the ATR (section $15.2.1$ ) |

| 0101       | protocol indicated with bit 5 of Support protocol bindings element in the ATR (section $15.2.1$ ) |

| 0110       | protocol indicated with bit 6 of Support protocol bindings element in the ATR (section $15.2.1$ ) |

| 0111       | protocol indicated with bit 7 of Support protocol bindings element in the ATR (section $15.2.1$ ) |

| 1          | RFU                                                                                               |

#### **Table 14 Protocol Binding Confirmation code**

The value of the protocol binding confirmation returned by the slave device SHALL have the same value as the protocol binding request in the PCB send by the master device.

The bits b0 to b3 of the PCB returned by the slave device are RFU.

The slave device SHALL NOT respond any data bytes within the command (except the PCB itself). The slave device SHALL set the LEN field to 01h accordingly.

The slave device SHALL switch to the protocol binding selected by the master device immediately after the end of the Stop Condition of the protocol binding Selection command.

The slave device SHALL be able to receive a next command in the applied protocol binding within  $t_{CMDG}$  after the end of the Stop Condition of the Protocol Binding Selection command.

The master device SHALL detect a mismatch between the protocol binding request and the protocol binding confirmation and it SHALL issue a Protocol Exception in case of a mismatch (see chapter <u>14.2</u>).

The master device SHALL use the selected protocol binding for any command following the Protocol Binding Selection command.

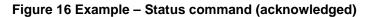

## 13.9 Status

The Status command SHALL be based on the Read block packet.

The master device SHALL implement the Parameter Exchange command.

The master device SHALL issue the Status command to query the status of the slave device and to check for pending protocol exceptions of the slave device.

The PCB sent by the master device SHALL have a value in accordance with Table 15.

| Value |    | Meaning                        |

|-------|----|--------------------------------|

| 011   | 1b | Protocol Data – Status command |

Table 15 Status- PCB Master to Slave

The bits b0 to b3 of the PCB set to 0111b indicate the Status command.

The bits b4 to b7 of the PCB are RFU.

The slave device SHALL acknowledge the command when in ACTIVE state and it MAY acknowledge the command when in PROCESSING state.

The slave device SHALL NOT change its state when receiving a Status command.

The PCB returned by the slave device SHALL have a value in accordance with Table 16.

|   | Value | Meaning                        |

|---|-------|--------------------------------|

| ĺ | 0111b | Protocol Data – Status command |

|   | ҮҮҮҮb | YYYYb codes the status code    |

Table 16 Status- PCB Slave to Master

The bits b4 to b7 of the PCB returned by the slave device code the exception information according to Table 21.

The bits b0 to b3 of the PCB returned by the slave device set to 0111b indicate the Status response.

The slave device SHALL NOT respond any data bytes within the command (except the PCB itself). The slave device SHALL set the LEN field to 01h accordingly.

The master device SHALL raise a protocol exception in case the slave device returns status information different from 0000b and 0001b and SHALL continue as described in chapter <u>14.1.2</u>.

The slave device SHALL only return its current protocol status exception information and it SHALL NOT reset any pending protocol exception.

The slave device MAY NOT acknowledge the Status command when busy.

Note: The Status command allows the master device to detect error occurred on the slave device as well as to detect a busy but still responsive slave device. In the first case an exception handling will be started whereas in the latter case the master device will continue to wait until a timeout occurs.

AN12207

**Smart Card I2C Protocol**

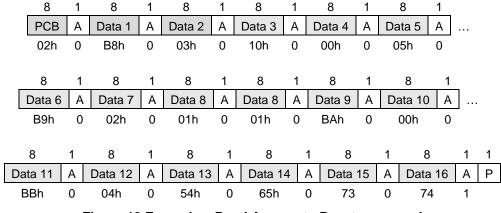

# 13.10 Data Exchange

Two kinds of Data Transmission commands are defined for exchanging data:

- Master to Slave Data Transmission and

- Slave to Master Data Transmission

Both commands are used to exchange Payload Streams and Payload Chunks as defined by the mappings (see chapter <u>16</u>).

Note: The data transmission commands are used to actually exchange in a fully transparent way the Payload Streams. The Payload Streams are typically APDUs that are exchanged.

#### 13.10.1 Protocol Control Byte

The elements contained within a PCB that SHALL be used within Data Transmission commands are based on Table 17.

| Value | Meaning                                                   |  |

|-------|-----------------------------------------------------------|--|

| 00b   | Protocol Data – Master to Slave Data Transmission command |  |

| 10b   | Protocol Data –Slave to Master Data Transmission command  |  |

| EEb   | EEb codes the error detection code used                   |  |

| -SSSb | SSSb codes the sequence counter                           |  |

| Mb    | Mb codes the More bit                                     |  |

#### Table 17 Data Transmission – Protocol Control Byte

The individual elements of the PCB MAY or MAY NOT be used depending on the communication direction or Data Transmission command used (see chapter 13.10.1.3 and chapter 13.10.4).

The bits b0 and b1 set to 00b indicate a Master to Slave Data Transmission command and the bits b0 and b1 set to 10b indicate a Slave to Master Data Transmission command

#### 13.10.1.1 Error Detection Code

The bits b2 and b3 of the PCB encode the error detection code used as defined in <u>Table</u> <u>18</u>.

| Value                                               | Meaning                         |  |

|-----------------------------------------------------|---------------------------------|--|

| 00b                                                 | No error detection code is used |  |

| 01b LRC error detection is used (see chapter 15.1.2 |                                 |  |

## Table 18 PCB – Error Detection Code

The master device MAY NOT use any error detection code.

The master device SHALL only use error detection codes indicated to be supported by the slave device (see chapter 15.1.2).

The master device sets the used error detection code used for communication with the slave device by its indication in the first Master to Slave Data Transmission command.

The master device SHALL NOT switch between different or no error detection code use during a single session.

#### 13.10.1.2 Sequence counter

The bits b4 to b6 of the PCB of a Master to Slave Data Transmission command as well as a Slave to Master Data Transmission command encode each an independent sequence counter of 3 bits in size.

The master device and the slave device manage each two independent sequence counter.

The master device SHALL implement a sequence counter used within Master to Slave Data Transmission commands called  $SC_{M,MS}$  (Sequence Counter Master, Master to Slave) and a sequence counter to be compared with the sequence counter received in Slave to Master Data Transmission commands called  $SC_{M,SM}$  (Sequence Counter Master Slave to Master).

The slave device SHALL implement a sequence counter used within Slave to Master Data Transmission commands called  $SC_{S,SM}$  (Sequence Counter Slave, Slave to Master) and a sequence counter to be compared with the sequence counter received in Master to slave Data Transmission commands called  $SC_{S,MS}$  (Sequence Counter Slave, Master to Slave).

Sequence counter are defined to be able to identify disordered or more specifically missed Data Transmission commands.

Sequence counter SHALL be implemented as a rolling code that starts at zero again when it overruns (after 111b it transitions to 000b at the next increment).

The master device SHALL initialize both of its sequence counter to zero at the activation of a slave device.

The master device SHALL increment  $SC_{M,MS}$  at any time it has successfully transmitted a Master to Slave Data Transmission command.

The slave device SHALL initialize both of its sequence counter to 111b when entering the READY state.

The slave device SHALL increment  $SC_{S,SM}$  at any time it has acknowledged a Slave to Master Data Transmission command.

Note: Acknowledged as used above means in this case that the slave device has acknowledged the address byte of a Slave to Master Data Transmission command.

#### 13.10.1.3 Data Chaining

The bit b7 of the PCB encodes the More bit.

For the usage of data transmission, for both master to slave and as slave to master communication, the More bit set to 1b indicates that the data bytes of this packet to contain a Payload Chunk and not a complete Payload Stream and so to be continued by a subsequent Payload Chunk in the next Data Transmission command (see chapter <u>16</u>).

The last Data Transmission command of chain SHALL always have the More bit set to 0b.

The master device and the slave device SHALL use the chaining in case the Payload Stream does not fit into a single Data Transmission Command.

The master device SHALL split the Payload Stream into Payload Chunks so that the individual Data Transmission commands with the More bit set to 1b are filled to its

maximum amount of bytes taking the use of the OPTIONAL error detection code into account.

The slave device MAY typically split the Payload Stream into Payload Chunks so that the individual Data Transmission commands with the More bit set to 1b are filled to its maximum amount of bytes.

## 13.10.2 Length

The LEN (LENgth) byte indicates the number of bytes to send or receive.

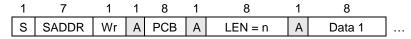

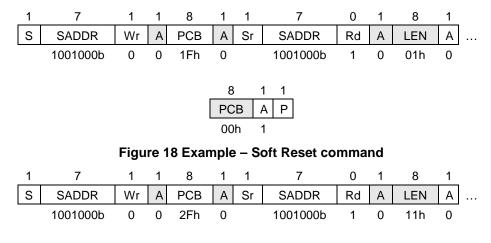

#### 13.10.3 Master to Slave Data Transmission

The Master to Slave Data Transmission command SHALL be based on the Write block packet.

The master device SHALL implement the Master to Slave Data Transmission command.

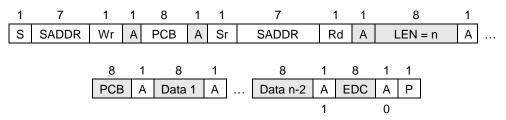

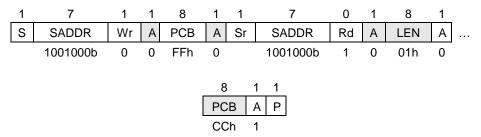

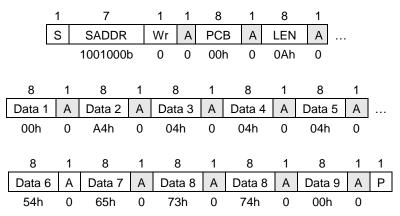

The master device SHALL use the structure for the Master to Slave Data Transmission command as shown in <u>Figure 5</u> when no error detection code is used:

Figure 5 Master to Slave Data Transmission – Structure no EDC

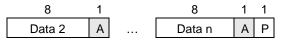

The Master to Slave Data Transmission command SHALL use the structure as shown in <u>Figure 6</u> when the OPTIONAL error detection code is used:

| 8      | 1 | 8            | 1 | 8   | 1 | 8     | 1 | 1 |

|--------|---|--------------|---|-----|---|-------|---|---|

| Data 2 | А | <br>Data n-2 | А | EDC | А | EDCCB | А | Р |

Figure 6 Master to Slave Data Transmission – Structure with EDC

Note: CDB<sub>MS</sub> equals n in the structure without EDC (<u>Figure 5</u>) and CDB<sub>MS</sub> equals n-2 in the structure with EDC (<u>Figure 6</u>). Hence, the maximum number of Data bytes (CDB<sub>MS,MAX</sub>) sent by the slave device is the same in both cases.

The master device SHALL issue the command to transmit Payload Streams to the slave device following the rules and order defined below:

- 1. The master device SHALL send as many Master to Slave Data Transmission commands in a chain indicating data chaining as needed to convey the Payload Stream as defined by the selected mapping and the selected error detection code (see chapter <u>16</u>).