# **MSC8113 Reference Manual**

Tri Core 16-Bit Digital Signal Processor

MSC8113RM Rev 0, May 2008

#### How to Reach Us:

#### Home Page:

www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc.

Technical Information Center, EL516

2100 East Elliot Road

Tempe, Arizona 85284

+1-800-521-6274 or

+1-480-768-2130

#### Europe, Middle East, and Africa:

www.freescale.com/support

www.freescale.com/support

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French)

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters

ARCO Tower 15F

1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064

Japan

0120 191014 or

+81 3 5437 9125

support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 010 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor

Literature Distribution Center

P.O. Box 5405

Denver, Colorado 80217

+1-800 441-2447 or

+1-303-675-2140

Fax: +1-303-675-2150

LDCForFreescaleSemiconductor

@hibbertgroup.com

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale, the Freescale logo, StarCore, and CodeWarrior are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2008.

MSC8113RM Rev. 0 5/2008

| MSC8113 Overview                                   | 1  |

|----------------------------------------------------|----|

| SC140 Core Overview                                | 2  |

| External Signals                                   | 3  |

| System Interface Unit (SIU)                        | 4  |

| Reset                                              | 5  |

| Boot Program                                       | 6  |

| Clocks                                             | 7  |

| Memory Map                                         | 8  |

| Extended Core                                      | 9  |

| MQBus and M2 Memory                                | 10 |

| SQBus                                              | 11 |

| Memory Controller                                  | 12 |

| System Bus                                         | 13 |

| Direct Slave Interface (DSI)                       | 14 |

| Hardware Semaphores                                | 15 |

| Direct Memory Access (DMA) Controller              | 16 |

| Interrupt Processing                               | 17 |

| Debugging                                          | 18 |

| Internal Peripheral Bus (IPBus)                    | 19 |

| Time-Division Multiplexing (TDM) Interface         | 20 |

| Universal Asynchronous Receiver/Transmitter (UART) | 21 |

| Timers                                             | 22 |

| General-Purpose Input/Output (GPIO)                | 23 |

| I <sup>2</sup> C Software Module                   | 24 |

| Ethernet Controller                                | 25 |

| Programming Reference                              | Α  |

| MSC8113 Dictionary                                 | В  |

| MSC8113 Boot Code                                  | С  |

| Index                                              | I  |

| NO |                                                    |

|----|----------------------------------------------------|

|    | MSC8113 Overview                                   |

| 2  | SC140 Core Overview                                |

| 3  | External Signals                                   |

| 4  | System Interface Unit (SIU)                        |

| 5  | Reset                                              |

| 6  | Boot Program                                       |

| 7  | Clocks                                             |

| 8  | Memory Map                                         |

| 9  | Extended Core                                      |

| 10 | MQBus and M2 Memory                                |

| 11 | SQBus                                              |

| 12 | Memory Controller                                  |

| 13 | System Bus                                         |

| 14 | Direct Slave Interface (DSI)                       |

| 15 | Hardware Semaphores                                |

| 16 | Direct Memory Access (DMA) Controller              |

| 17 | Interrupt Processing                               |

| 18 | Debugging                                          |

| 19 | Internal Peripheral Bus (IPBus)                    |

| 20 | Time-Division Multiplexing (TDM) Interface         |

| 21 | Universal Asynchronous Receiver/Transmitter (UART) |

| 22 | Timers                                             |

| 23 | General-Purpose Input/Output (GPIO)                |

| 24 | I <sup>2</sup> C Software Module                   |

| 25 | Ethernet Controller                                |

| Α  | Programming Reference                              |

| В  | MSC8113 Dictionary                                 |

| С  | MSC8113 Boot Code                                  |

| I  | Index                                              |

|    |                                                    |

| COII    | lents                                                   |

|---------|---------------------------------------------------------|

|         | About This Book                                         |

|         | Before Using This Manual—Important Notexxii             |

|         | Audience and Helpful Hintsxxii                          |

|         | Notational Conventions and Definitions                  |

|         | Conventions for Registers xxiv                          |

|         | Organization                                            |

|         | Other MSC8113 Documentation                             |

|         | Further Reading                                         |

| 1       | MSC8113 Overview                                        |

| 1.1     | Features                                                |

| 1.2     | Architecture                                            |

| 1.2.1   | Extended Core                                           |

| 1.2.1.1 | SC140 Core                                              |

| 1.2.1.2 | M1 Memory                                               |

| 1.2.1.3 | Instruction Cache                                       |

| 1.2.1.4 | QBus System                                             |

| 1.2.2   | Power Saving Modes1-15                                  |

| 1.2.2.1 | Extended Core Wait Mode                                 |

| 1.2.2.2 | Extended Core Stop Mode                                 |

| 1.2.3   | M2 Memory1-16                                           |

| 1.2.4   | System Interface Unit (SIU)                             |

| 1.2.4.1 | 60x-Compatible System Bus Interface1-16                 |

| 1.2.4.2 | Memory Controller1-17                                   |

| 1.2.5   | Direct Slave Interface (DSI)                            |

| 1.2.6   | Direct Memory Access (DMA) Controller                   |

| 1.2.7   | Internal and External Bus Architecture1-19              |

| 1.2.8   | TDM Serial Interface                                    |

| 1.2.9   | Ethernet Controller                                     |

| 1.2.10  | Universal Asynchronous Receiver/Transmitter (UART) 1-23 |

| 1.2.11  | Timers                                                  |

| 1.2.12  | GPIOs                                                   |

| 1.2.13  | Reset and Boot                                          |

| 1.2.14  | Interrupt Scheme                                        |

| 1.2.15  | Signal Multiplexing Options                             |

| 1.3     | Internal Communication and Semaphores                   |

| ents    |                                                                     |      |

|---------|---------------------------------------------------------------------|------|

| 1.3.1   | Internal Communication                                              | 1-26 |

| 1.3.2   | Atomic Operations                                                   | 1-27 |

| 1.3.3   | Hardware Semaphores                                                 |      |

| 2       | SC140 Core Overview                                                 |      |

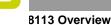

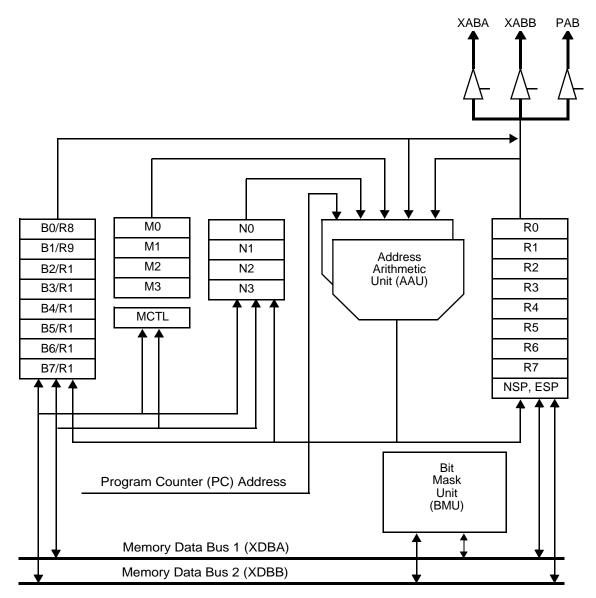

| 2.1     | Architecture                                                        | 2-2  |

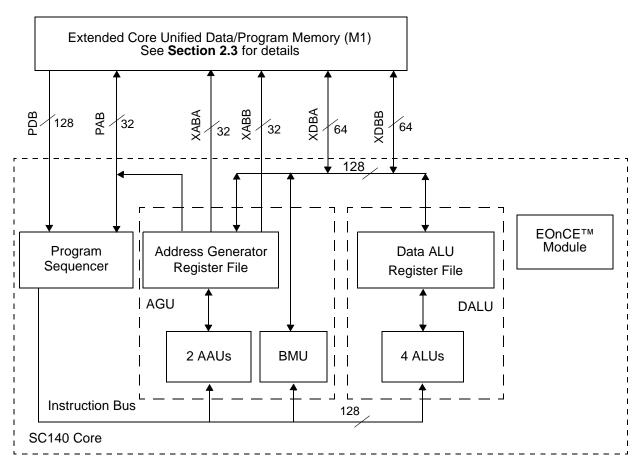

| 2.1.1   | Data Arithmetic Logic Unit (Data ALU)                               | 2-3  |

| 2.1.1.1 | Data Registers                                                      | 2-4  |

| 2.1.1.2 | Multiply-Accumulate (MAC) Unit                                      | 2-4  |

| 2.1.1.3 | Bit-Field Unit (BFU)                                                | 2-5  |

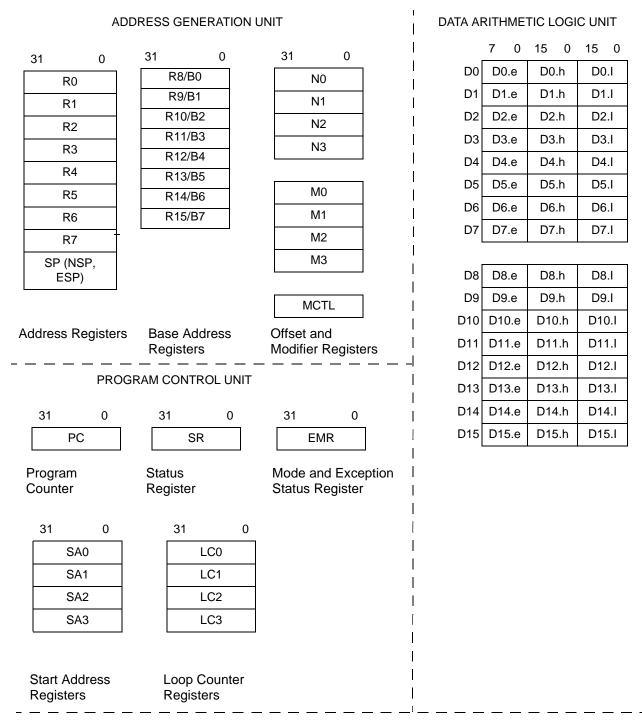

| 2.1.2   | Address Generation Unit (AGU)                                       | 2-5  |

| 2.1.2.1 | Stack Pointer Registers                                             | 2-7  |

| 2.1.2.2 | Bit Mask Unit (BMU)                                                 | 2-7  |

| 2.1.3   | Program Sequencer Unit (PSEQ)                                       | 2-7  |

| 2.1.4   | Enhanced On-Chip Emulation (EOnCE)                                  | 2-8  |

| 2.2     | Programming Model                                                   | 2-8  |

| 2.2.1   | AGU Programming Model                                               | 2-8  |

| 2.2.2   | Data Arithmetic Logic Programming Model                             | 2-11 |

| 2.2.3   | Program Control Unit Programming Model                              | 2-12 |

| 2.3     | Instruction Set Overview                                            | 2-12 |

| 2.4     | Additional Programming Considerations                               | 2-19 |

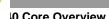

| 3       | External Signals                                                    |      |

| 3.1     | Power Signals                                                       | 3-3  |

| 3.2     | Clock Signals                                                       |      |

| 3.3     | Reset and Configuration Signals                                     |      |

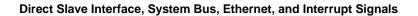

| 3.4     | Direct Slave Interface, System Bus, Ethernet, and Interrupt Signals |      |

| 3.5     | Memory Controller Signals                                           |      |

| 3.6     | GPIO, TDM, UART, and Timer Signals                                  |      |

| 3.7     | Dedicated Ethernet Signals                                          |      |

| 3.8     | EOnCE Event and JTAG Test Access Port Signals                       |      |

| 3.9     | Reserved Signals                                                    |      |

| 4       | System Interface Unit (SIU)                                         |      |

| 4.1     | Architecture                                                        | 4-2  |

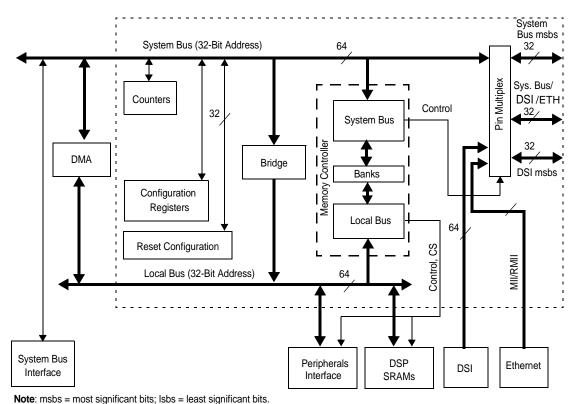

| 4.1.1   | Bus Monitors                                                        |      |

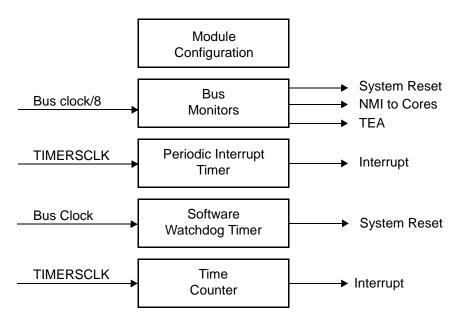

| 4.1.2   | Timers Clock                                                        |      |

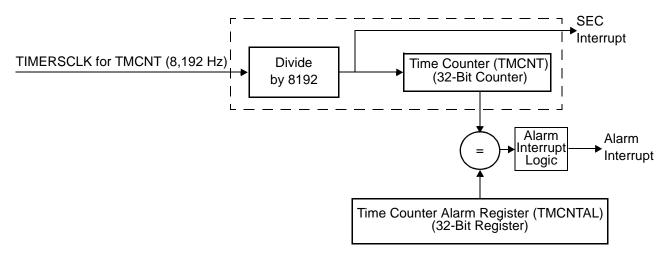

| 4.1.3   | Time Counter (TMCNT)                                                |      |

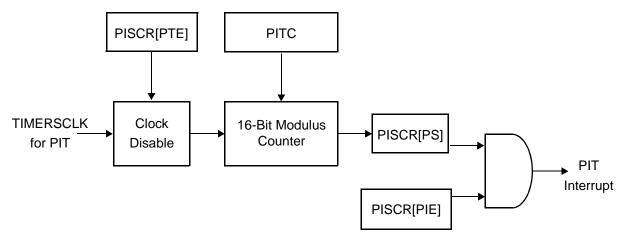

| 4.1.4   | Periodic Interrupt Timer (PIT)                                      |      |

MSC8113 Reference Manual, Rev. 0

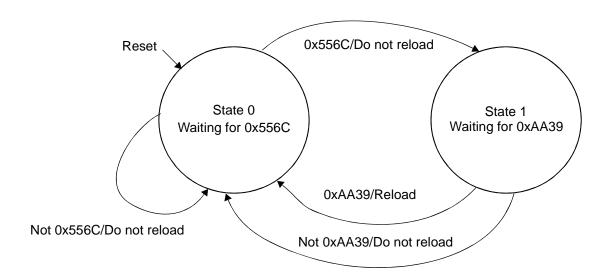

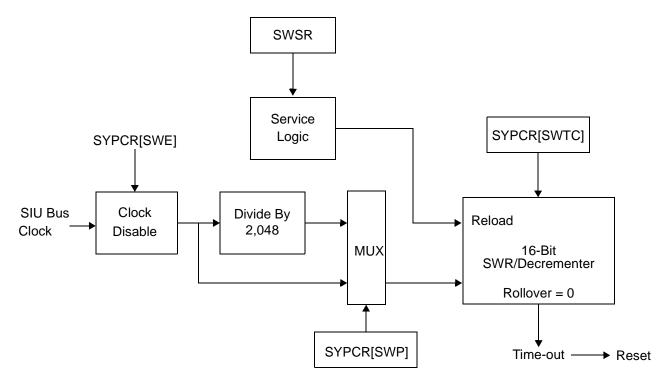

SIU and General Software Watchdog Timers..... 4-6

4.1.5

4.1.6

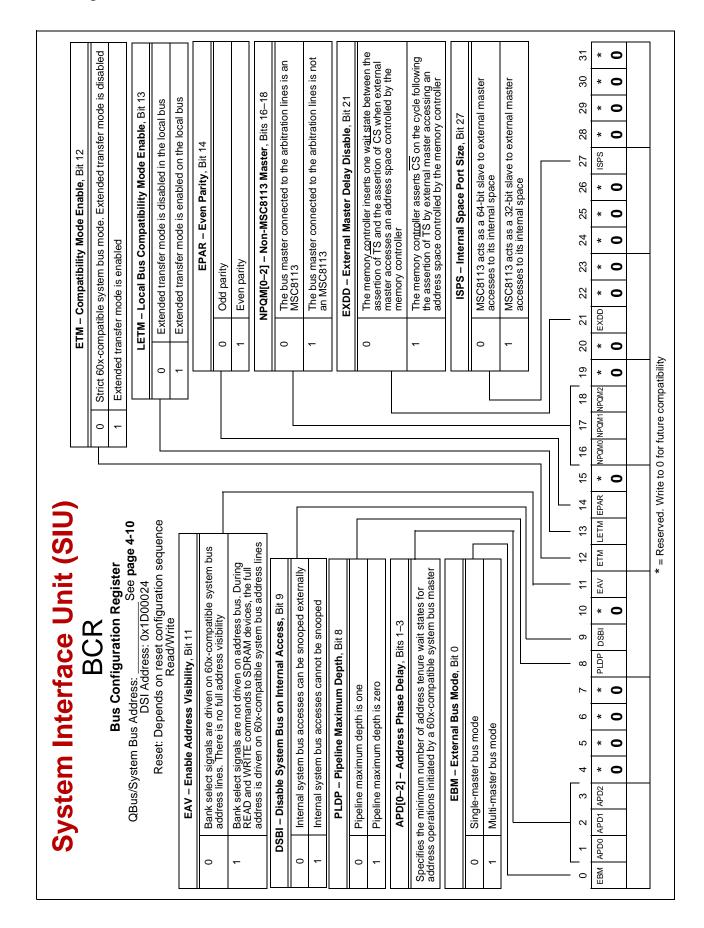

| 4.2         | SIU Programming Model                                      |

|-------------|------------------------------------------------------------|

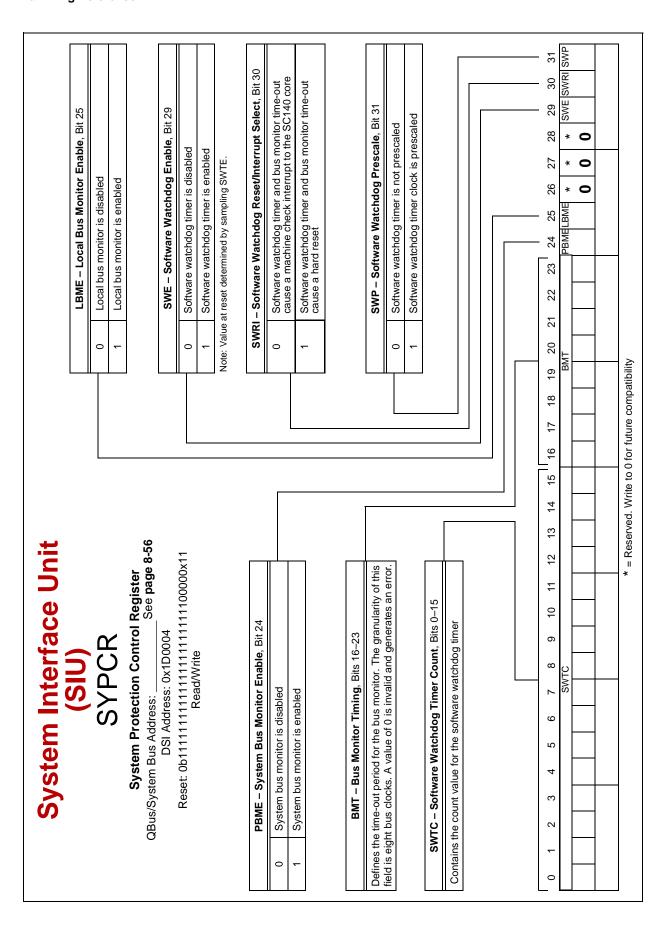

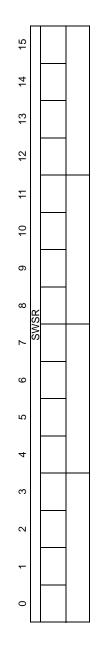

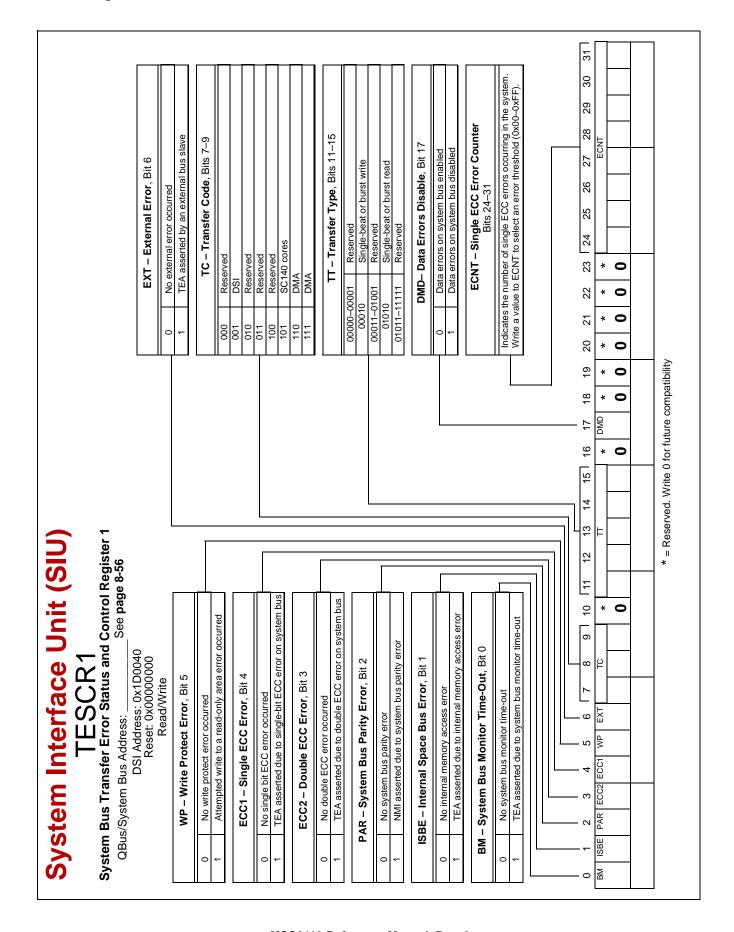

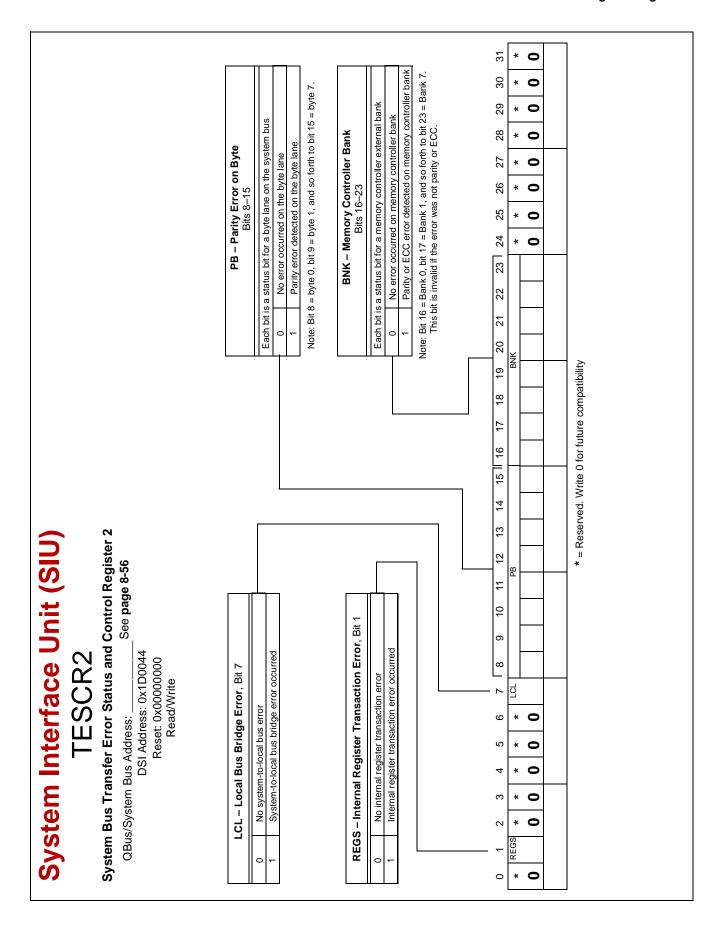

| 4.2.1       | System Configuration and Protection Registers              |

| 4.2.2       | Periodic Interrupt Registers                               |

| 5           | Reset                                                      |

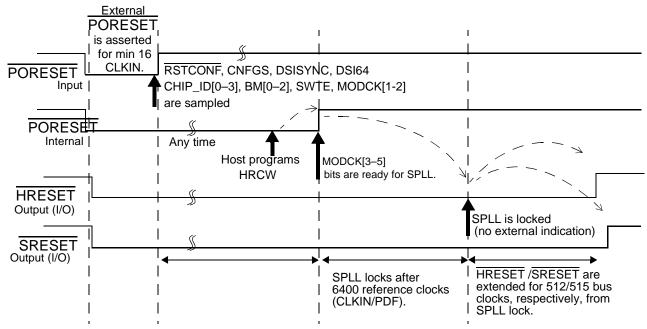

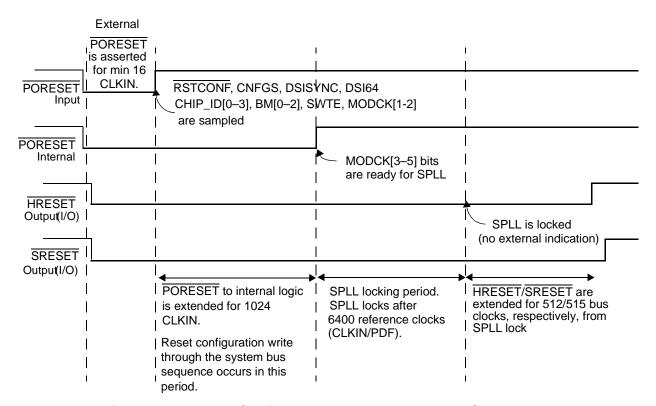

| 5.1         | Power-On Reset (PORESET)                                   |

| 5.2         | Reset Configuration                                        |

| 5.2.1       | Reset Configuration Through the DSI                        |

| 5.2.2       | Reset Configuration Through the System Bus                 |

| 5.3         | Hard Reset                                                 |

| 5.4         | Soft Reset                                                 |

| 5.5         | Reset Configuration Writes Through the System Bus 5-9      |

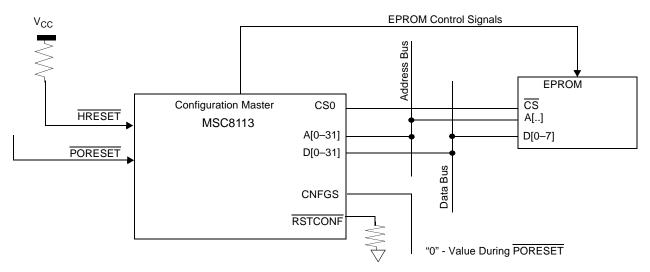

| 5.5.1       | Single MSC8113 System Configuration From EPROM 5-9         |

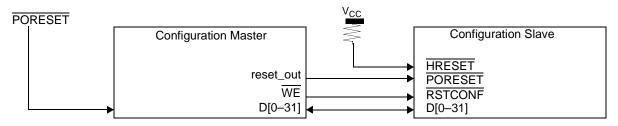

| 5.5.2       | Single Slave MSC8113 Configuration by System Bus Host 5-10 |

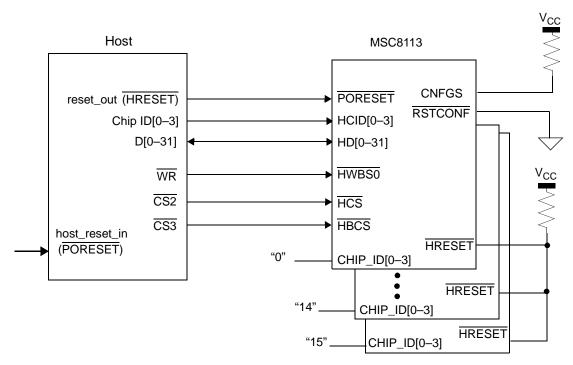

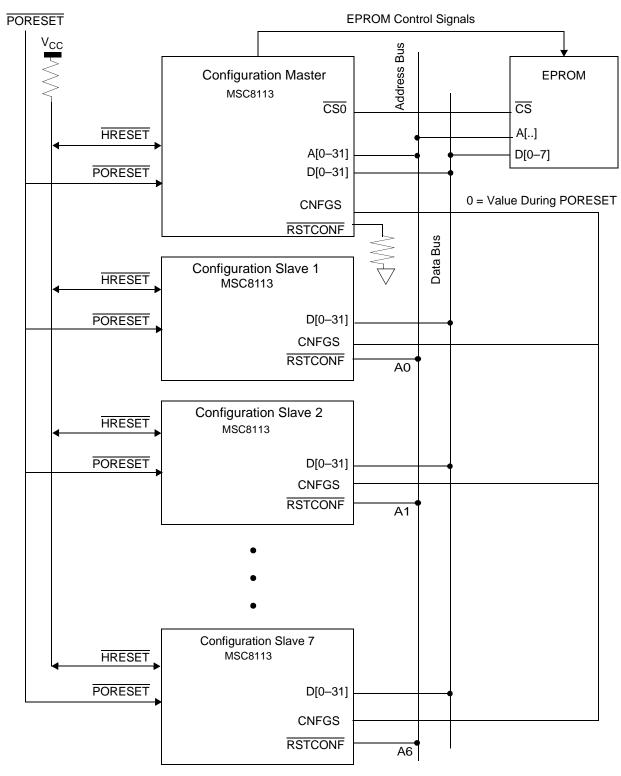

| 5.5.3       | Multi-MSC8113 System Configuration                         |

| 5.5.4       | Multiple MSC8113 Devices in a System With No EPROM 5-13    |

| 5.6         | Reset Programming Model                                    |

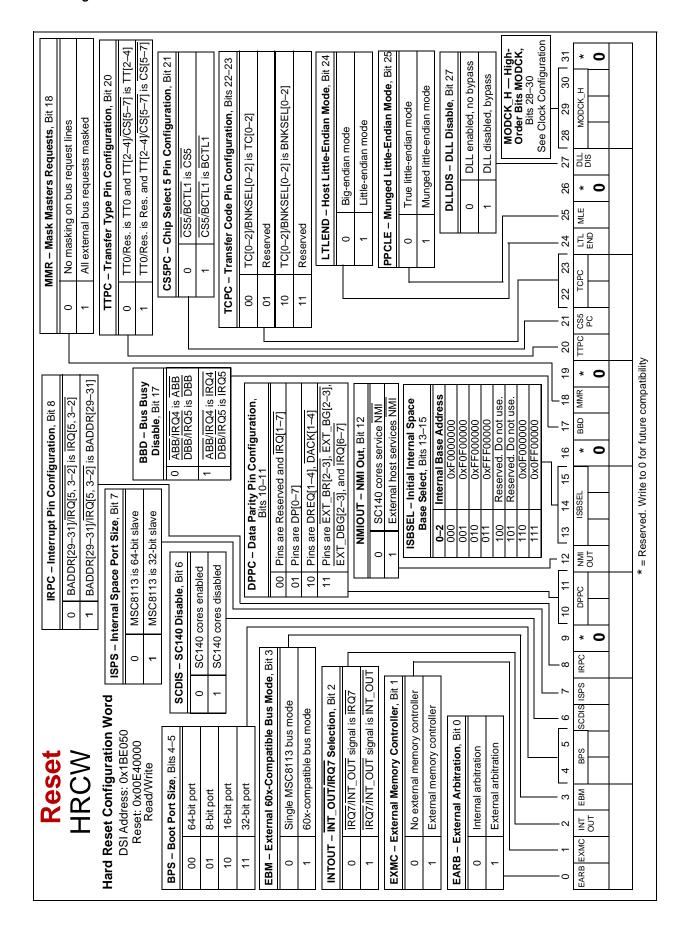

| 5.6.1       | Hard Reset Configuration Word                              |

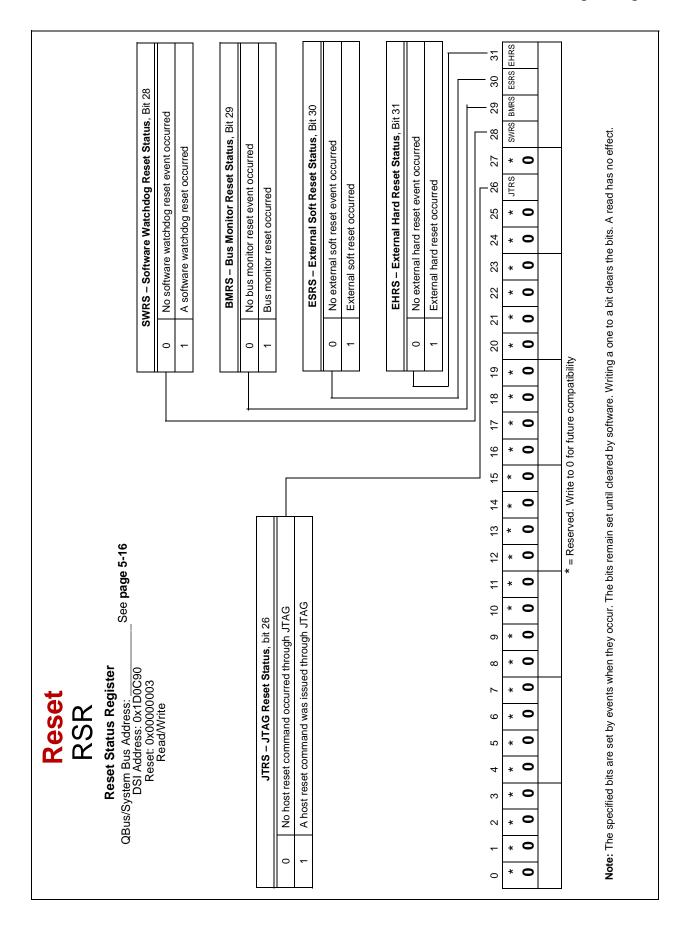

| 5.6.2       | Reset Status Registers                                     |

| 6           | Boot Program                                               |

| 6.1         | Boot Basics                                                |

| 6.2         | Booting From an External Memory Device                     |

| 6.3         | Booting from an External Host (DSI or System Bus) 6-4      |

| 6.4         | Booting From the TDM Interface                             |

| 6.4.1       | Initializing the TDM Physical Layer                        |

| 6.4.1.1     | Receiver Initialization                                    |

| 6.4.1.2     | Transmitter Initialization                                 |

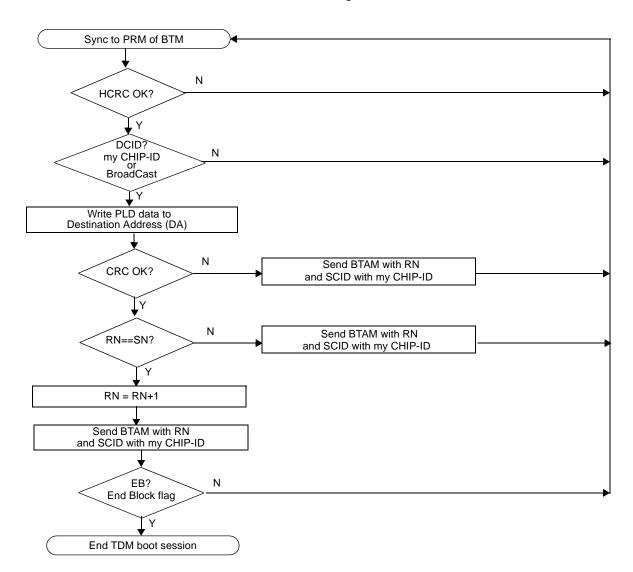

| 6.4.2       | TDM Logical Layer Handshake 6-8                            |

| 6.4.2.1     | Messages Structure                                         |

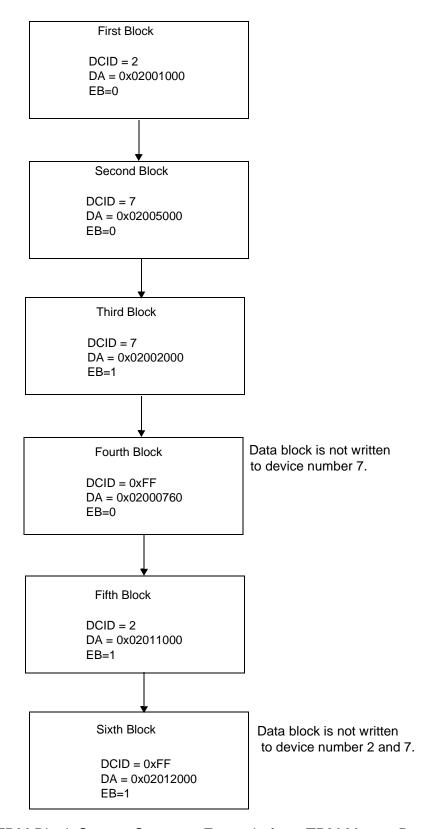

| 6.4.2.2     | Operation                                                  |

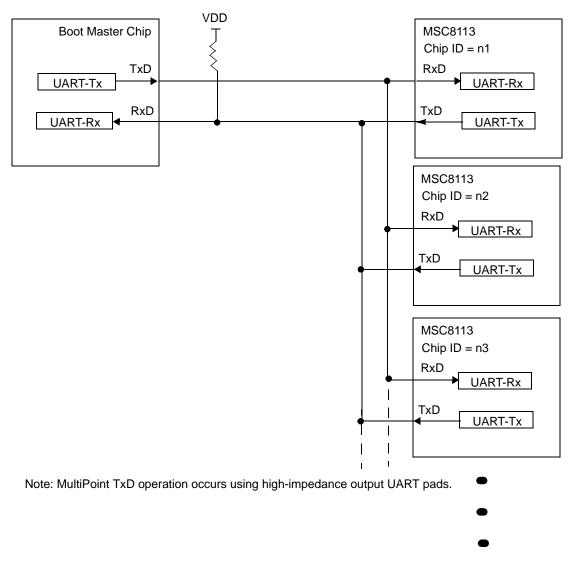

| 6.5         | Booting From a UART Device 6-13                            |

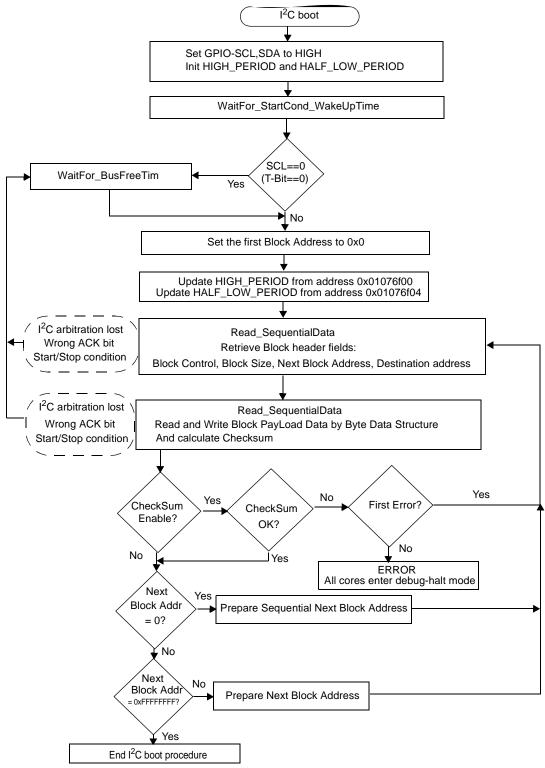

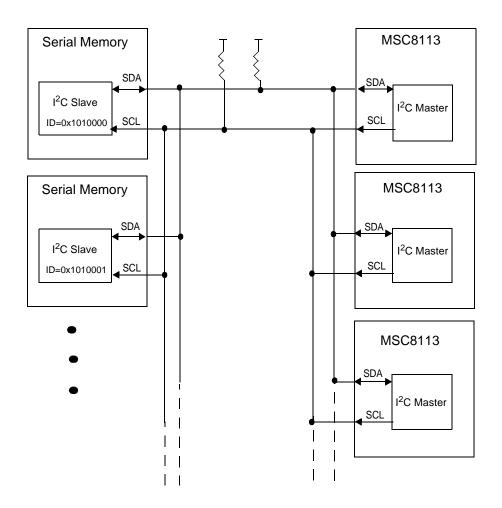

| 6.6         | Booting from I <sup>2</sup> C Slave Memory Device          |

| 6.6.1       | Procedure Flow                                             |

| 6.6.2       | I <sup>2</sup> C System                                    |

| 7           | Clocks                                                     |

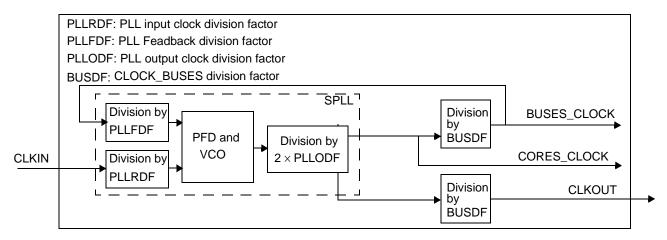

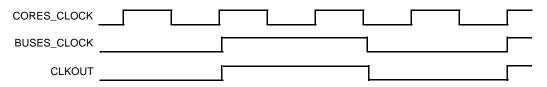

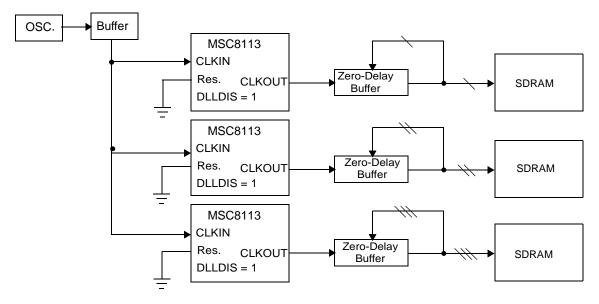

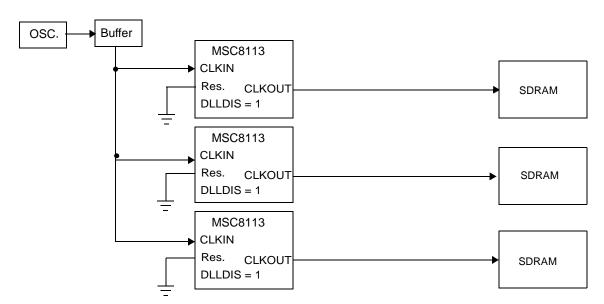

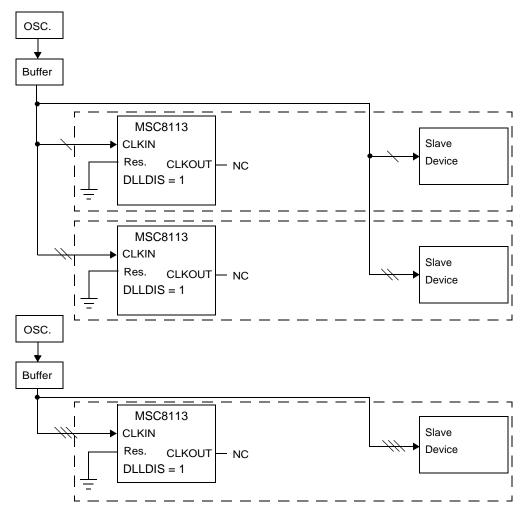

| <b>7</b> .1 | Clock Generation         7-2                               |

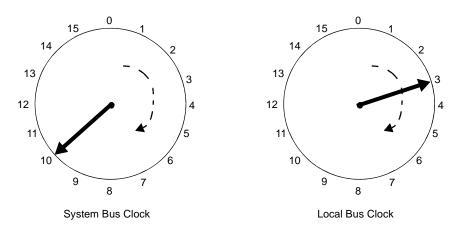

| 7.2         | Board-Level Clock Distribution                             |

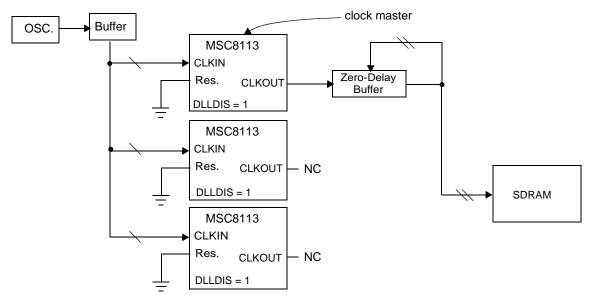

| 7.2.1       | Single Master Mode Board-Level Clock Distribution          |

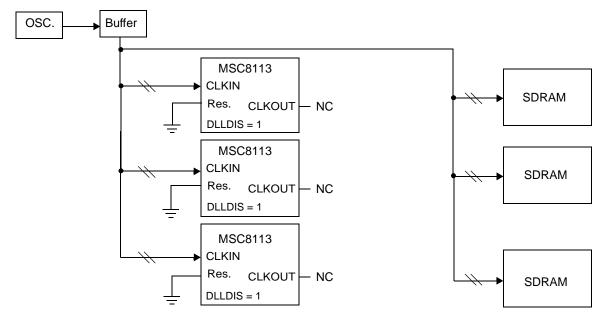

| 7.2.2       | Multi-Master Mode Board-Level Clock Distribution           |

| <b>_</b>    |                                                            |

Freescale Semiconductor vii

| Δ | n | te |

|---|---|----|

| 7.3                  | Clock Configuration               | 7-7     |

|----------------------|-----------------------------------|---------|

| 7.4                  | Clocks Programming Model          | 7-10    |

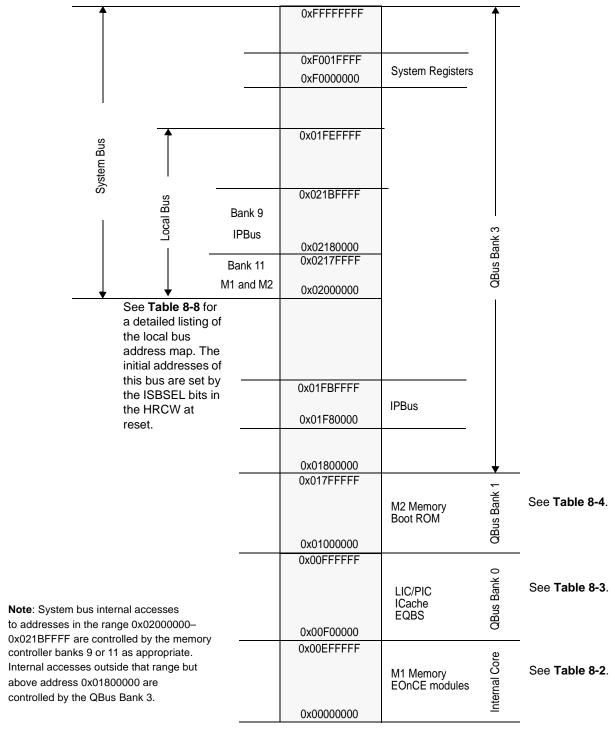

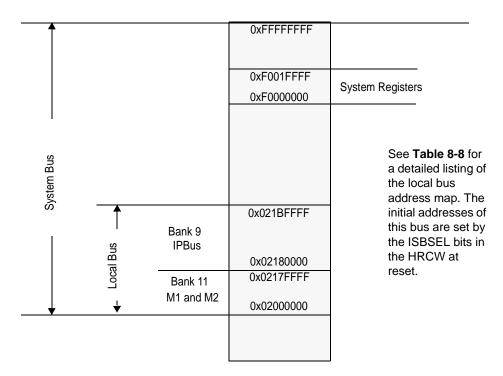

| 8                    | Memory Map                        |         |

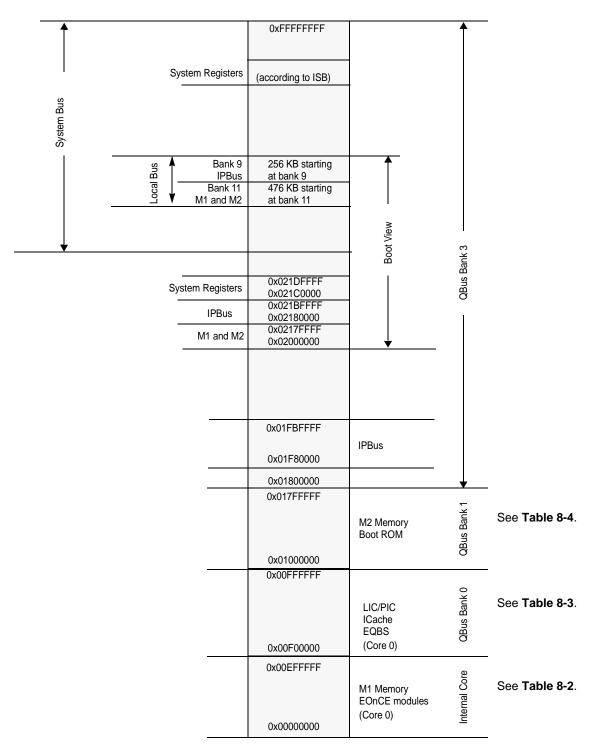

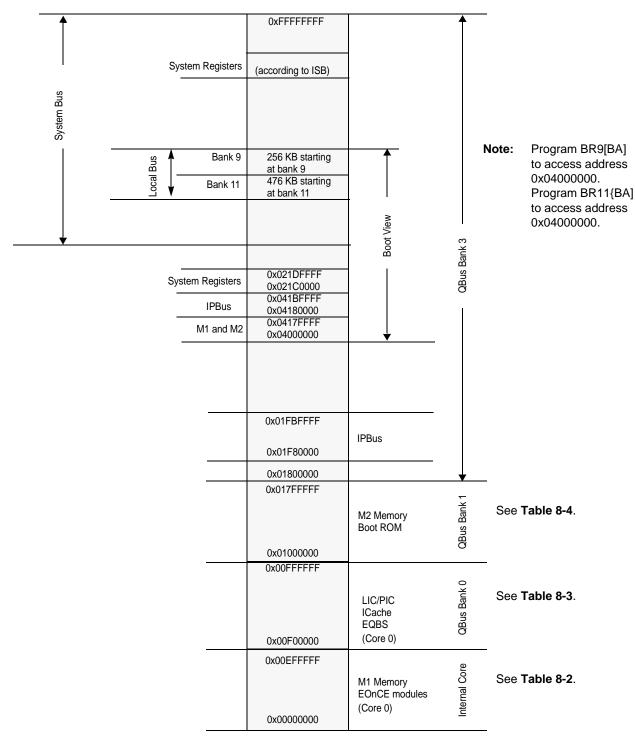

| 8.1                  | SC140 Core Internal Address Space | 8-8     |

| 8.2                  | QBus Address Space                |         |

| 8.3                  | MQBus Address Space               |         |

| 8.4                  | SQBus Address Space               |         |

| 8.5                  | IPBus Address Space               |         |

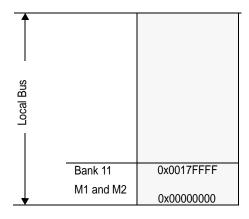

| 8.6                  | Local Bus Address Space           |         |

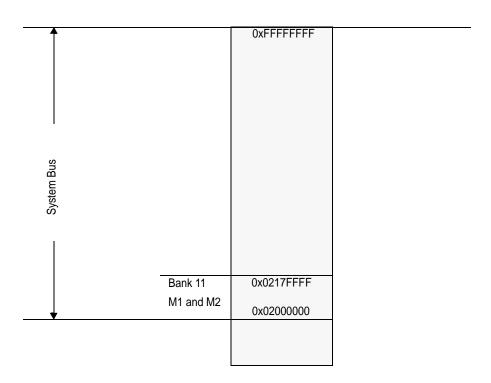

| 8.7                  | System Bus Address Space          |         |

| 8.8                  | DSI Address Map                   |         |

| 8.9                  | Pseudo Command Address Space      |         |

| 8.10                 | Notes                             |         |

| 9                    | Extended Core                     |         |

| 9.1                  | SC140 DSP Core                    | 0.2     |

| 9.1                  | Extended Core Memory (M1)         |         |

| 9.2.1                | Memory Organization               |         |

| 9.2.1.1              | Memory Groups                     |         |

| 9.2.1.1              | Memory Contention and Priority    |         |

| 9.2.1.2              | Errors and Exceptions             |         |

| 9.2.2.1              | Errors                            |         |

| 9.2.2.1              | Exceptions                        |         |

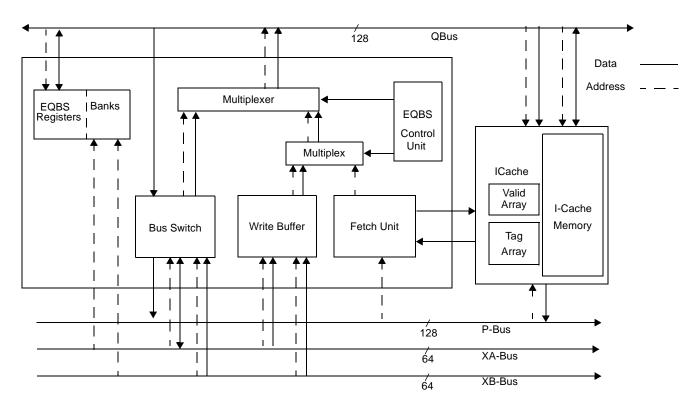

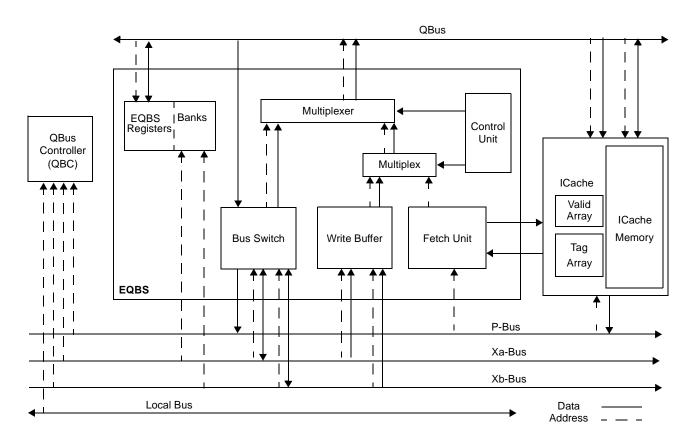

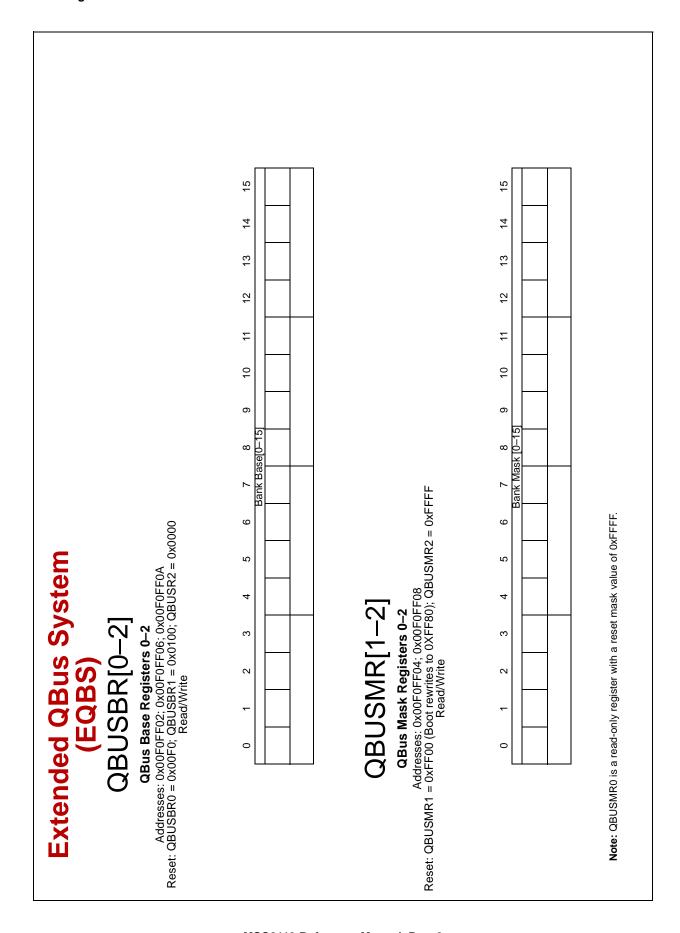

| 9.3                  | Extended QBus System              |         |

| 9.3.1                | Architecture                      |         |

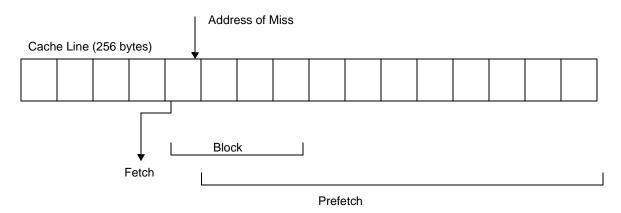

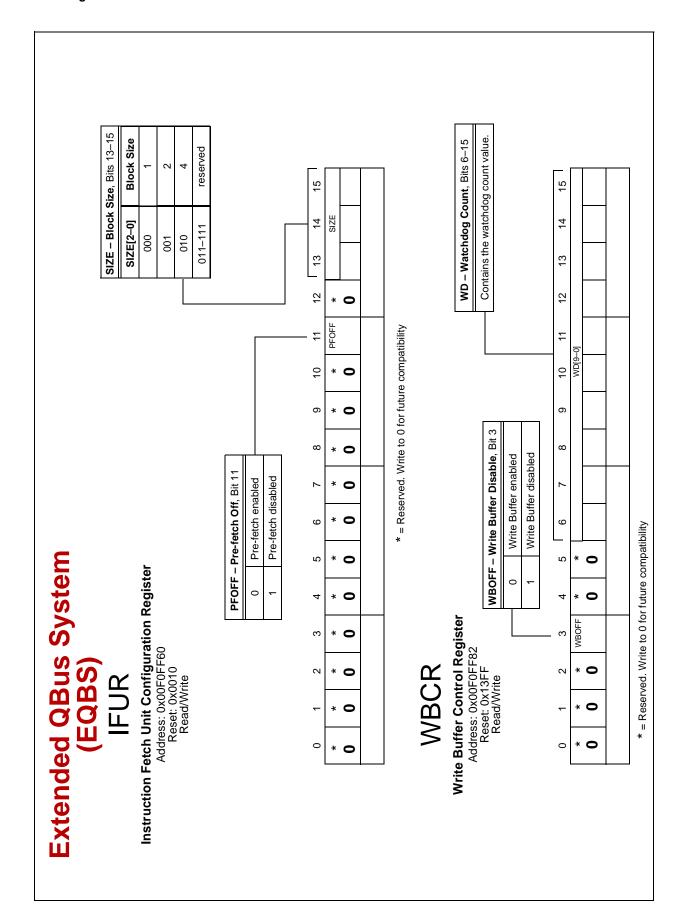

| 9.3.1.1              | Fetch Unit                        |         |

| 9.3.2                | QBus Execution Order              |         |

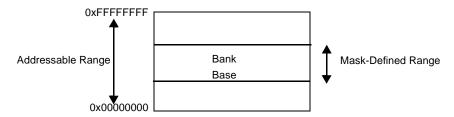

| 9.3.2                | QBus Banks                        |         |

| 9.3.4                | Bank Registers.                   |         |

| 9.3.5                | Bank Addressing                   |         |

| 9.3.6                | Reservation Process.              |         |

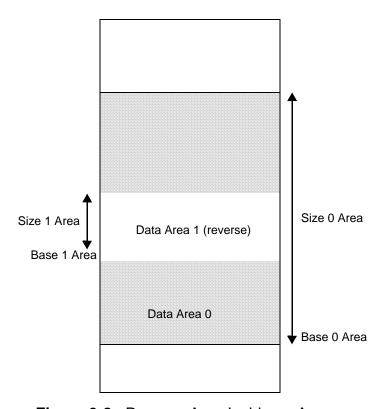

| 9.3.7                | Setting a Data Area               |         |

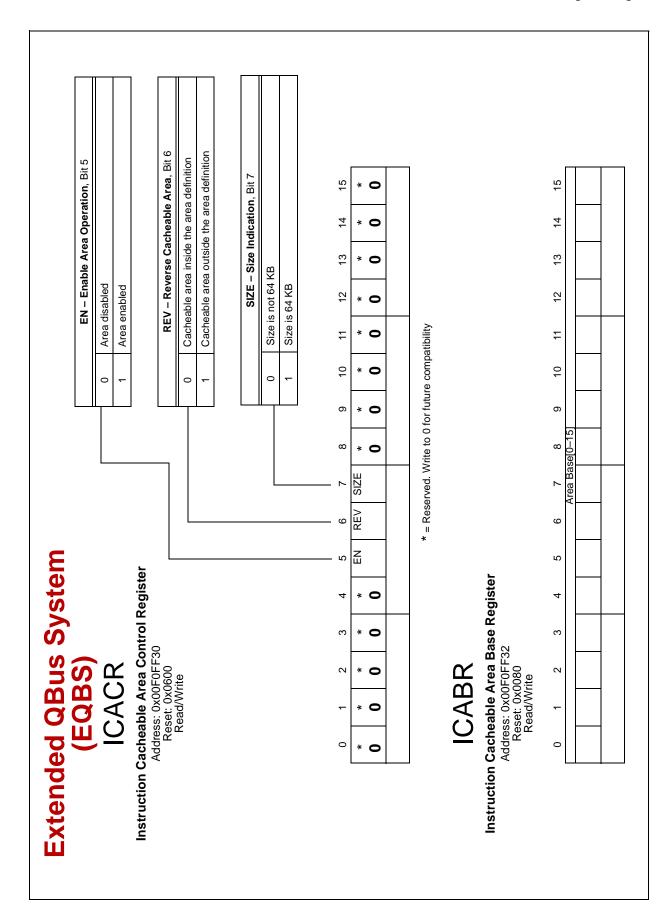

| 9.3.8                | Instruction Cacheable Area        |         |

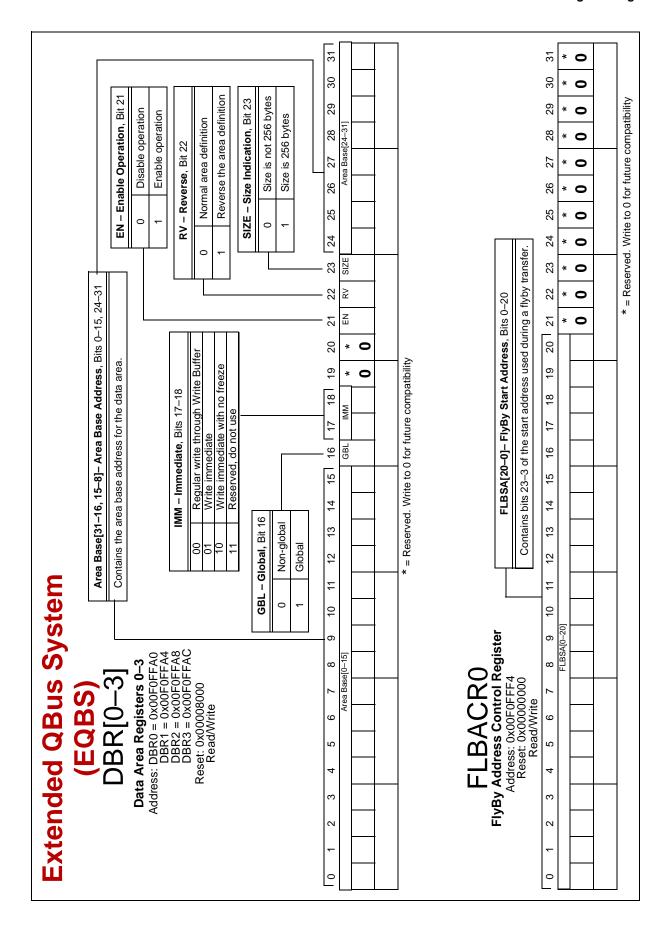

| 9.3.9                | EQBS Programming Model            |         |

| 9.4                  | Instruction Cache (ICache)        |         |

| 9.4.1                | ICache Attributes                 |         |

| 9.4.1                | Debugging                         |         |

| 9.4.2                | Multi-Task Support                |         |

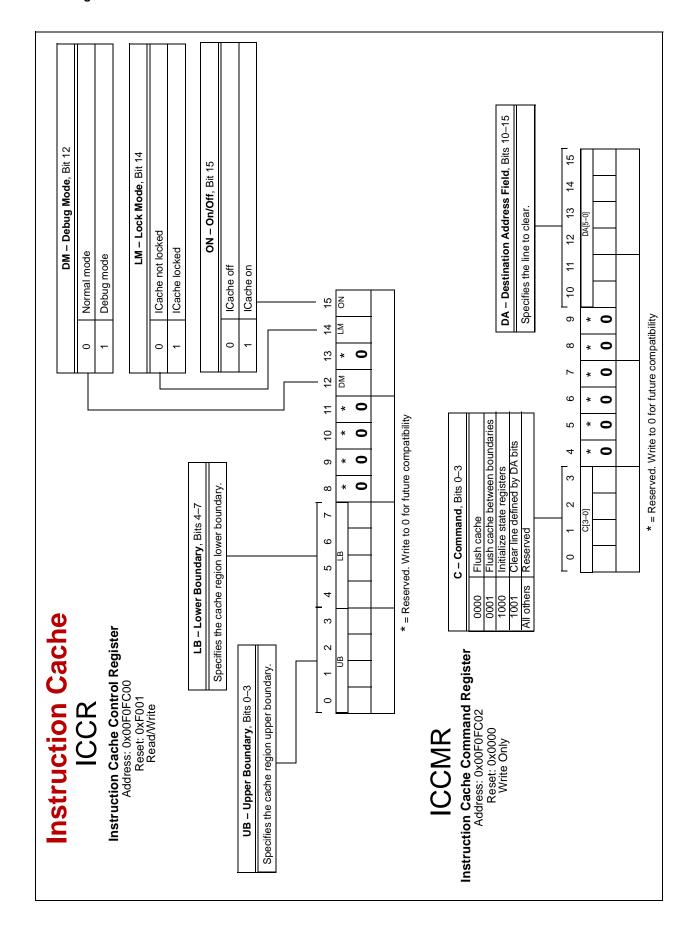

| 9.4.3                | ICache Programming Model          |         |

| 9.4.4                | Modes                             | 9-34    |

| , <del>-, -,  </del> | (vi) B B -3                       | -/- 1/4 |

| 9.4.4.2            | Commands                                            |

|--------------------|-----------------------------------------------------|

| 9.4.4.3            | Reads                                               |

| 9.4.4.4            | Restrictions                                        |

| 9.4.4.5            | ICache Registers                                    |

| 9.5                | Programmable Interrupt Controller (PIC)             |

| 9.6                | Local Interrupt Controller (LIC)                    |

| 9.7                | Extended Core Power Saving Modes                    |

| 9.7.1              | Extended Core Wait Mode                             |

| 9.7.2              | Extended Core Stop Mode                             |

| 10                 | MQBus and M2 Memory                                 |

| 10.1               | MQBus Arbitration Model                             |

| 10.1               | M2 Memory                                           |

| 10.2               | Reservation Operation                               |

| 10.5               | Reservation Operation                               |

| 11                 | SQBus                                               |

| 11.1               | System Bus Interface                                |

| 11.2               | Reservation (Atomic) Operation                      |

| 11.2.1             | Reservation Operation in the SQBus Arbiter          |

| 11.2.2             | Reservation Operation on the System Bus             |

| 11.2.3             | Conditions for Failure of the Reservation Operation |

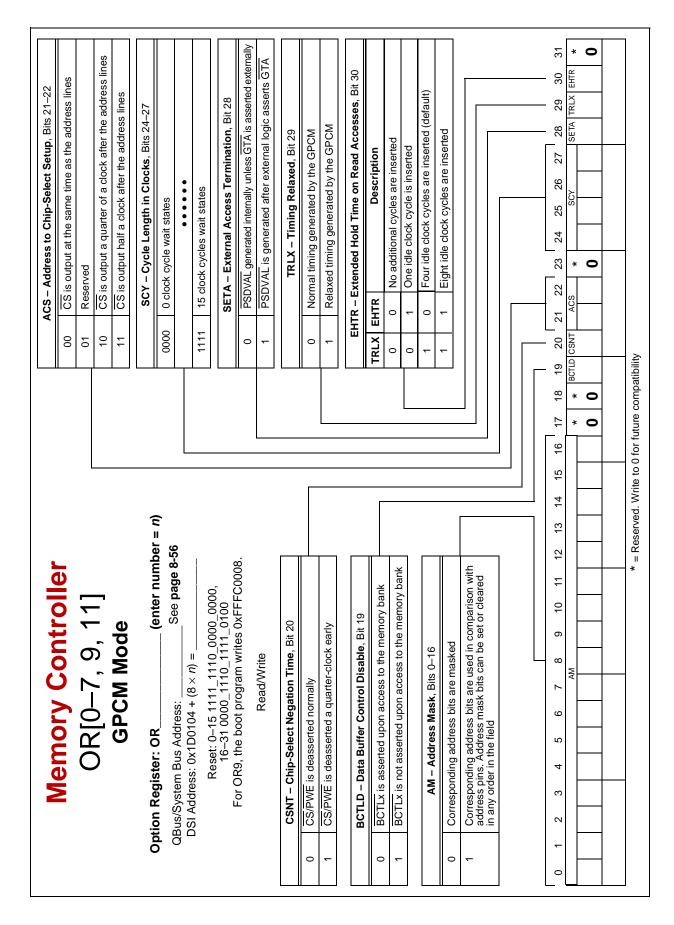

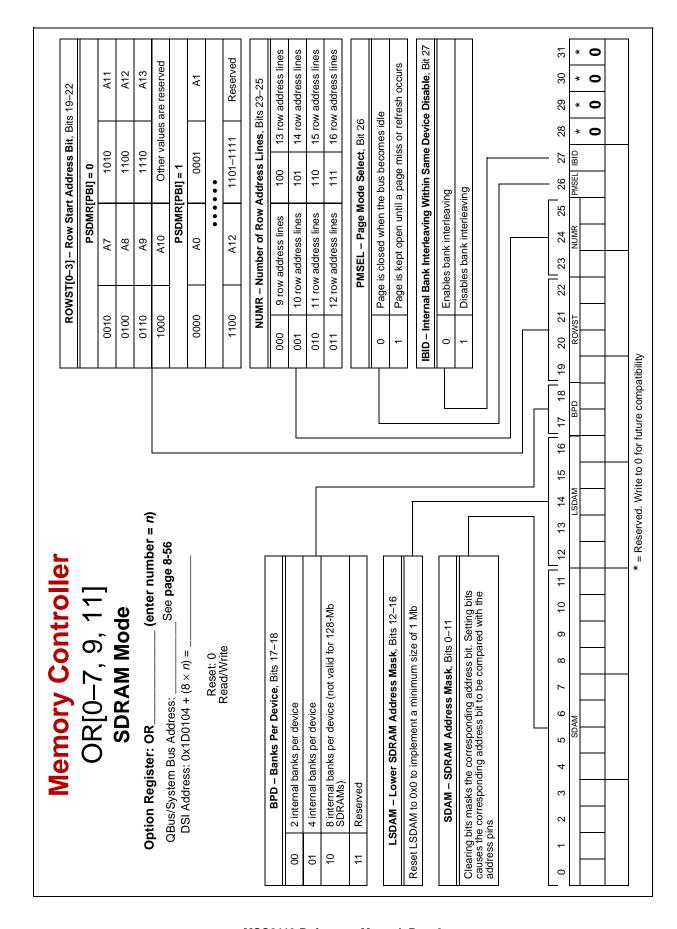

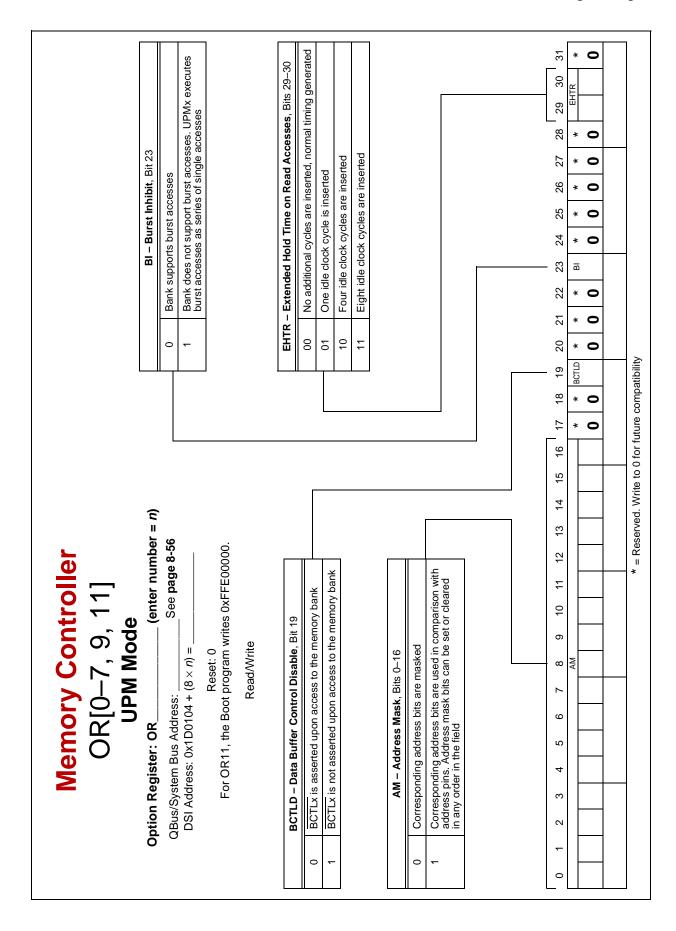

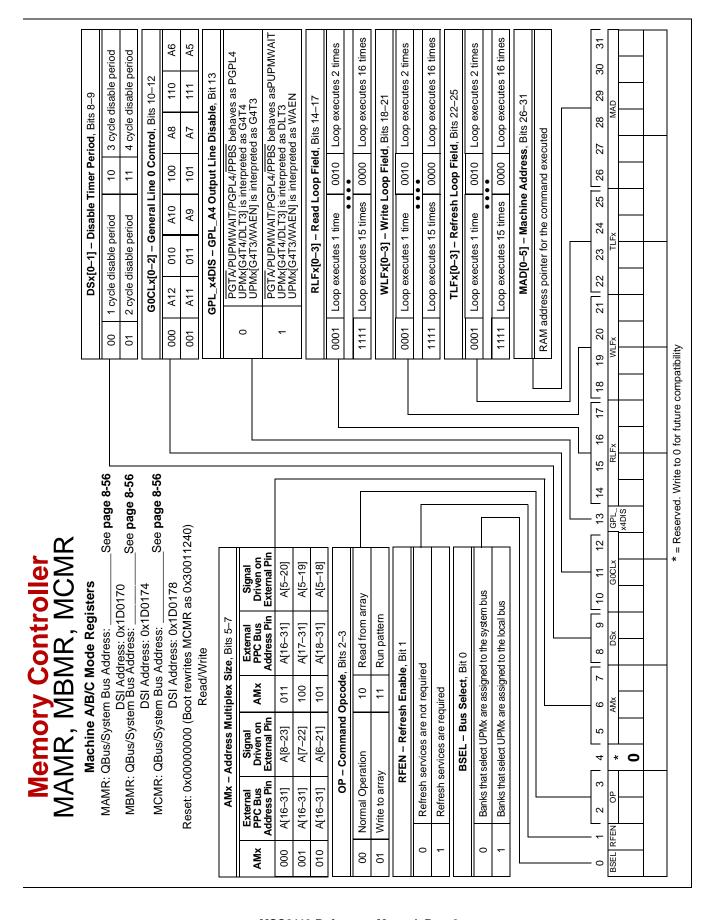

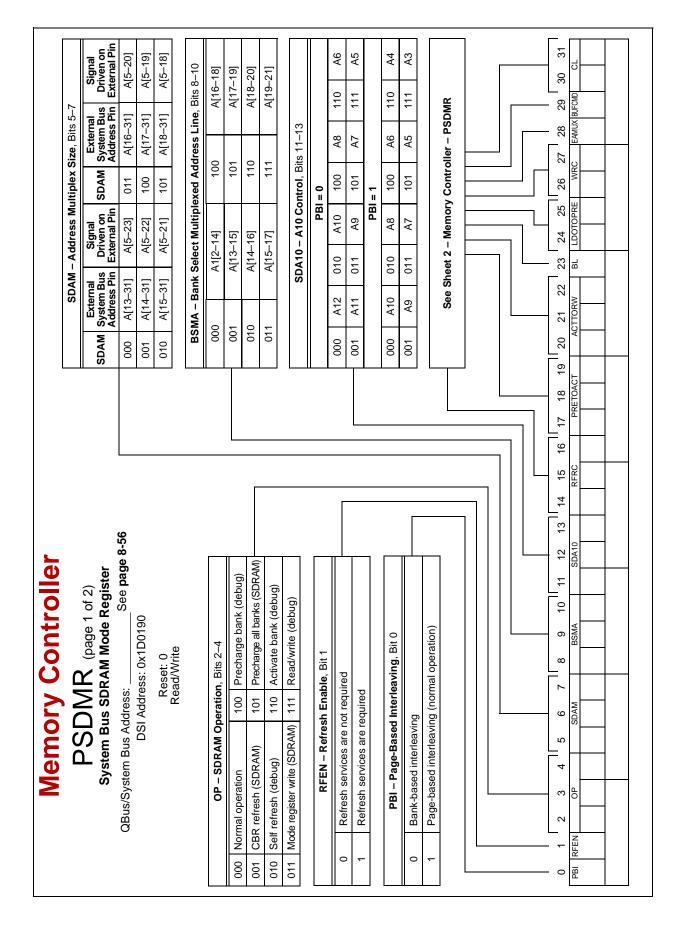

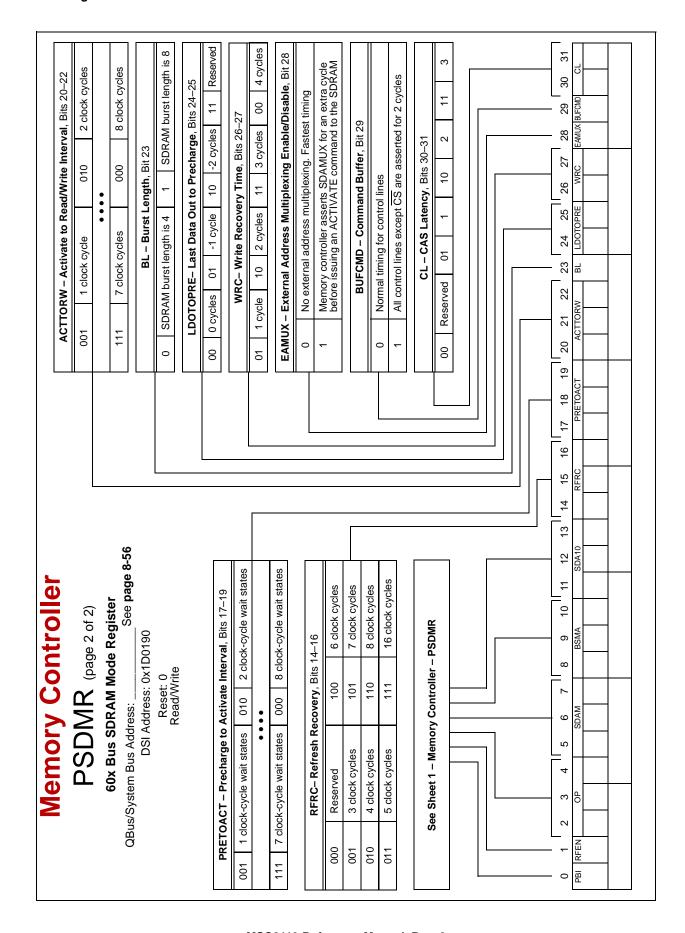

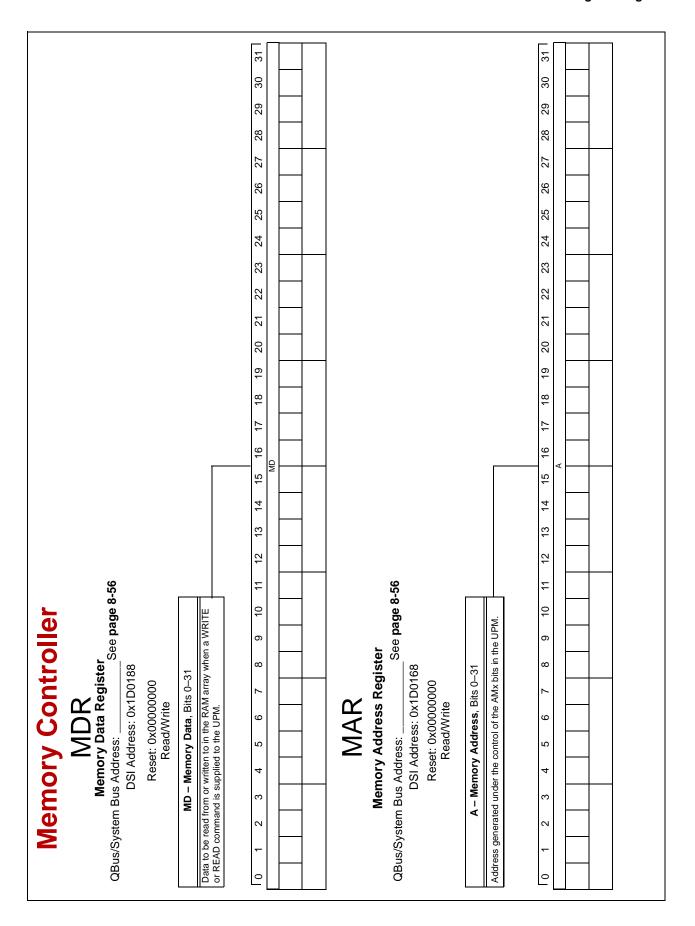

| 12                 | Memory Controller                                   |

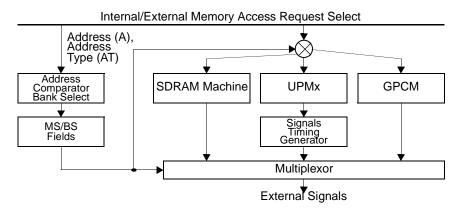

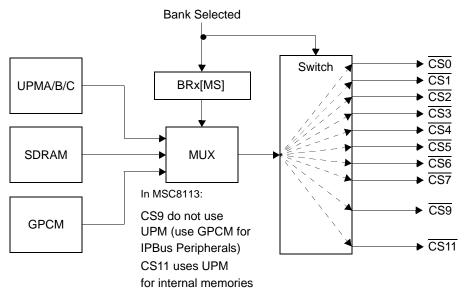

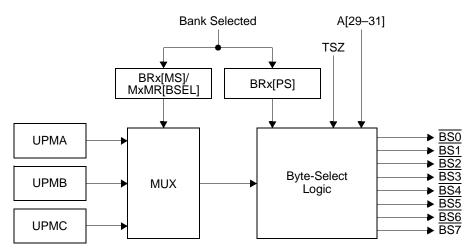

| 12.1               | Basic Architecture                                  |

| 12.1.1             | Address and Address Space Checking                  |

| 12.1.1             | Page Hit Checking                                   |

| 12.1.2             |                                                     |

| 12.1.3             | Parity Generation and Checking                      |

| 12.1.4             | Machine Check Interrupt (MCP) Generation            |

| 12.1.5             | Data Buffer Controls (BCTL[0–1])                    |

| 12.1.7             | Atomic Bus Operation                                |

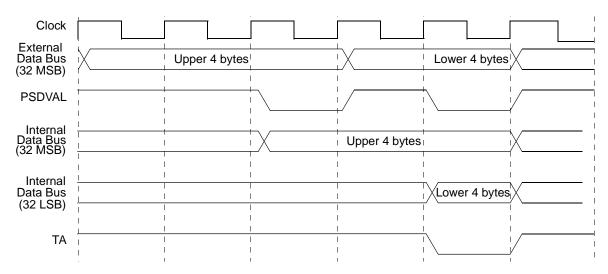

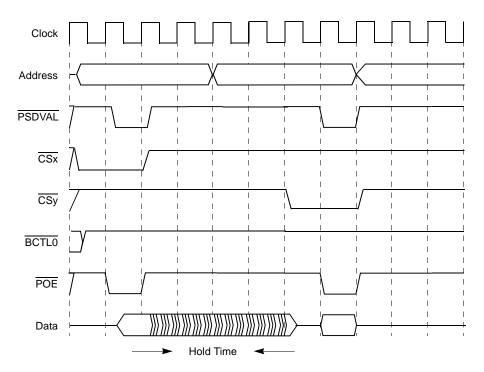

| 12.1.7             | Partial Data Valid Indication (PSDVAL)              |

| 12.1.8             | ECC/Parity Byte-Select (PPBS)                       |

| 12.1.9             |                                                     |

| 12.1.10            | Data Pipelining                                     |

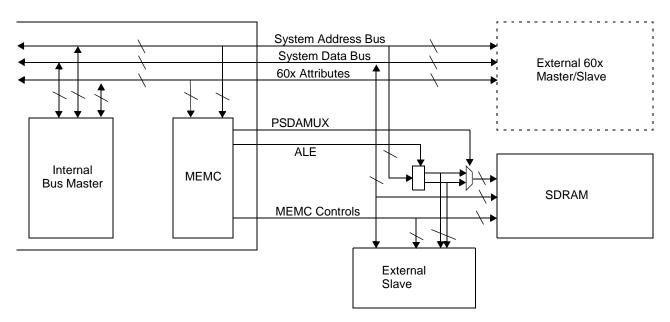

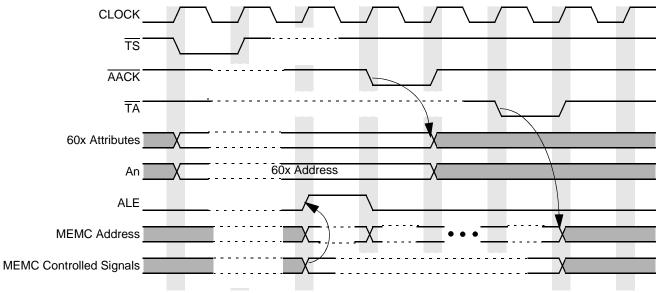

|                    | 60x-Compatible Mode                                 |

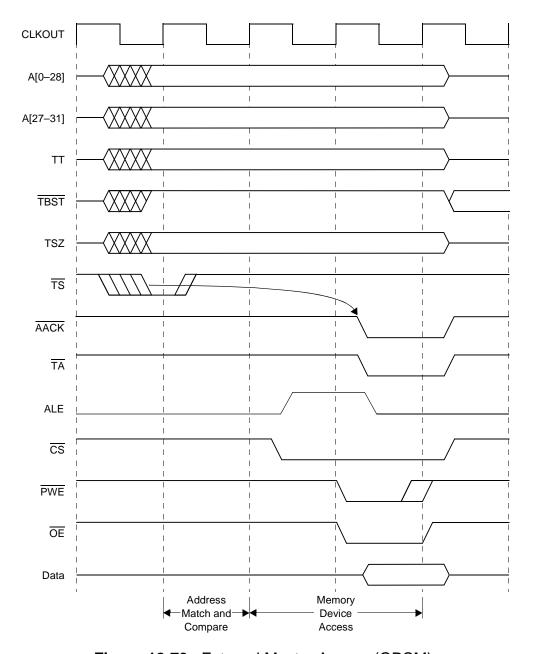

| 12.1.12<br>12.1.13 | External Memory Controller Support                  |

|                    | External Address Latch Enable Signal (ALE)          |

| 12.1.14            | BADDR[27–31] Signal Connections                     |

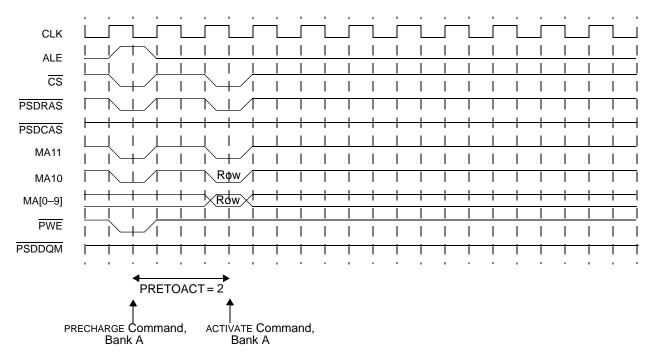

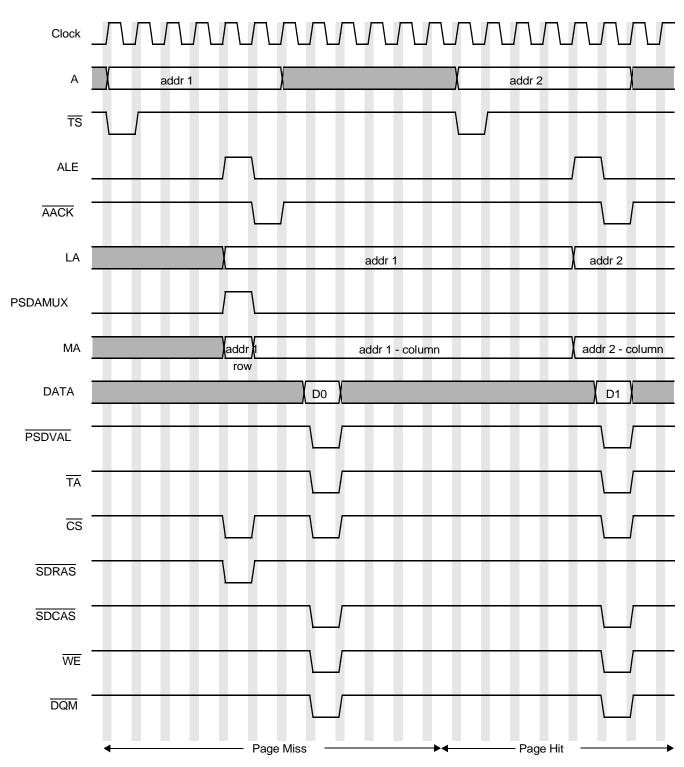

| 12.2               | SDRAM Machine                                       |

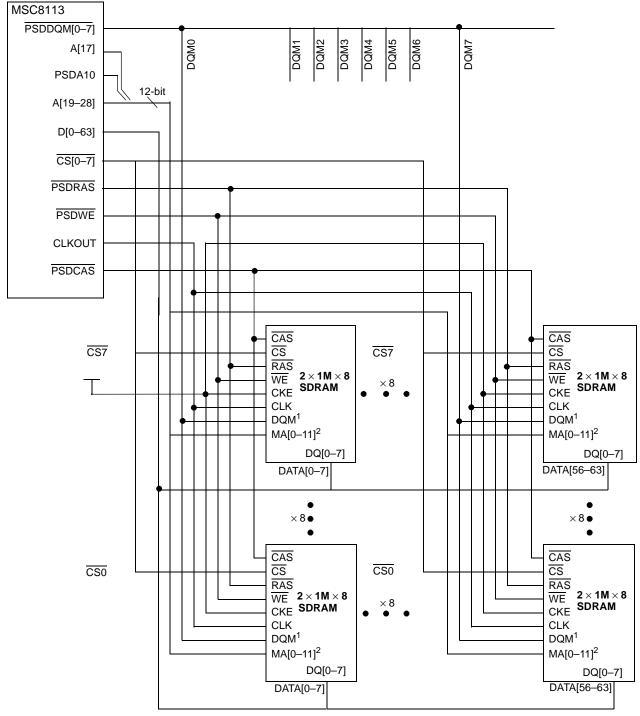

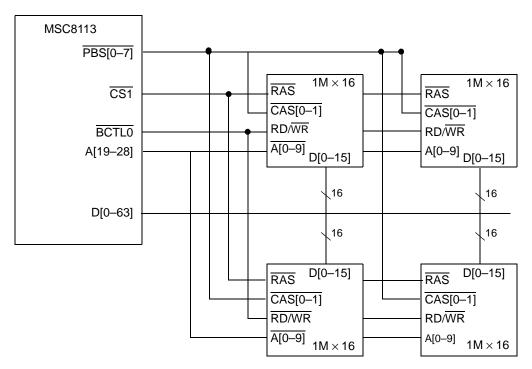

| 12.2.1             | Supported SDRAM Configurations                      |

| 12.2.2             | SDRAM Power-On Initialization                       |

Freescale Semiconductor ix

| 12.2.3    | JEDEC-Standard SDRAM Interface Commands               | 12-16 |

|-----------|-------------------------------------------------------|-------|

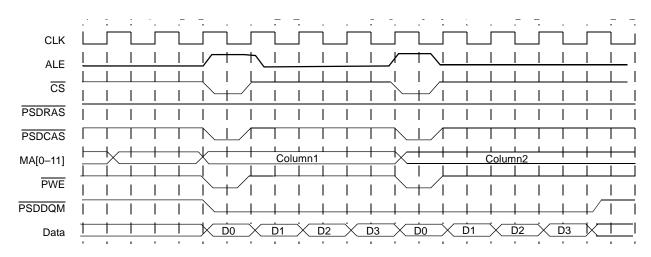

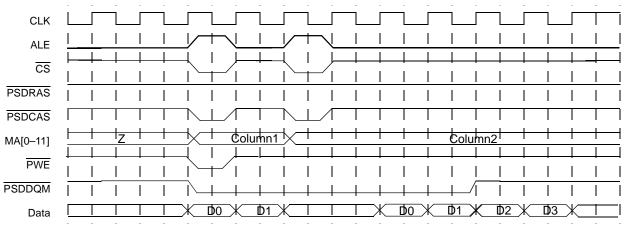

| 12.2.4    | Page-Mode Support and Pipeline Accesses               | 12-16 |

| 12.2.5    | Bank Interleaving                                     | 12-17 |

| 12.2.6    | BNKSEL Signals in Single-MSC8113 Bus Mode             | 12-18 |

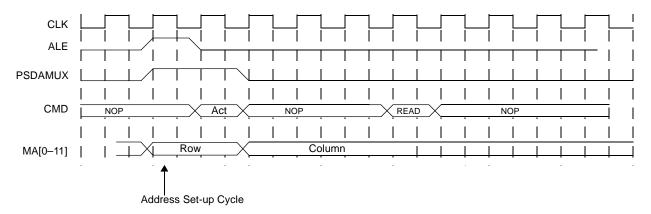

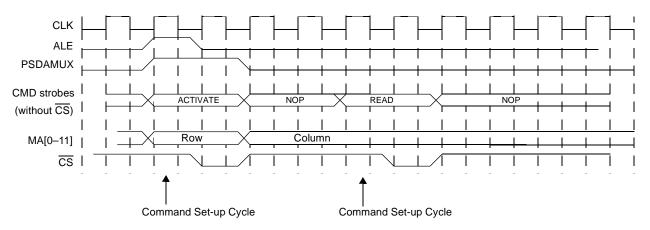

| 12.2.7    | SDRAM Address Multiplexing (SDAM and BSMA)            | 12-18 |

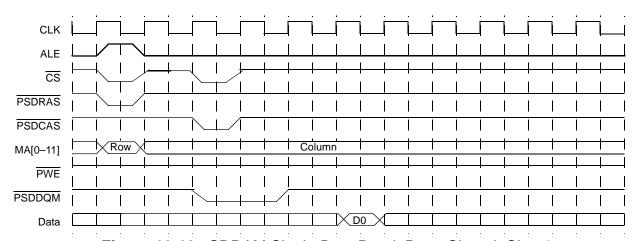

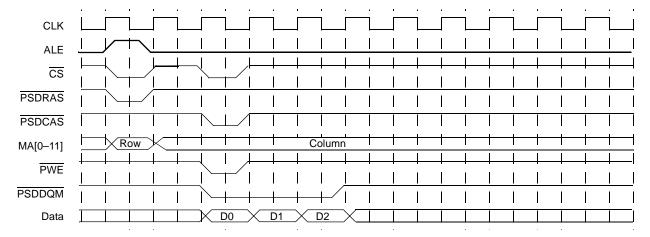

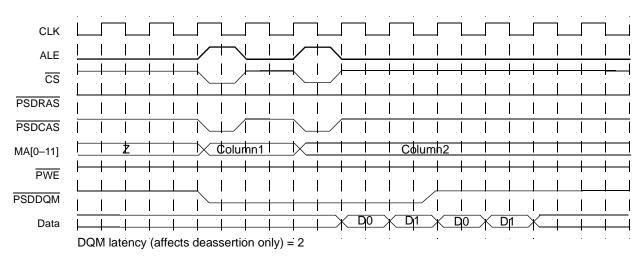

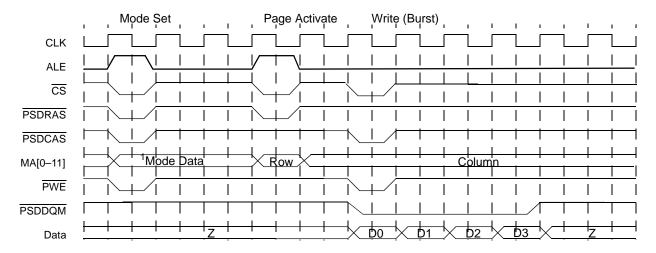

| 12.2.8    | SDRAM Read/Write Transactions                         | 12-20 |

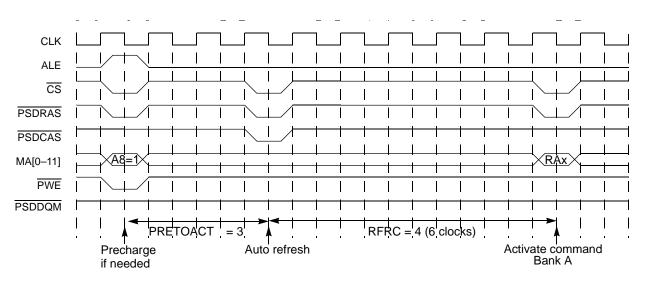

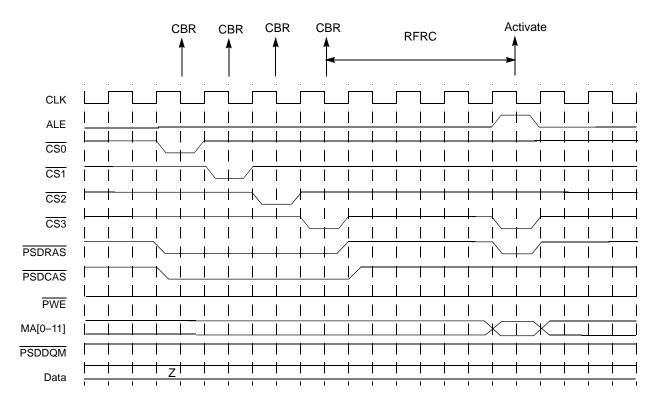

| 12.2.9    | SDRAM Refresh                                         | 12-20 |

| 12.2.10   | SDRAM Signals: Device-Specific Parameters             | 12-20 |

| 12.2.11   | SDRAM Signals: General Interface Timing               | 12-25 |

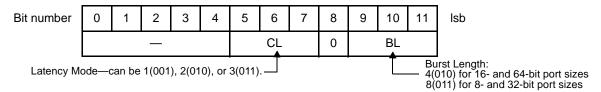

| 12.2.12   | SDRAM Signals: mode-set Command Timing                | 12-28 |

| 12.2.13   | SDRAM Signals: Refresh Timing                         | 12-28 |

| 12.2.14   | SDRAM Configuration Examples                          | 12-29 |

| 12.2.14.1 | SDRAM Configuration Example (Page-Based Interleaving) | 12-29 |

| 12.2.14.2 | SDRAM Configuration Example (Bank-Based Interleaving) | 12-31 |

| 12.3      | General-Purpose Chip-Select Machine (GPCM)            |       |

| 12.3.1    | GPCM Signals: Timing Configuration                    |       |

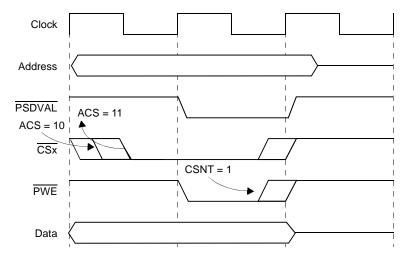

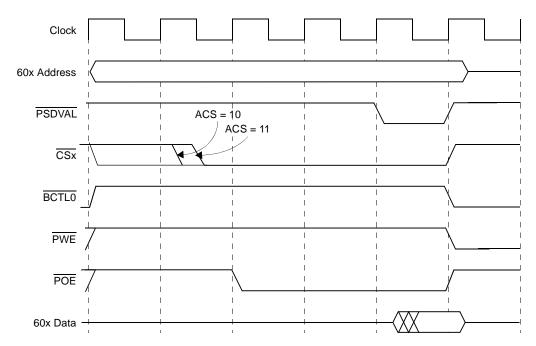

| 12.3.1.1  | Chip-Select Assertion Timing                          | 12-34 |

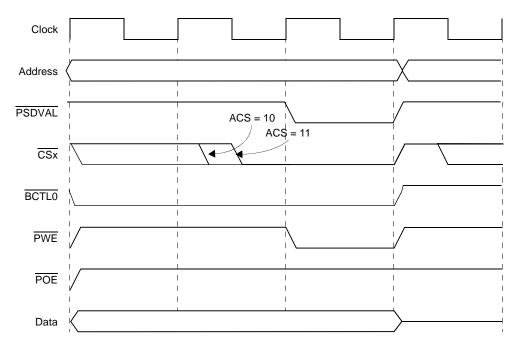

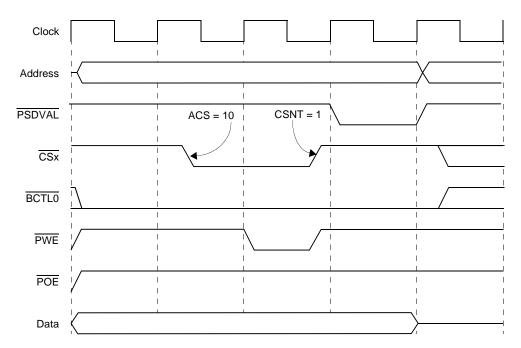

| 12.3.1.2  | Chip-Select and Write Enable Deassertion Timing       | 12-36 |

| 12.3.1.3  | Relaxed Timing                                        |       |

| 12.3.1.4  | Output Enable (POE) Timing                            |       |

| 12.3.1.5  | Programmable Wait State Configuration                 |       |

| 12.3.1.6  | Extended Hold Time on Read Accesses                   |       |

| 12.3.2    | GPCM Signals: External Access Termination             | 12-42 |

| 12.3.3    | Boot Chip-Select Operation                            |       |

| 12.3.4    | Differences Between MPC8xx GPCM and MSC8113 GPCM      |       |

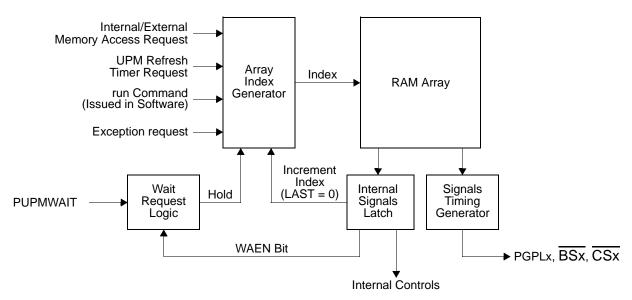

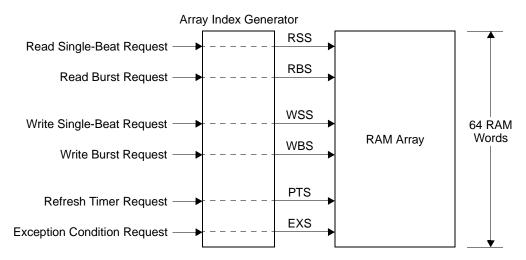

| 12.4      | User-Programmable Machines (UPMs)                     | 12-45 |

| 12.4.1    | Requests                                              | 12-46 |

| 12.4.1.1  | Memory Access Requests                                | 12-47 |

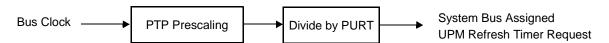

| 12.4.1.2  | UPM Refresh Timer Requests                            |       |

| 12.4.1.3  | Software Requests—run Command                         |       |

| 12.4.1.4  | Exception Requests                                    |       |

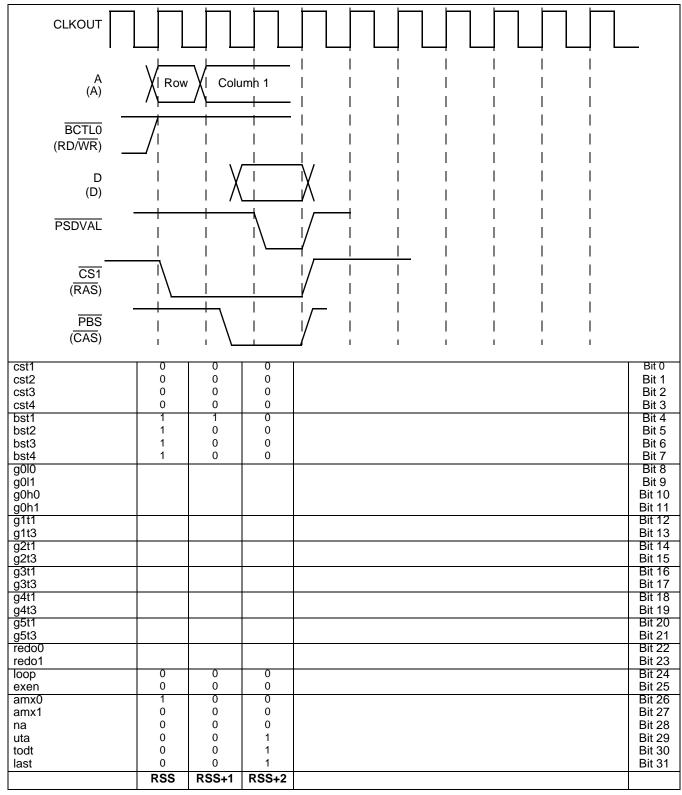

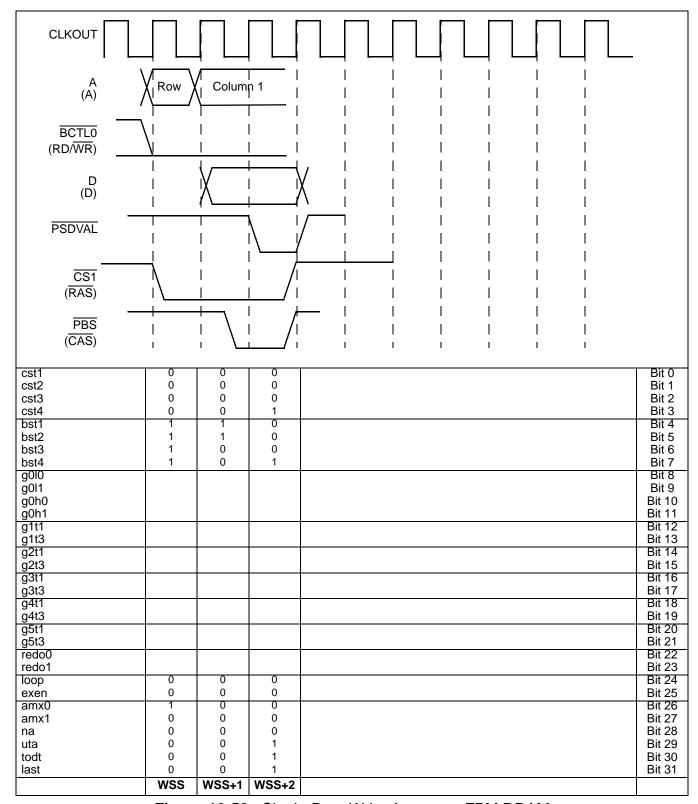

| 12.4.2    | Programming the UPMs                                  | 12-49 |

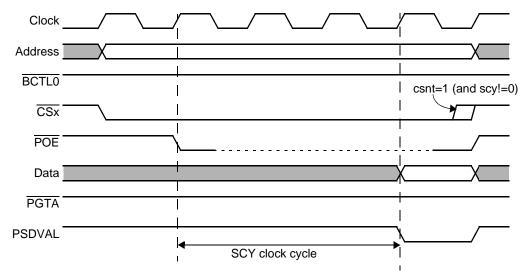

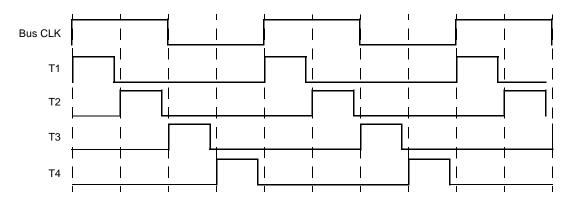

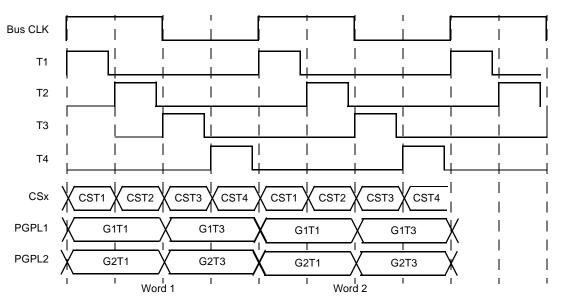

| 12.4.3    | Clock Timing                                          |       |

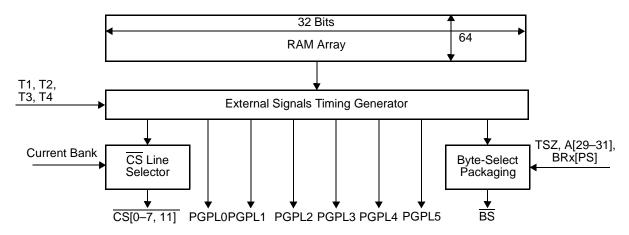

| 12.4.4    | RAM Array                                             |       |

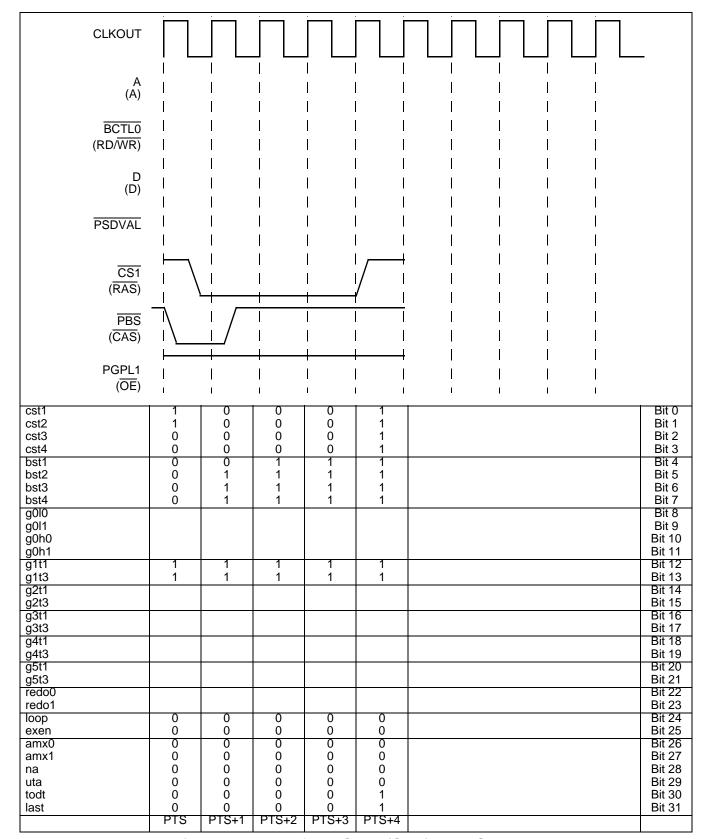

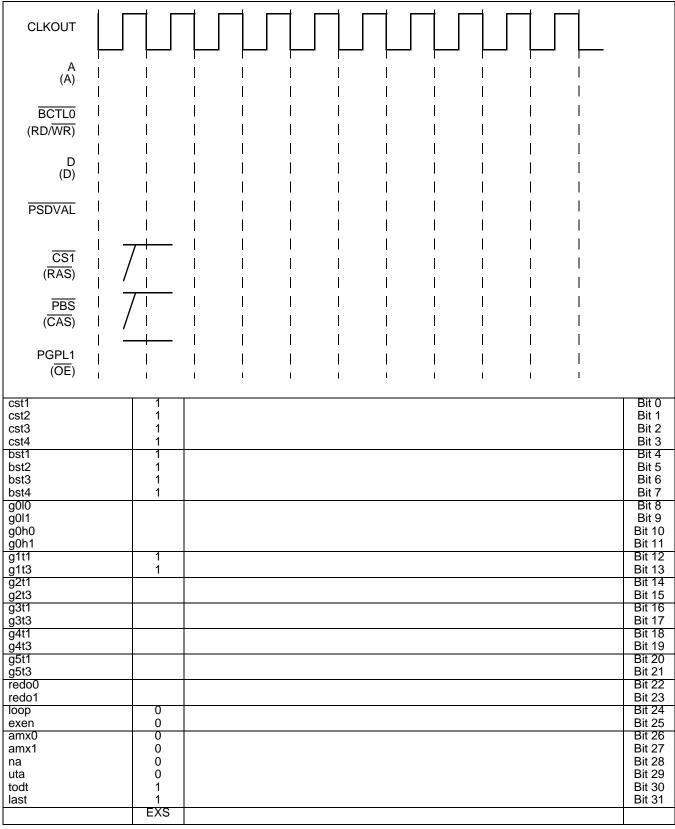

| 12.4.4.1  | RAM Words                                             | 12-51 |

| 12.4.4.2  | Last Word (LAST)                                      | 12-59 |

| 12.4.4.3  | Address Multiplexing                                  |       |

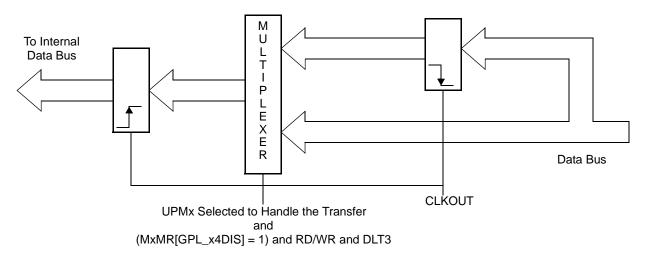

| 12.4.4.4  | Data Valid and Data Sample Control                    |       |

| 12.4.4.5  | Disable Timer Mechanism (TODT)                        |       |

| 12.4.4.6  | Signal Deassertion                                    |       |

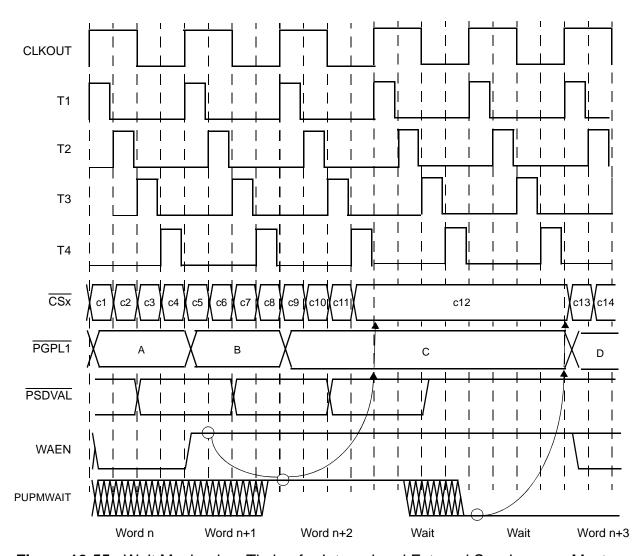

| 12447     | Wait Mechanism                                        |       |

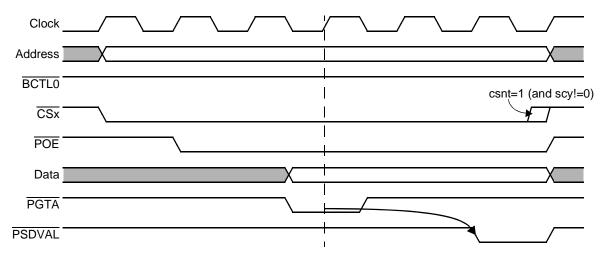

| 12.4.4.8 | Extended Hold Time on Read Accesses                 | 12-61 |

|----------|-----------------------------------------------------|-------|

| 12.4.5   | DRAM Configuration Example                          | 12-62 |

| 12.4.6   | Interface Examples                                  | 12-63 |

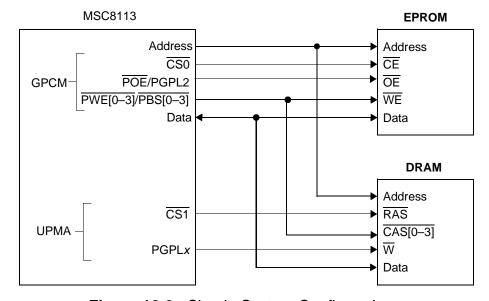

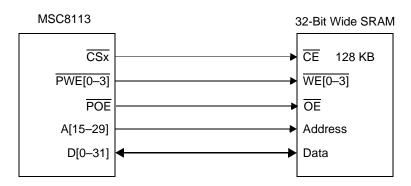

| 12.4.6.1 | Memory System Interface Example Using UPM           | 12-63 |

| 12.4.6.2 | EDO Interface Example                               | 12-74 |

| 12.4.7   | Differences Between MPC8xx UPM and MSC8113 UPM      | 12-82 |

| 12.5     | Handling Devices With Slow or Variable Access Times | 12-82 |

| 12.5.1   | Hierarchical Bus Interface Example                  | 12-83 |

| 12.5.2   | Slow Devices Example                                |       |

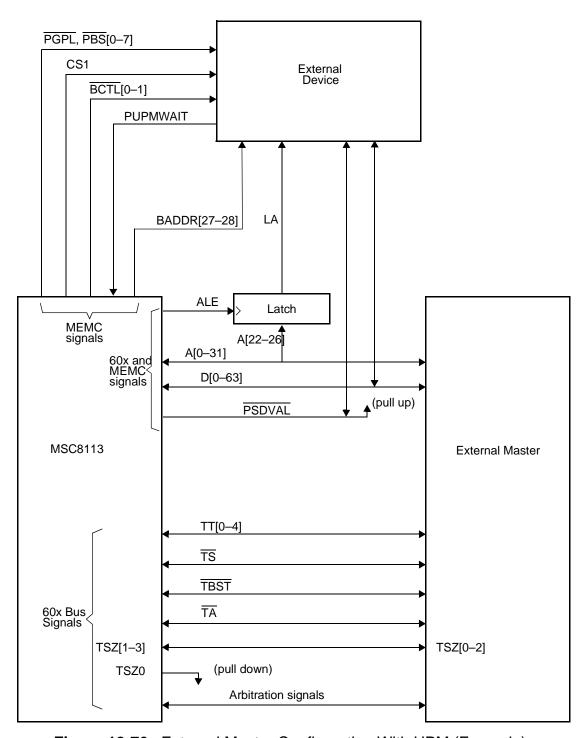

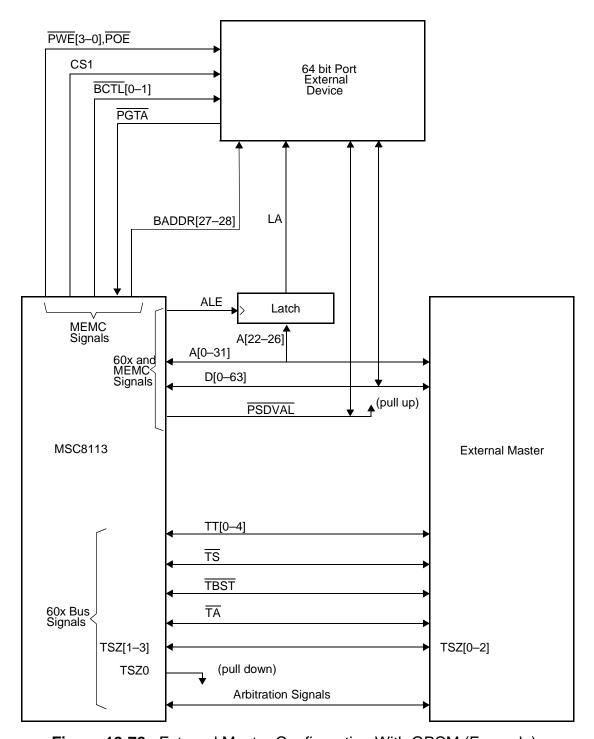

| 12.6     | External Master Support (60x-Compatible Mode)       |       |

| 12.6.1   | Strict 60x-Compatible External Masters              | 12-84 |

| 12.6.2   | MSC8113-Type External Masters                       |       |

| 12.6.3   | Extended Controls in 60x-Compatible Mode            |       |

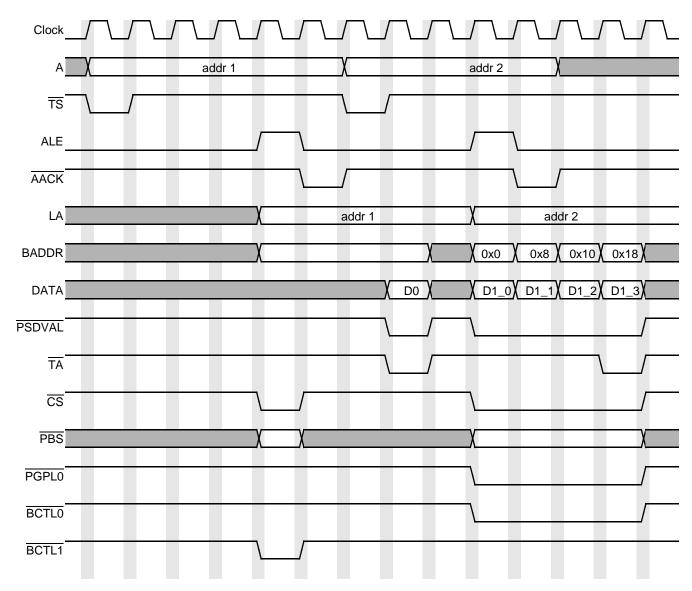

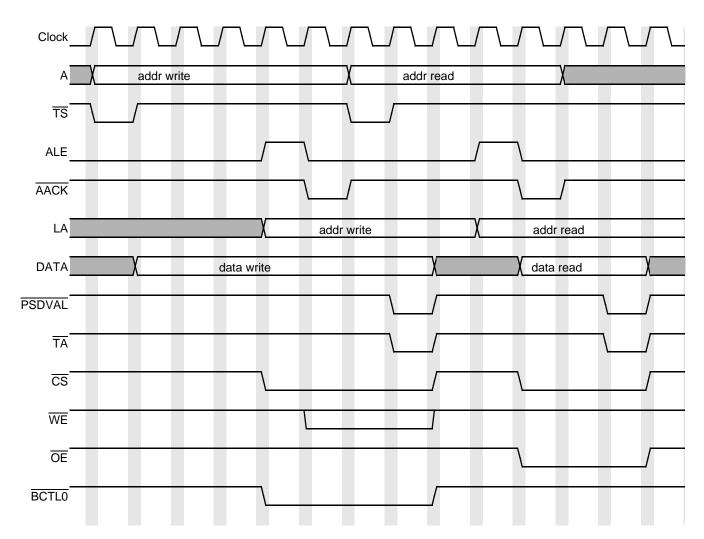

| 12.6.4   | Address Incrementing for External Bursting Masters  |       |

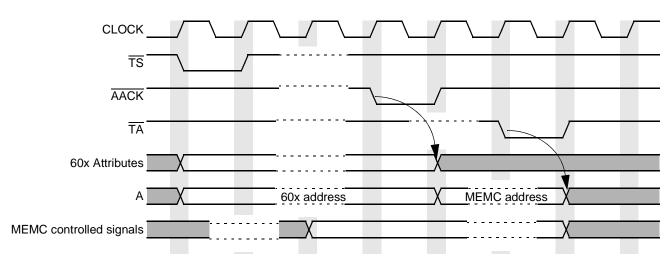

| 12.6.5   | External Masters Timing                             |       |

| 12.7     | Internal SRAM and IPBus Peripherals Support         |       |

| 12.7.1   | UPM Programming Example — Internal SRAM             |       |

| 12.7.2   | GPCM Programming Example, IPBus Peripherals         |       |

| 12.7.3   | Flyby Mode                                          |       |

| 12.8     | Memory Controller Programming Model                 |       |

| 40       |                                                     |       |

| 13       | System Bus                                          |       |

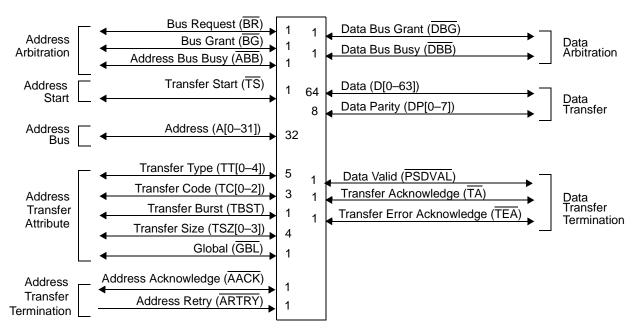

| 13.1     | System Bus Signals                                  | 13-1  |

| 13.1.1   | Address Arbitration                                 | 13-3  |

| 13.1.2   | Address Start                                       | 13-5  |

| 13.1.3   | Address Bus                                         | 13-5  |

| 13.1.4   | Address Transfer Attribute                          | 13-6  |

| 13.1.5   | Address Transfer Termination                        | 13-8  |

| 13.1.6   | Data Arbitration                                    | 13-9  |

| 13.1.7   | Data Transfer                                       | 13-10 |

| 13.1.8   | Data Transfer Termination                           | 13-12 |

| 13.2     | 60x-Compatible Bus Protocols                        | 13-14 |

| 13.2.1   | System Bus Operating Modes                          | 13-14 |

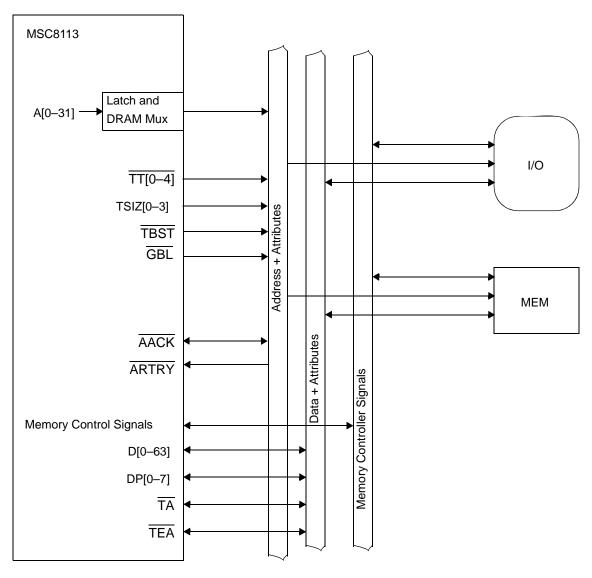

| 13.2.1.1 | Single MSC8113 Bus Mode                             | 13-14 |

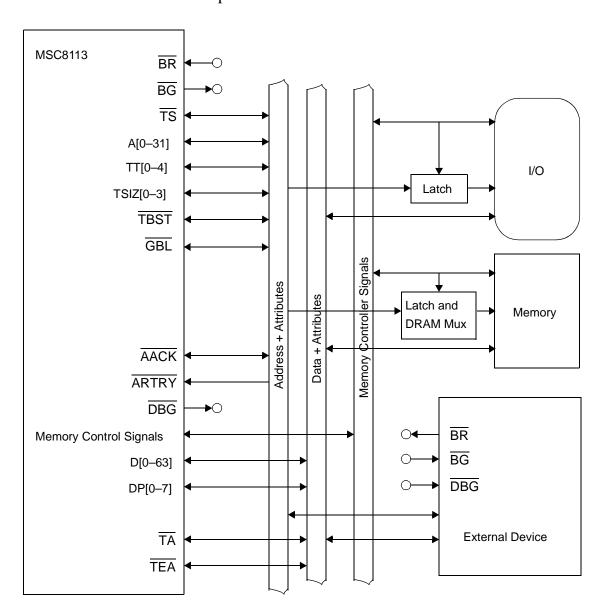

| 13.2.1.2 | 60x-Compatible Bus Mode                             | 13-16 |

| 13.2.2   | System Bus Protocols                                | 13-17 |

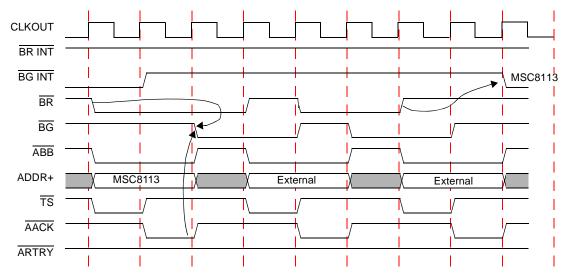

| 13.2.2.1 | Arbitration Phase                                   |       |

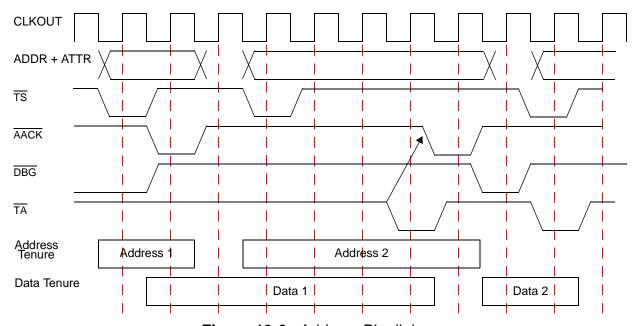

| 13.2.2.2 | Address Pipelining and Split-Bus Transactions       |       |

| 13.2.2.3 | Memory Coherency                                    |       |

| 13.2.3   | Address Tenure Operations                           |       |

| 13.2.3.1 | Address Arbitration                                 |       |

Freescale Semiconductor xi

| 13.2.3.2  | Address Pipelining                                         | 13-21 |

|-----------|------------------------------------------------------------|-------|

| 13.2.3.3  | Address Transfer Attribute Signals                         | 13-22 |

| 13.2.3.4  | Burst Ordering During Data Transfers                       | 13-24 |

| 13.2.3.5  | Effect of Alignment on Data Transfers                      |       |

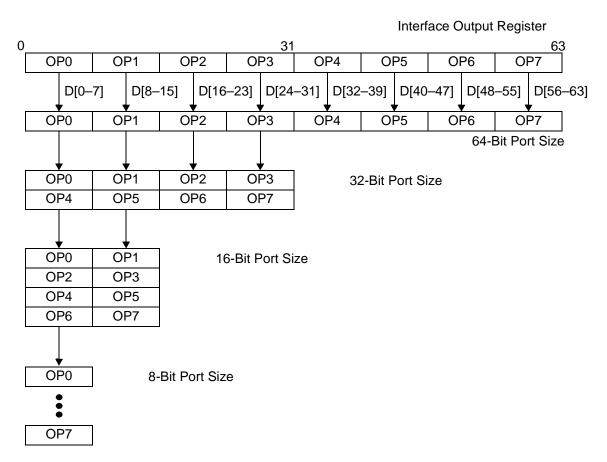

| 13.2.3.6  | Effect of Port Size on Data Transfers                      | 13-26 |

| 13.2.3.7  | 60x-Compatible System Bus Mode—Size Calculation            | 13-30 |

| 13.2.3.8  | Extended Transfer Mode                                     | 13-31 |

| 13.2.3.9  | Address Transfer Termination                               | 13-33 |

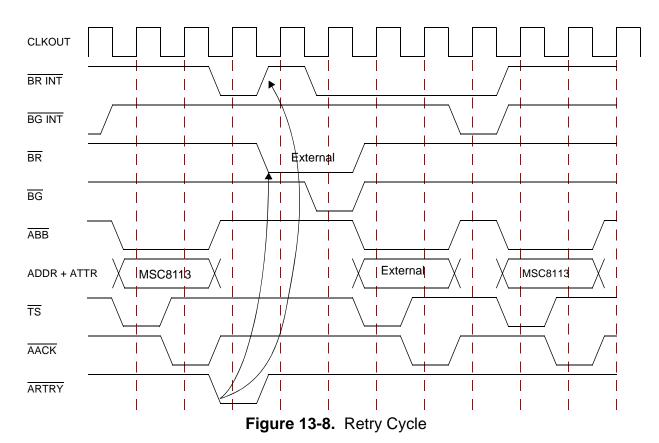

| 13.2.3.10 | Address Retried With ARTRY Signal                          | 13-33 |

| 13.2.3.11 | Address Tenure Timing Configuration                        | 13-34 |

| 13.2.3.12 | Pipeline Control                                           | 13-35 |

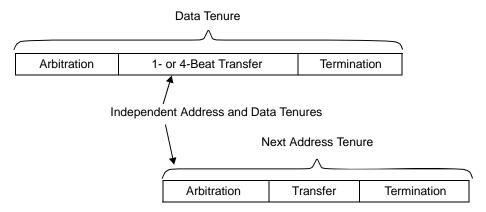

| 13.2.4    | Data Tenure Operations                                     | 13-36 |

| 13.2.4.1  | Data Bus Arbitration                                       | 13-36 |

| 13.2.4.2  | Data Streaming Mode                                        | 13-36 |

| 13.2.4.3  | Data Bus Transfers and Normal Termination                  | 13-37 |

| 13.2.4.4  | Effect of ARTRY Assertion on Data Transfer and Arbitration | 13-38 |

| 13.2.4.5  | Port Size Data Bus Transfers and PSDVAL Termination        | 13-38 |

| 13.2.4.6  | Data Bus Termination by Assertion of TEA Signal            | 13-40 |

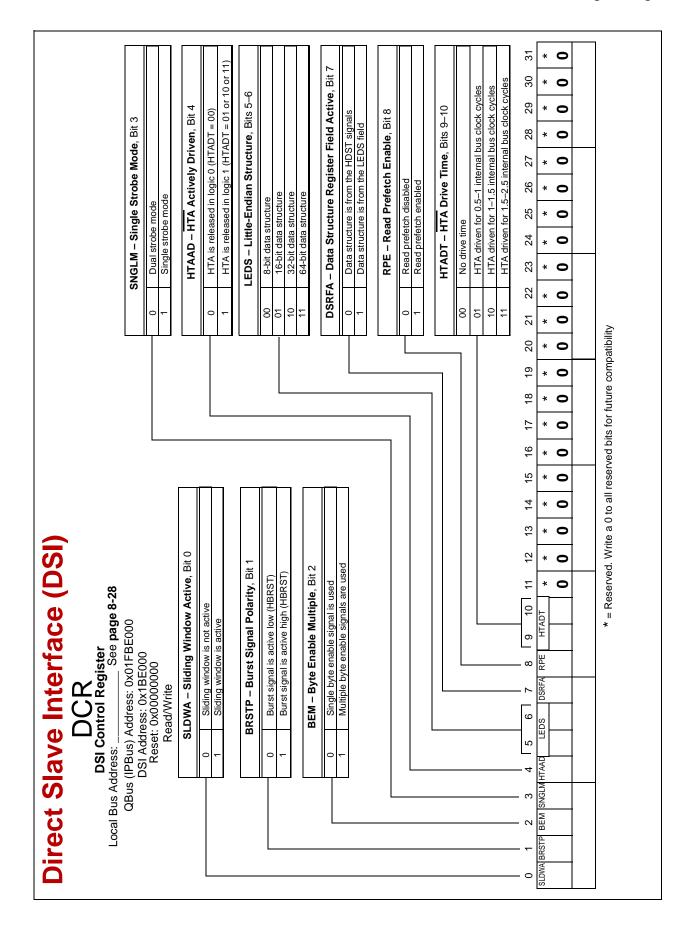

| 14        | Direct Slave Interface (DSI)                               |       |

| 14.1      | Data Bus                                                   | 14-3  |

| 14.1.1    | Data Bus Width                                             | 14-3  |

| 14.1.2    | DCR[BEM] Bit Access Considerations                         | 14-4  |

| 14.2      | Address Bus                                                | 14-6  |

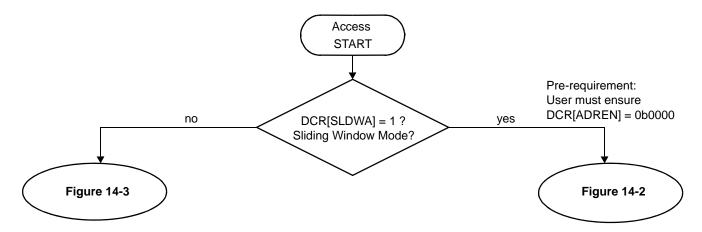

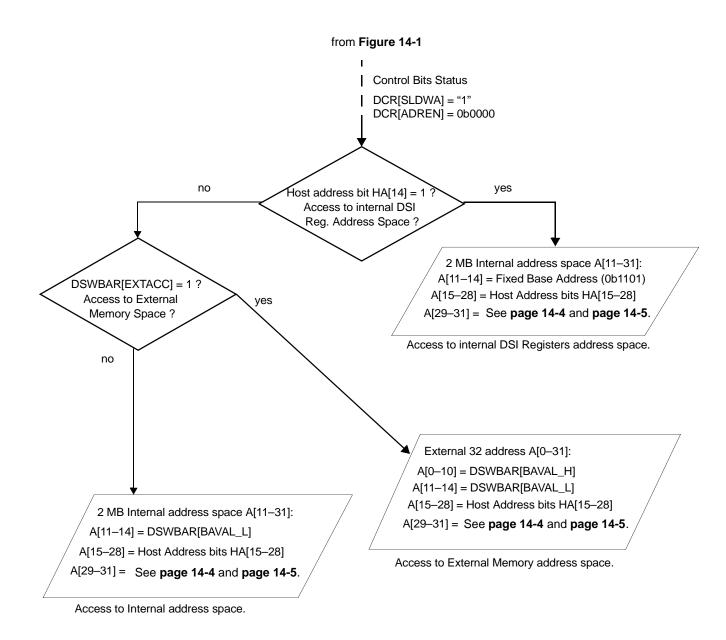

| 14.2.1    | Sliding Window Addressing Mode                             | 14-6  |

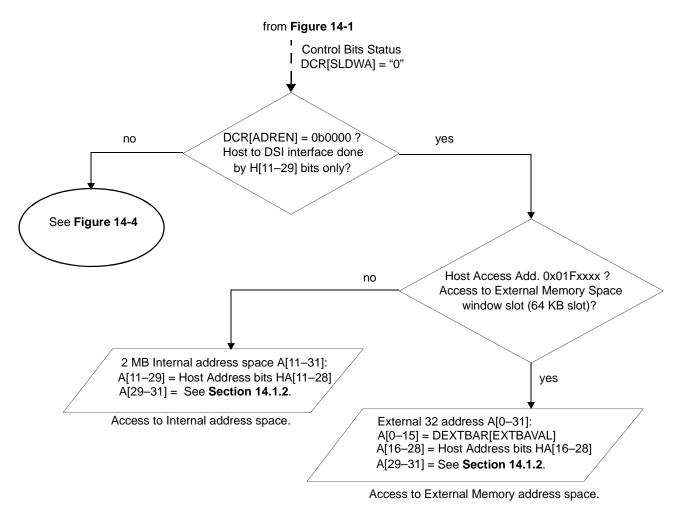

| 14.2.2    | Full Address Addressing Mode                               |       |

| 14.2.3    | Host Chip ID Signals (HCID[0–3])                           | 14-10 |

| 14.2.4    | DSI Endian Modes                                           | 14-10 |

| 14.3      | Host Access Modes and Timings                              |       |

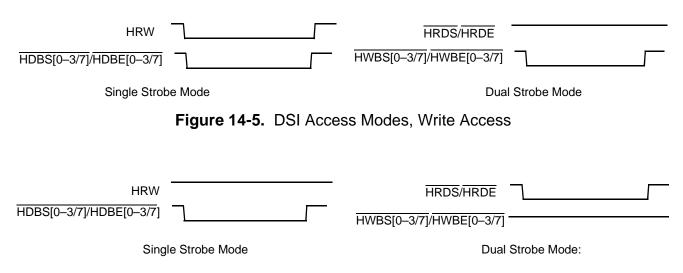

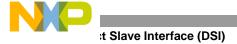

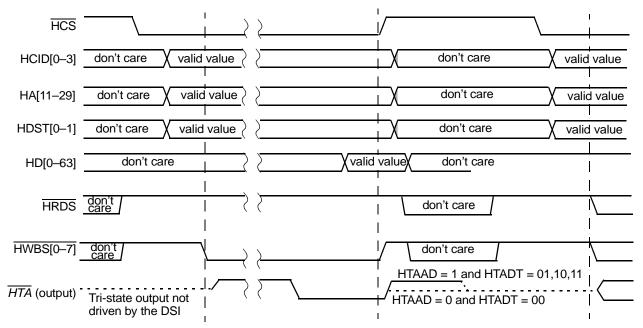

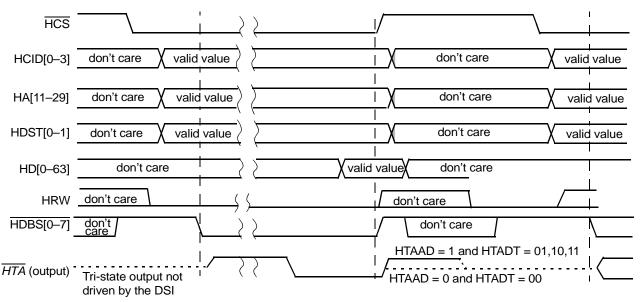

| 14.3.1    | Single Strobe Versus Dual Strobe Access Modes              | 14-11 |

| 14.3.2    | Synchronous Versus Asynchronous Access Mode                | 14-12 |

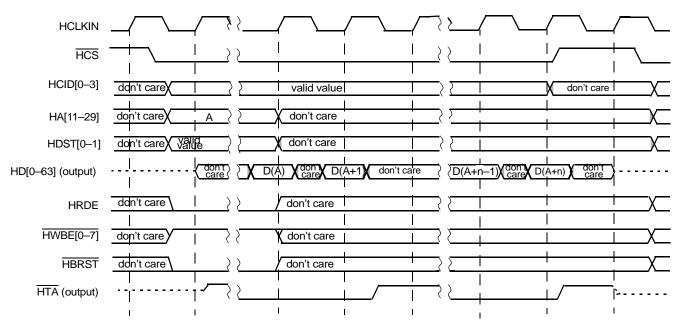

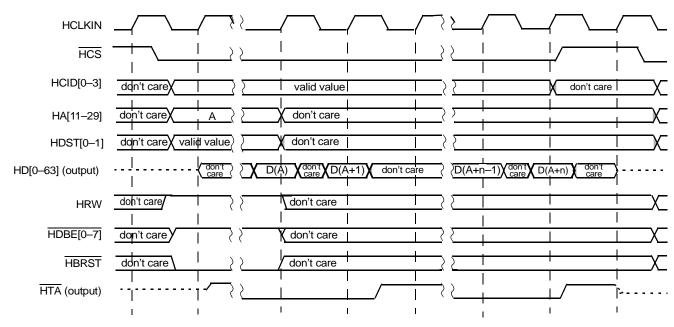

| 14.3.2.1  | Burst Transfers                                            |       |

| 14.3.2.2  | DSI Access Modes                                           | 14-13 |

| 14.3.3    | Asynchronous Mode Operation                                | 14-13 |

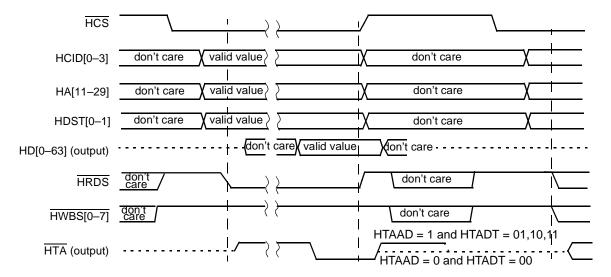

| 14.3.3.1  | Asynchronous Write Using Dual Strobe Mode                  | 14-13 |

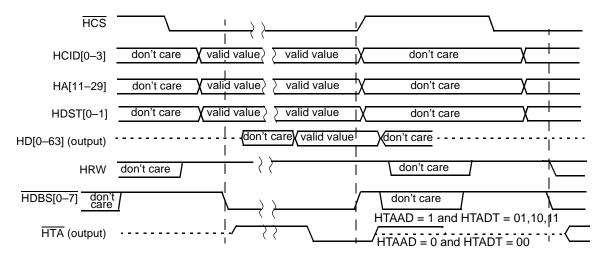

| 14.3.3.2  | Asynchronous Write Using Single Strobe Mode                | 14-15 |

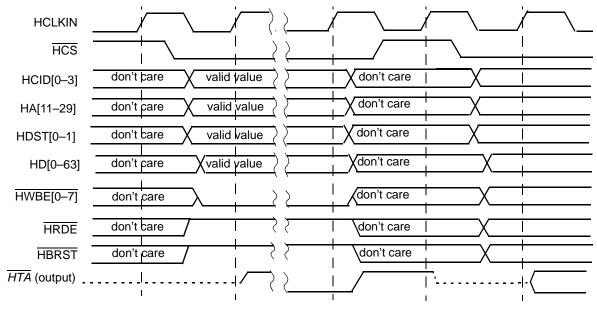

| 14.3.3.3  | Asynchronous Read Using Dual Strobe Mode                   |       |

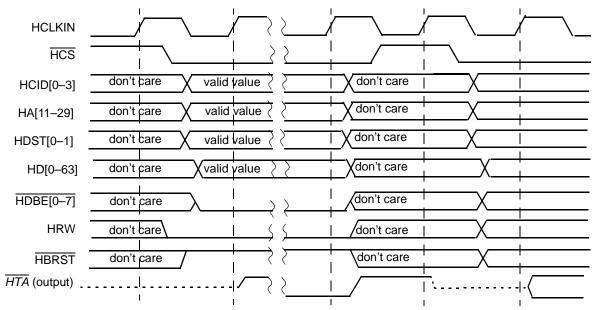

| 14.3.3.4  | Asynchronous Read Using Single Strobe Mode                 |       |

| 14.3.4    | Synchronous Mode Operation                                 |       |

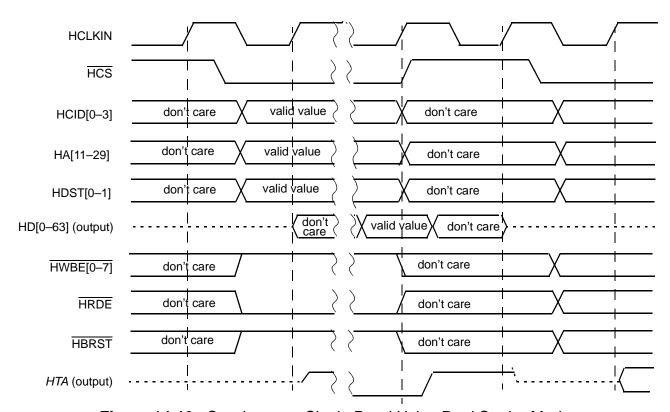

| 14.3.4.1  | Synchronous Single Write Using Dual Strobe Mode            |       |

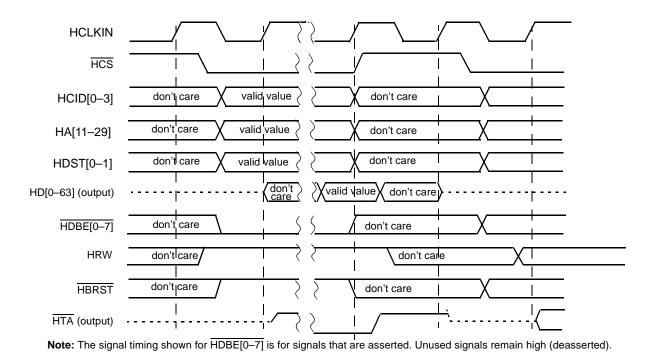

| 14.3.4.2  | e e e e e e e e e e e e e e e e e e e                      | 14-19 |

|          | Contents                                                           |

|----------|--------------------------------------------------------------------|

| 14.3.4.3 | Synchronous Single Read Using Dual Strobe Mode                     |

| 14.3.4.4 | Synchronous Single Read Using Single Strobe Mode                   |

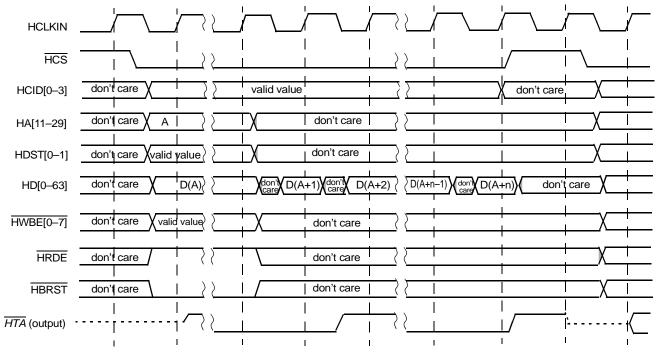

| 14.3.4.5 | Synchronous Burst Write Using Dual Strobe Mode                     |

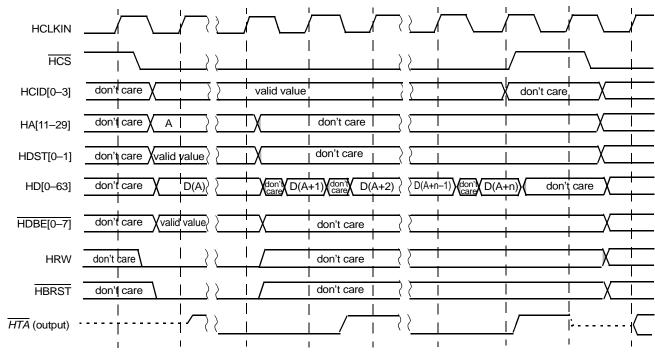

| 14.3.4.6 | Synchronous Burst Write Using Single Strobe Mode                   |

| 14.3.4.7 | Synchronous Burst Read Using Dual Strobe Mode                      |

| 14.3.4.8 | Synchronous Burst Read Using Single Strobe Mode                    |

| 14.3.5   | Broadcast Accesses                                                 |

| 14.4     | DSI Configuration                                                  |

| 14.4.1   | Stop Mode                                                          |

| 14.4.2   | DSI Reset During Host Access                                       |

| 14.5     | DSI Programming Model                                              |

| 14.5.1   | Control Registers                                                  |

| 14.5.2   | Status Registers                                                   |

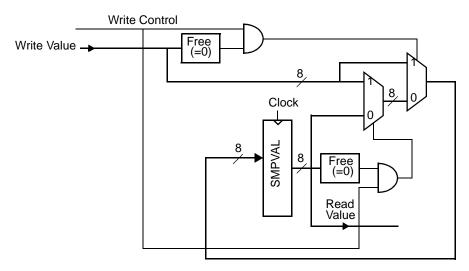

| 15       | Hardware Semaphores                                                |

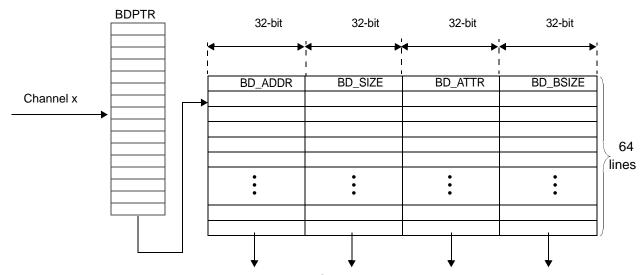

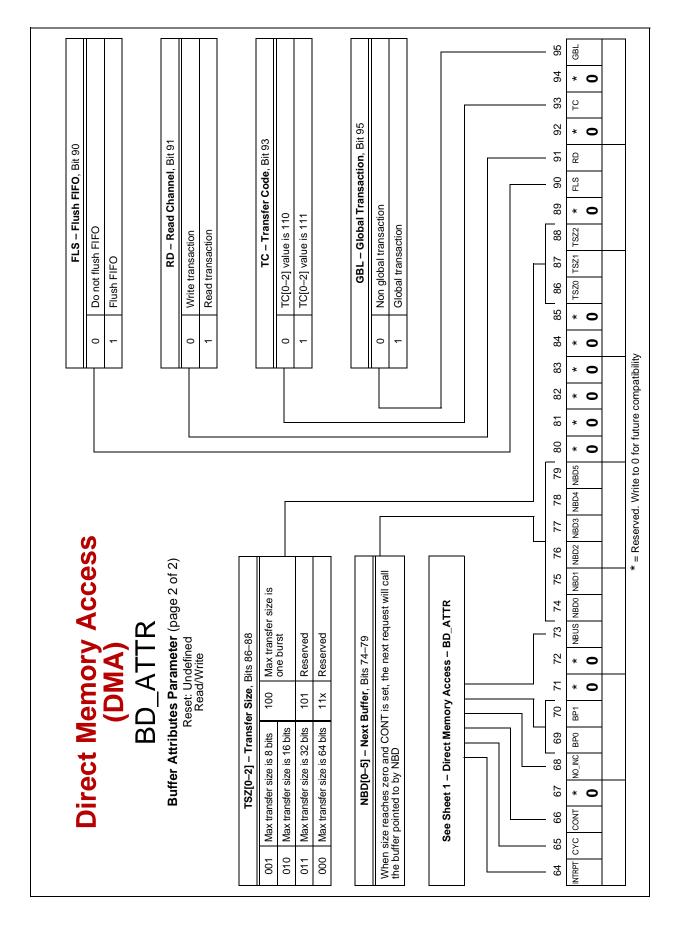

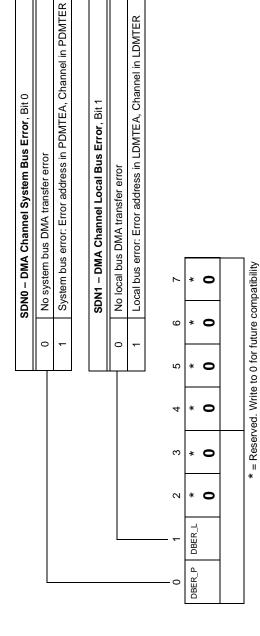

| 16       | Direct Memory Access (DMA) Controller                              |

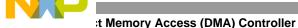

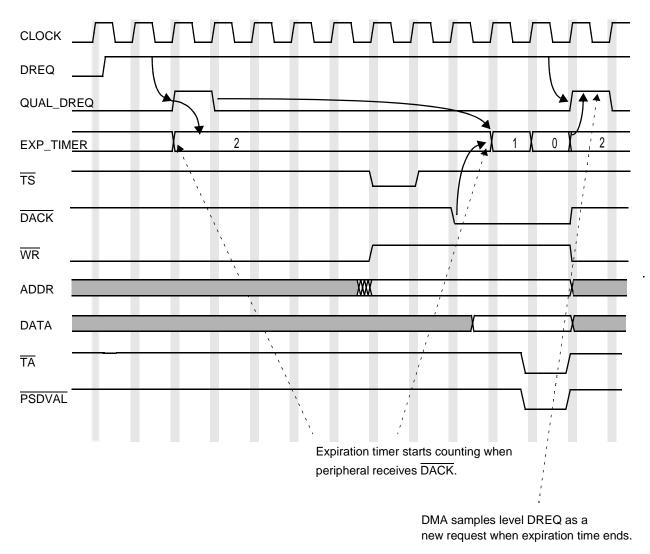

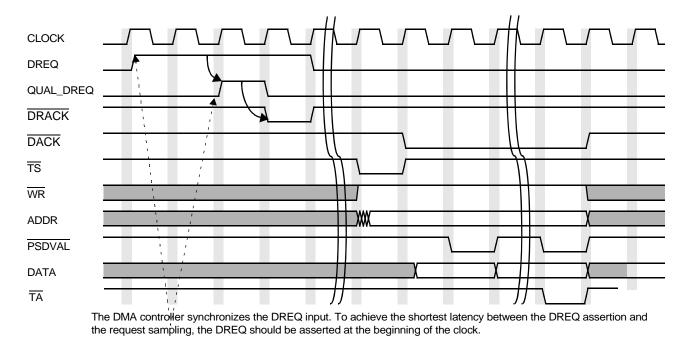

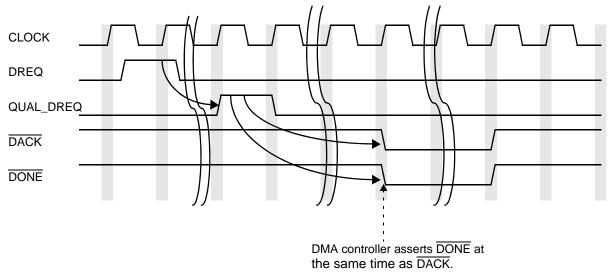

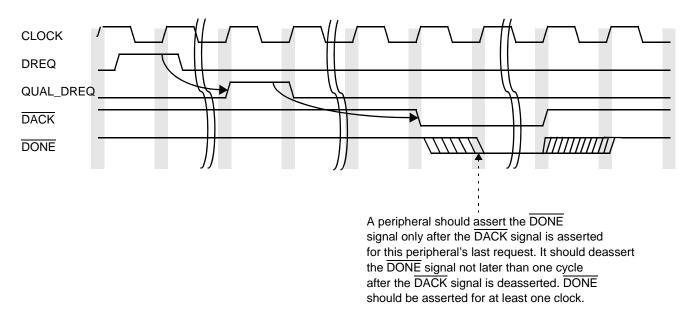

| 16.1     | DMA Signals: Requestor Interface                                   |

| 16.1.1   | Signal Functionality                                               |

| 16.1.2   | Peripheral Access Timing                                           |

| 16.1.2   | DMA Operating Modes: Transfer Types                                |

| 16.2.1   | DMA Transfer Size and Peripheral Port Size                         |

| 16.2.2   | DMA Access Modes                                                   |

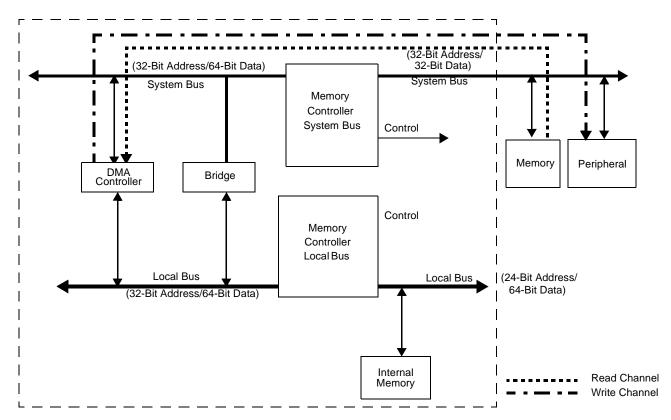

| 16.2.3   | Application Examples                                               |

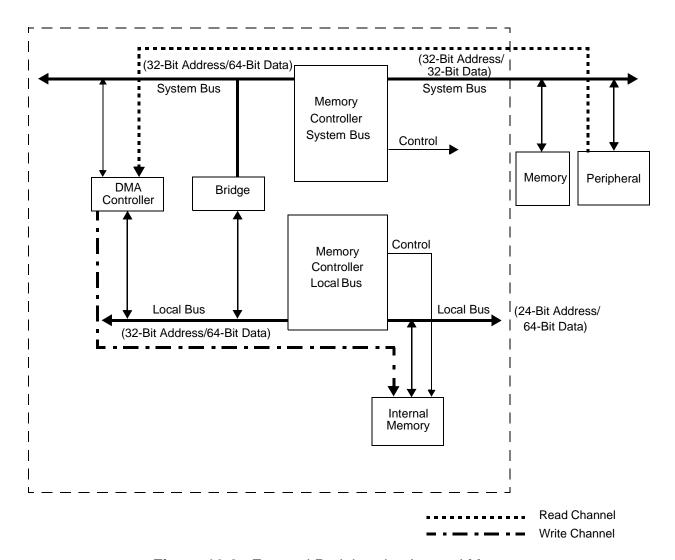

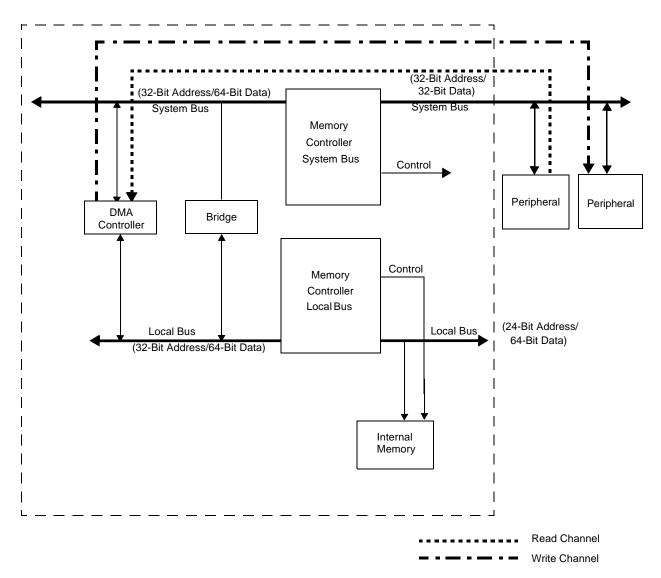

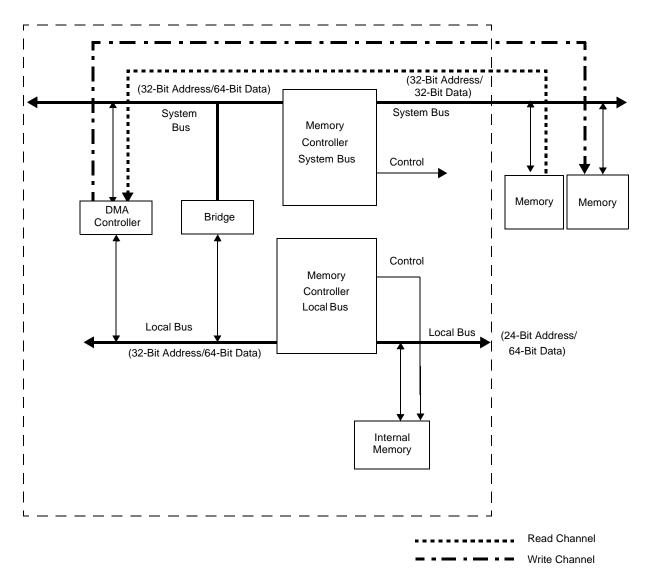

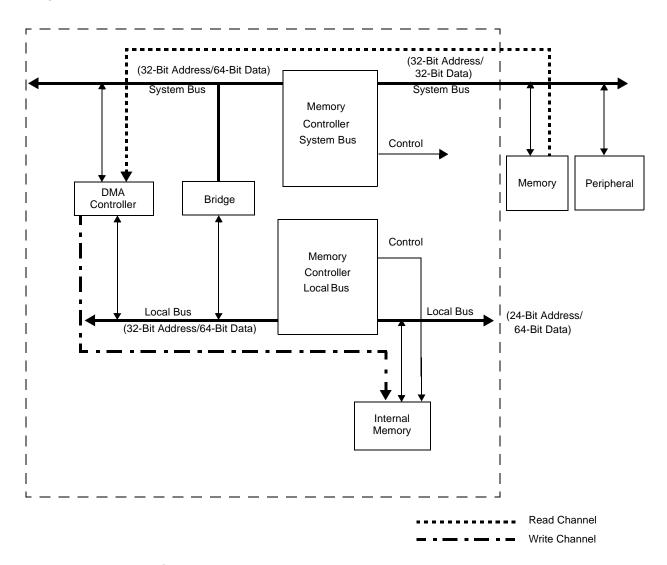

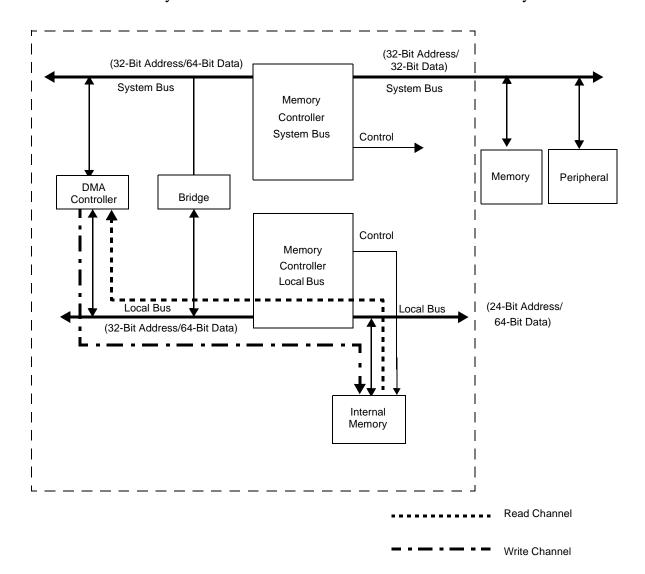

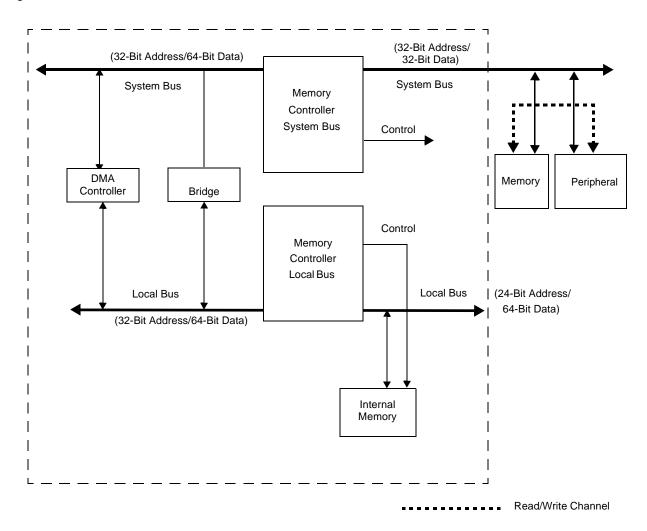

| 16.2.3.1 | External Memory and an External Peripheral on the System Bus 16-10 |

| 16.2.3.2 | External Peripheral to Internal Memory                             |

| 16.2.3.3 | External Peripheral to External Peripheral                         |

| 16.2.3.4 | External Memory and External Memory on the System Bus 16-13        |

| 16.2.3.5 | External Memory to Internal Memory on the System Bus 16-14         |

| 16.2.3.6 | Internal Memory to Internal Memory                                 |

| 16.2.3.7 | Flyby Transfer from External Peripheral to External Memory 16-16   |

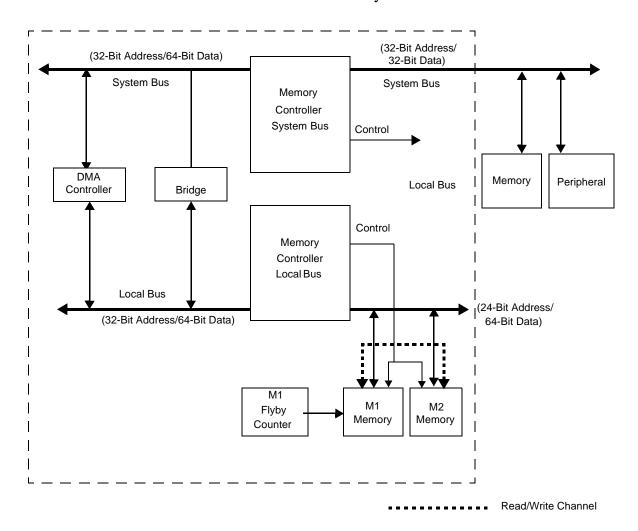

| 16.2.3.8 | Flyby Transfers Between Internal Memories, M2 and M1 16-17         |

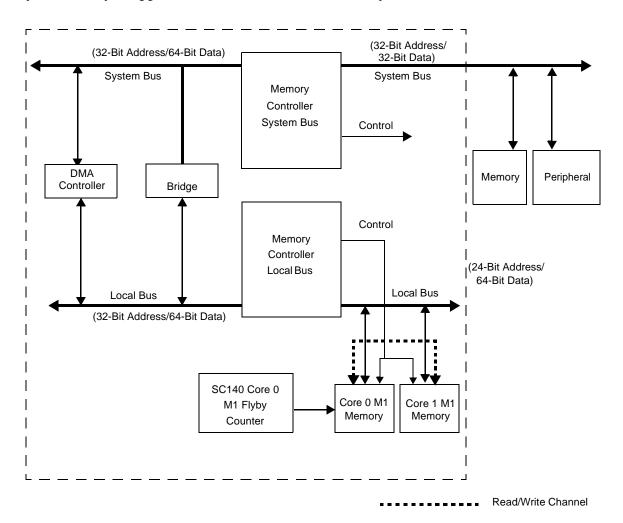

| 16.2.3.9 | Transfers Between Internal Memories M1 and M1 (Flyby Mode) 16-18   |

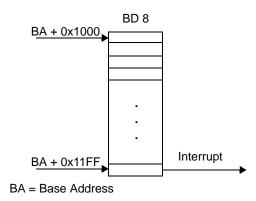

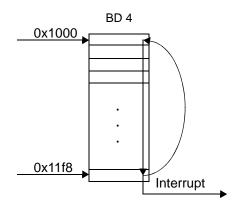

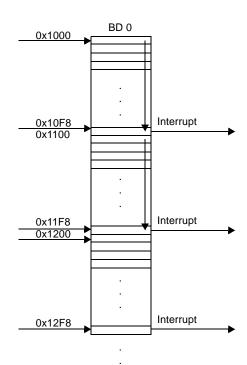

| 16.2.4   | DMA Operating Modes: Buffer Types                                  |

| 16.2.4.1 | Simple Buffer                                                      |

| 16.2.4.2 | Cyclic Buffer                                                      |

| 16.2.4.3 | Incremental Buffer                                                 |

| 16.2.4.4 | Chained Buffer                                                     |

| 16.2.4.5 | Complex Buffers—Dual Cyclic Buffers                                |

| 16.2.5   | 2D Data Transfers                                                  |

| 16.3     | DMA Transfer Programming                                           |

MSC8113 Reference Manual, Rev. 0

Freescale Semiconductor xiii

| ^ | n | • |

|---|---|---|

| 16.3.1    | DMA Priority Type                                 | 16-30 |

|-----------|---------------------------------------------------|-------|

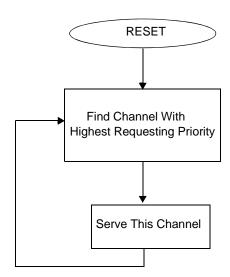

| 16.3.1.1  | Fixed-Priority Mode                               | 16-30 |

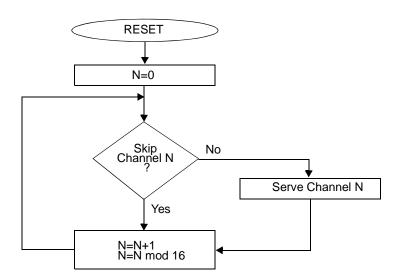

| 16.3.1.2  | Round-Robin Priority Mode                         | 16-30 |

| 16.3.1.3  | DMA Arbitration Device Level Considerations       |       |

| 16.3.2    | DMA Data Transfer Examples                        | 16-33 |

| 16.3.3    | Terminating a DMA Transfer                        |       |

| 16.4      | DMA Programming Model                             |       |

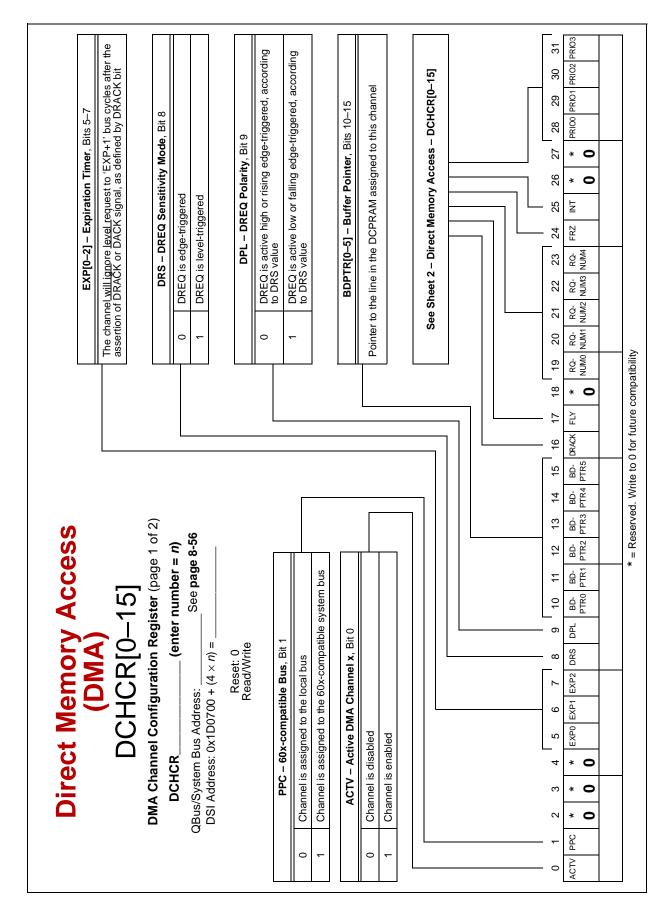

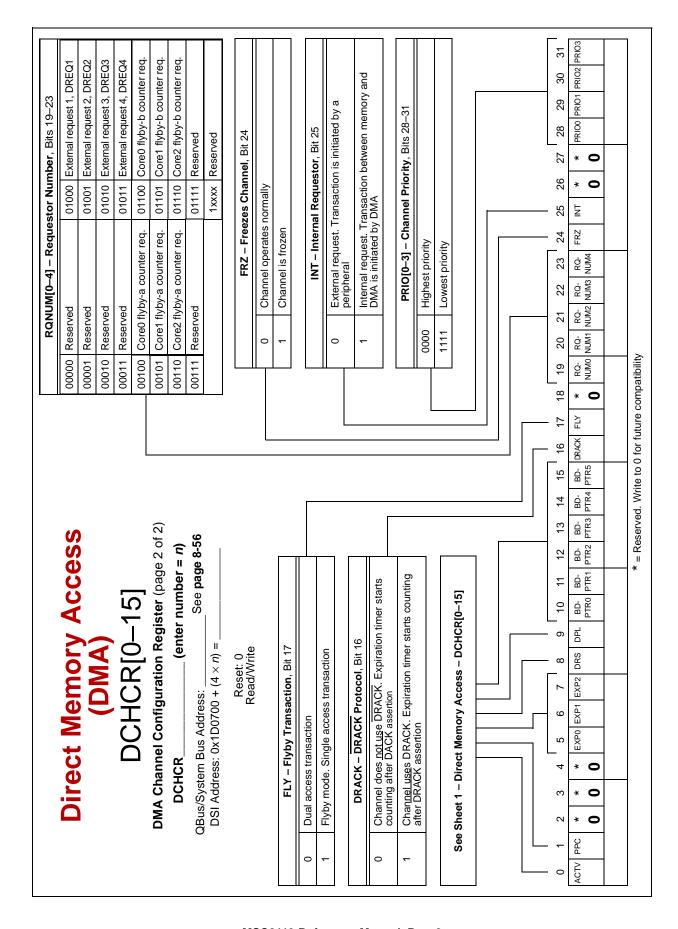

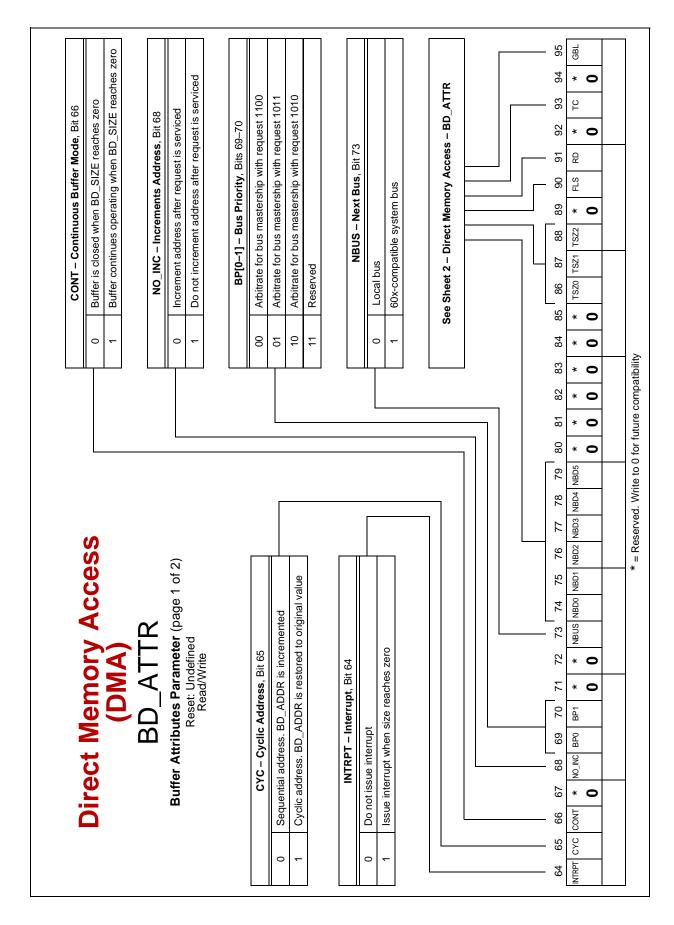

| 16.4.1    | Configuration Registers                           |       |

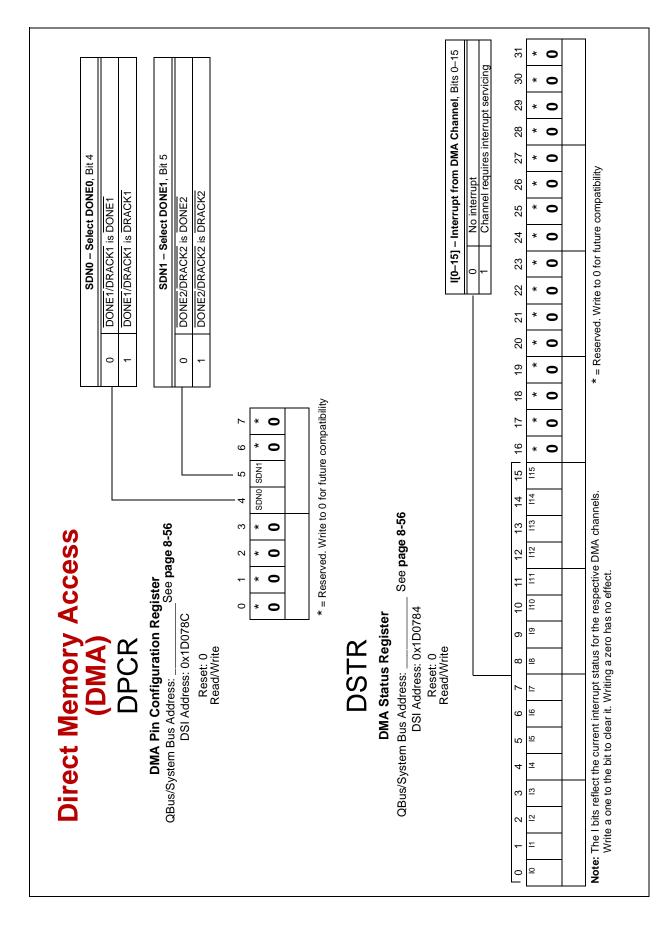

| 16.4.2    | DMA Status and Interrupt Registers                |       |

| 16.4.3    | Bus Error Registers                               |       |

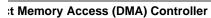

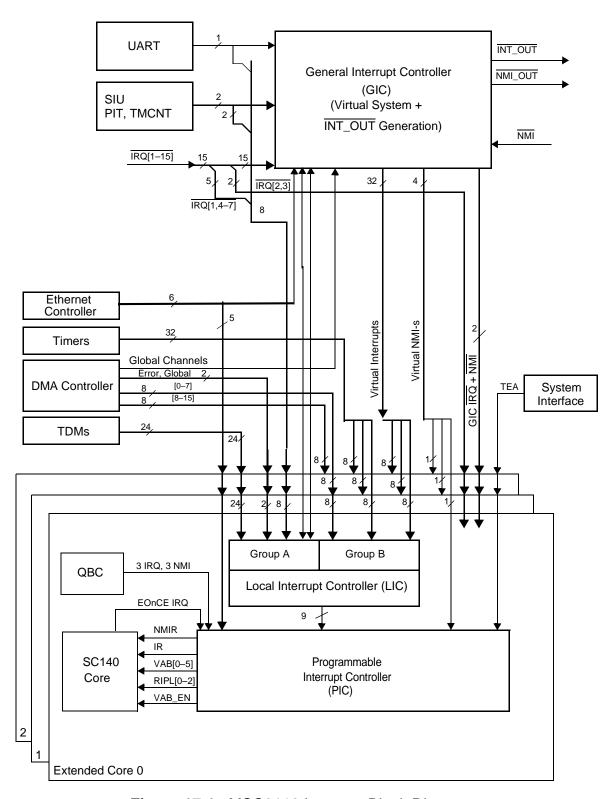

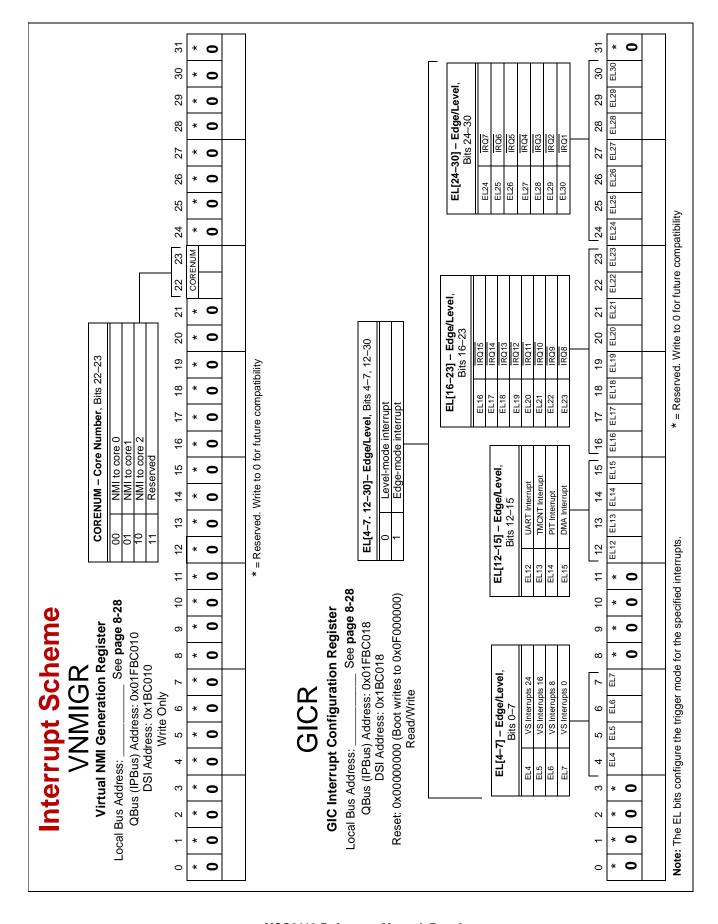

| <b>17</b> | Interrupt Processing                              |       |

| 17.1      | Architecture                                      | 17-4  |

| 17.1.1    | Global Interrupt Controller                       |       |

| 17.1.1.1  | INT_OUT Generation                                |       |

| 17.1.1.2  | NMI or NMI_OUT Generation                         |       |

| 17.1.1.3  | Virtual Interrupt Generation                      |       |

| 17.1.1.4  | Virtual NMI Generation                            |       |

| 17.1.1.5  | GIC Stop Mode                                     |       |

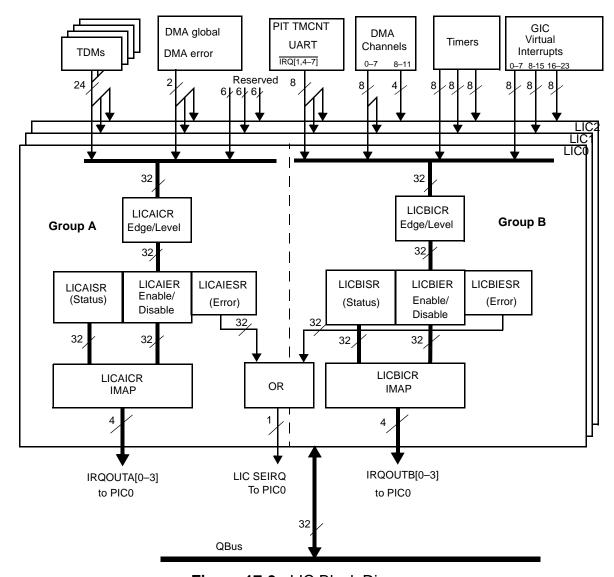

| 17.1.2    | Local Interrupt Controller (LIC)                  |       |

| 17.1.2.1  | Resolving LIC Interrupts by the SC140 Cores       |       |

| 17.1.2.2  | Level Interrupt Mode                              |       |

| 17.1.2.3  | Edge Interrupt Mode                               |       |

| 17.1.2.4  | DMA Interrupts                                    | 17-13 |

| 17.1.2.5  | LIC Interrupt Sources                             |       |

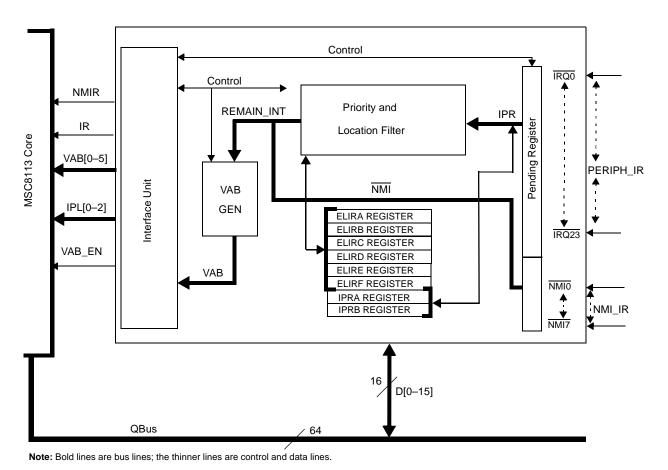

| 17.1.3    | Programmable Interrupt Controller (PIC)           |       |

| 17.1.4    | Peripheral Bus (QBus) Interface                   | 17-18 |

| 17.1.4.1  | Interrupt Request Generation                      | 17-18 |

| 17.1.5    | Interrupt Routing                                 |       |

| 17.2      | Interrupt Programming Examples                    | 17-21 |

| 17.2.1    | Initialization                                    | 17-21 |

| 17.2.2    | LIC and PIC Programming                           | 17-22 |

| 17.2.3    | Clearing Pending Requests                         | 17-23 |

| 17.3      | Interrupts Programming Model                      | 17-23 |

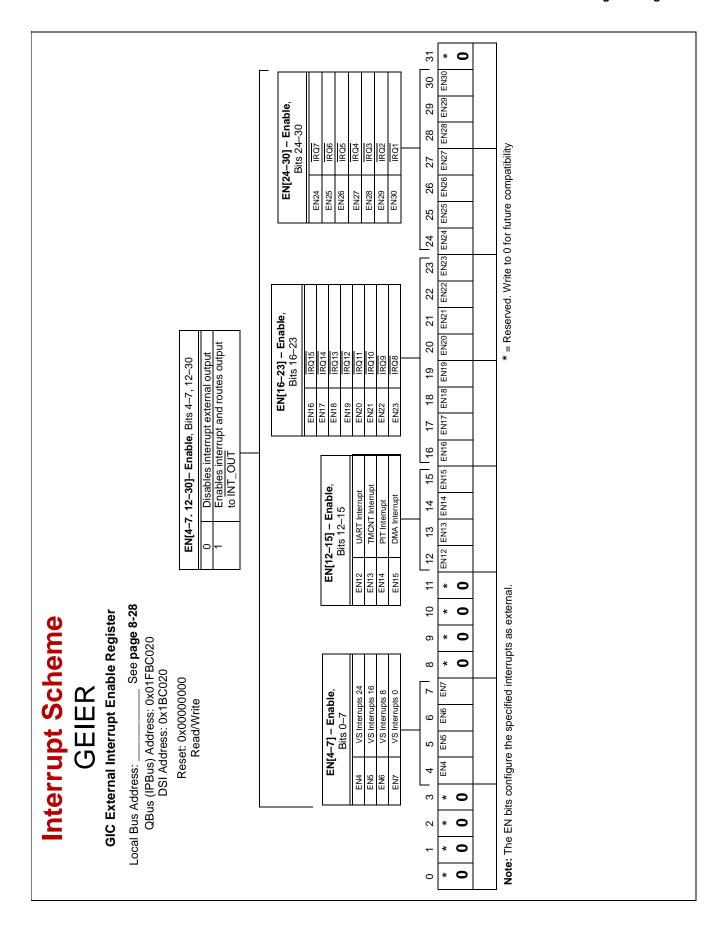

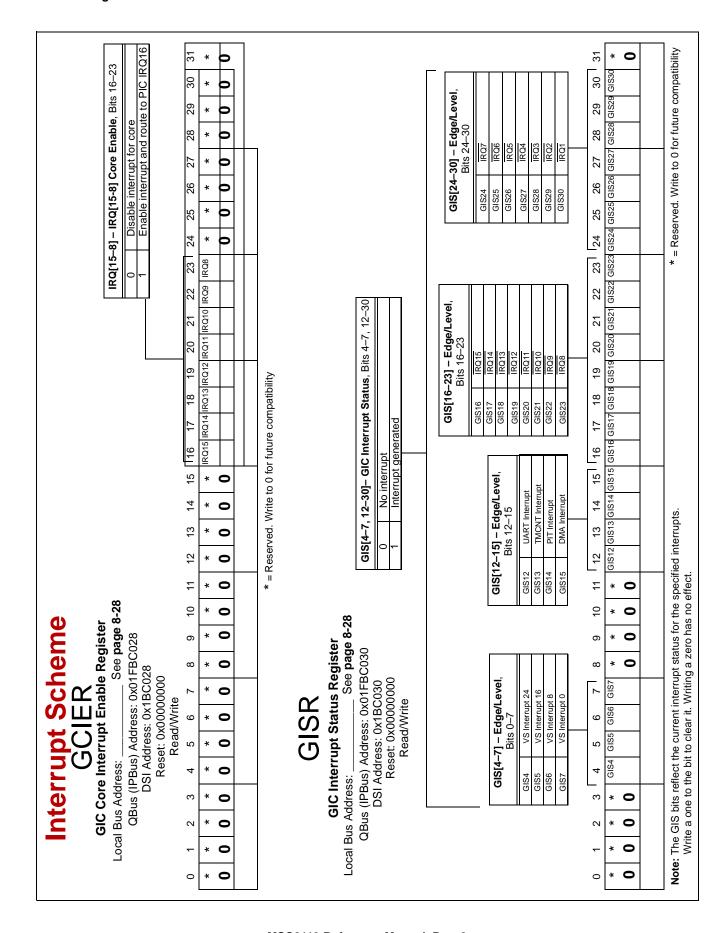

| 17.3.1    | GIC Programming Model                             | 17-23 |

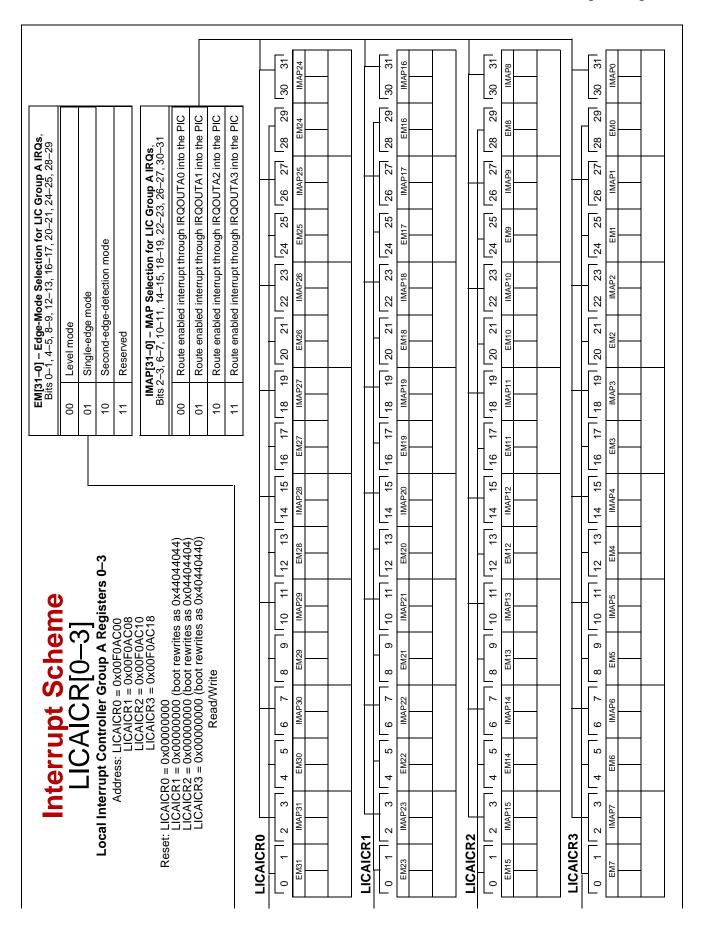

| 17.3.2    | LIC Programming Model                             | 17-29 |

| 17.3.2.1  | LIC Interrupt Configuration Registers             |       |

| 17.3.2.2  | LIC Interrupt Enable Registers                    |       |

| 17.3.2.3  | LIC Interrupt Status Registers                    | 17-38 |

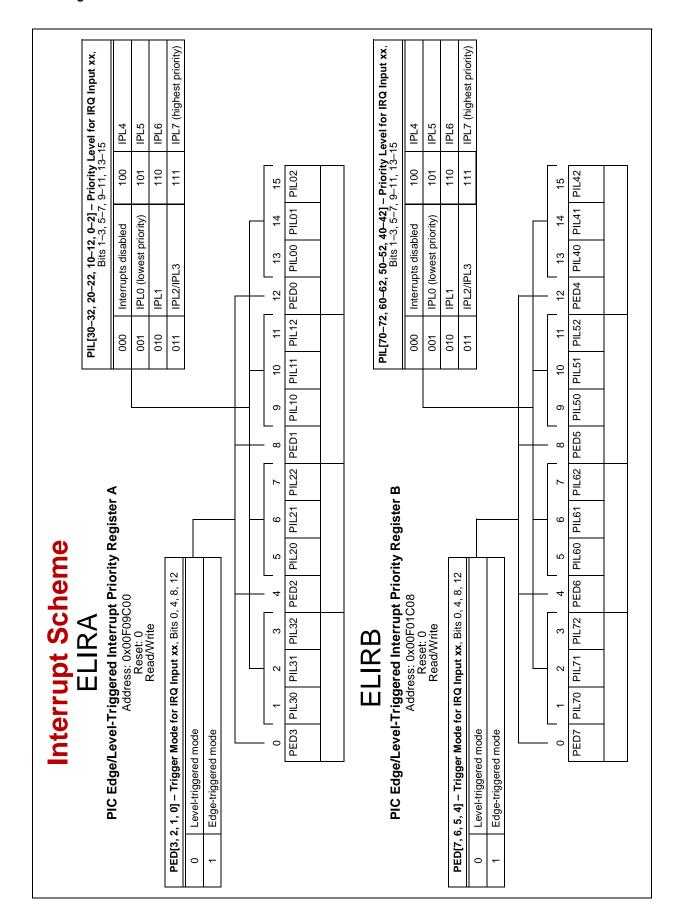

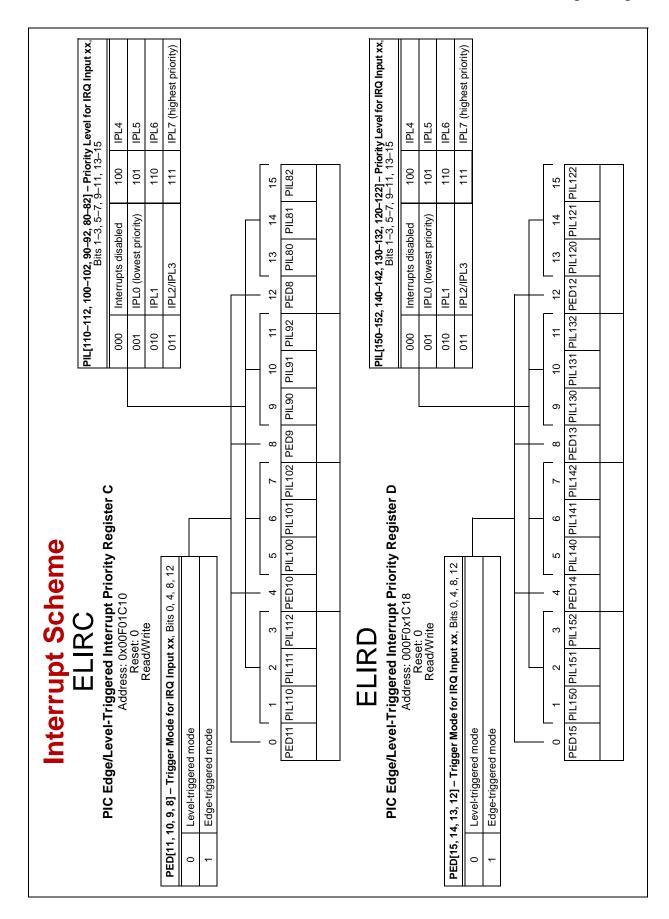

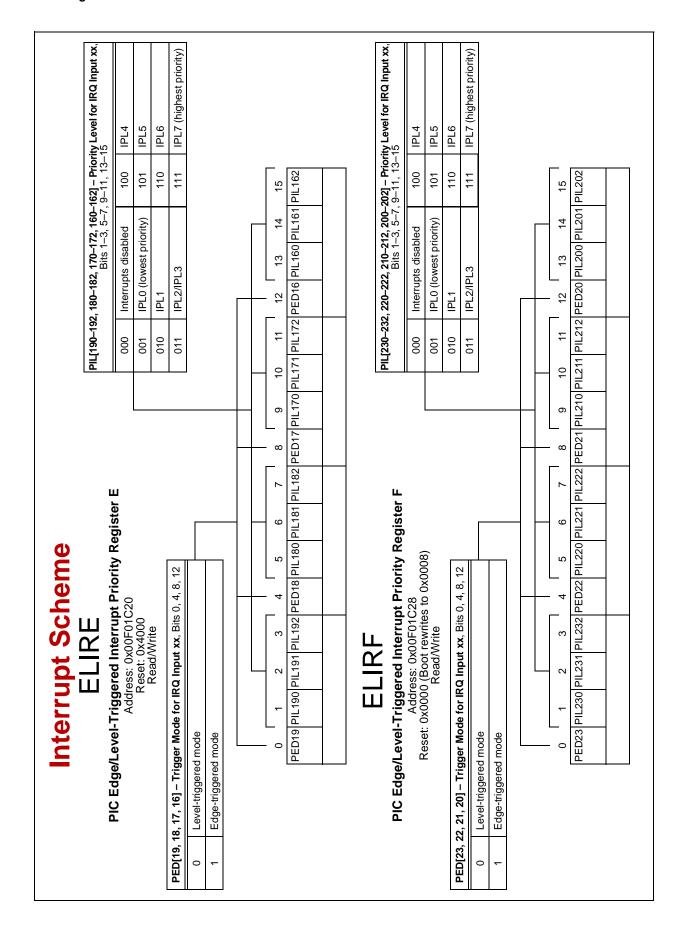

| 17.3.3    | PIC Registers                                     |       |

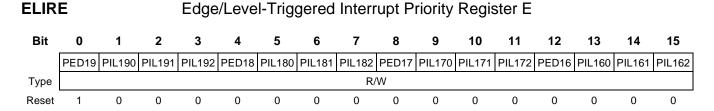

| 17331     | Edge/Level-Triggered Interrupt Priority Registers |       |

| 17.3.3.2 | Interrupt Priority Structure and Mode                        | 17-40 |

|----------|--------------------------------------------------------------|-------|

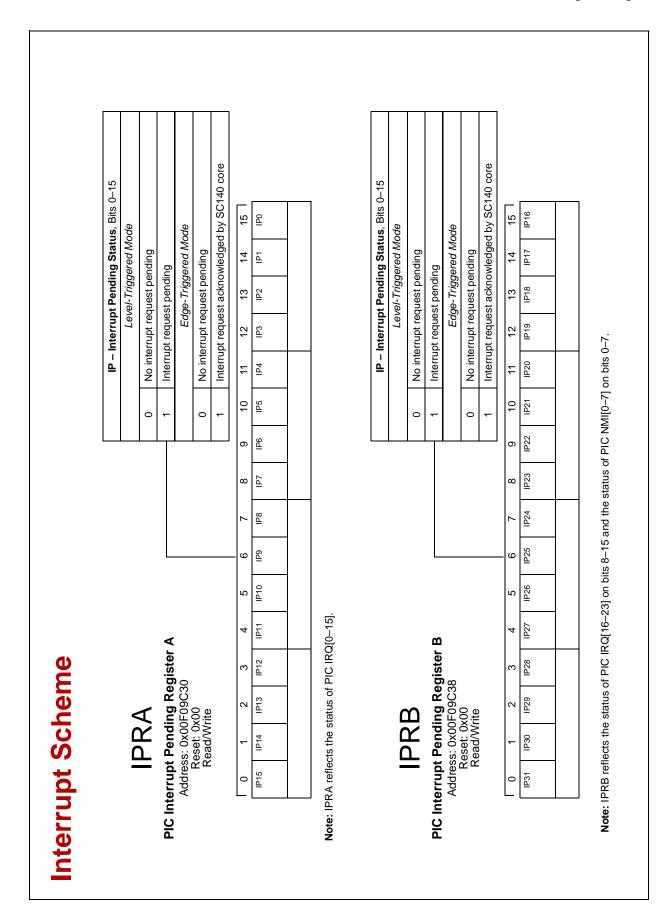

| 17.3.3.3 | Interrupt Pending Registers                                  |       |

|          |                                                              |       |

| 18       | Debugging                                                    |       |

| 18.1     | Overview                                                     | 18-2  |

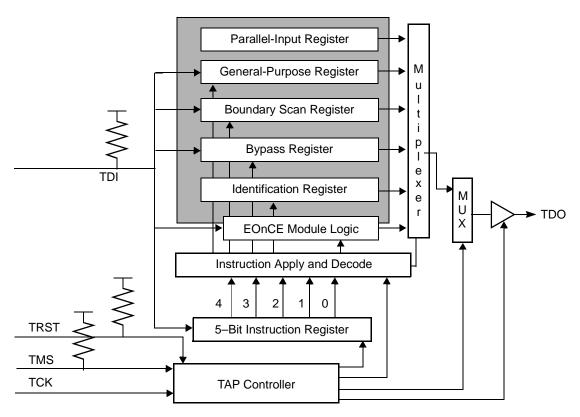

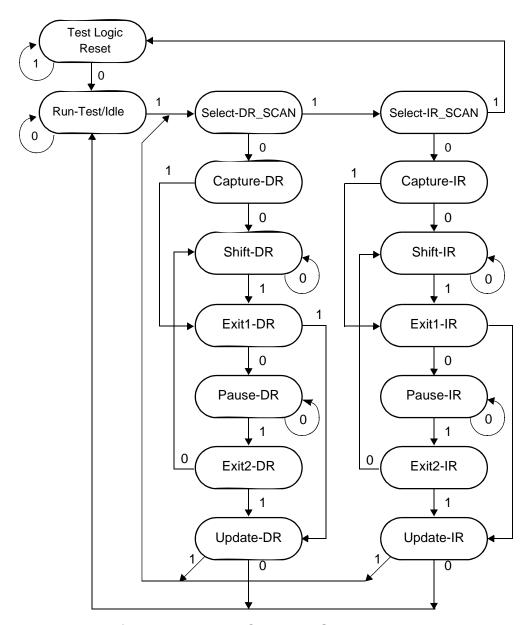

| 18.2     | TAP Controller                                               | 18-4  |

| 18.3     | Instruction Decoding                                         | 18-5  |

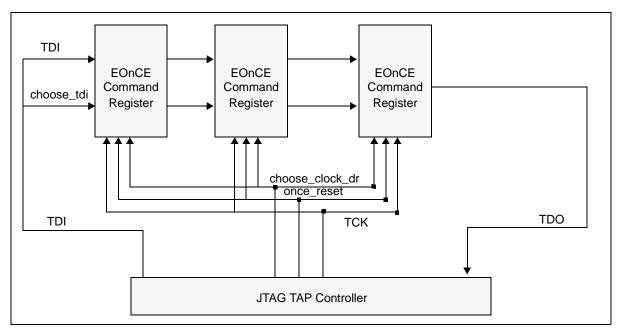

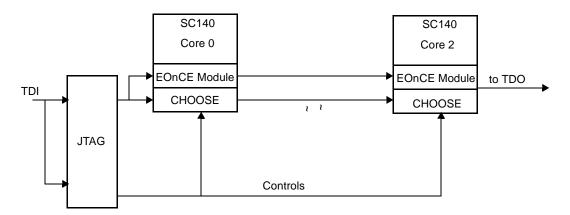

| 18.4     | Multi-Core JTAG and EOnCE Module Concept                     |       |

| 18.4.1   | Enabling the EOnCE Module                                    |       |

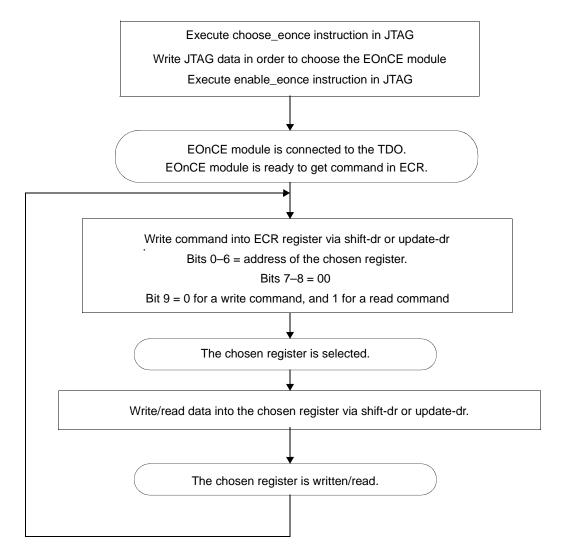

| 18.4.2   | DEBUG_REQUEST and ENABLE_EOnCE Commands                      |       |

| 18.4.3   | Reading/Writing EOnCE Registers Through JTAG                 |       |

| 18.5     | Signalling a Debug Request                                   |       |

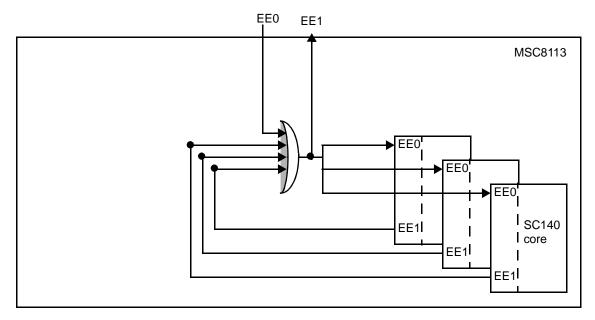

| 18.5.1   | EE_CTRL Modifications for the MSC8113                        |       |

| 18.5.2   | Event Selector Register Programming                          |       |

| 18.5.3   | EDCA1_CTRL Register Programming                              |       |

| 18.5.4   | Real-Time Debug Request                                      |       |

| 18.5.5   | Exiting Debug Mode                                           |       |

| 18.5.6   | Accessing EOnCE Registers Through JTAG in Real Time          |       |

| 18.5.7   | External Debug Exception Request                             |       |

| 18.5.8   | Generating a Debug Exception From an EDCA PC Detection Event |       |

| 18.6     | Tracing in the MSC8113                                       |       |

| 18.7     | General JTAG Mode Restrictions                               |       |

| 18.8     | JTAG and EOnCE Module Programming Model                      |       |

| 18.8.1   | Identification Register                                      |       |

| 18.8.2   | Boundary Scan Register (BSR)                                 |       |

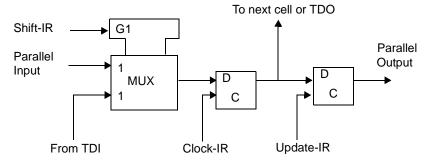

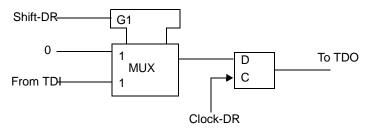

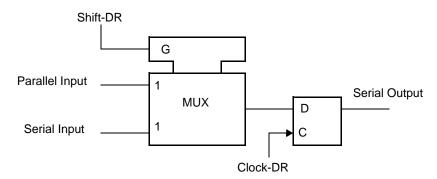

| 18.8.3   | Shift Registers                                              |       |

| 18.8.3.1 | Bypass Register                                              |       |

| 18.8.3.2 | Identification Register                                      |       |

| 18.8.3.3 | General-Purpose Register                                     |       |

| 18.8.3.4 | Parallel Input Register                                      |       |

| 40       |                                                              |       |

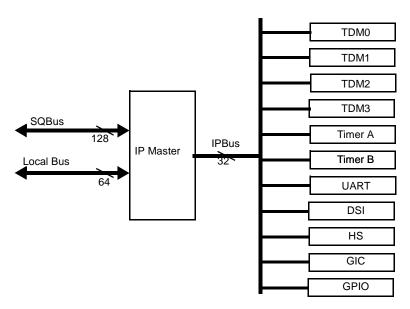

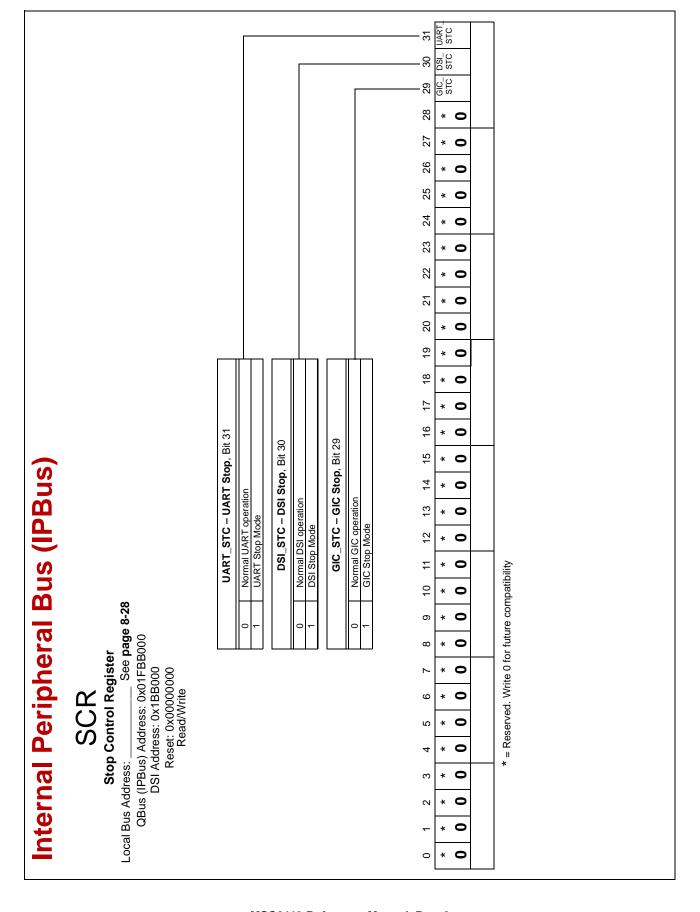

| 19       | Internal Peripheral Bus (IPBus)                              |       |

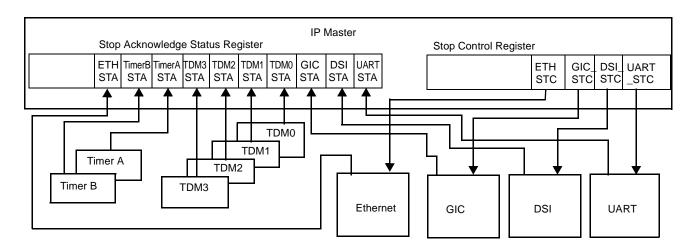

| 19.1     | TDM Interface                                                |       |

| 19.2     | UART                                                         |       |

| 19.3     | Timers                                                       | 19-2  |

| 19.4     | GPIOs                                                        |       |

| 19.5     | Hardware Semaphore Registers                                 |       |

| 19.6     | Global Interrupt Controller (GIC)                            | 19-2  |

| 19.7     | Direct Slave Interface (DSI)                                 |       |

| 19.8     | Ethernet Controller                                          | 19-3  |

| 19.9     | IPBus Functionality                                          | 19-4  |

Freescale Semiconductor xv

| $\sim$ | n | 4 | • |

|--------|---|---|---|

| 19.10    | Stop Options                                             | 19-4  |

|----------|----------------------------------------------------------|-------|

| 19.11    | IPBus Programming Model                                  | 19-5  |

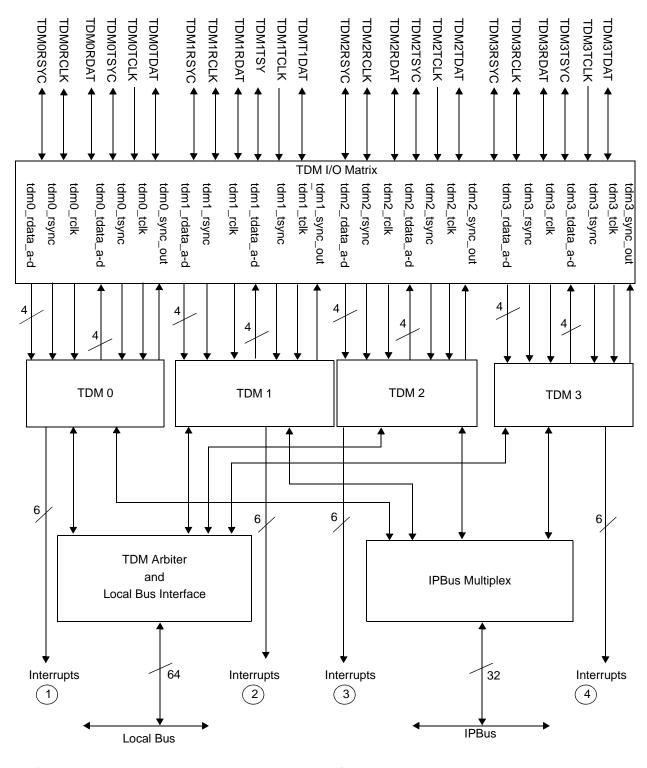

| 20       | TDM Interface                                            |       |

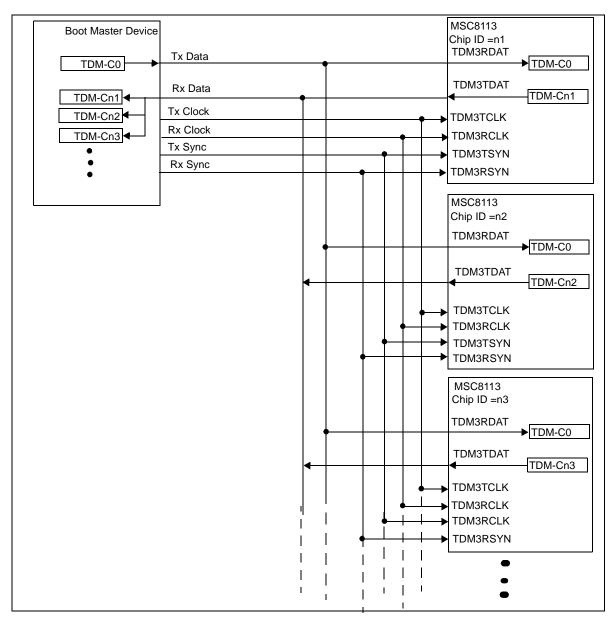

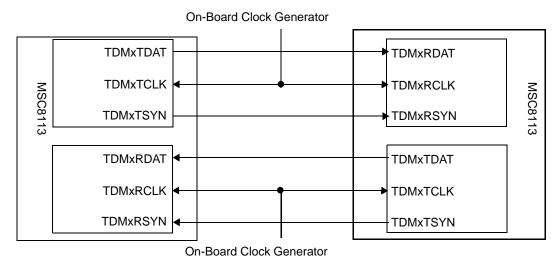

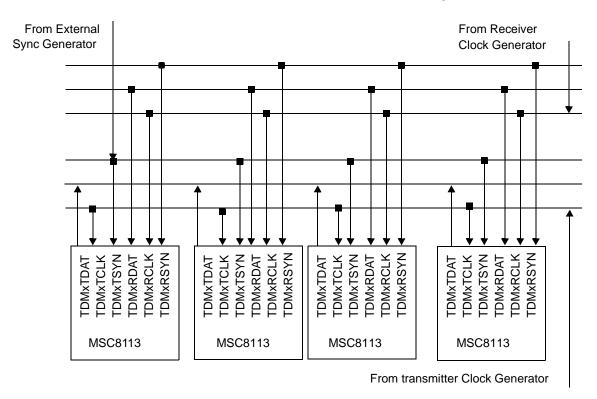

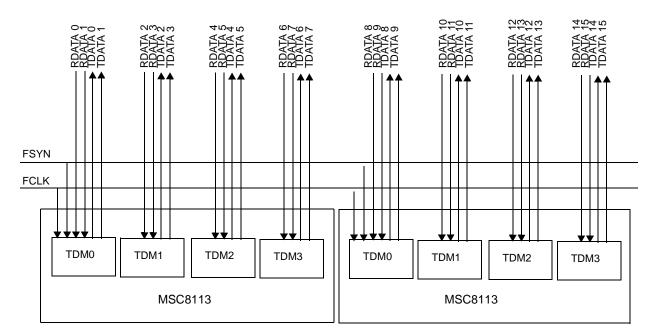

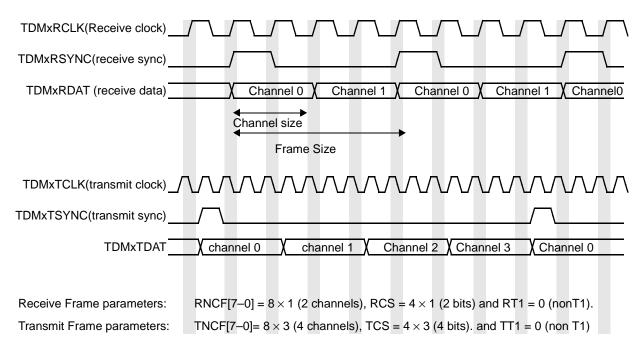

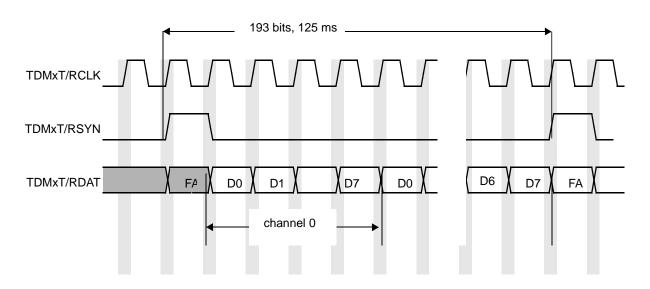

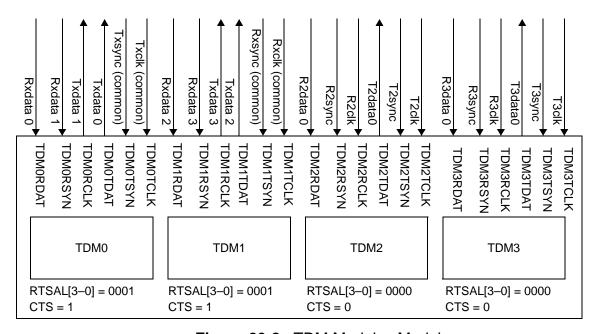

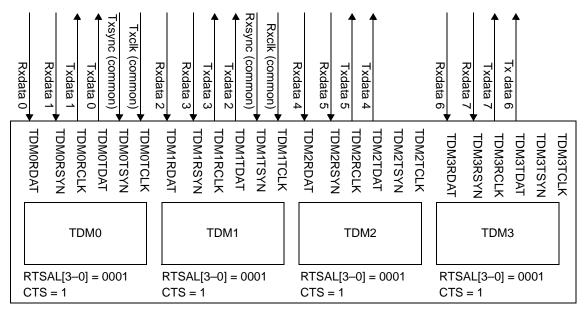

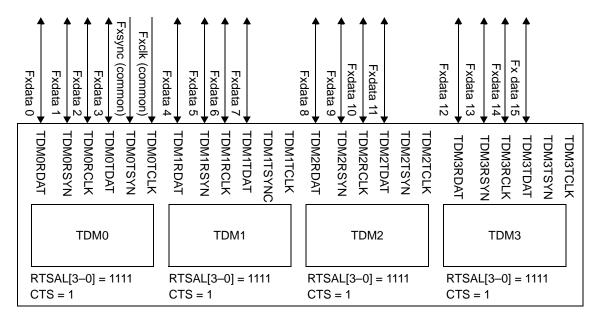

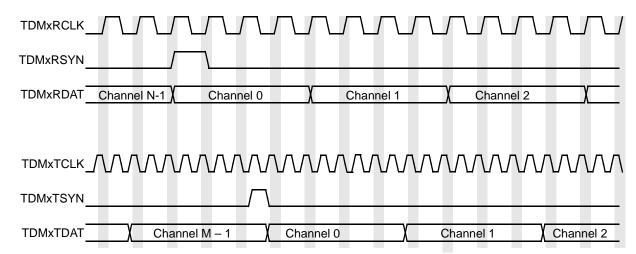

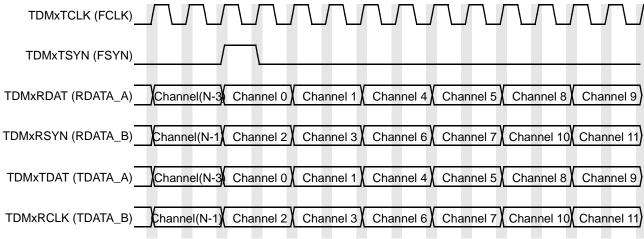

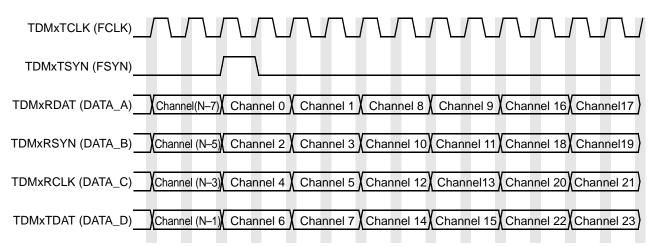

| 20.1     | Typical Configurations                                   | 20-5  |

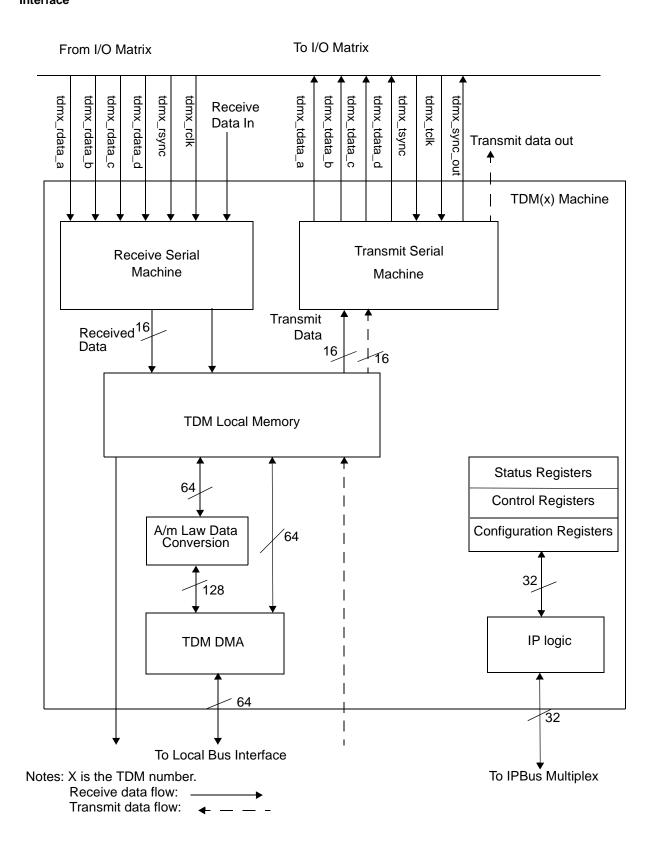

| 20.2     | TDM Basics                                               |       |

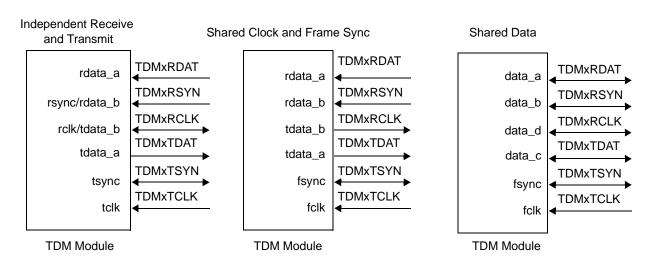

| 20.2.1   | Common Signals for the TDM Modules                       |       |

| 20.2.2   | Receiver and Transmitter Independent or Shared Operation |       |

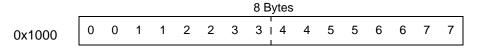

| 20.2.3   | TDM Data Structures                                      |       |

| 20.2.4   | Serial Interface                                         |       |

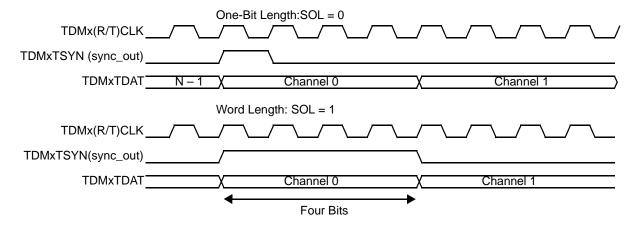

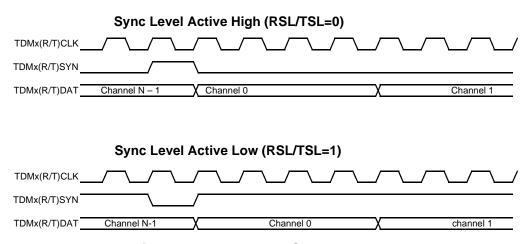

| 20.2.4.1 | Sync Out Configuration                                   |       |

| 20.2.4.2 | Sync In Configuration                                    |       |

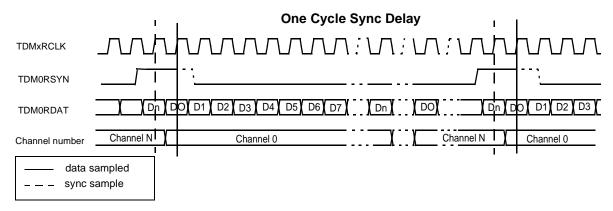

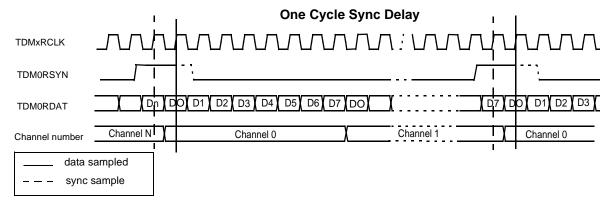

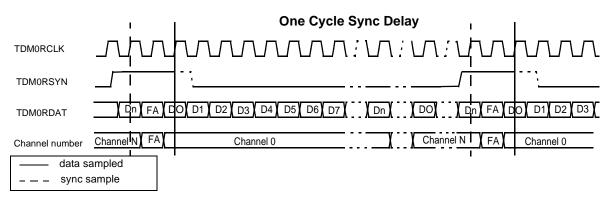

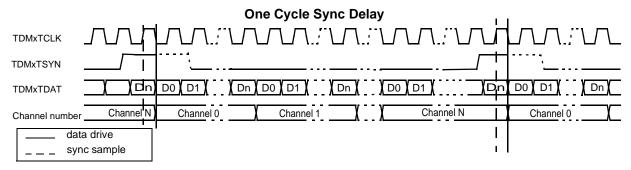

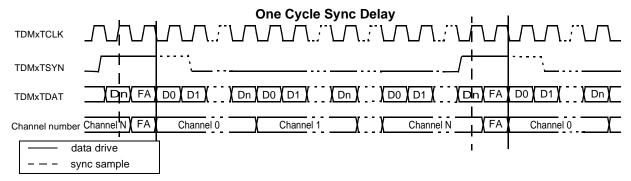

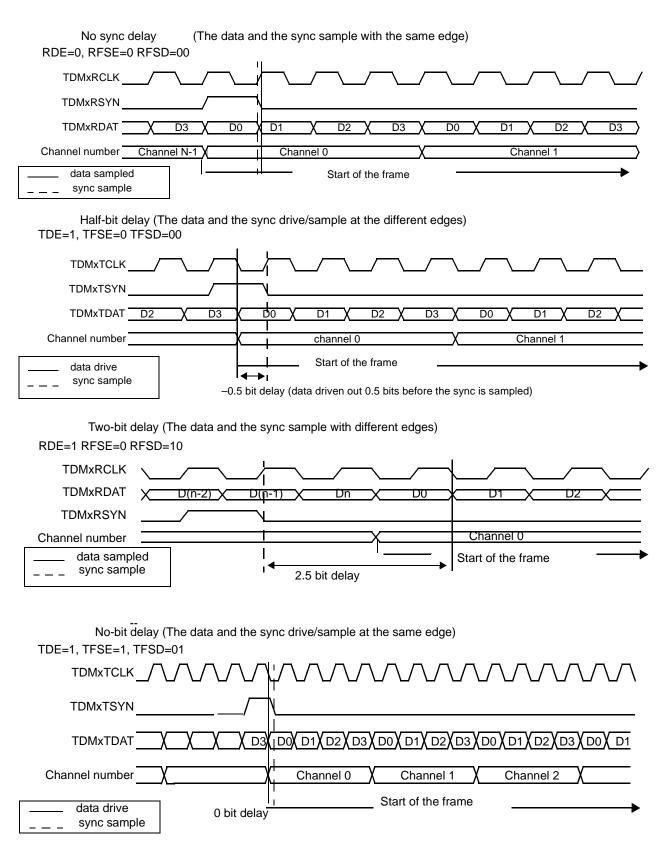

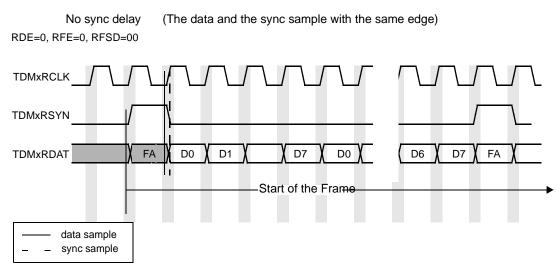

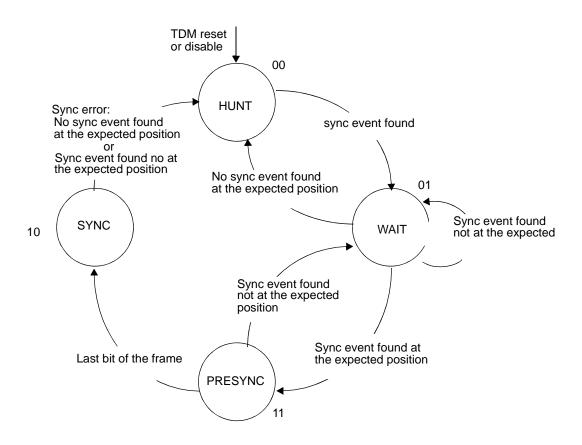

| 20.2.4.3 | Serial Interface Synchronization                         |       |

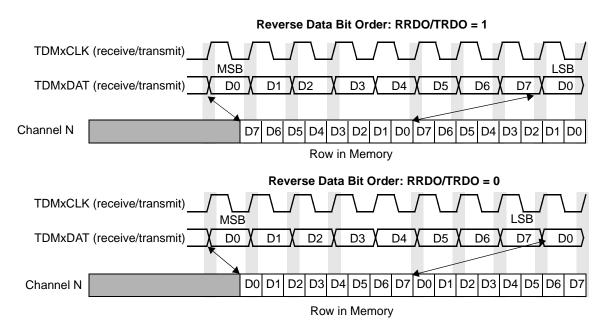

| 20.2.4.4 | Reverse Data Order                                       |       |

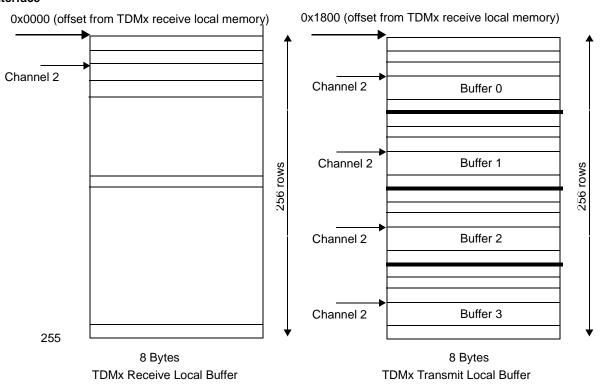

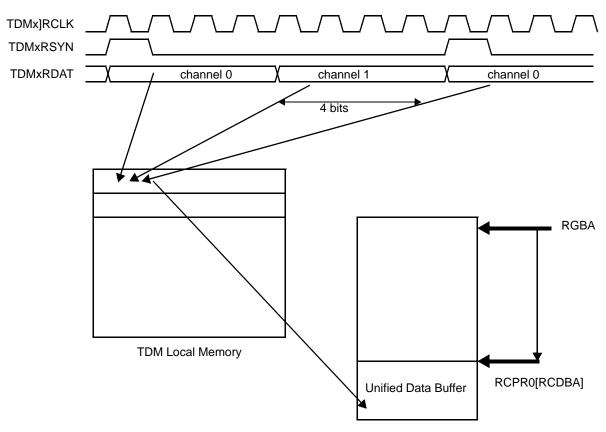

| 20.2.5   | TDM Local Memory                                         |       |

| 20.2.6   | Buffers Mapped on the Local Bus                          |       |

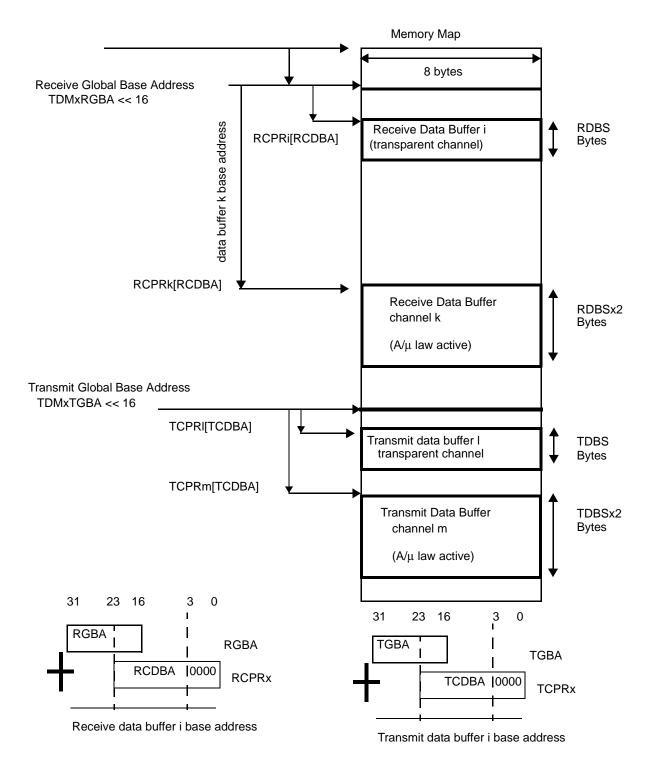

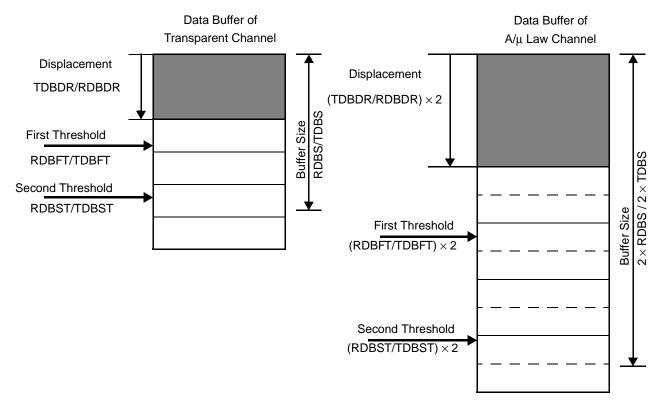

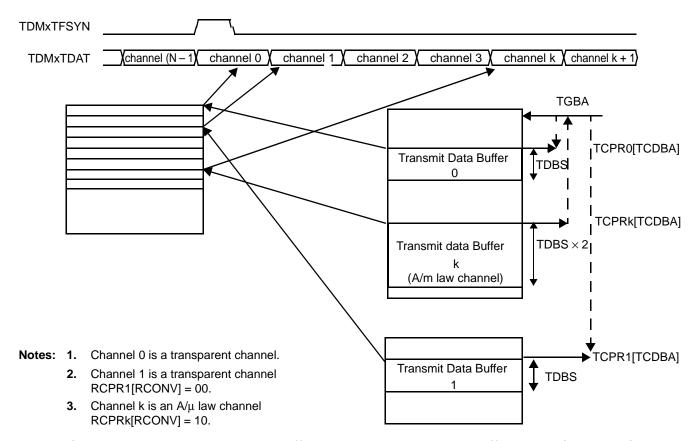

| 20.2.6.1 | Data Buffer Size and A/m-law Channels                    |       |

| 20.2.6.2 | Data Buffer Address                                      | 20-23 |

| 20.2.6.3 | Threshold Pointers and Interrupts                        |       |

| 20.2.6.4 | Unified Buffer Mode                                      |       |

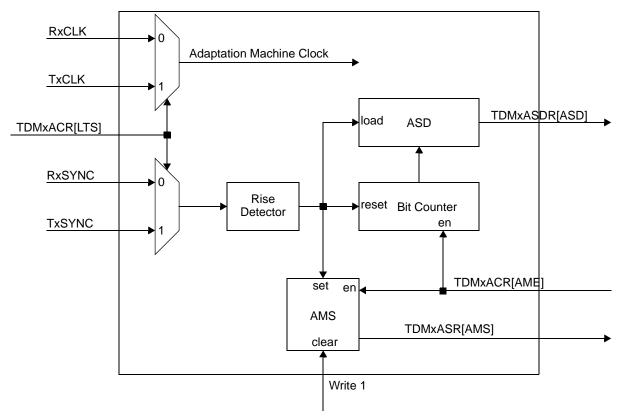

| 20.2.7   | Adaptation Machine                                       | 20-29 |

| 20.3     | TDM Power Saving                                         |       |

| 20.4     | Channel Activation                                       |       |

| 20.5     | Loopback Support                                         | 20-32 |

| 20.6     | TDM Initialization                                       |       |

| 20.7     | TDM Programming Model                                    | 20-34 |

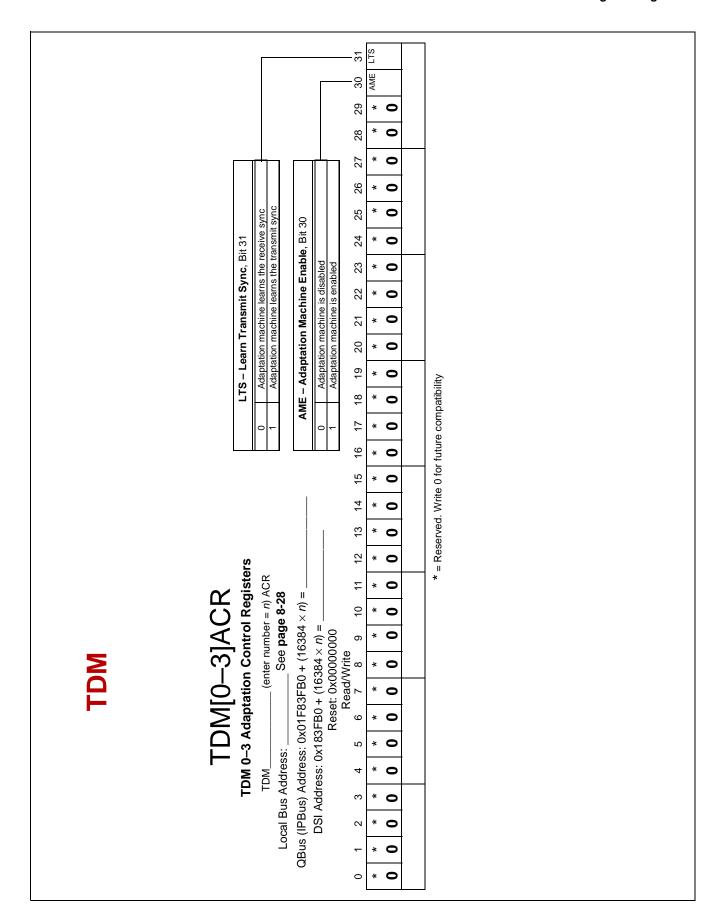

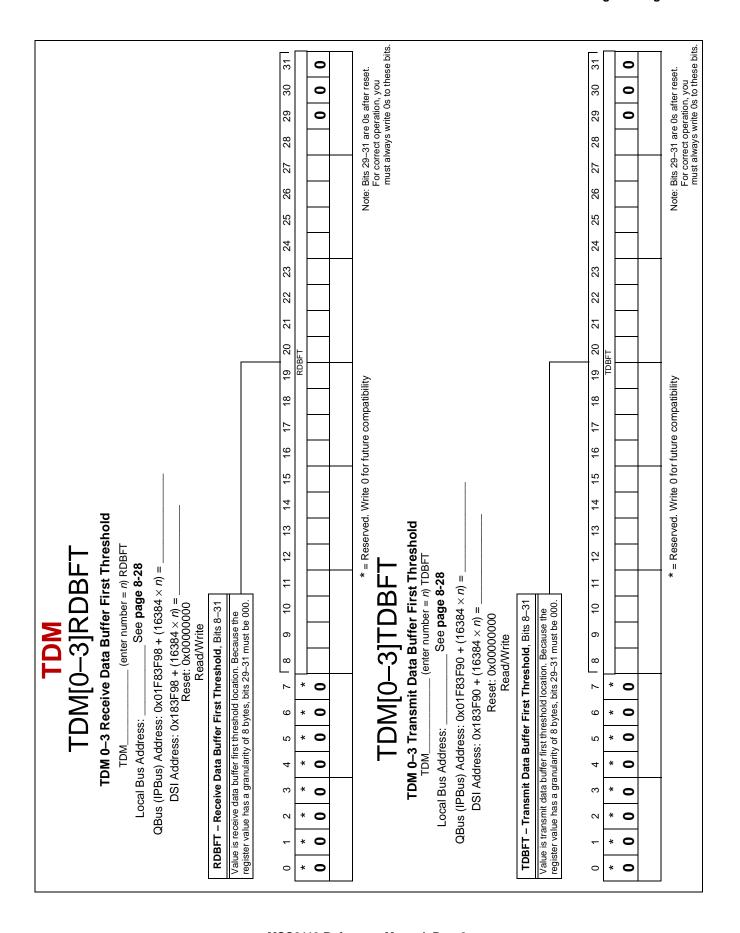

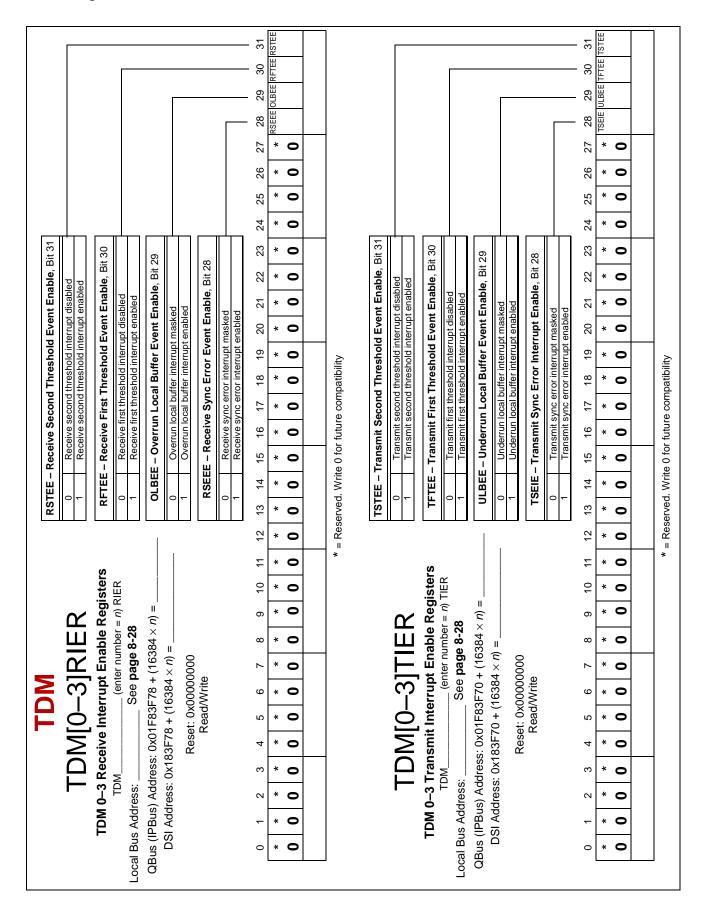

| 20.7.1   | Configuration Registers                                  |       |

| 20.7.2   | Control Registers                                        |       |

| 20.7.3   | Status Registers                                         |       |

| 20.7.4   | System Bus Registers                                     | 20-69 |

| 21       | UART                                                     |       |

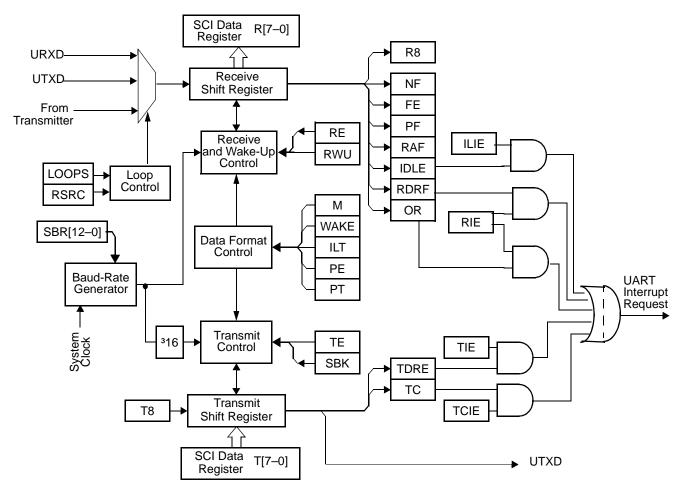

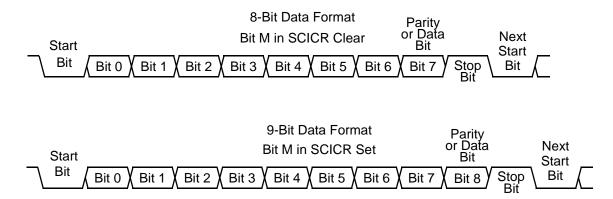

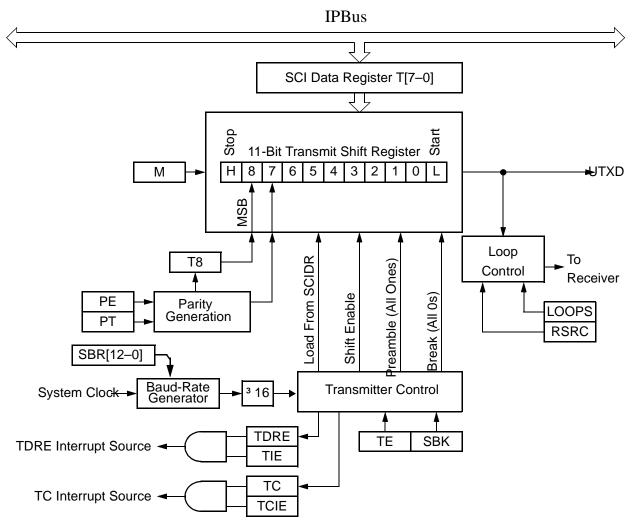

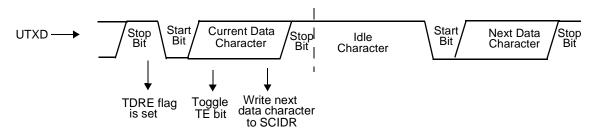

| 21.1     | Transmitter                                              | 21-6  |

| 21.1.1   | Character Transmission                                   |       |

| 21.1.2   | Break Characters                                         | 21-9  |

| 21.1.3   | Idle Characters                                          | 21-10 |

| 21.1.4   | Parity Bit Generation                                    |       |

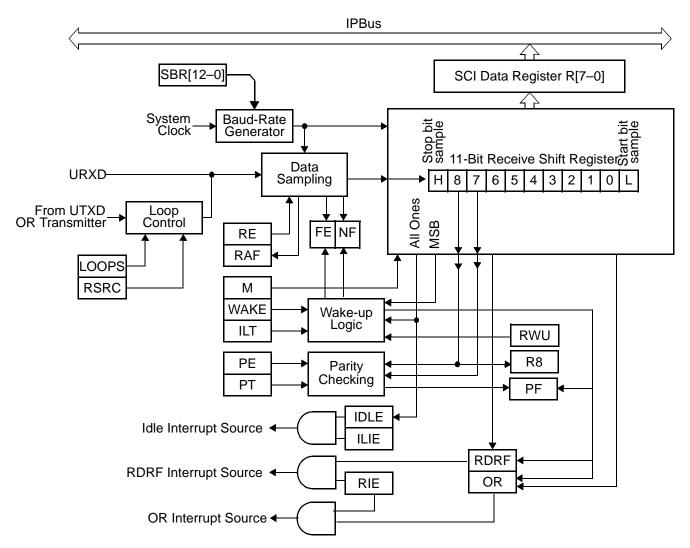

| 21.2     | Receiver                                                 |       |

| 21.2.1   | Character Reception                                      |       |

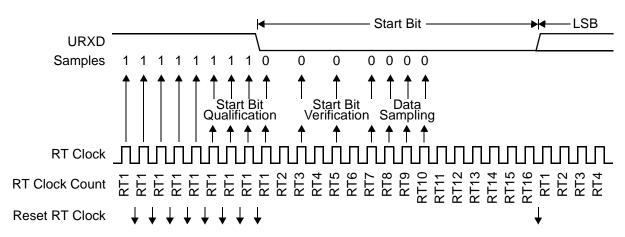

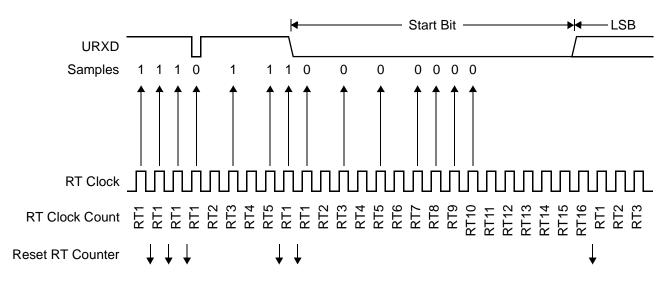

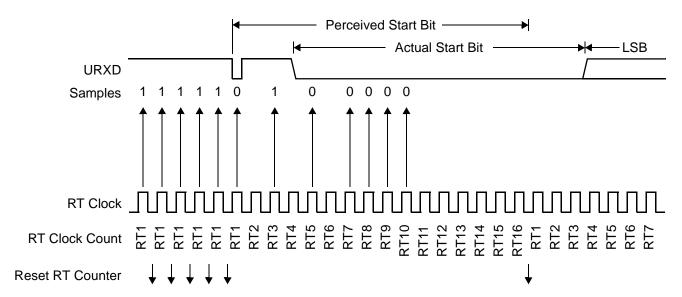

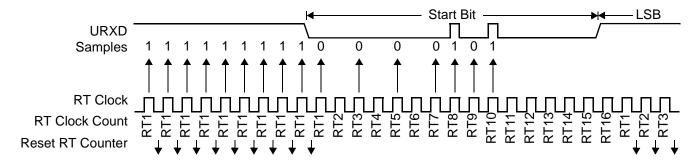

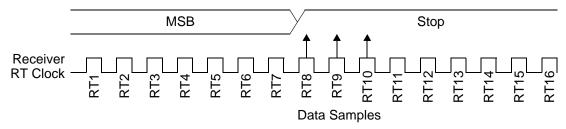

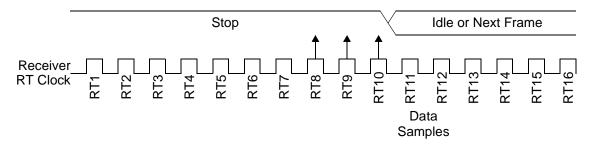

| 21.2.2   | Data Sampling                                            |       |

| 21.2.3   | Framing Error                                            |       |

| 21.2.4       | Parity Error                              | 21-18 |

|--------------|-------------------------------------------|-------|

| 21.2.5       | Break Characters                          | 21-18 |

| 21.2.6       | Baud-Rate Tolerance                       | 21-18 |

| 21.2.6.1     | Slow Data Tolerance                       | 21-19 |

| 21.2.6.2     | Fast Data Tolerance                       | 21-20 |

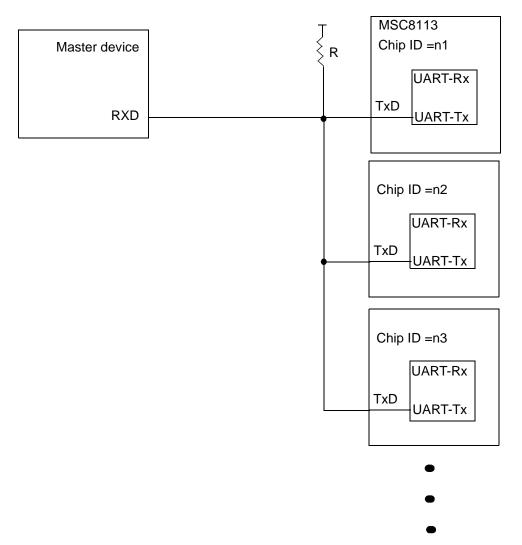

| 21.2.7       | Receiver Wake-Up                          |       |

| 21.2.7.1     | Idle Input Line Wake-Up (WAKE = 0)        | 21-21 |

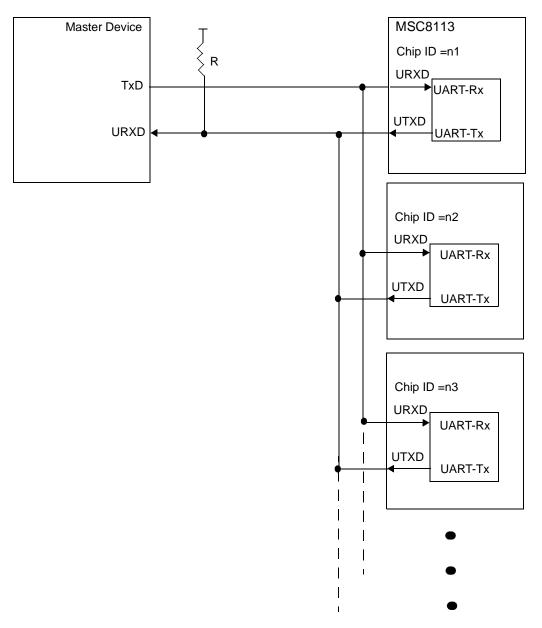

| 21.2.7.2     | Address Mark Wake-Up (WAKE = 1)           | 21-21 |

| 21.3         | Reset Initialization                      | 21-21 |

| 21.4         | Modes of Operation                        | 21-22 |

| 21.4.1       | Run Mode                                  | 21-22 |

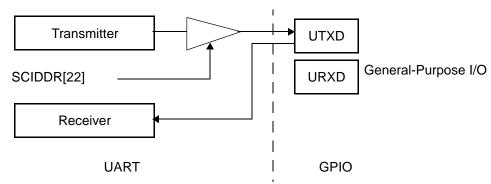

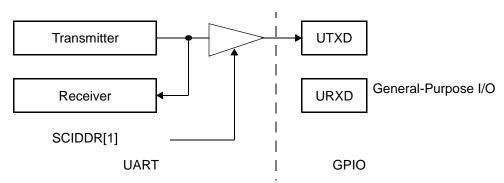

| 21.4.2       | Single-Wire Operation                     | 21-22 |

| 21.4.3       | Loop Operation                            | 21-23 |

| 21.4.4       | Stop Mode                                 | 21-23 |

| 21.4.5       | Receiver Standby Mode                     | 21-23 |

| 21.5         | Interrupt Operation                       | 21-24 |

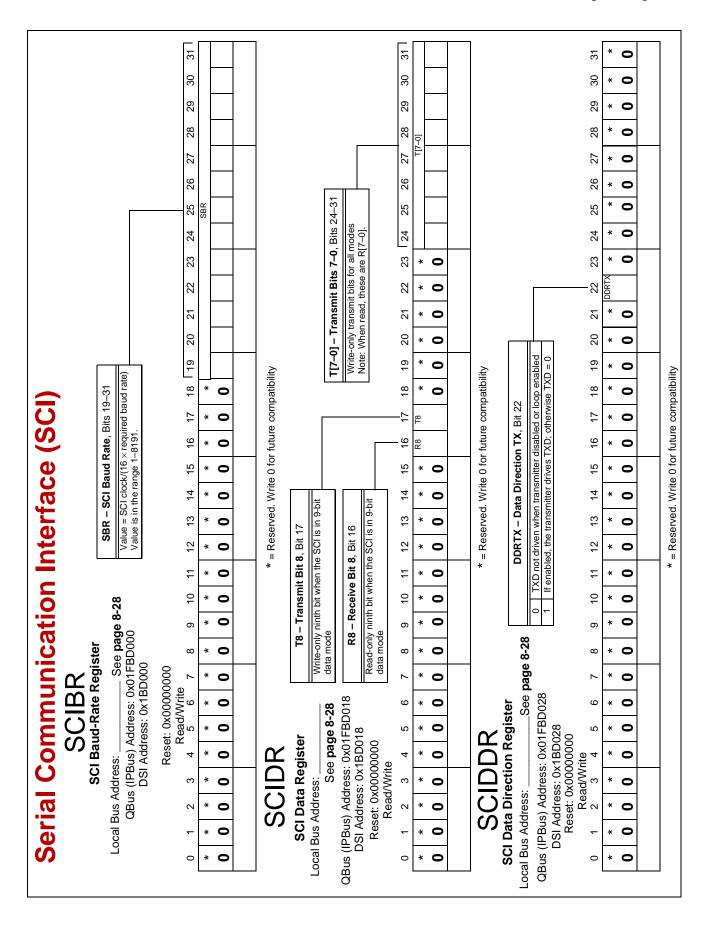

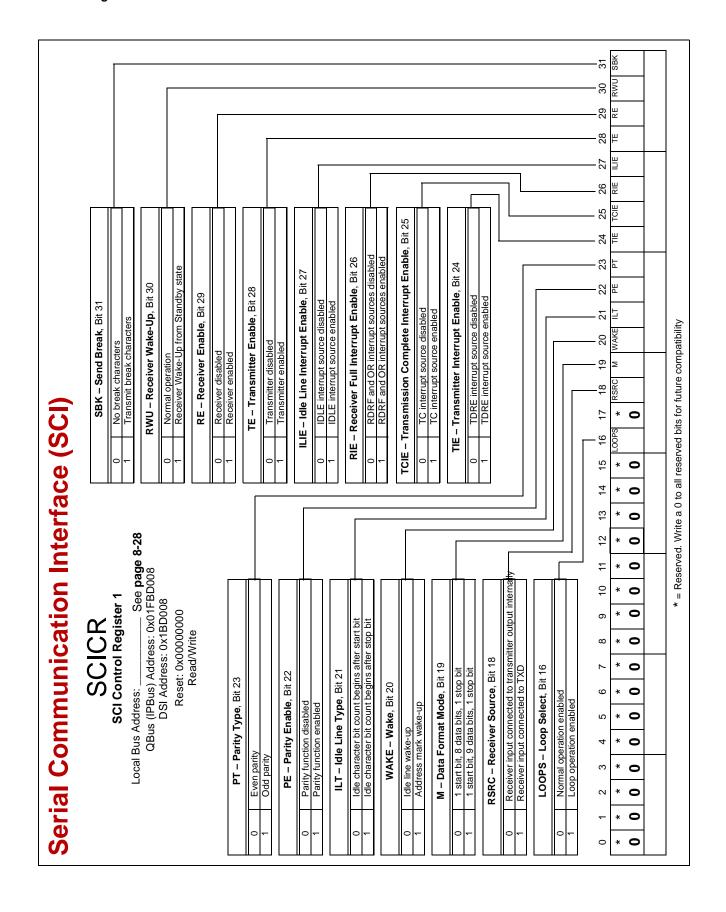

| 21.6         | UART Programming Model                    | 21-24 |

| 22           | Timers                                    |       |

| 22.1         |                                           | 22.0  |

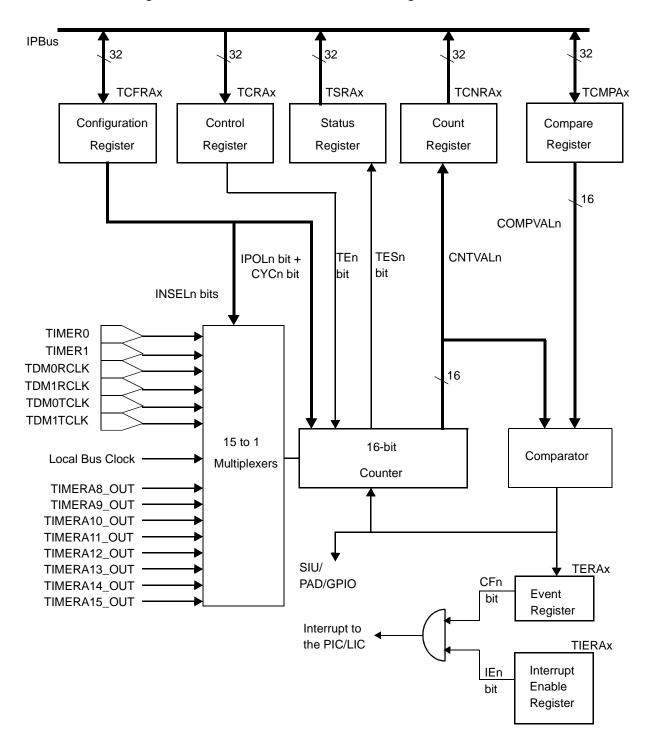

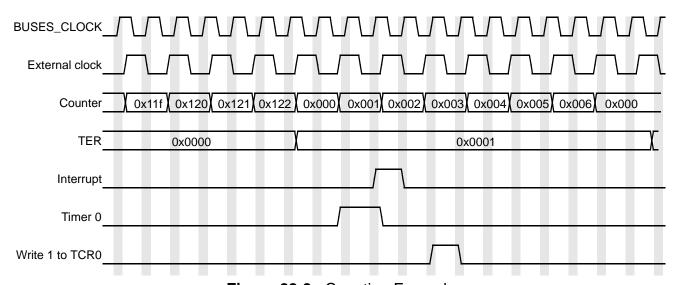

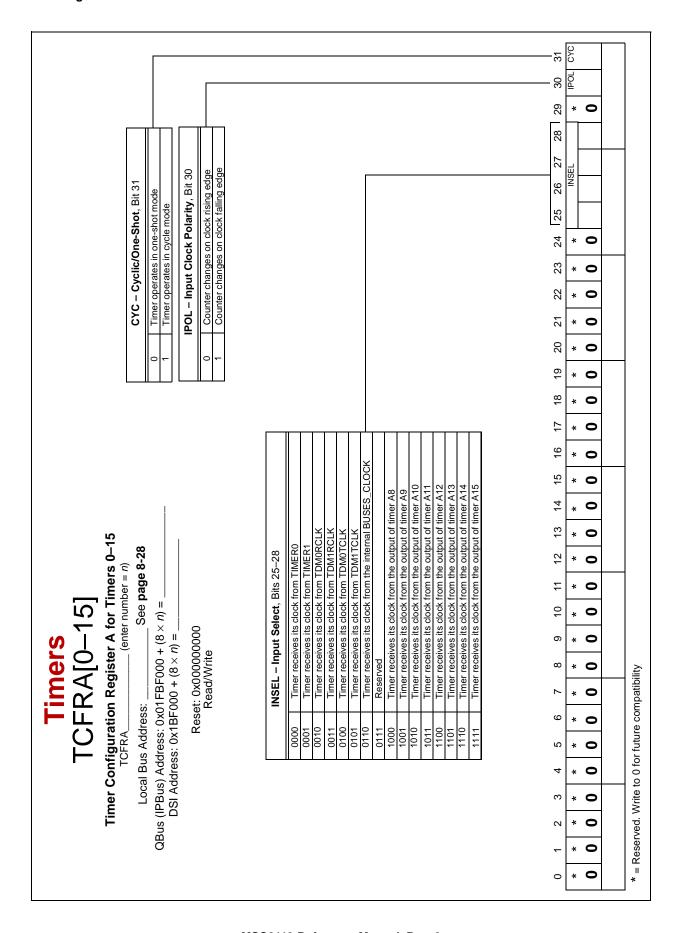

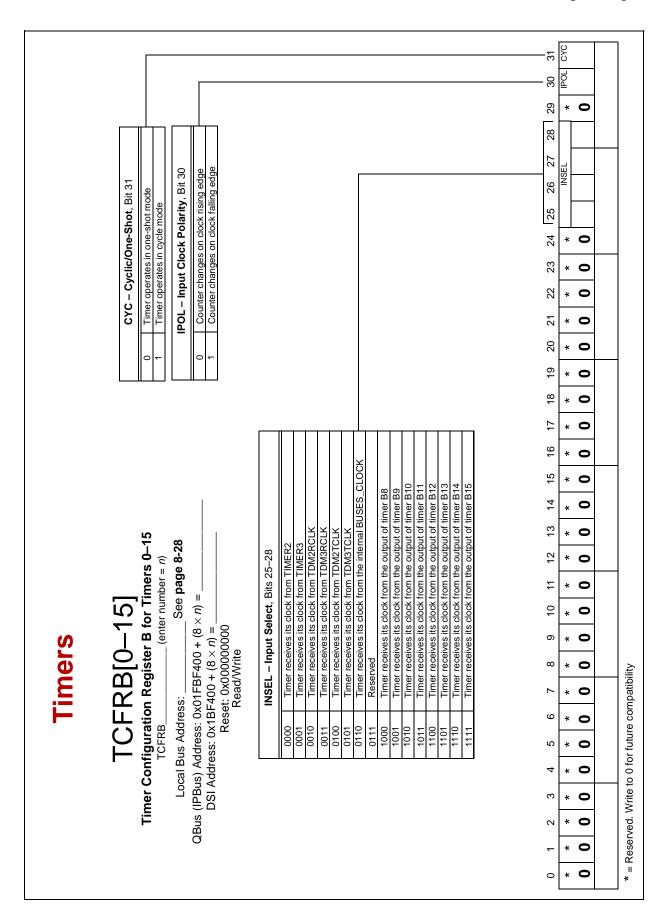

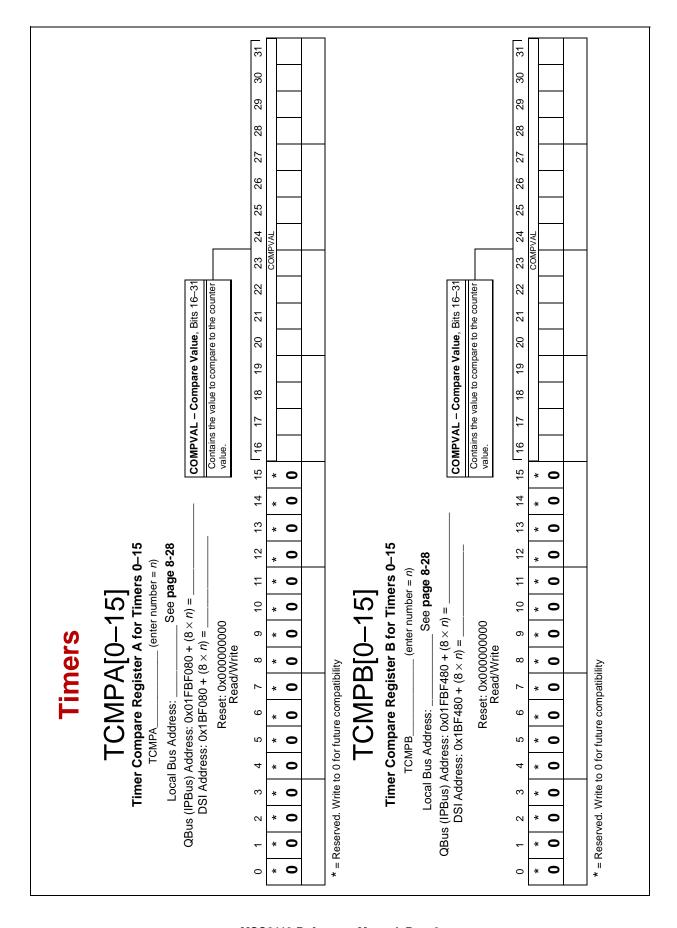

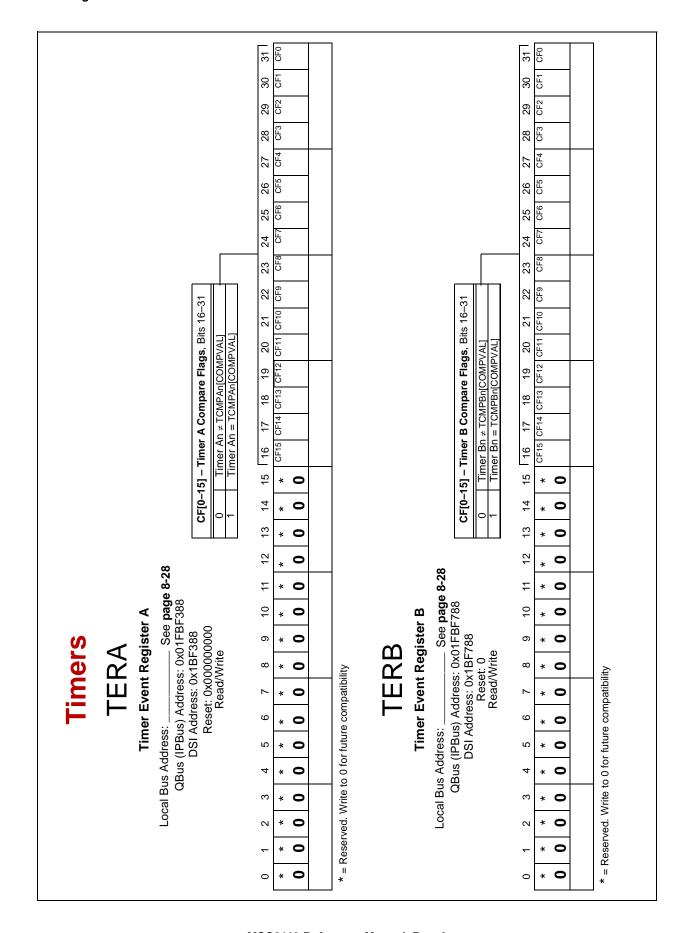

| 22.1.1       | Timers Programming Model                  |       |

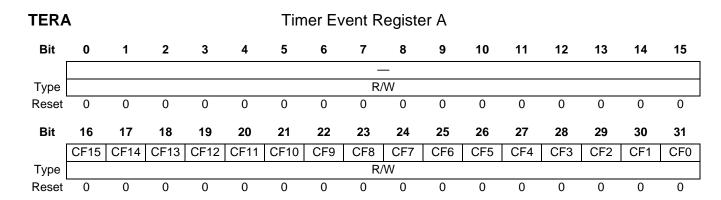

| 22.1.1       | Configuration Registers                   |       |

| 22.1.2       | Control Registers                         |       |

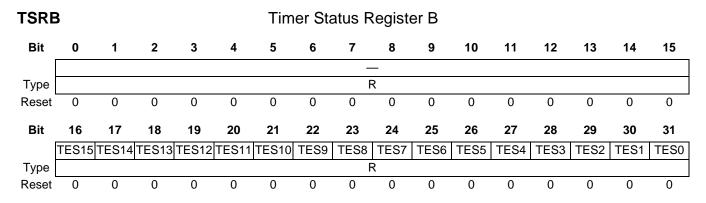

| 22.1.3       | Status Registers                          | 22-17 |

| <b>23</b>    | GPIO                                      |       |

| 23.1         | Features                                  | 23-1  |

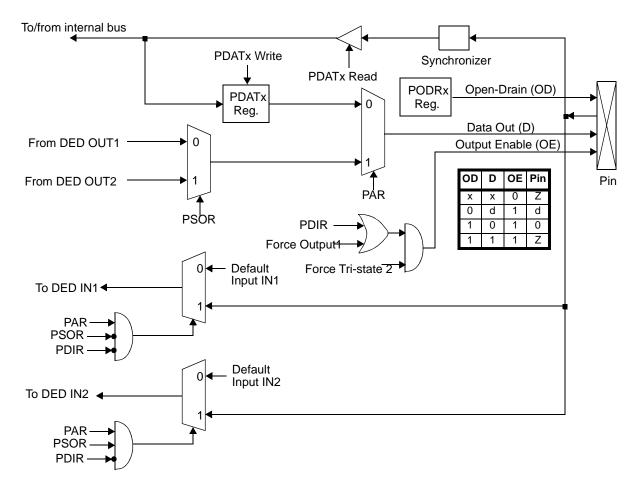

| 23.2         | GPIO Block Diagram                        | 23-2  |

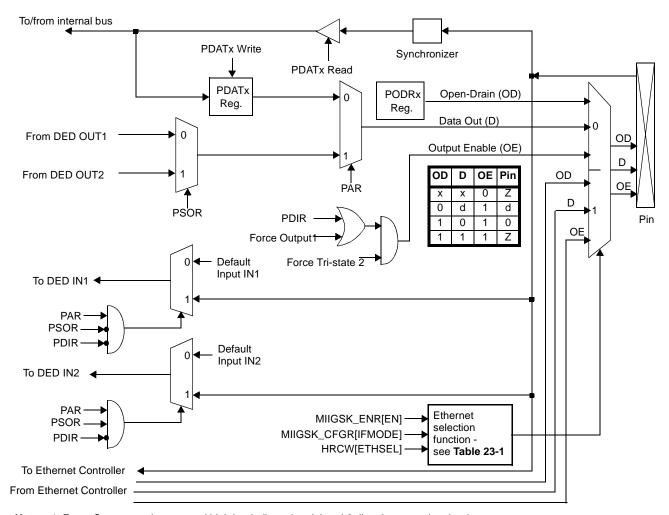

| 23.3         | Ethernet Functionality of GPIO            | 23-4  |

| 23.4         | GPIO Connection Functions                 | 23-6  |

| 23.5         | GPIO Programming Model                    | 23-9  |

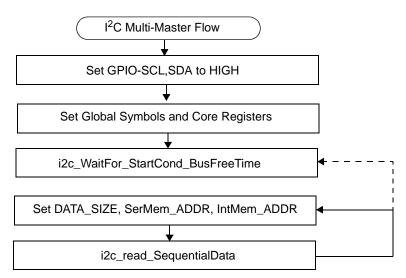

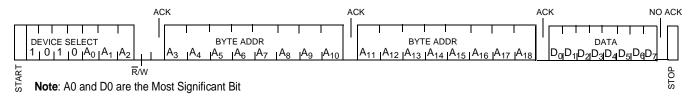

| 24           | I <sup>2</sup> C Software Module          |       |

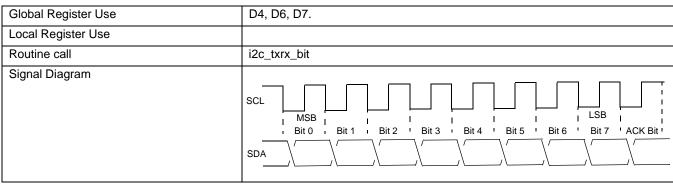

| 24.1         | i2c_txrx_bit Routine                      | 24-3  |

| 24.2         | i2c_txrx_byte Routine                     |       |

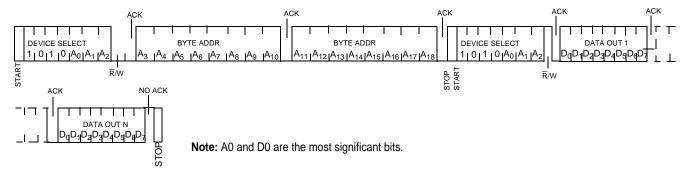

| 24.3         | i2c_read_SequentialData Routine           |       |

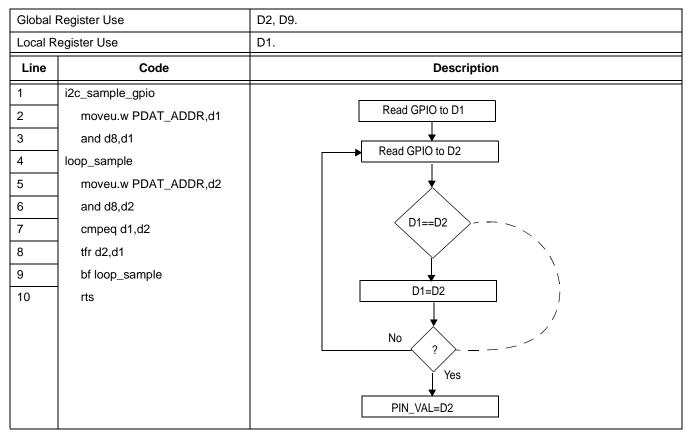

| 24.4         | i2c_sample_gpio Routine                   |       |

| 24.4         | i2c_assert_start Routine                  |       |

| 24.6         | i2c_assert_stop Routine                   |       |

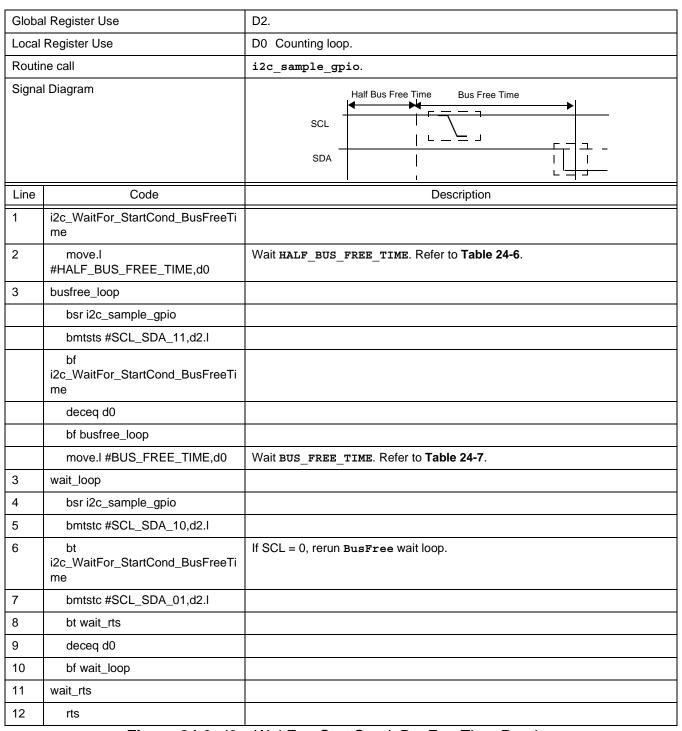

| 24.7         | i2c_WaitFor_StartCond_BusFreeTime Routine |       |

| 24.7         | i2c_write_SequentialData Routine          |       |

| <b>∠⊤.</b> ∪ |                                           | 4-13  |

MSC8113 Reference Manual, Rev. 0

Freescale Semiconductor xvii

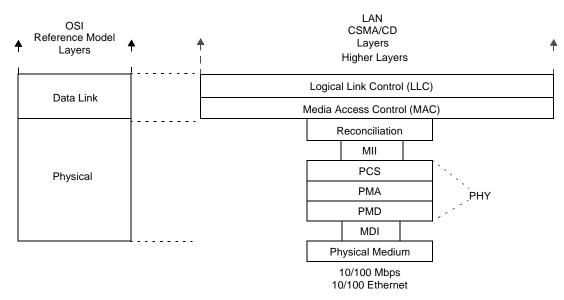

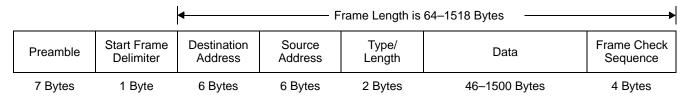

| <b>25</b> | Ethernet Controller                            |        |

|-----------|------------------------------------------------|--------|

| 25.1      | Ethernet Basics                                | . 25-1 |

| 25.2      | Media-Independent Interfaces                   | . 25-5 |

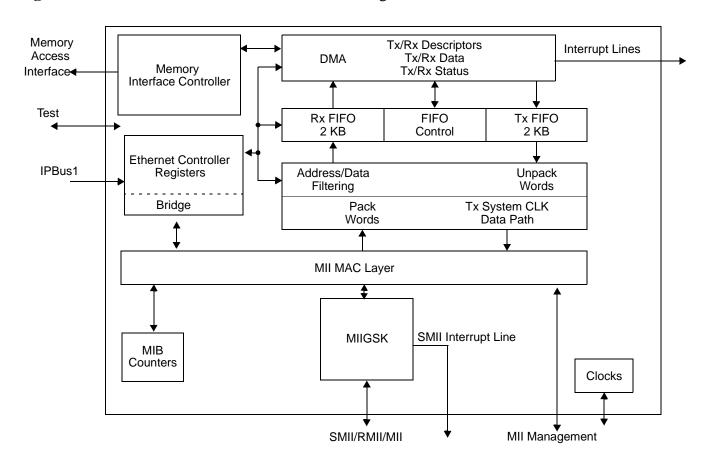

| 25.3      | MSC8113 Ethernet Controller                    | . 25-5 |

| 25.4      | Modes of Operation                             | . 25-6 |

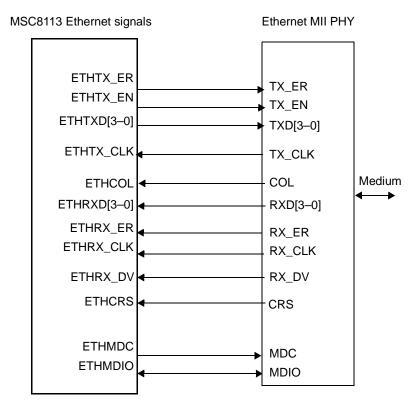

| 25.4.1    | MII Mode                                       | . 25-7 |

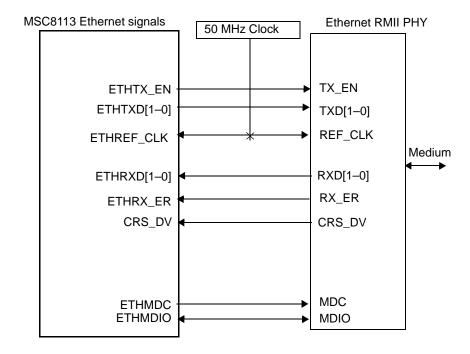

| 25.4.2    | RMII Mode                                      | . 25-7 |

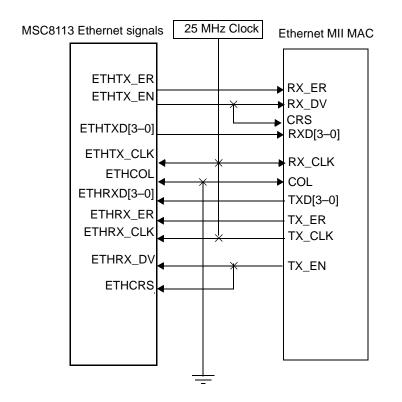

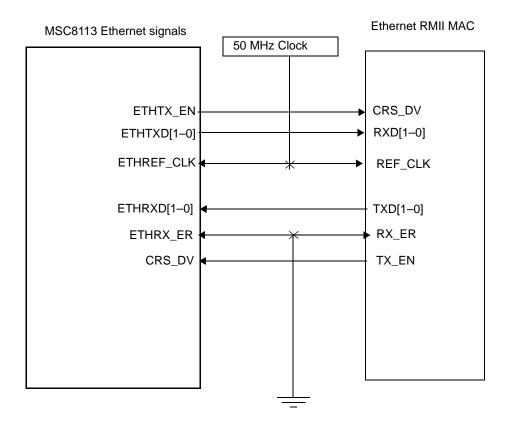

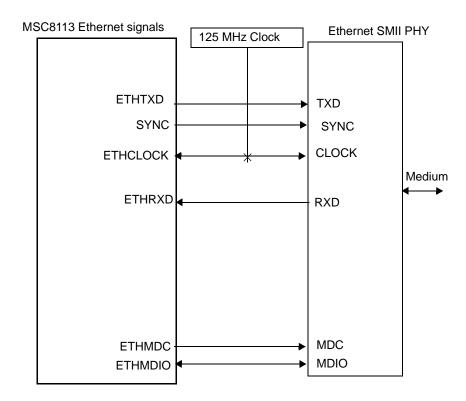

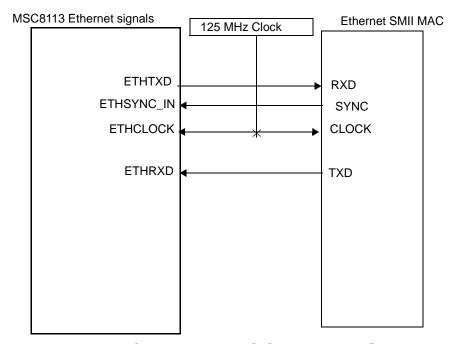

| 25.4.3    | SMII Mode                                      | . 25-7 |

| 25.4.4    | Special Modes                                  | . 25-8 |

| 25.4.4.1  | Loopback Mode                                  | . 25-8 |

| 25.4.4.2  | Echo Mode                                      | . 25-9 |

| 25.4.4.3  | Low-Power Stop Mode                            | . 25-9 |

| 25.4.5    | Management Interface                           | . 25-9 |

| 25.5      | External Signals                               | 25-10  |

| 25.6      | Ethernet Controller Interfaces                 | 25-12  |

| 25.6.1    | MII                                            | 25-13  |

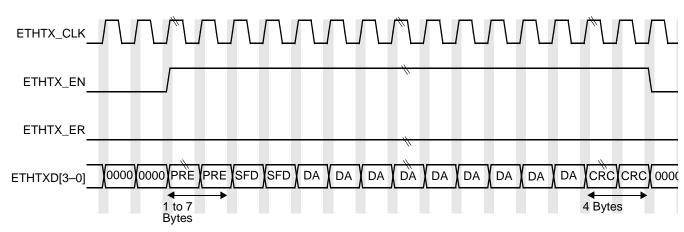

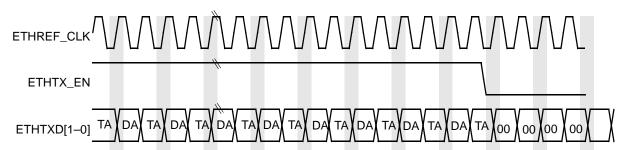

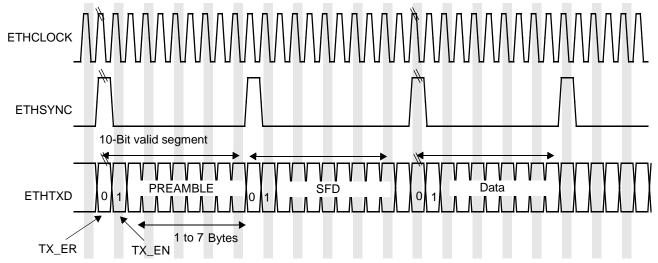

| 25.6.1.1  | MII Transmit Flow                              | 25-13  |

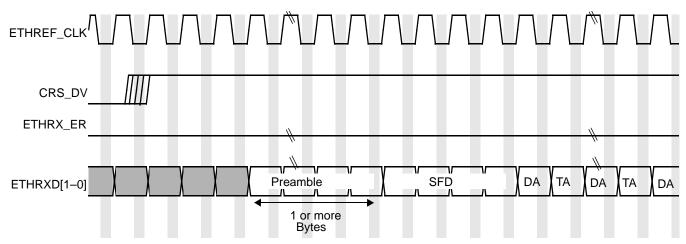

| 25.6.1.2  | MII Receive Flow                               | 25-14  |

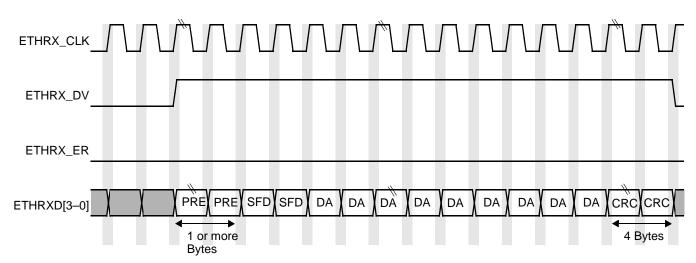

| 25.6.2    | RMII                                           | 25-14  |

| 25.6.2.1  | RMII Transmit Flow                             | 25-15  |

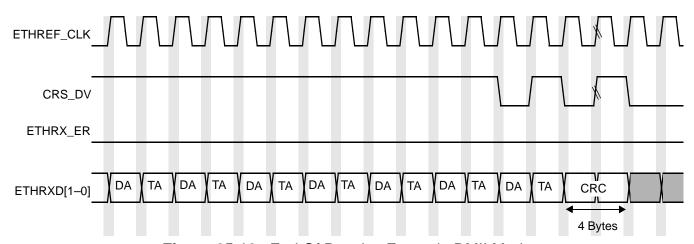

| 25.6.2.2  | RMII Receive Flow                              | 25-16  |

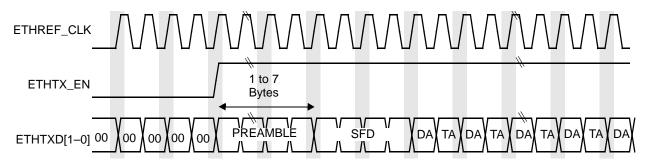

| 25.6.3    | SMII                                           | 25-16  |

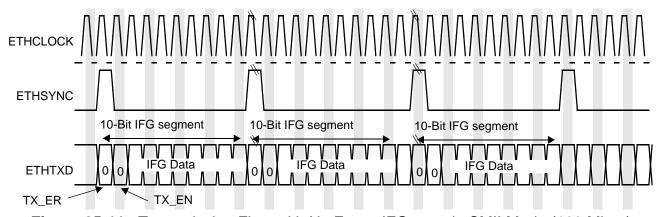

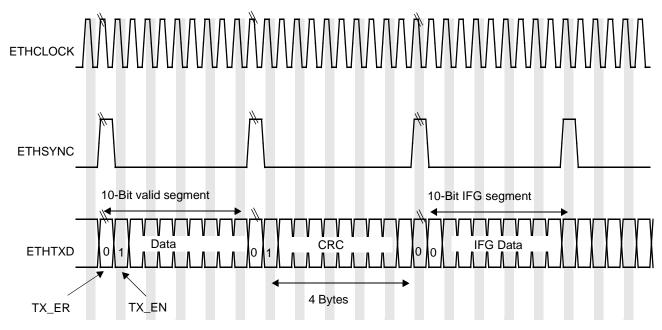

| 25.6.3.1  | SMII Transmit Flow                             | 25-17  |

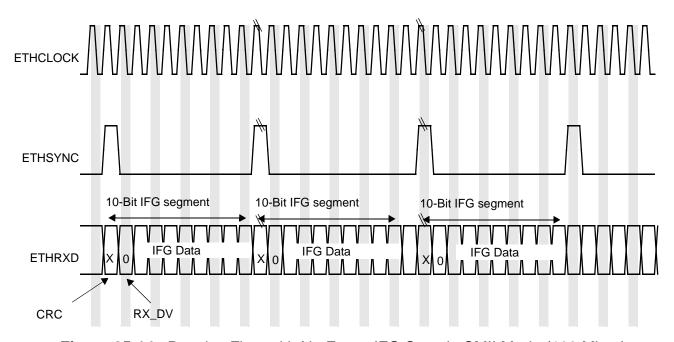

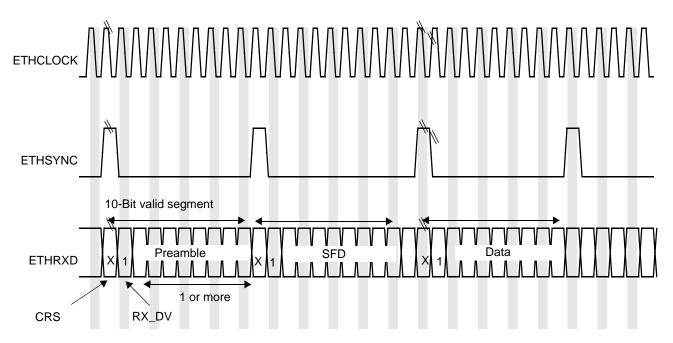

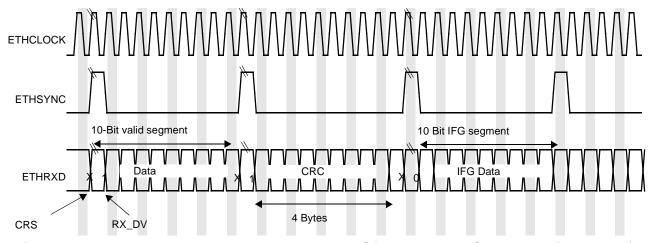

| 25.6.3.2  | SMII Receive Flow Mode                         | 25-19  |

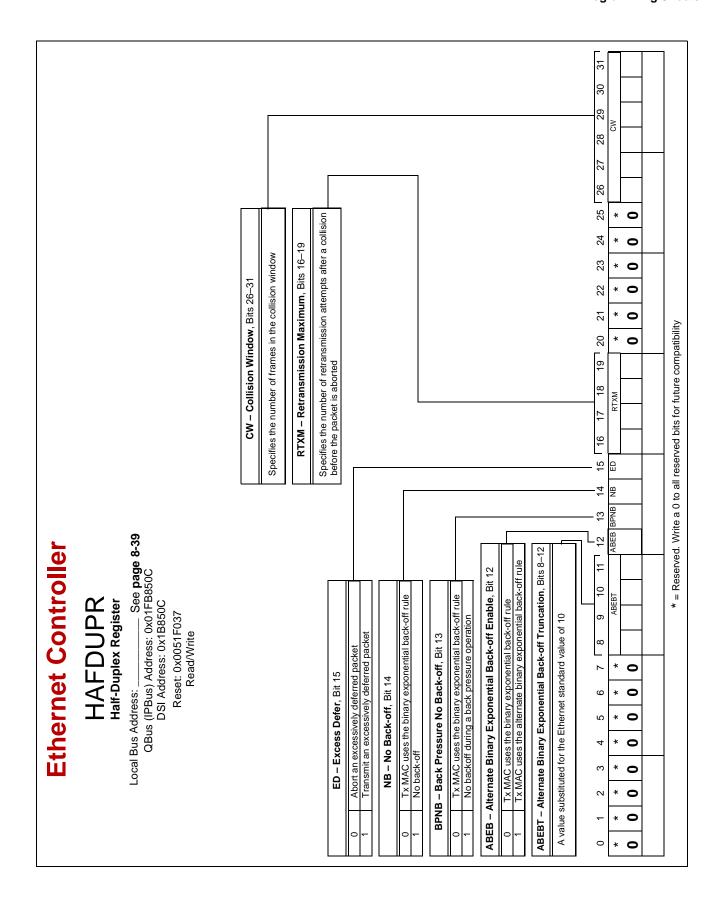

| 25.7      | MAC Control of CSMA/CD                         | 25-21  |

| 25.7.1    | Handling Packet Collisions                     | 25-21  |

| 25.7.2    | Controlling Packet Flow                        | 25-22  |

| 25.7.3    | Controlling PHY Links                          | 25-22  |

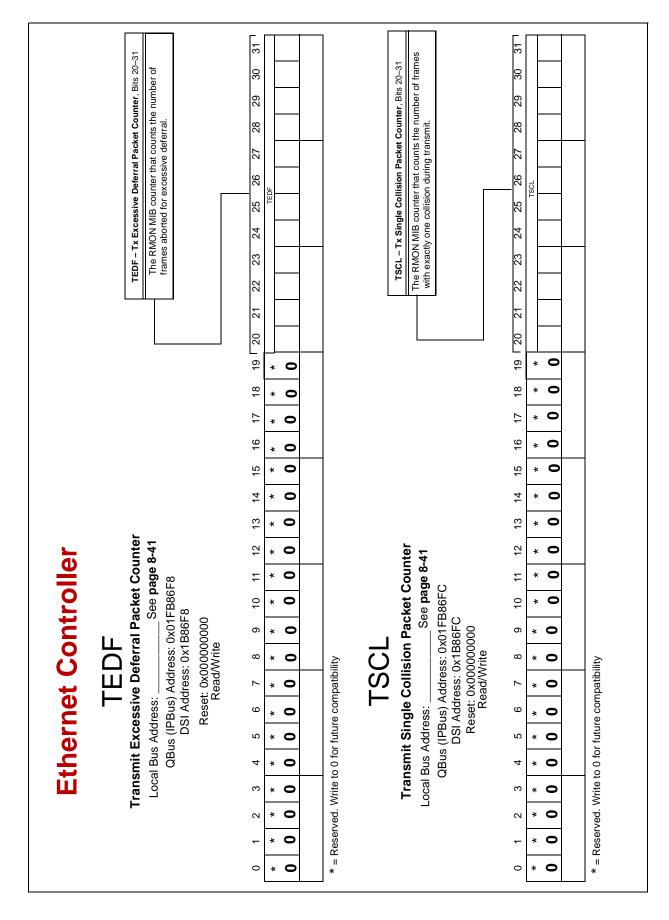

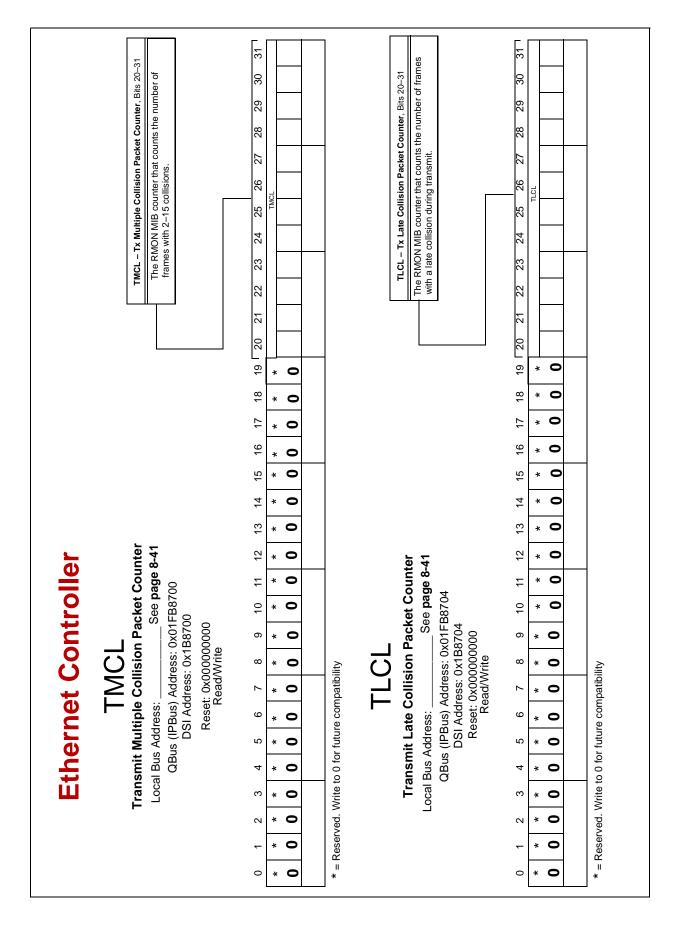

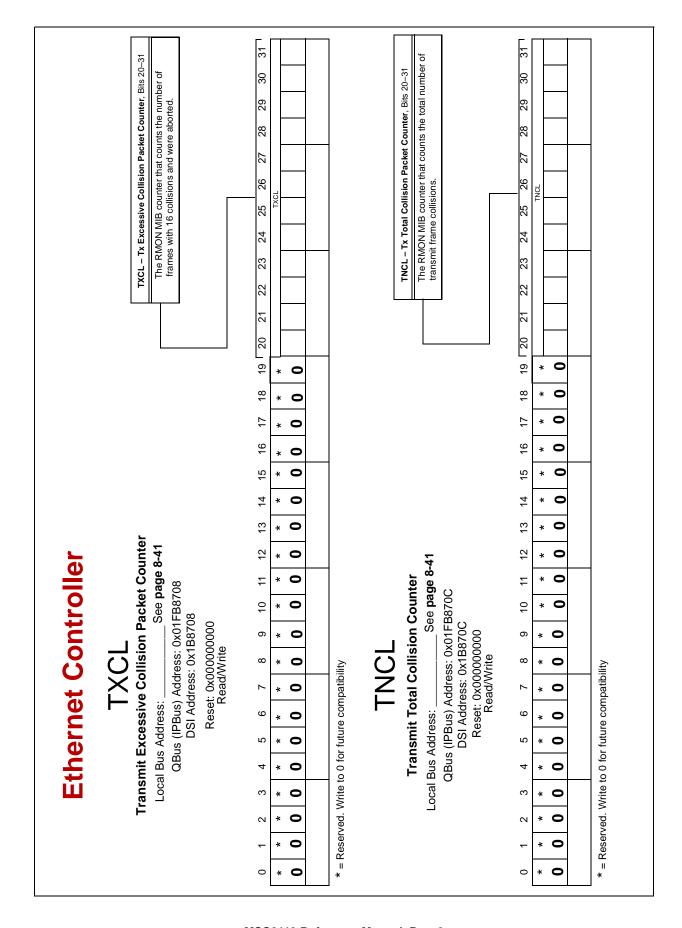

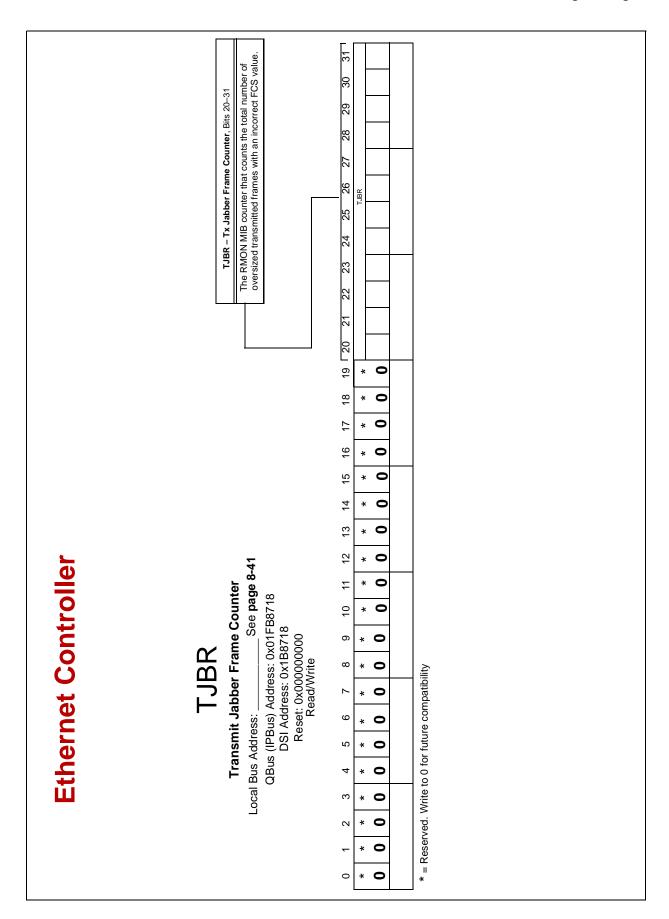

| 25.8      | RMON Support                                   | 25-23  |

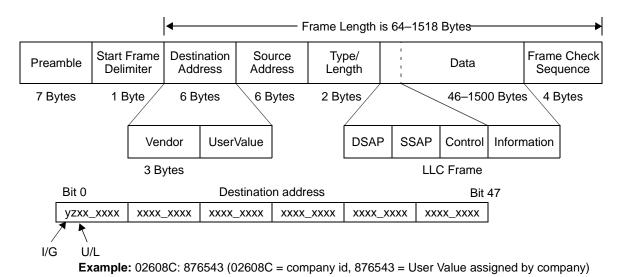

| 25.9      | Frame Recognition                              | 25-23  |

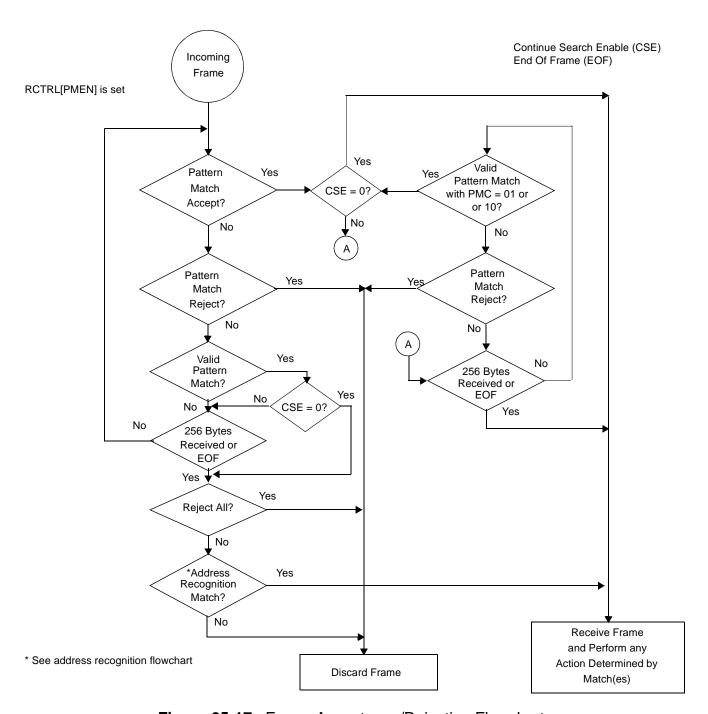

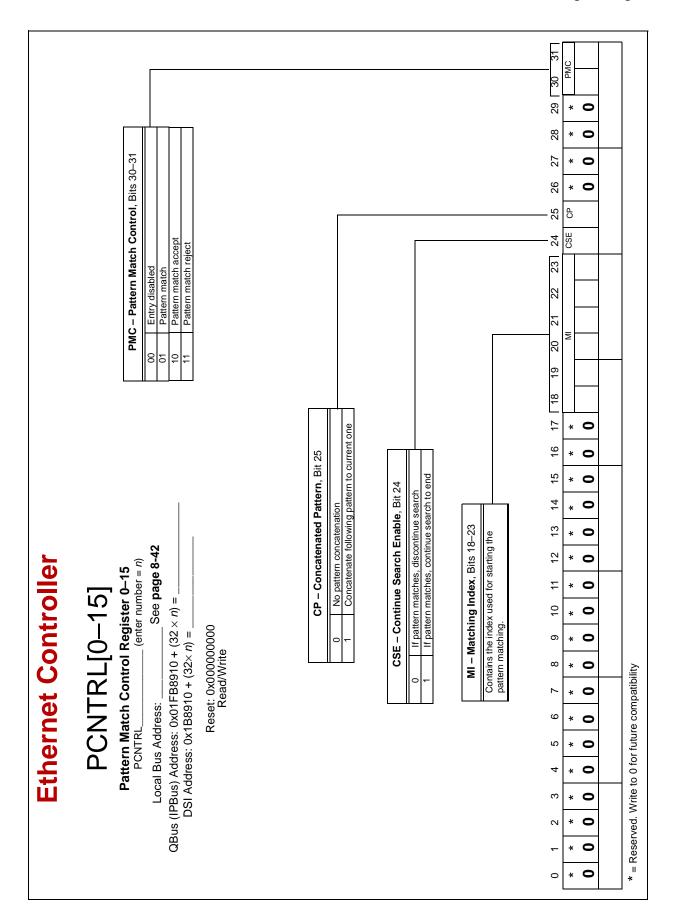

| 25.9.1    | Pattern Matching Recognition                   | 25-23  |

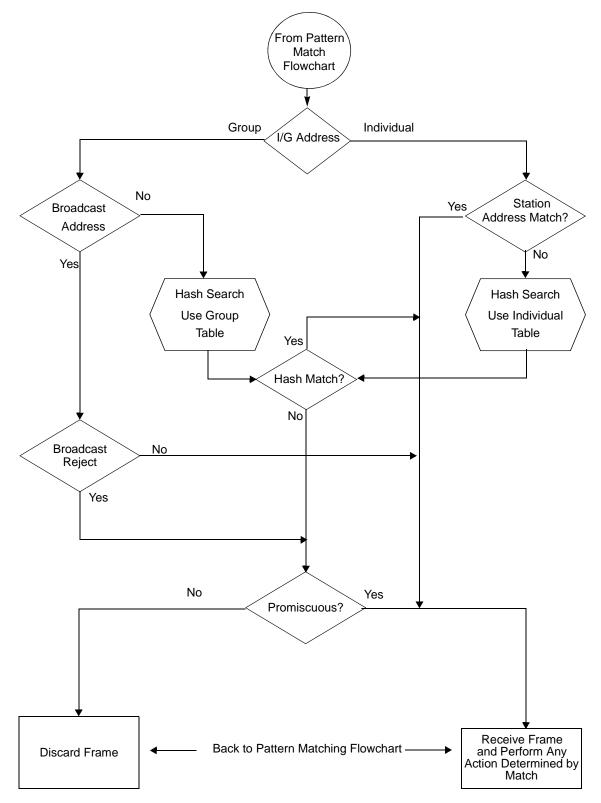

| 25.9.2    | Destination Address Recognition                | 25-25  |

| 25.9.3    | Hash Table Algorithm                           | 25-27  |

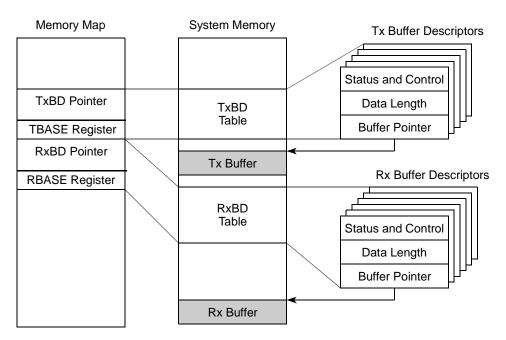

| 25.10     | Buffer Descriptors                             | 25-28  |

| 25.10.1   | Data Buffer Descriptor                         | 25-28  |

| 25.10.2   | Receive Frame Processing with Pattern Matching | 25-30  |

| 25.10.3   | Receive Pattern Matching Filing                | 25-31  |

| 25.10.4   | Filing                                         | 25-35  |

| 25.10.5   | Transmit Frame Processing with Insertion       | 25-36  |

| 25.11     | Flow Control                                   | 25-38  |

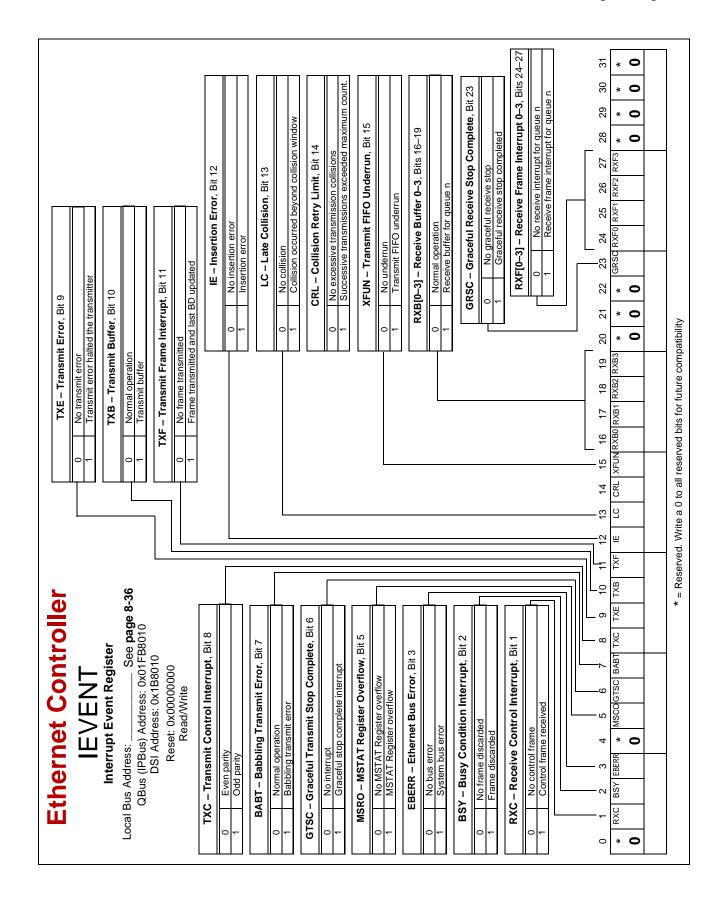

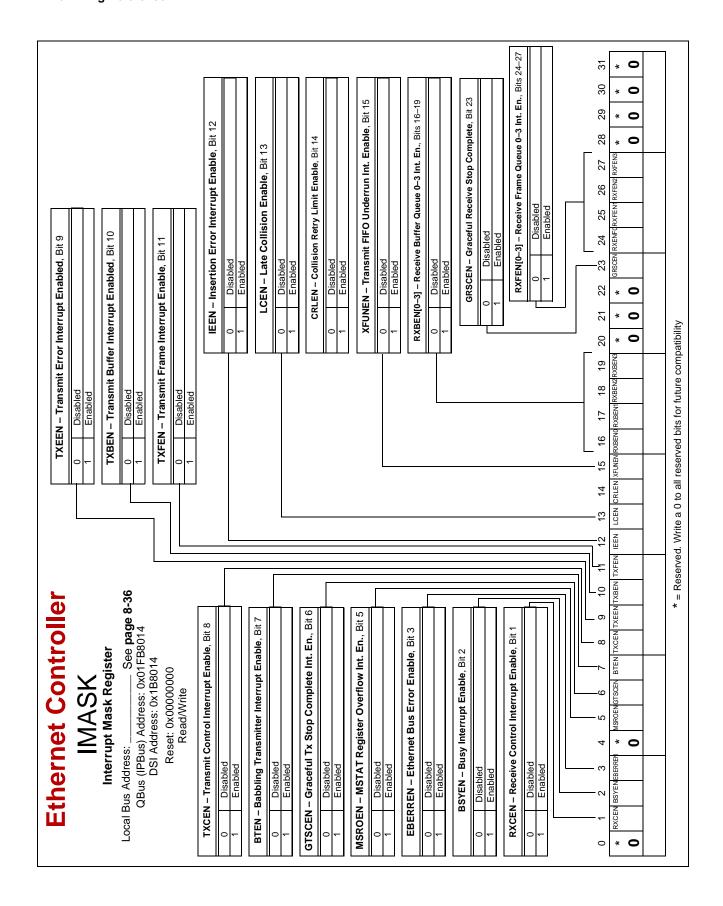

| 25.12     | Interrupt Handling                             | 25-39  |

|          | Contents                               |

|----------|----------------------------------------|

| 25.13    | Error-Handling                         |

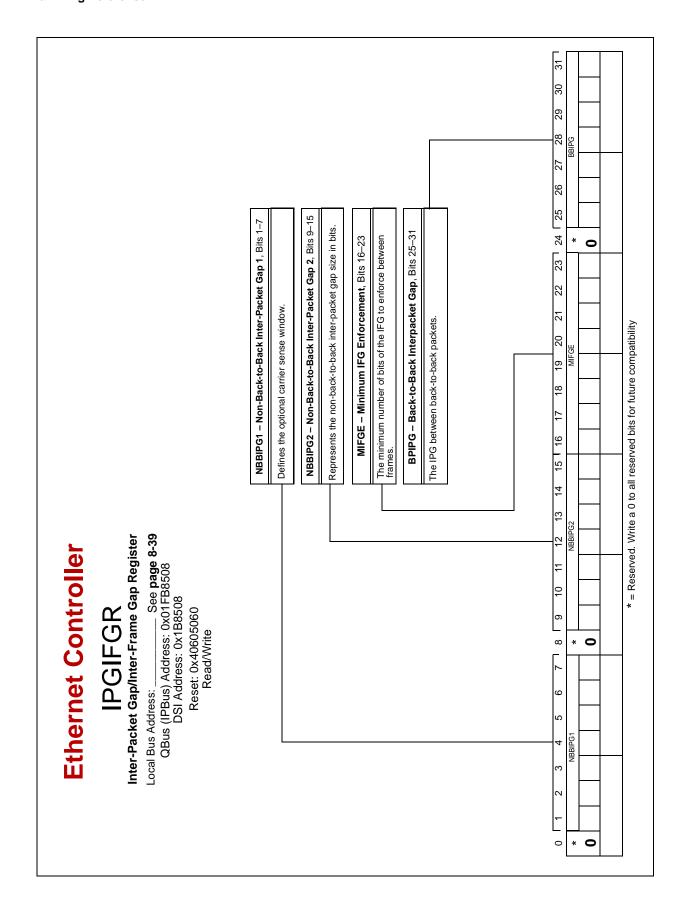

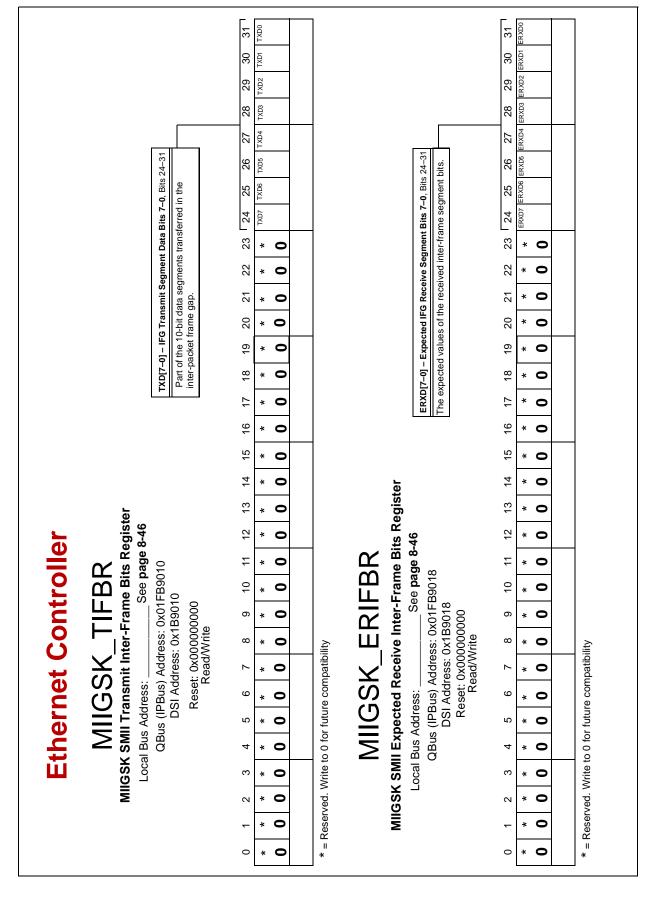

| 25.14    | Inter-Packet Gap Time                  |

| 25.15    | Connecting to Physical Interfaces      |

| 25.16    | Initialization and Reset               |

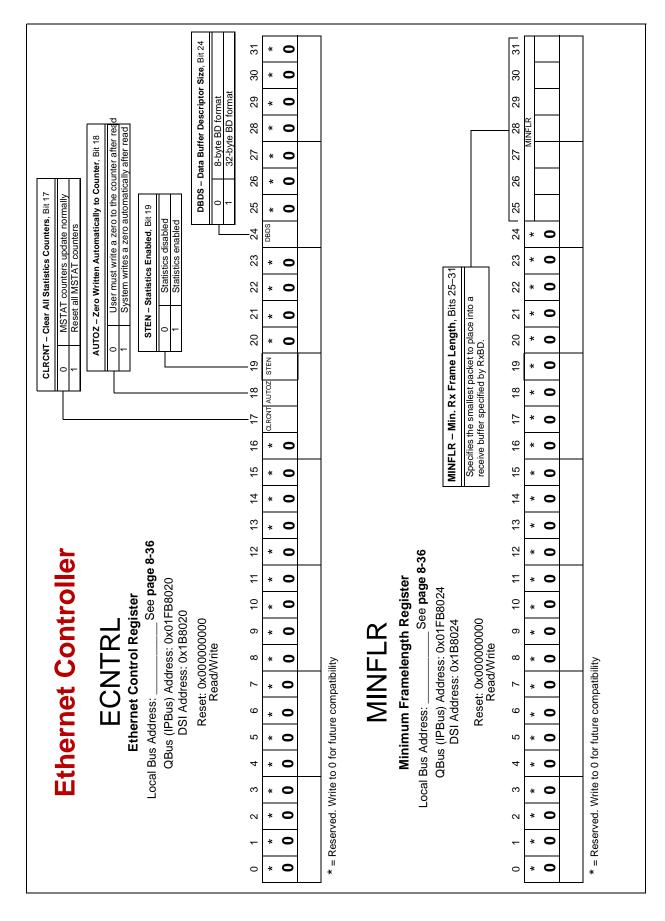

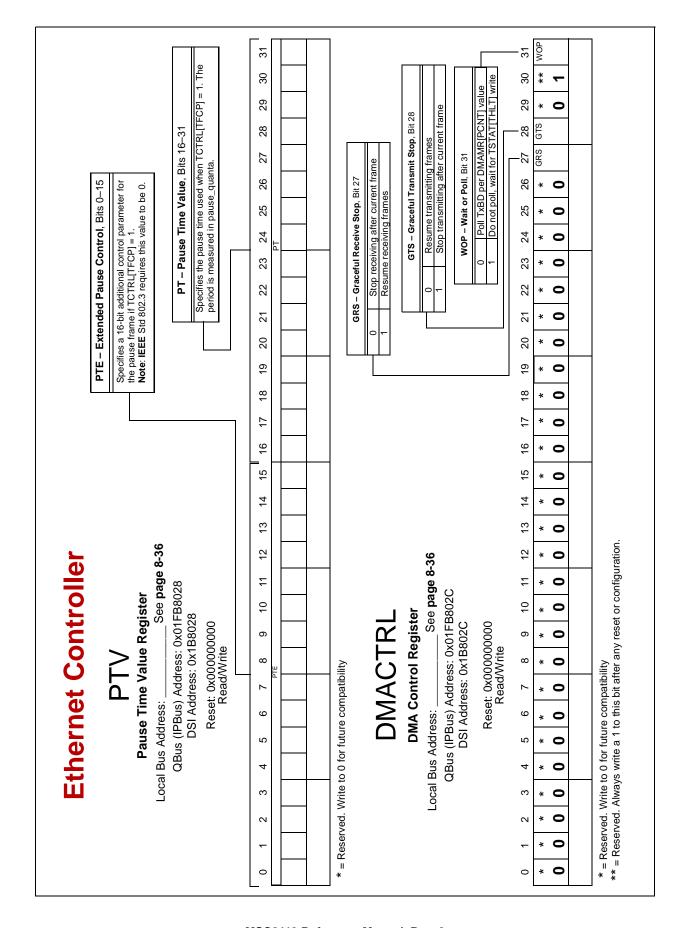

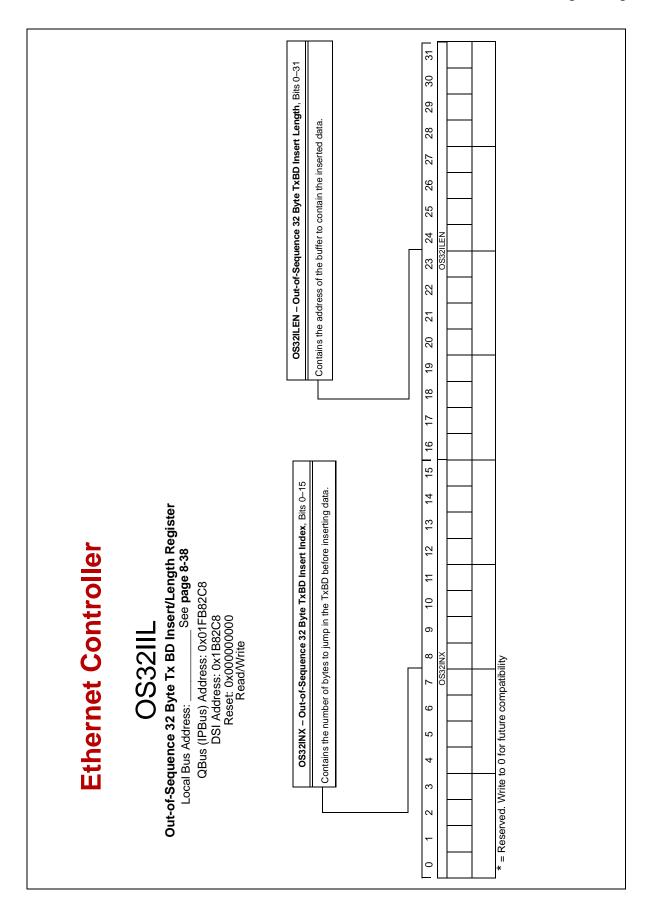

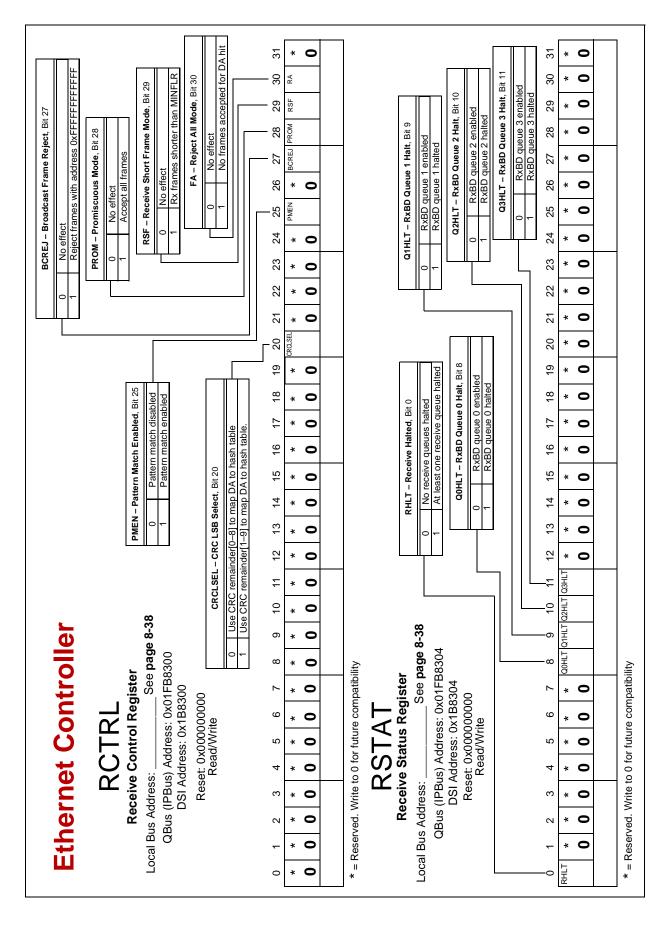

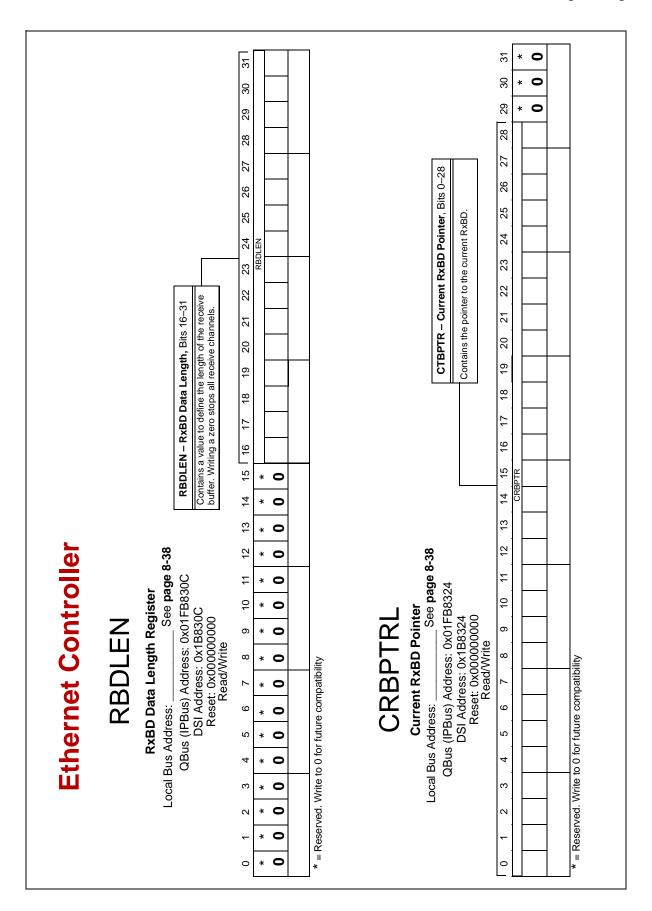

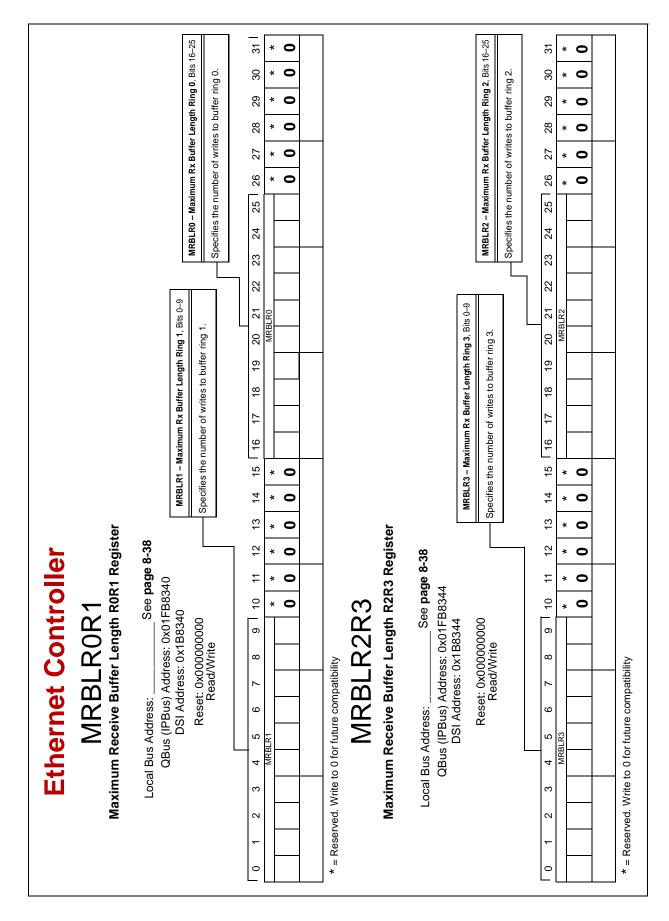

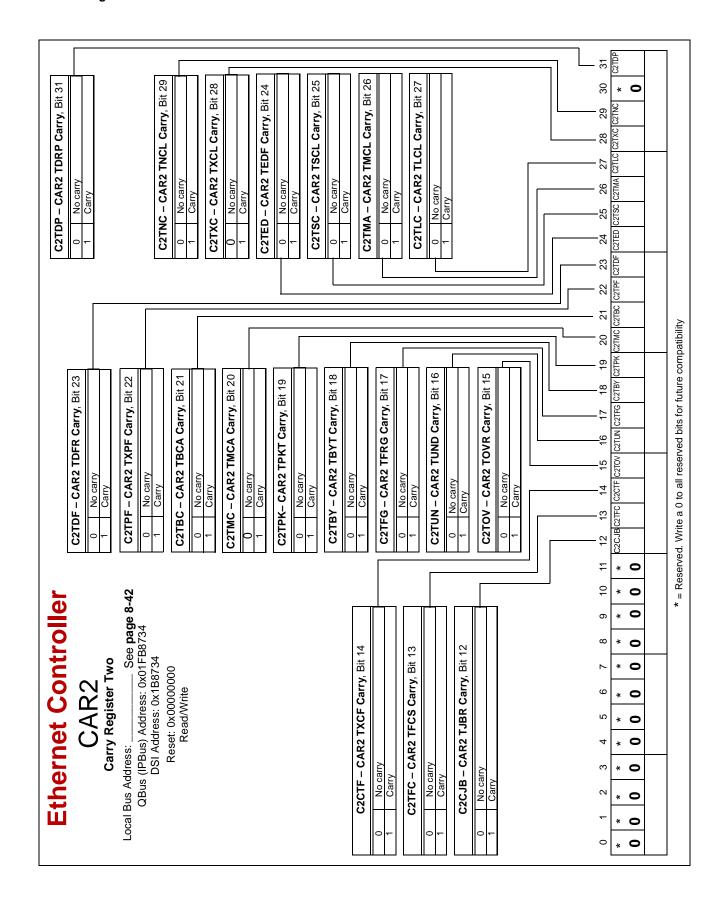

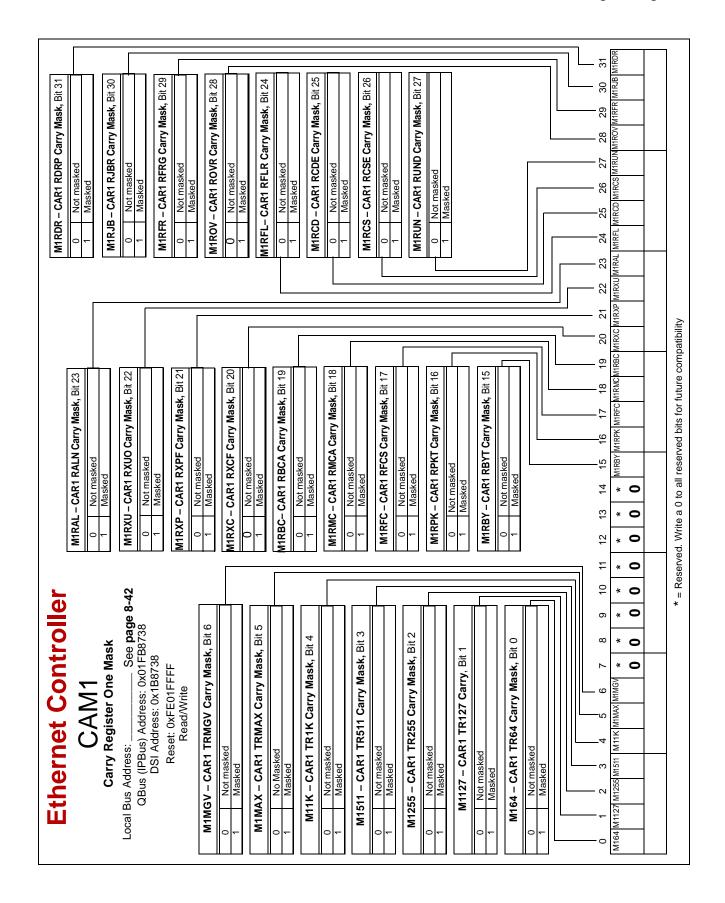

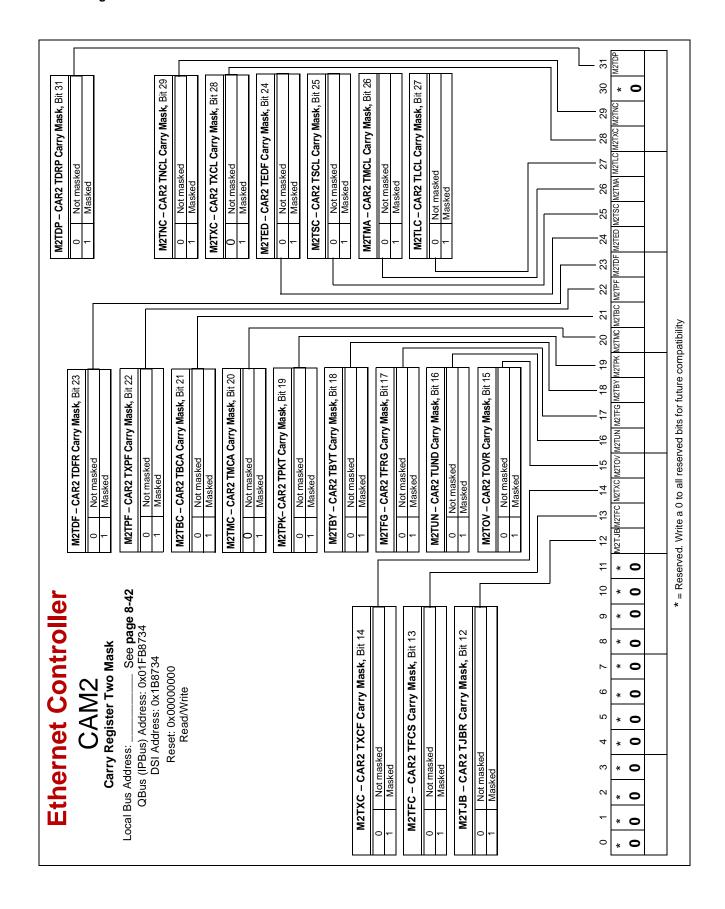

| 25.17    | Ethernet Controller Programming Model  |

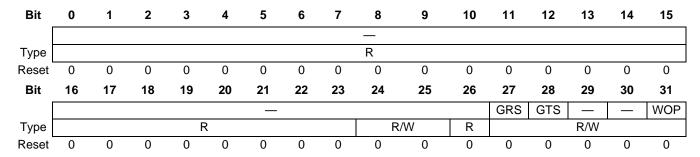

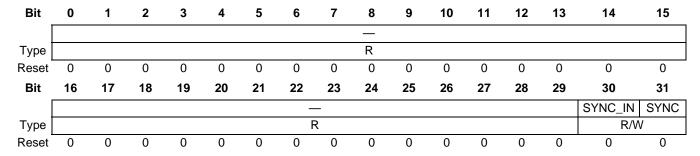

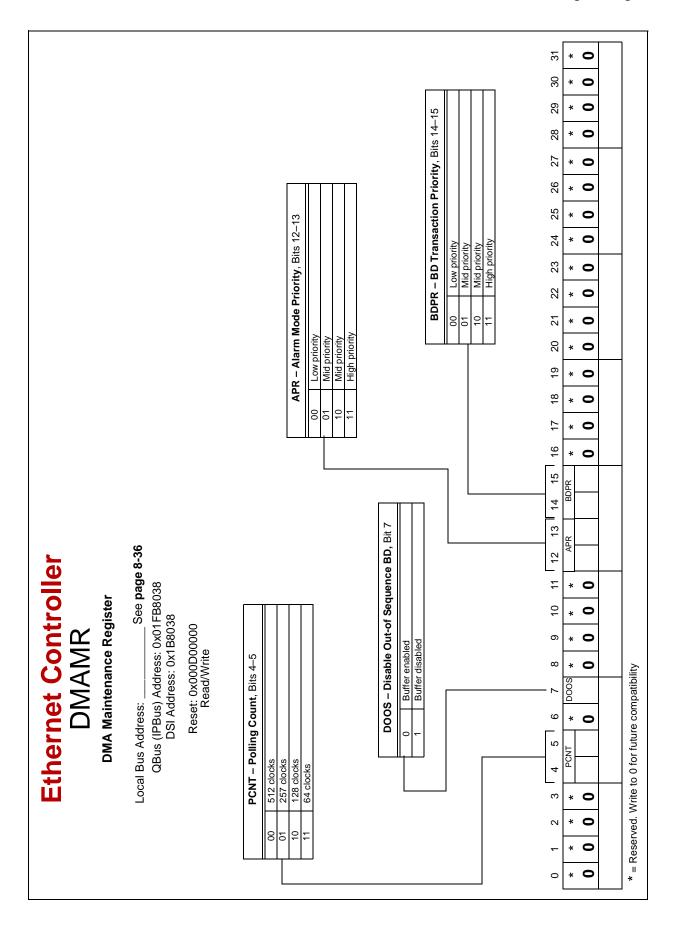

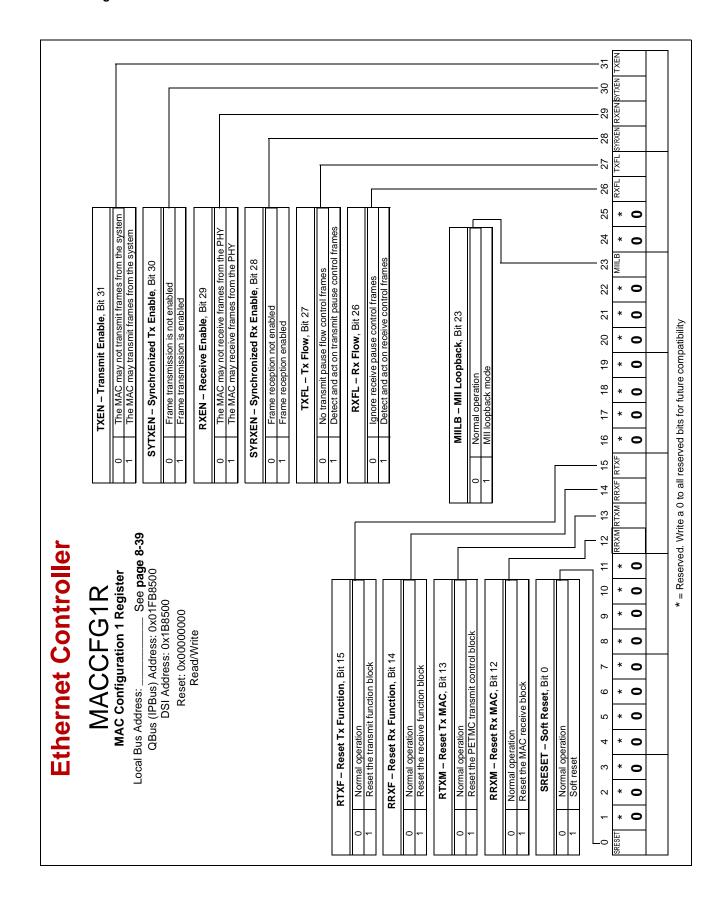

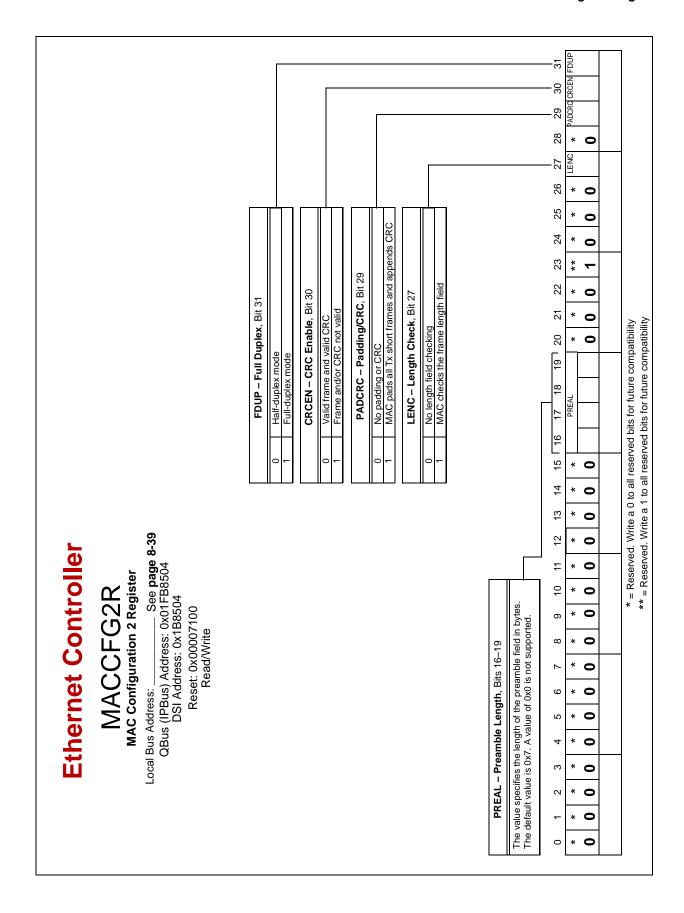

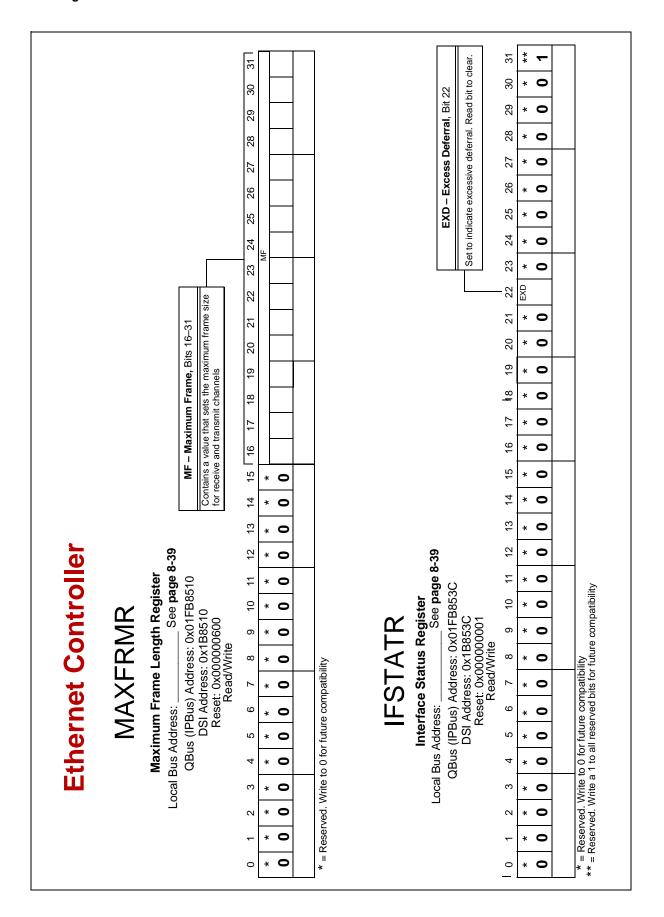

| 25.17.1  | General Control and Status Registers   |

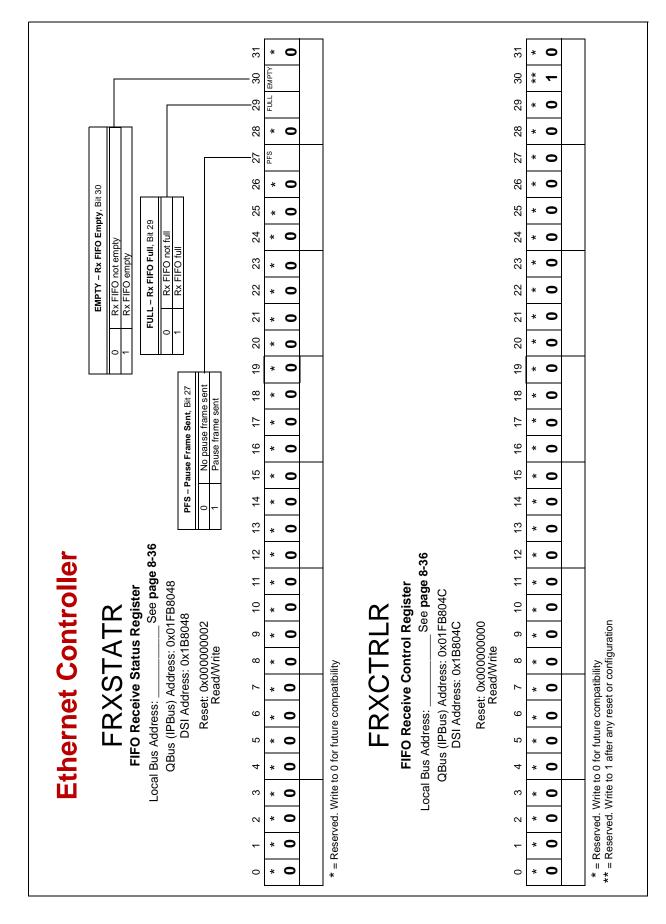

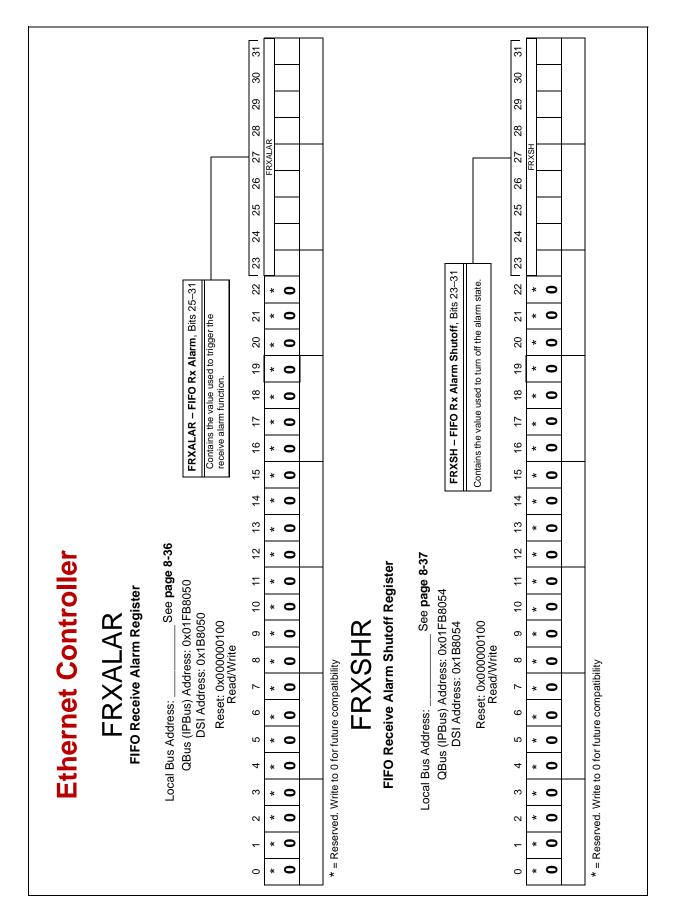

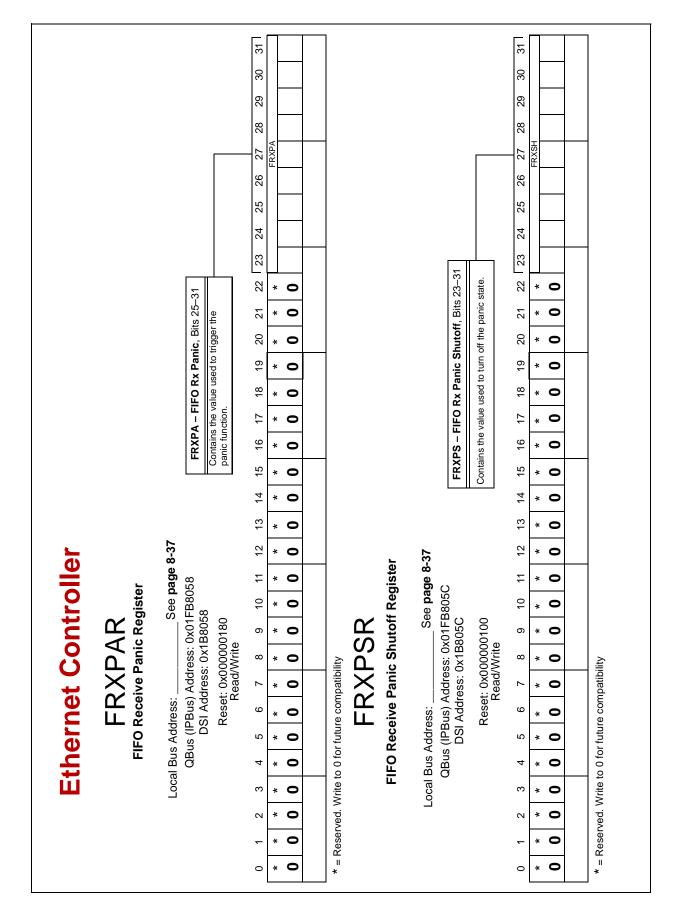

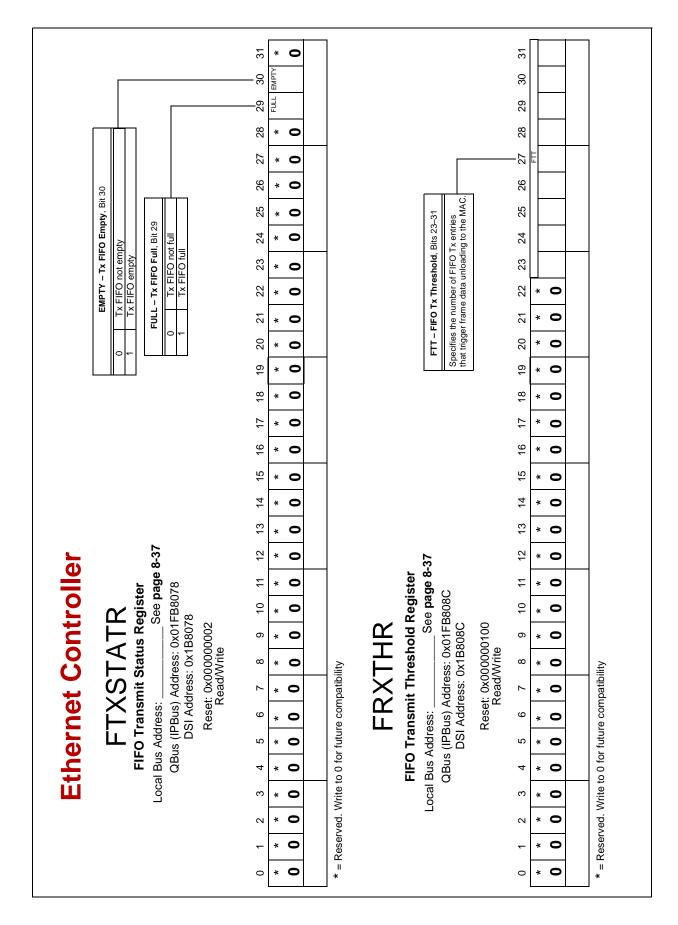

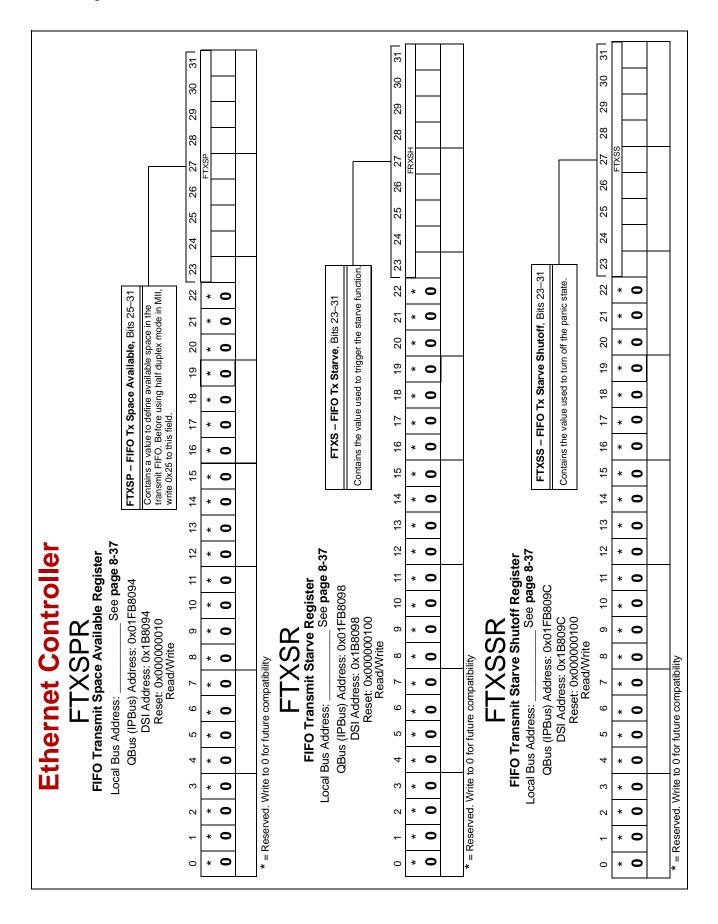

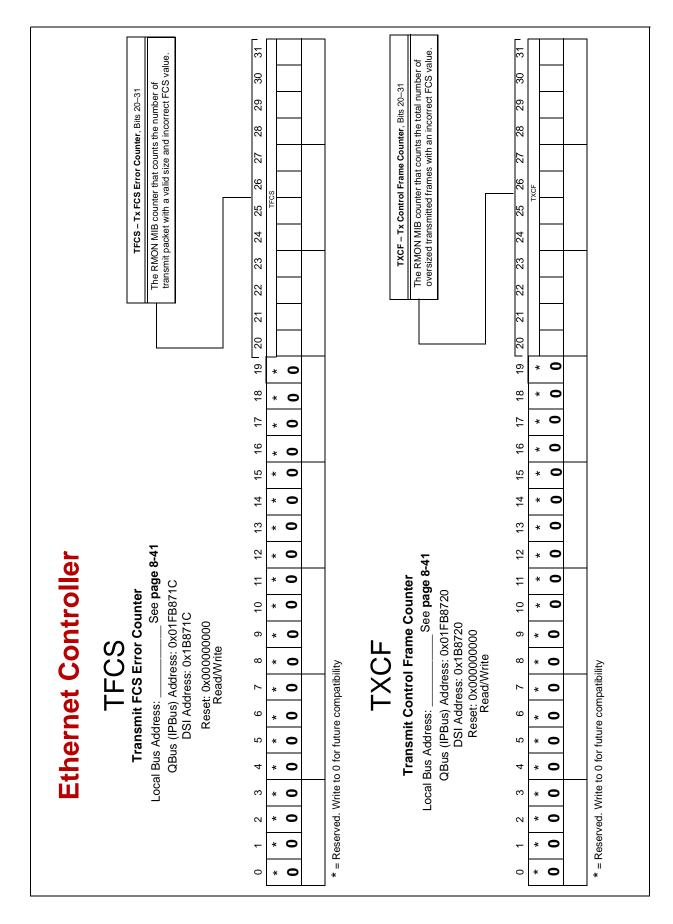

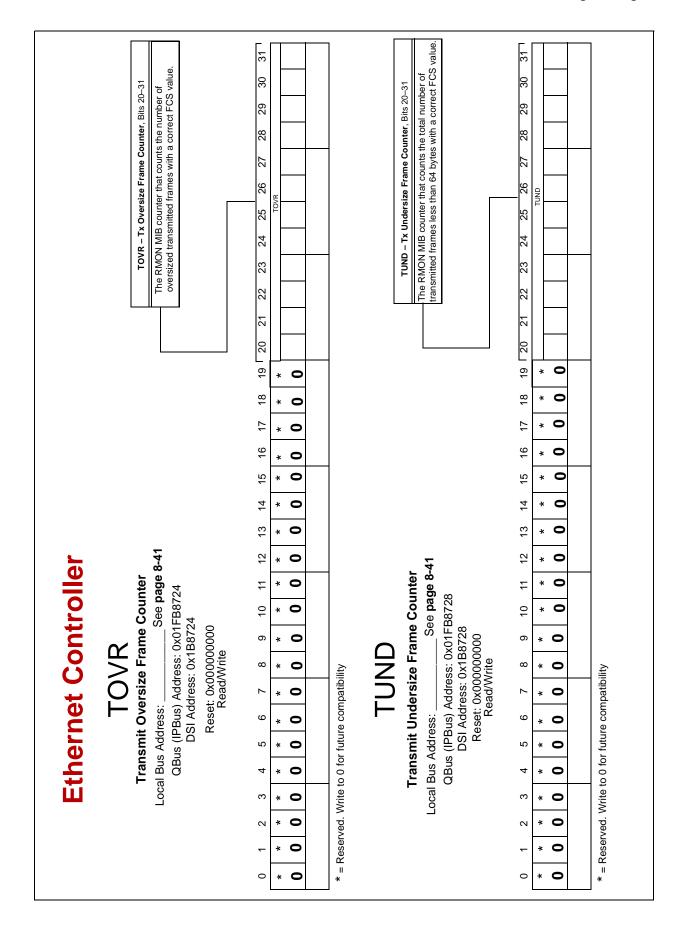

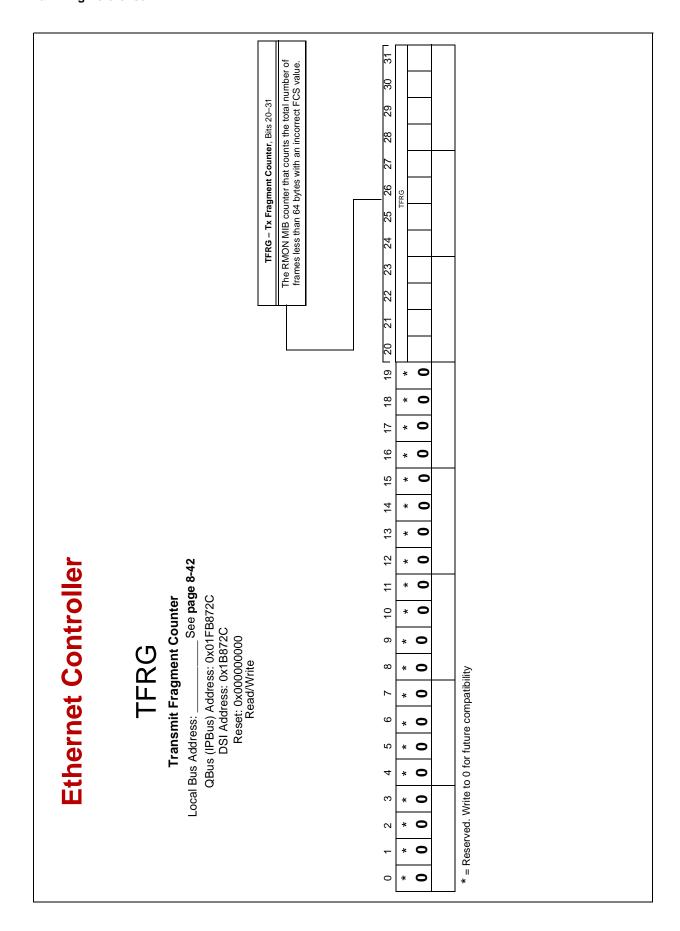

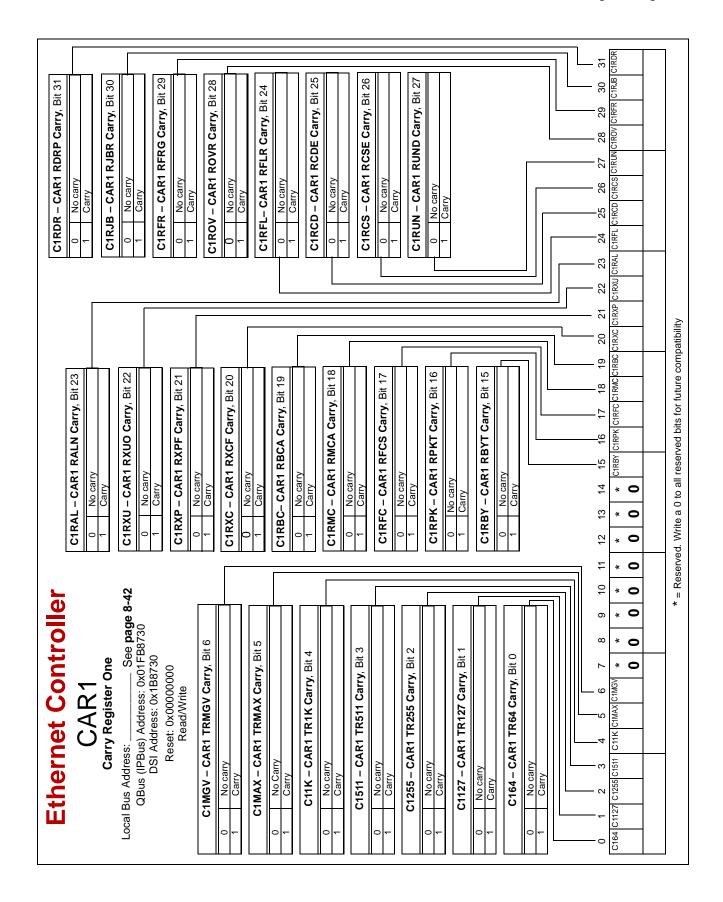

| 25.17.2  | FIFO Control and Status Registers      |

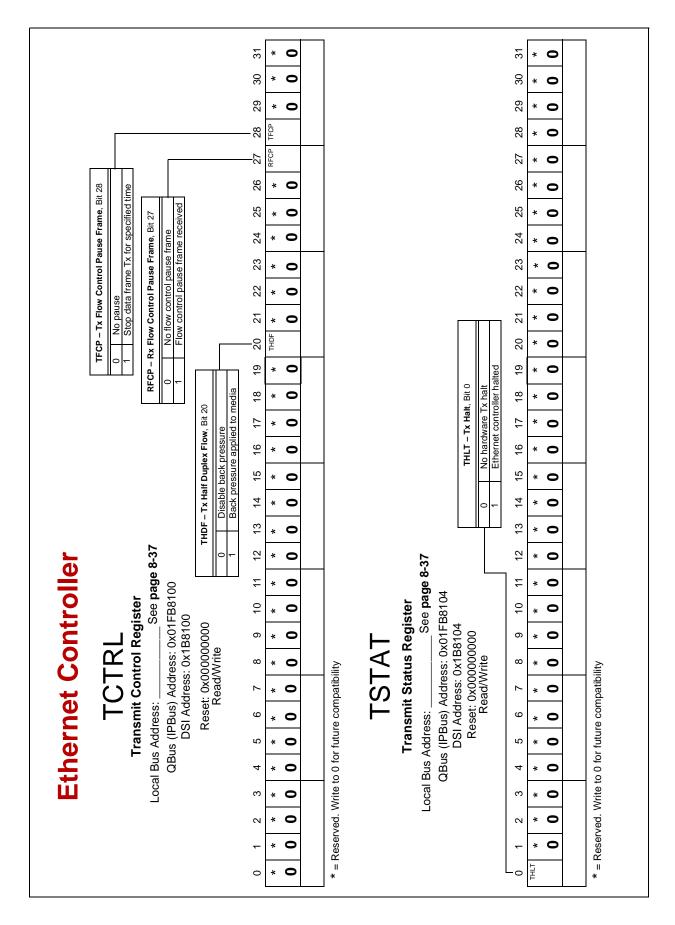

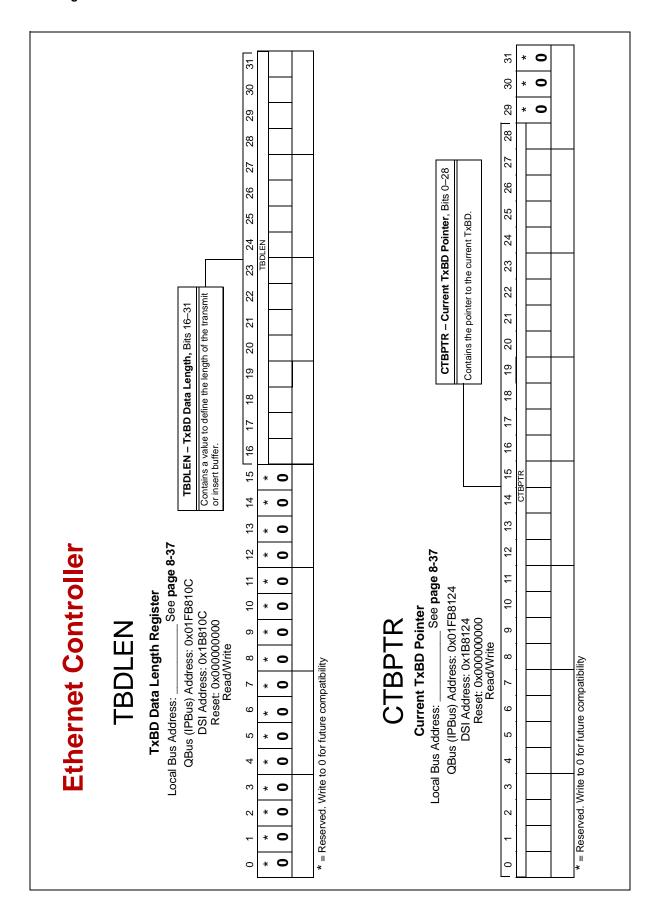

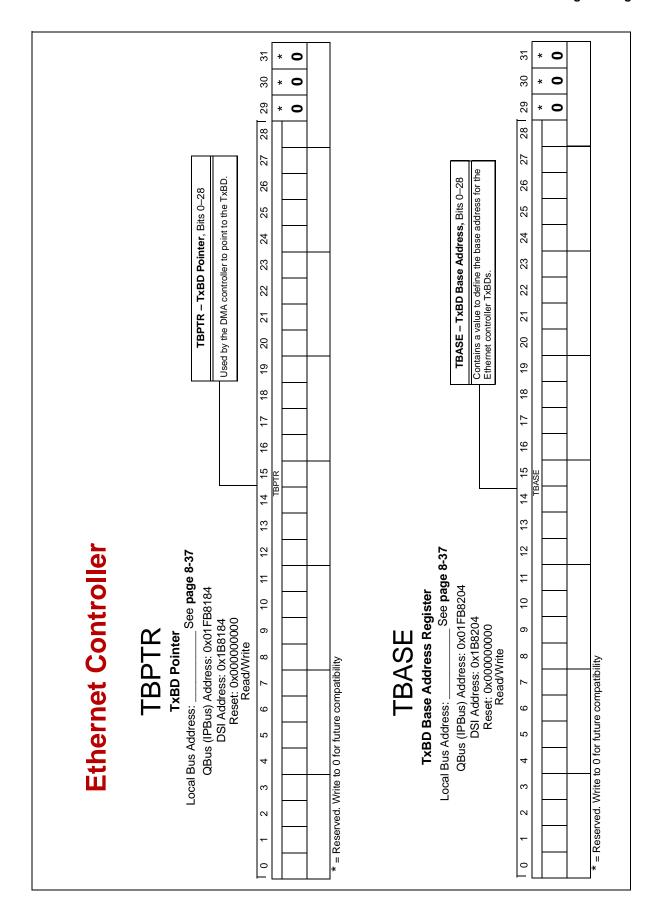

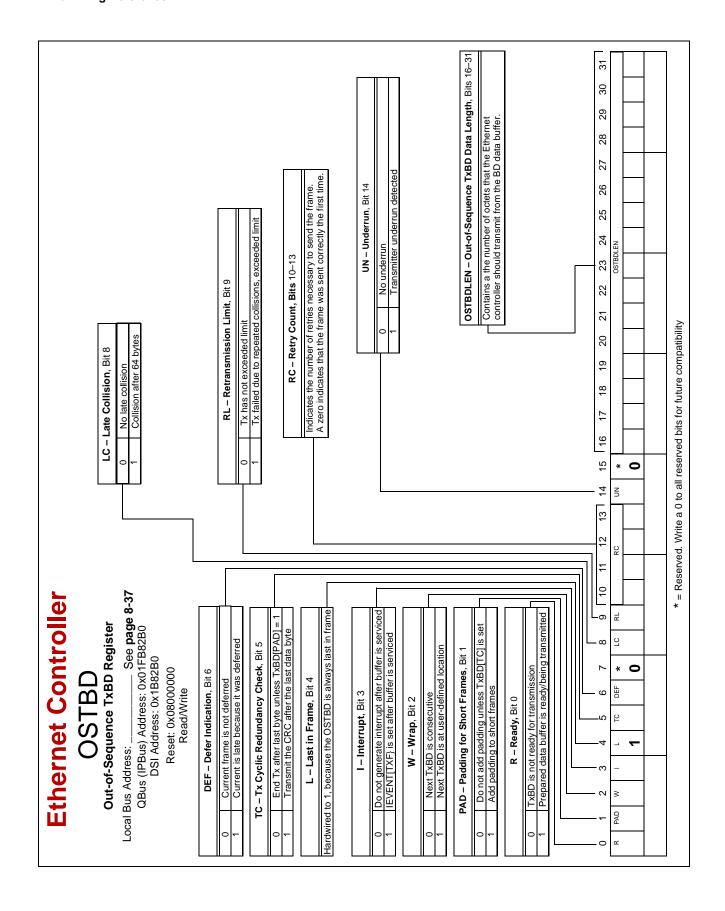

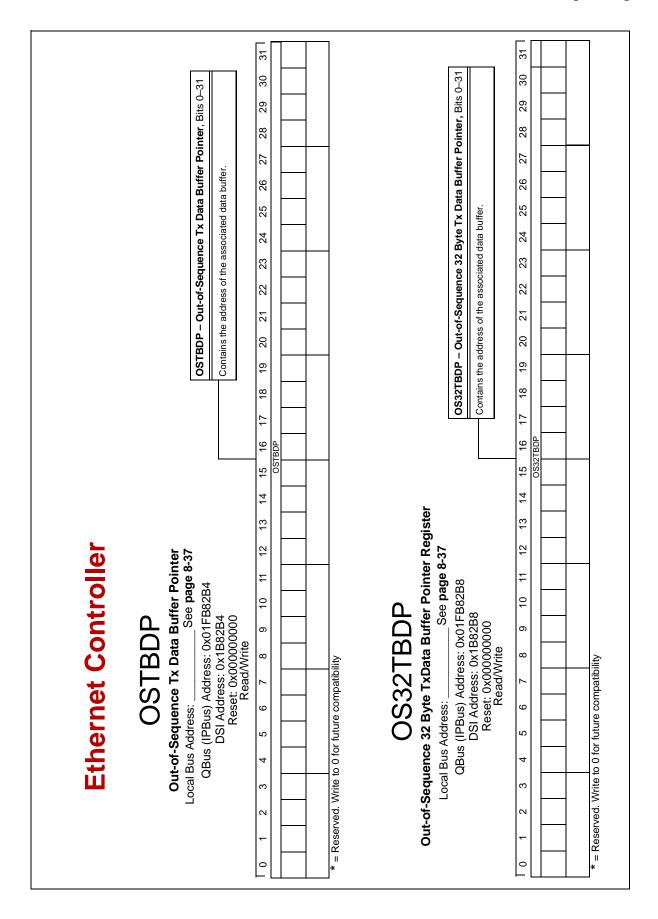

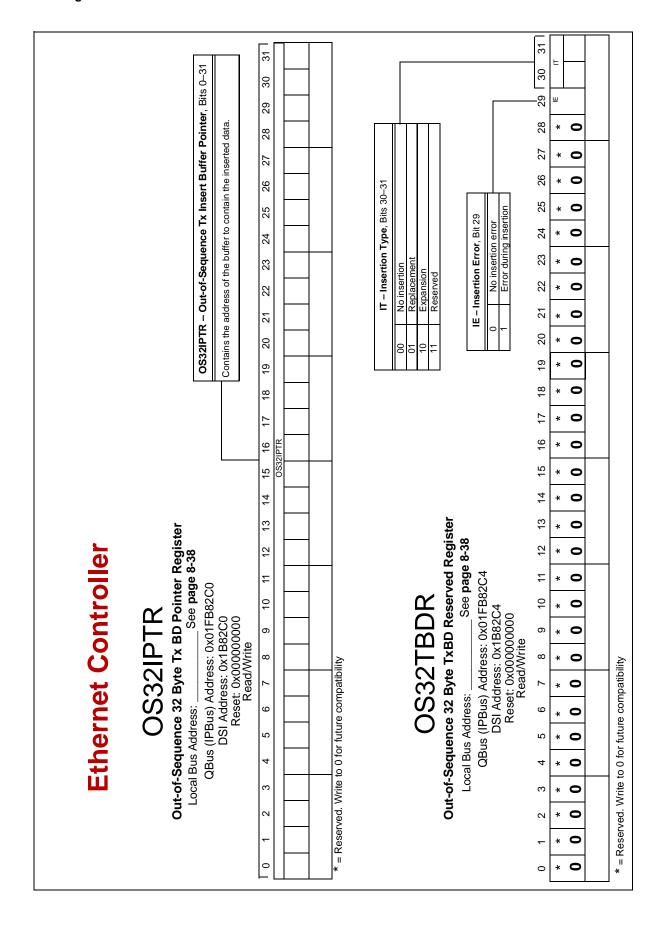

| 25.17.3  | Transmit Control and Status Registers  |

| 25.17.4  | Receive Control and Status Registers   |

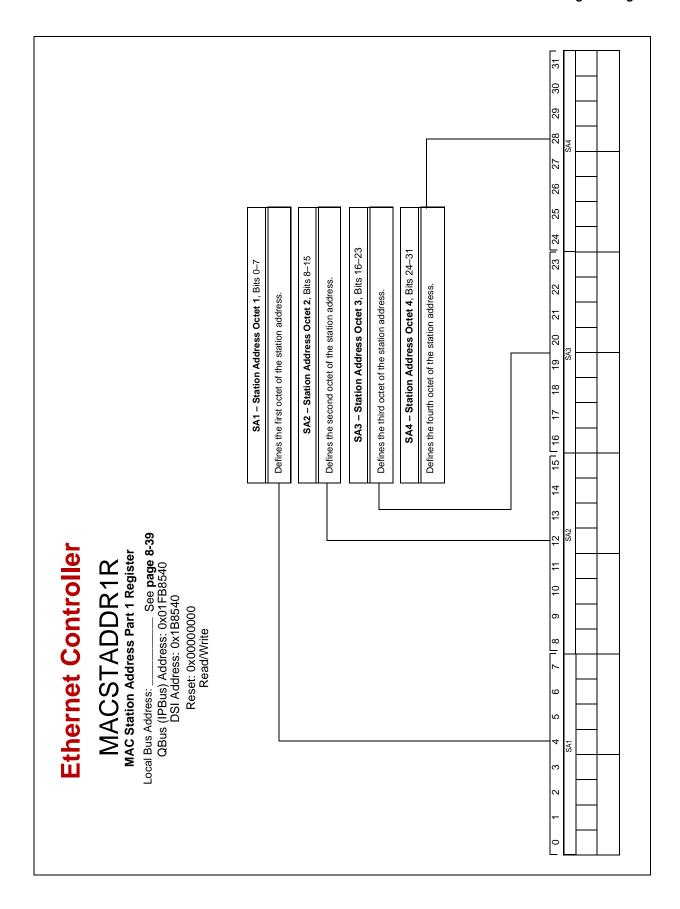

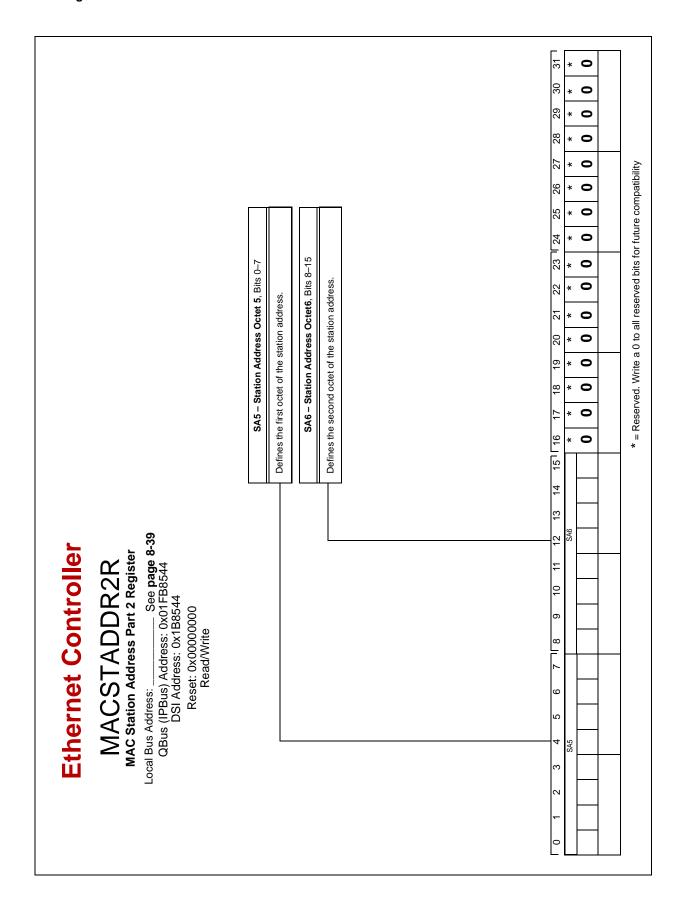

| 25.17.5  | MAC Registers                          |

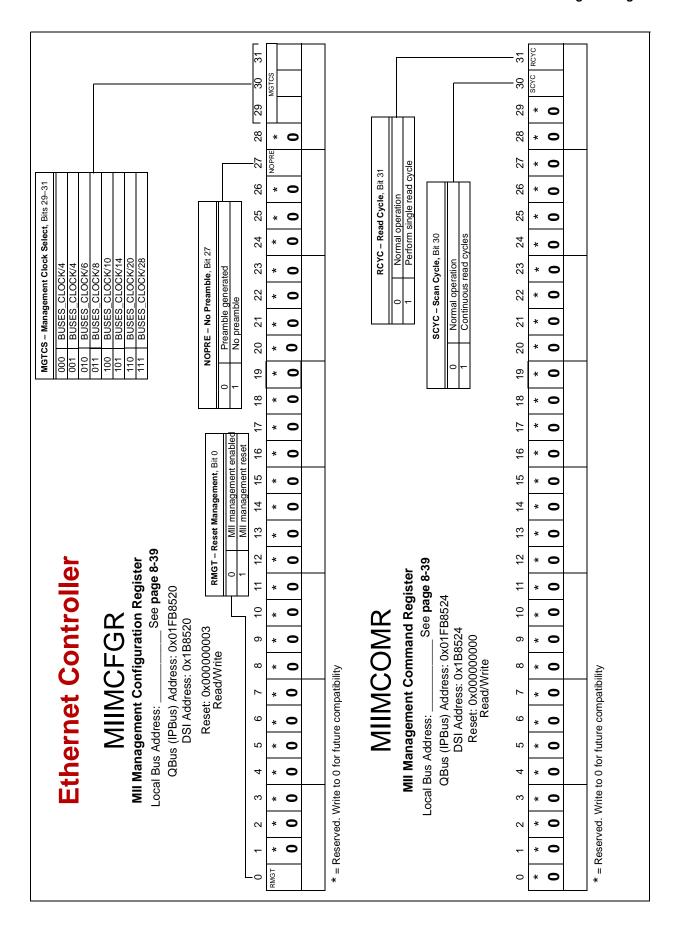

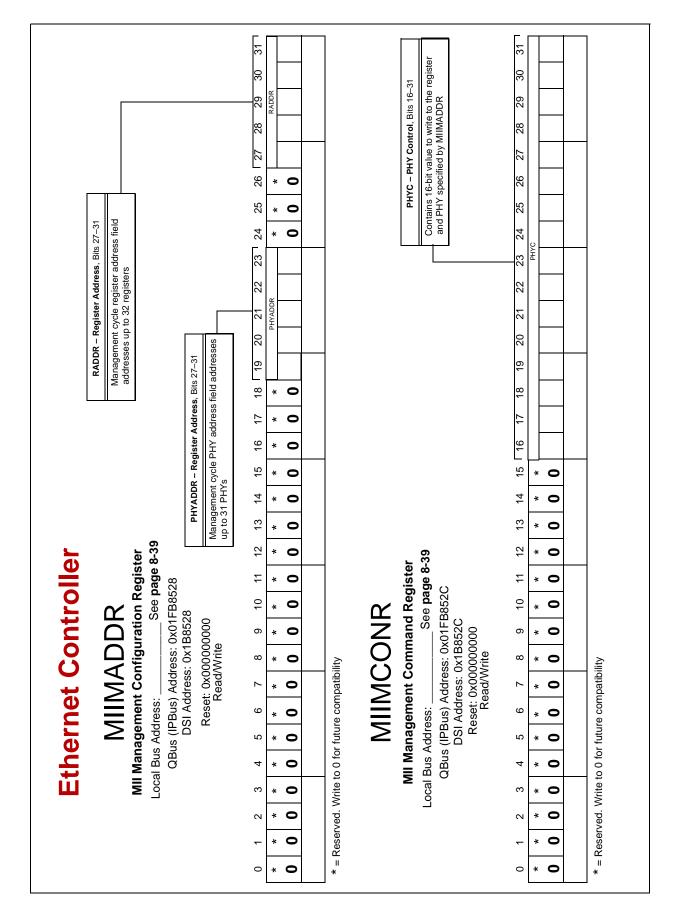

| 25.17.6  | MII Management Registers               |

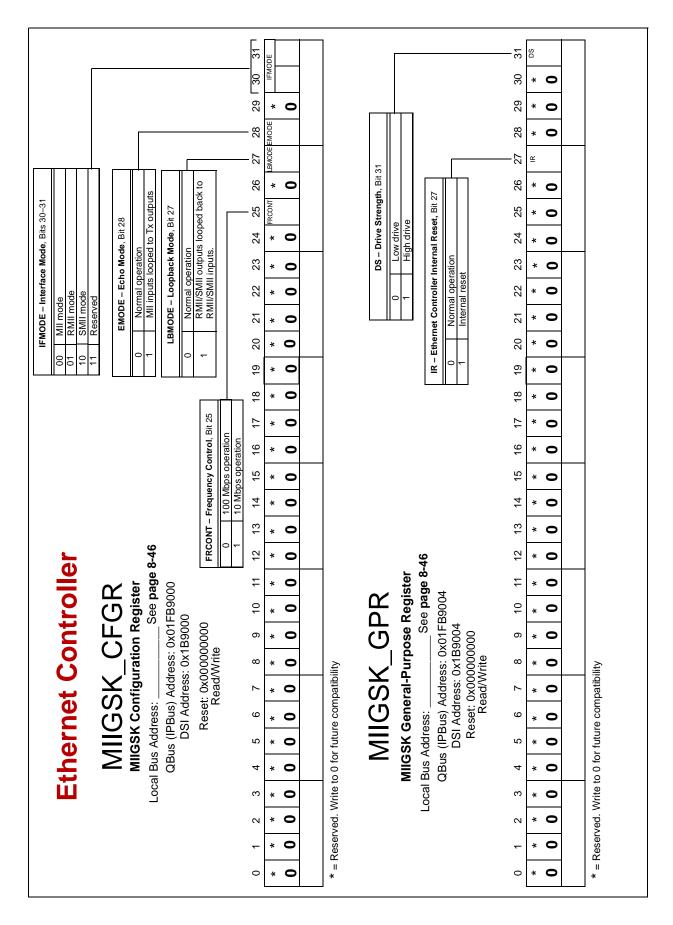

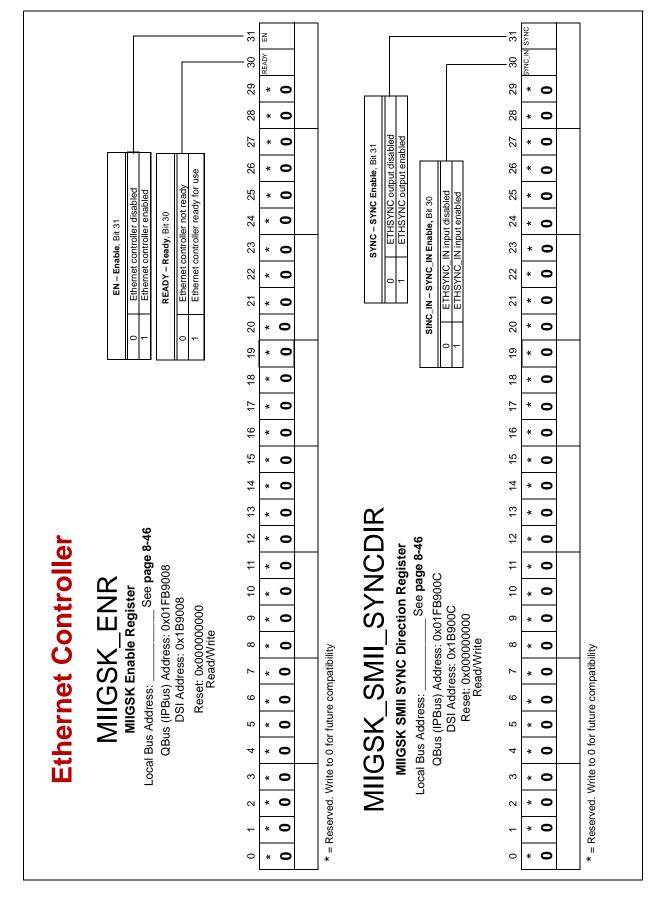

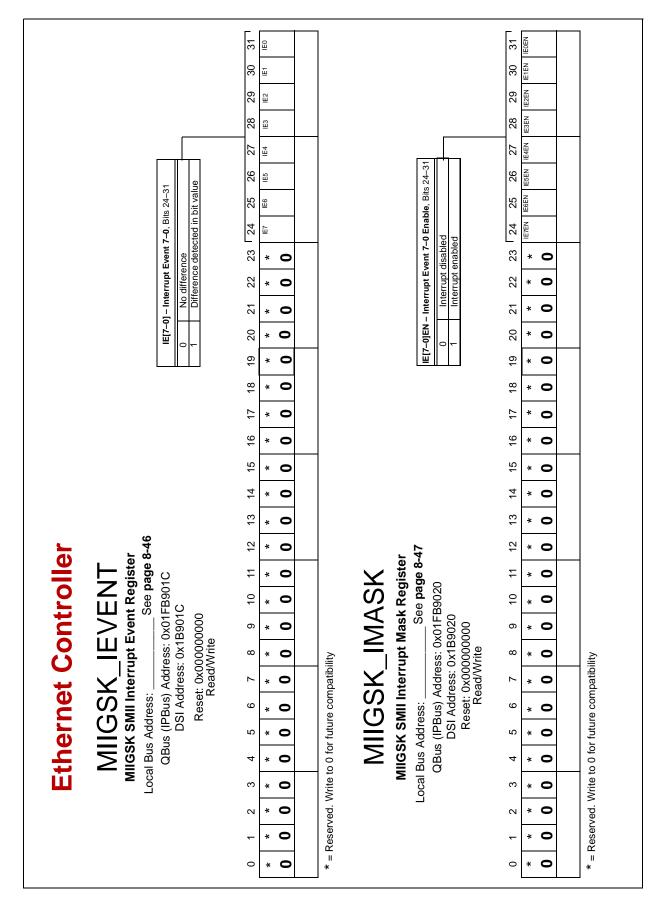

| 25.17.7  | MIIGSK Registers                       |

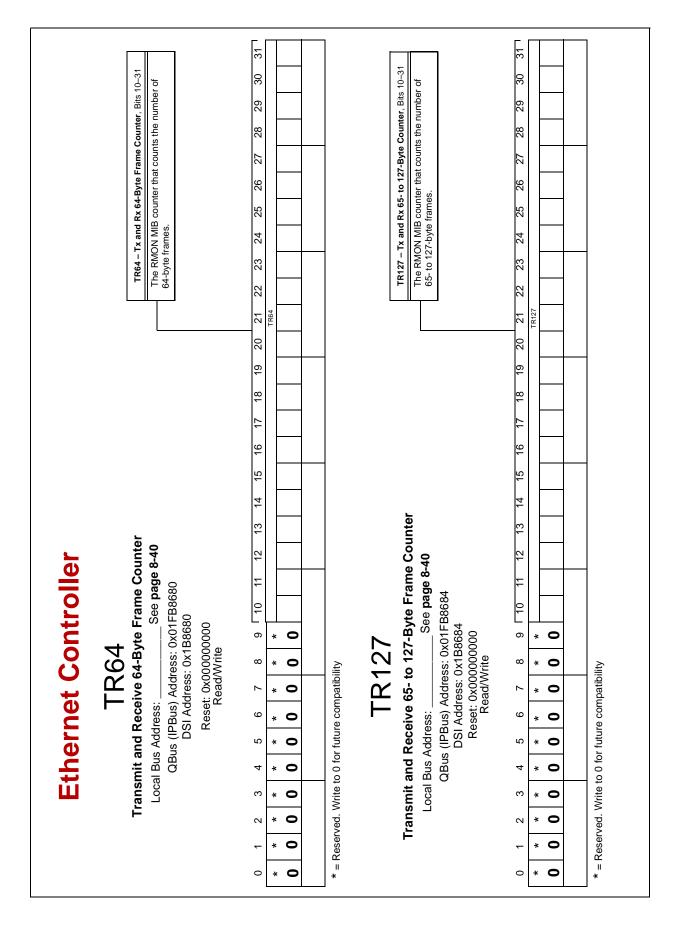

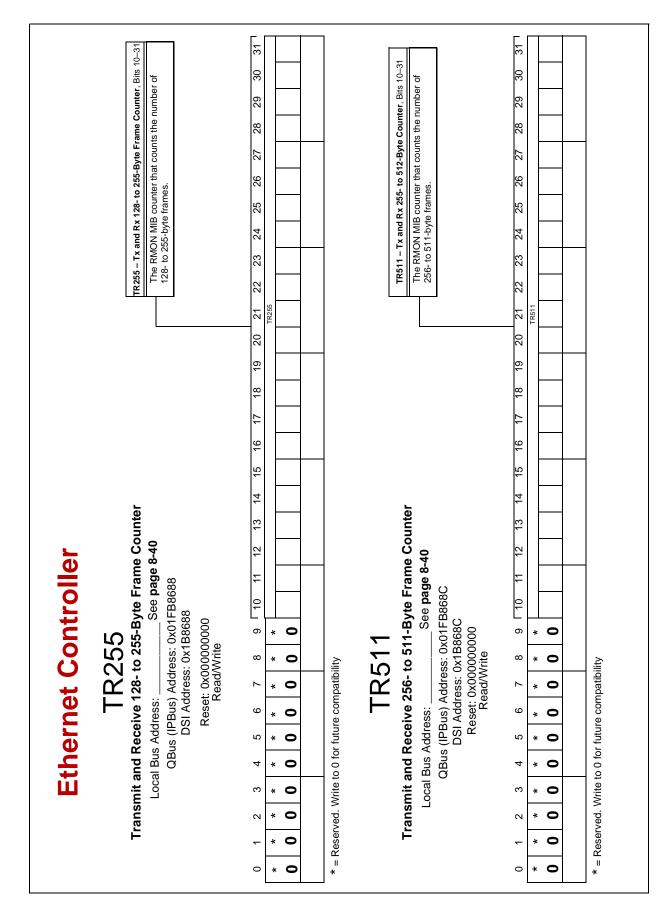

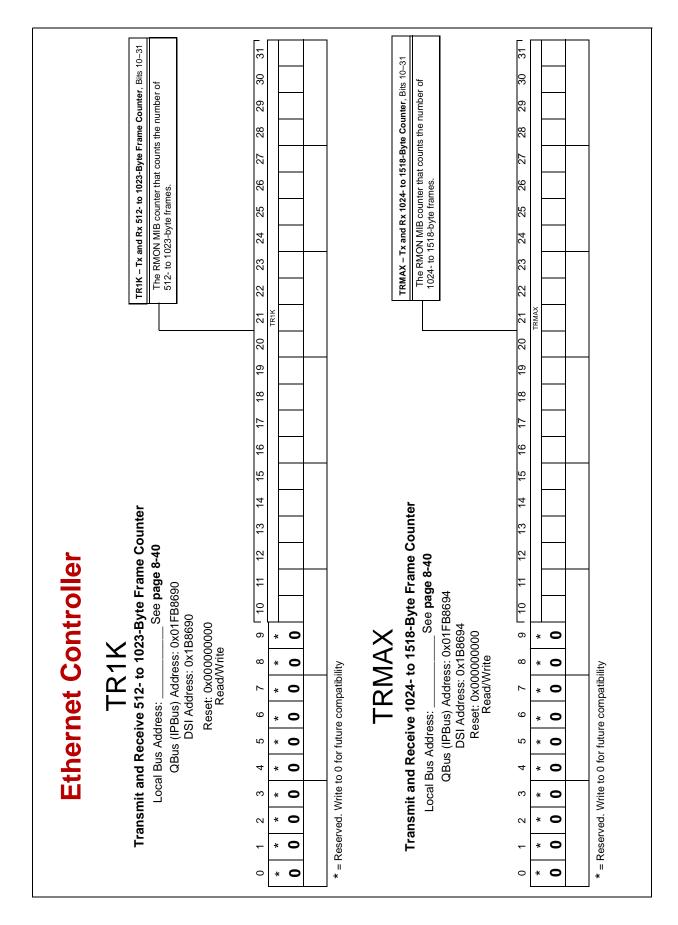

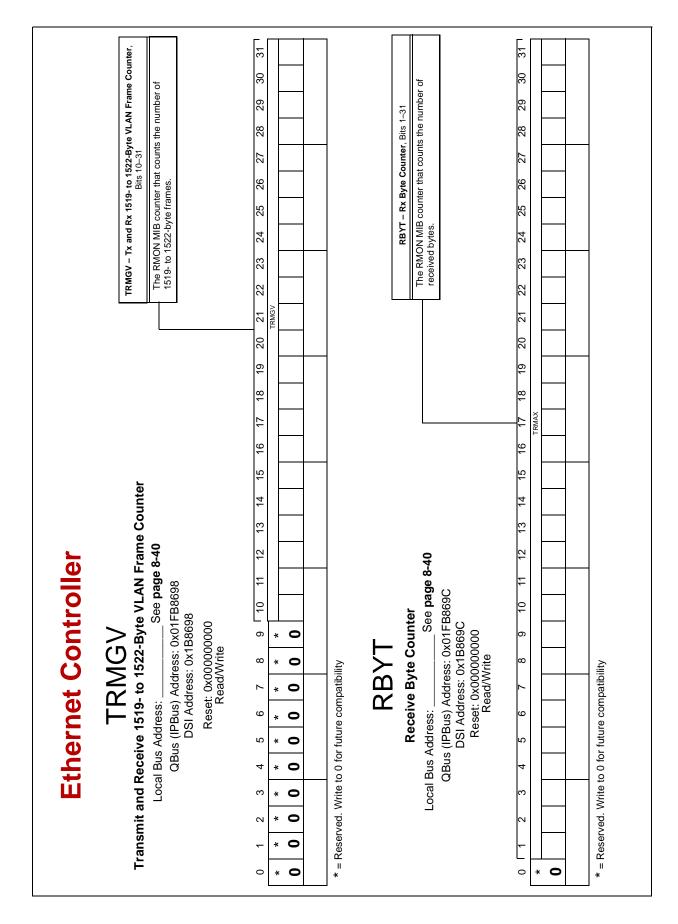

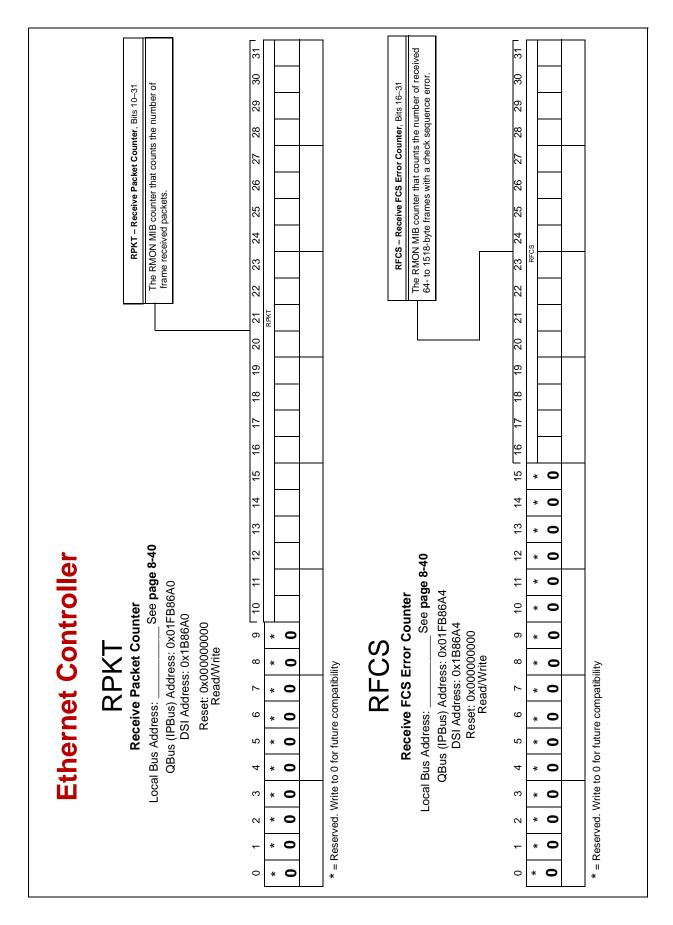

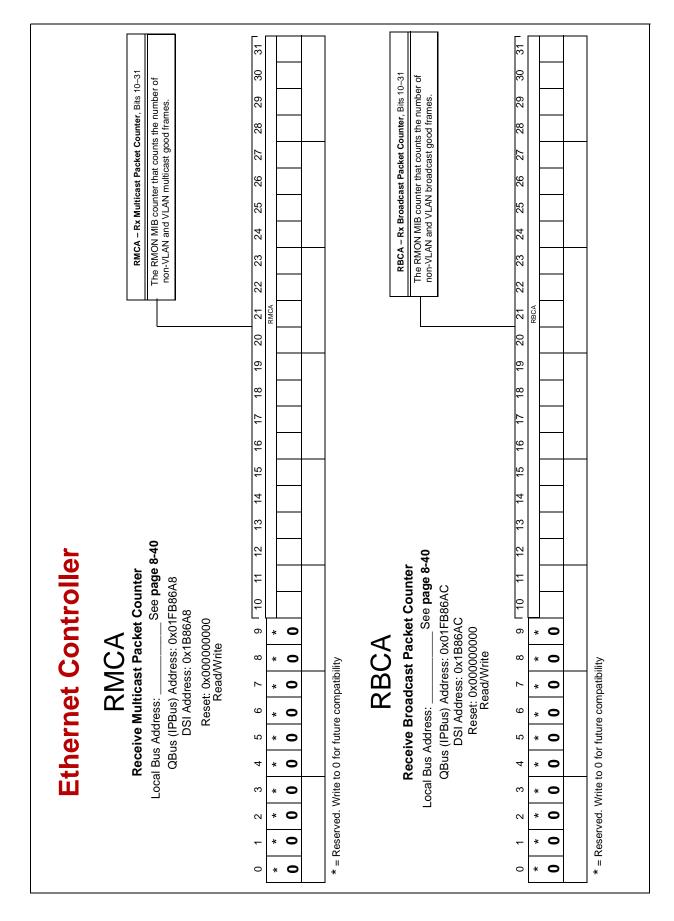

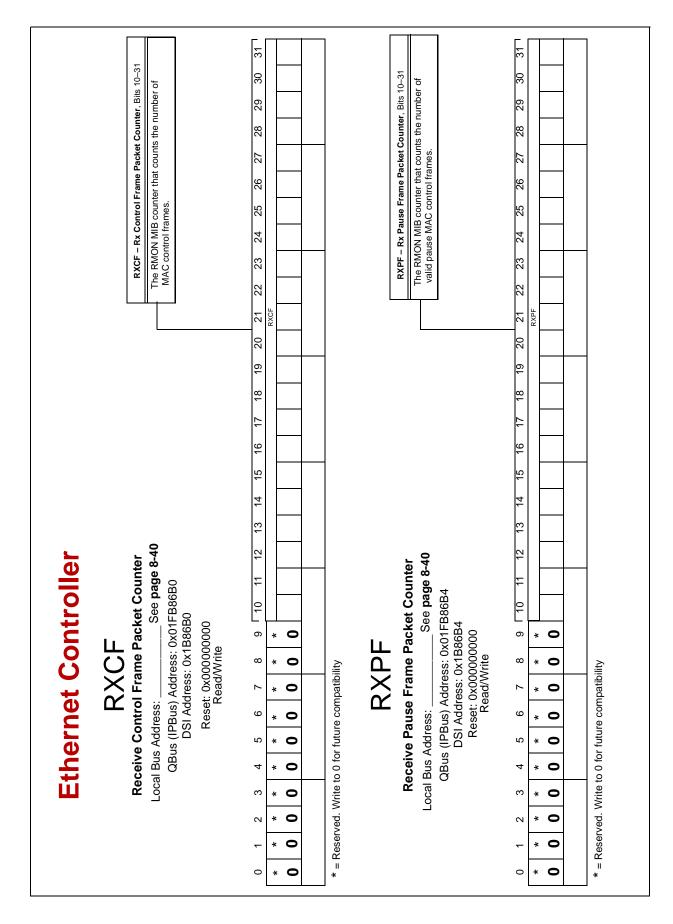

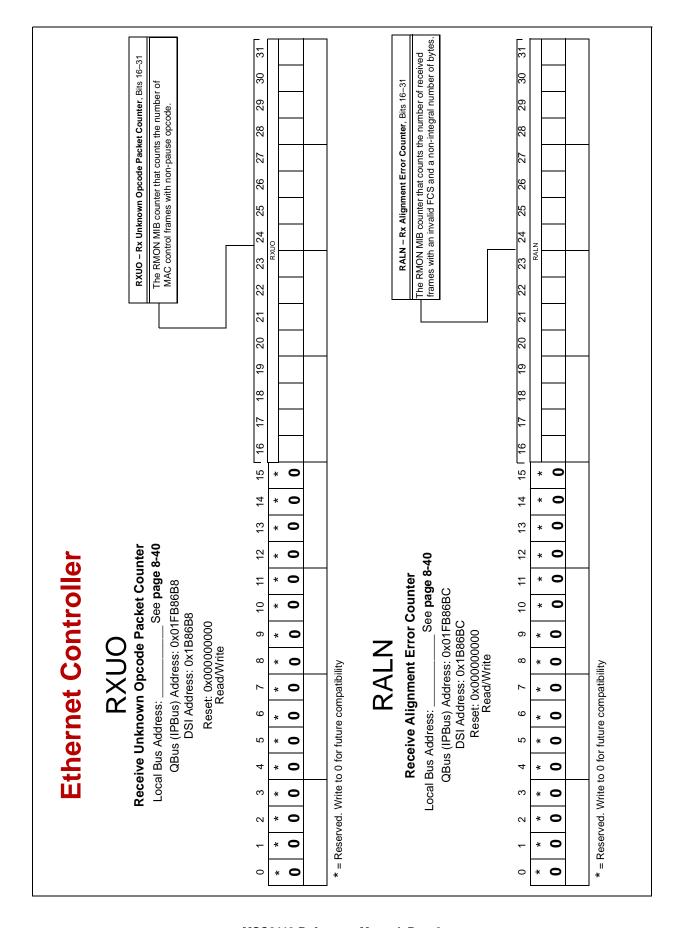

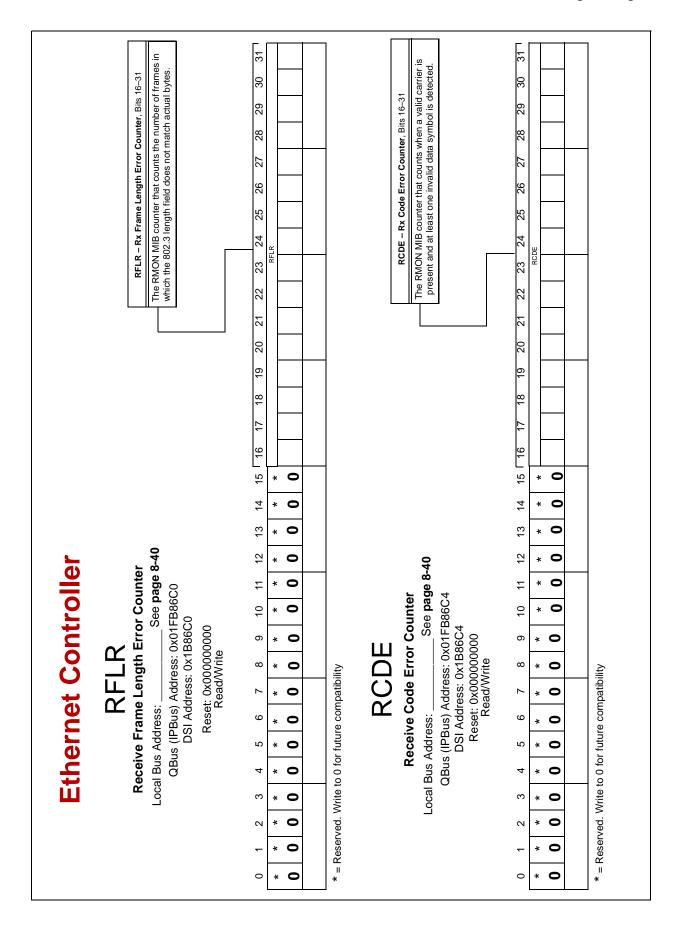

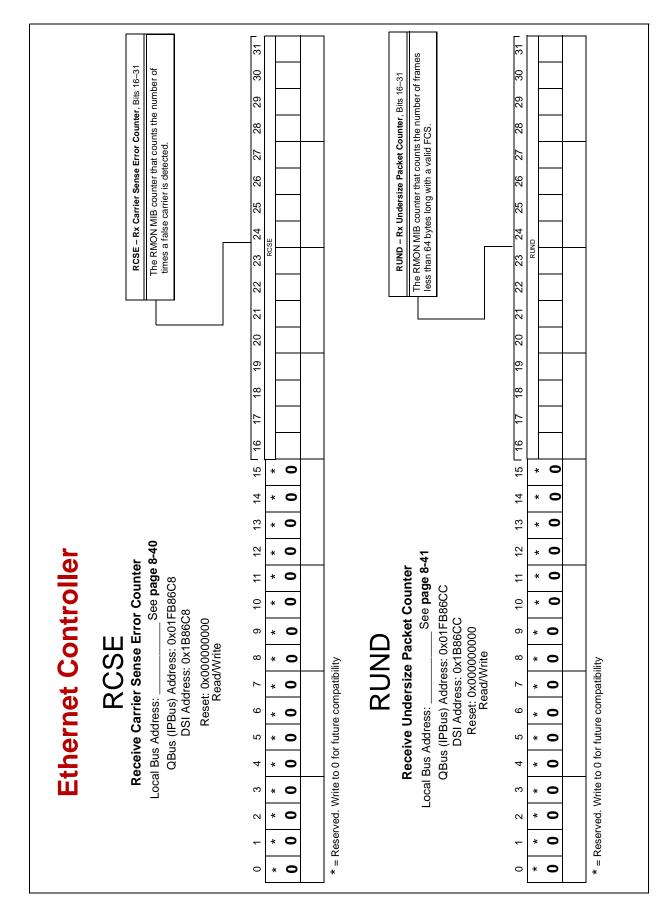

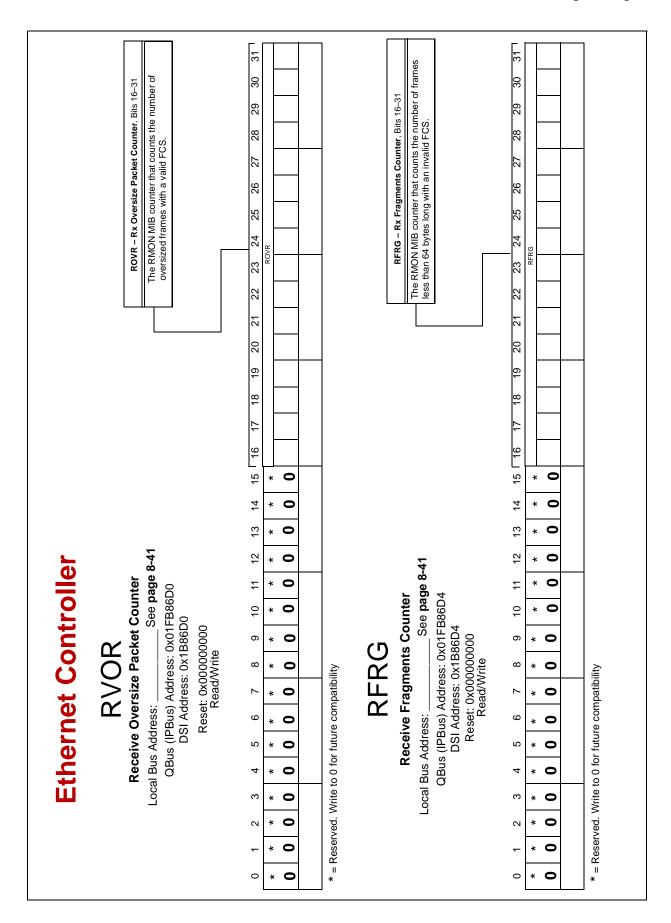

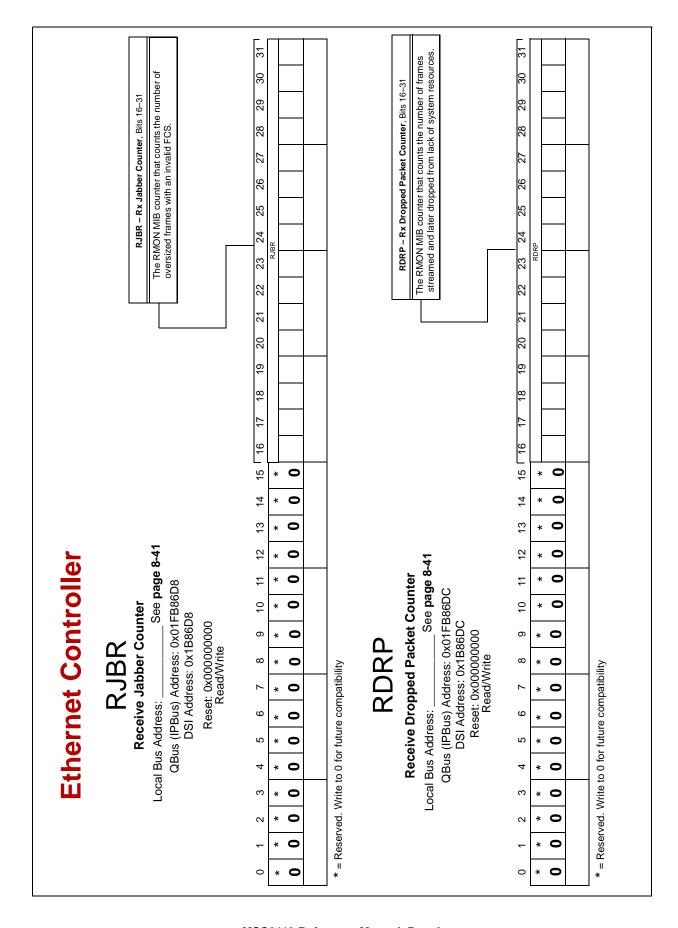

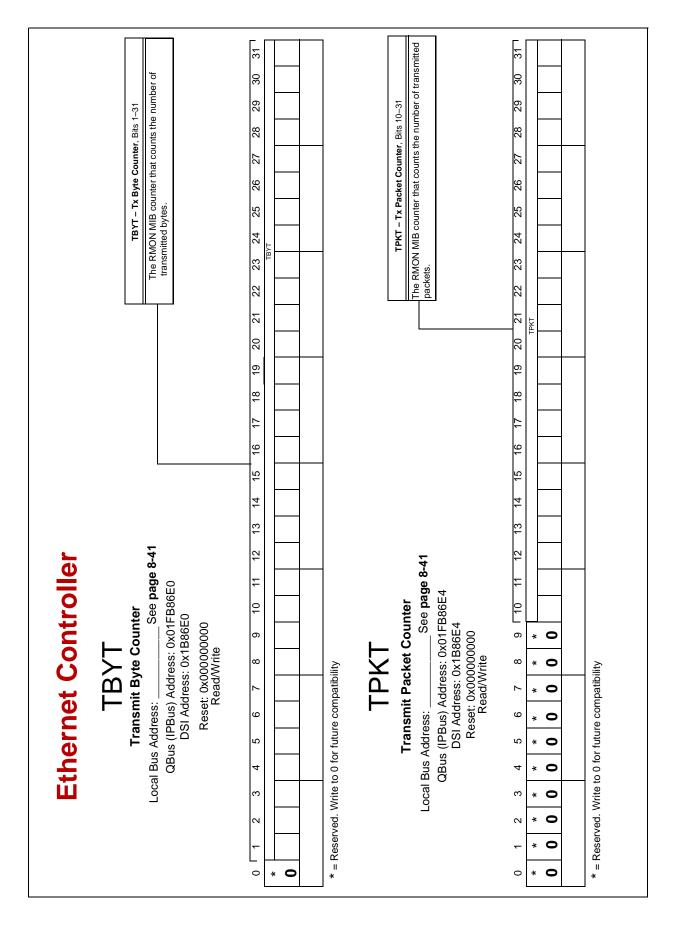

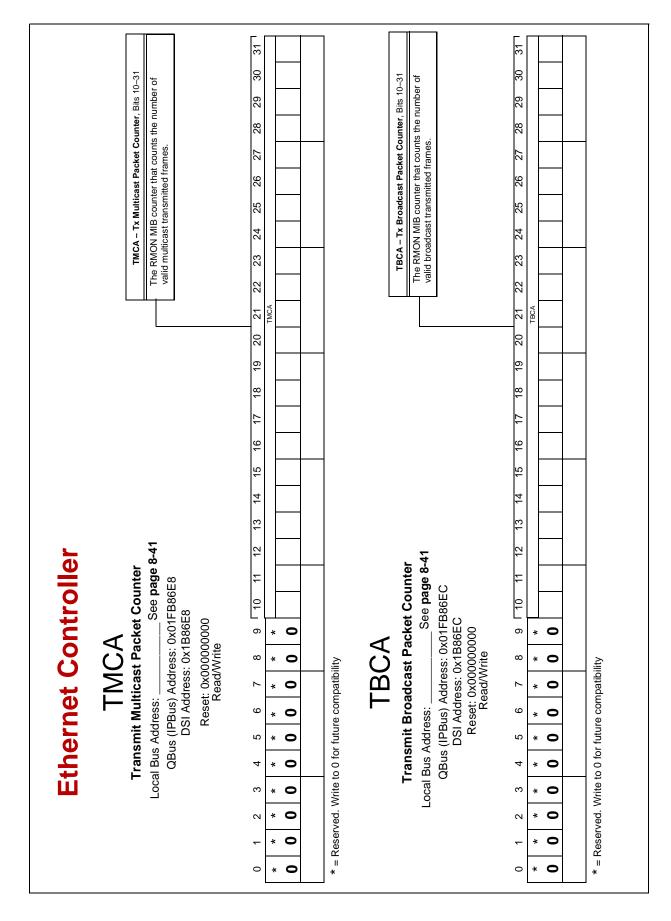

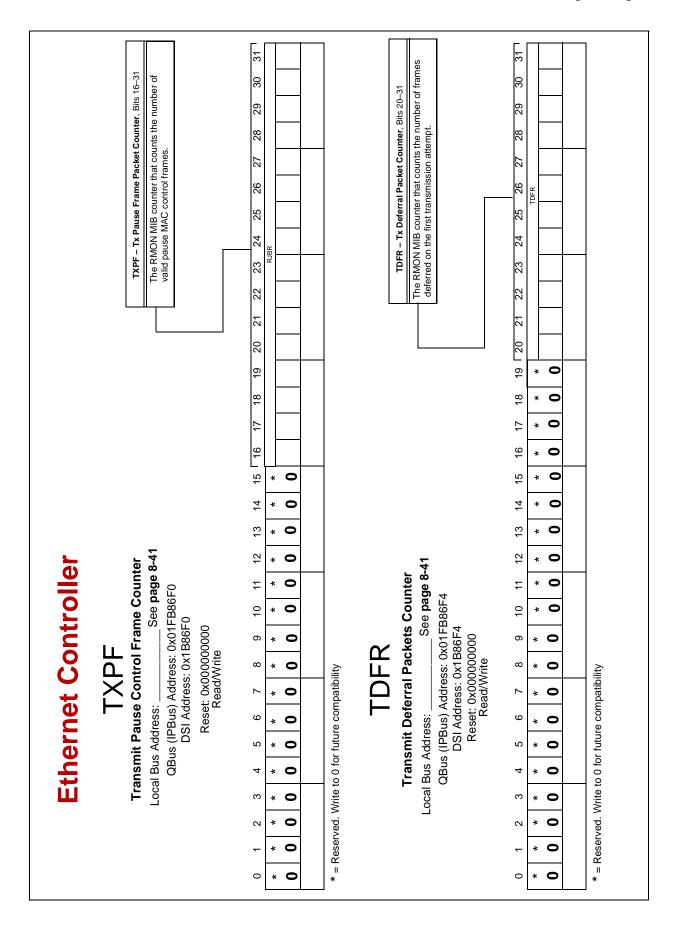

| 25.17.8  | RMON Management Information Base (MIB) |

| 25.17.9  | Hash Function Registers                |

| 25.17.10 | Pattern Matching Registers             |

| 25.17.11 | Data Structures (Buffer Descriptors)   |

| Α        | Programming Reference                  |

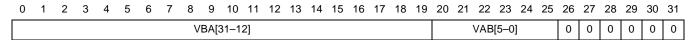

| A.1      | Register Addressing                    |

| A.2      | Interrupts                             |

| A.3      | Programming Sheets                     |

| В        | MSC8113 Dictionary                     |

| C        | MSC8113 Boot Code                      |

MSC8113 Reference Manual, Rev. 0

Freescale Semiconductor xix

ents

# **About This Book**

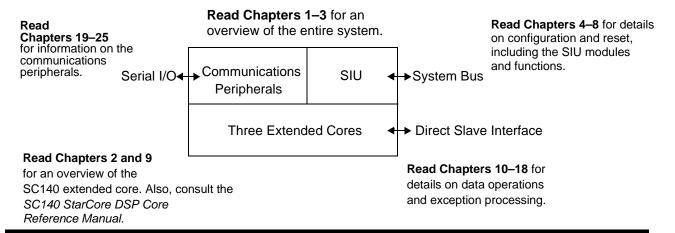

The MSC8113 device is based on the StarCore<sup>®</sup> SC140 DSP core. It addresses the challenges of the networking market. The benefits of the MSC8113 include not only a very high level of performance but also a product design that enables effective software development and integration. Its tool suite provides a full-featured development environment for C/C++ and assembly languages as well as ease of integration with third-party software, such as off-the-shelf libraries and a real-time operating system. The MSC8113 is logically partitioned into three distinct blocks: three extended cores, a system interface unit (SIU), and communications peripherals.

#### **Three Extended Cores**

Each extended core contains an SC140 DSP core with internal memory for data and program storage, peripheral hardware, and two interrupt controllers. Memory includes 224 KB (896 KB total) of zero wait state SRAM and 16 KB (64 KB total) of instruction cache. The MSC8113 also includes 476 KB of shared memory (M2) and 4 KB of boot ROM. Minimum code density is achieved using a 16-bit instruction set that is grouped into execution sets by the compiler (or by the programmer) for high instruction parallelism. The DSI provides a glueless 32/64-bit interface to a host processor for data and command communication. The programmable interrupt controller (PIC) and local interrupt controller (LIC) process all internal interrupt requests, notifying the SC140 DSP cores or external devices of an interrupt event.

#### SIU

Supports internal and external system-related functions. The SIU includes hardware such as a direct memory access (DMA) controller, clocks, and reset configuration registers. It also includes the memory controllers, which interface to external memory devices and/or other devices such as a system host or other DSPs.

# Communications Peripherals

Includes four TDM interfaces with 256 channels each, a UART, thirty-two 16-bit timers, thirty-two programmable GPIO signals, eight hardware semaphore registers, an I<sup>2</sup>C software module, an Ethernet interface, and a global interrupt controller (GIC). The serial interfaces give additional functionality and flexibility. The semaphore registers provide resource control for external hosts. The GIC extends interrupt handling capability.

MSC8113 Reference Manual, Rev. 0

Freescale Semiconductor xxi

### **Before Using This Manual—Important Note**

This manual describes the structure and function of the MSC8113 device. The information in this manual is subject to change without notice, as described in the disclaimers on the title page of this manual. As with any technical documentation, it is your responsibility as the reader to ensure that you are using the most recent version of the documentation. For more information, contact your sales representative.

Before using this manual, determine whether it is the latest revision and whether there are errata or addenda. To locate any published errata or updates associated with this manual or this product, refer to the Freescale web site. The address for the web site is listed on the back cover of this manual.

### **Audience and Helpful Hints**

This manual is intended for software and hardware developers and applications programmers who want to develop products with the MSC8113. It is assumed that you have a working knowledge of DSP technology and that you may be familiar with Freescale products based on the Freescale DSP56000 or DSP56300 core. Familiarity with Freescale DSP products is not necessary.

For your convenience, the chapters of this manual are organized to make the information flow as predictably as possible. When feasible, the information in each chapter follows this general sequence:

- **■** Features

- Architecture

- Signals

- Operation/operating modes

- Programming

- Programming Examples

- Programming Model (registers)

In chapters that include a Programming Model section, this section is the last one in the chapter, or module subsection for those chapters that include multiple modules, and describes all registers for the module discussed. The Programming Model section begins with a bulleted overview of the registers that includes the page number where the description of each register begins.

# **Notational Conventions and Definitions**

This manual uses the following notational conventions:

| mnemonics              | Instruction mnemonics appear in lowercase bold.                                                                                                                                                                                                            |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COMMAND names          | Command names are set in small caps, as follows: GRACEFUL STOP TRANSMIT or ENTER HUNT MODE.                                                                                                                                                                |

| italics                | Book titles in text are set in italics, as are cross-referenced section titles. Also, italics are used for emphasis and to highlight the main items in bulleted lists.                                                                                     |

| 0x                     | Prefix to denote a hexadecimal number.                                                                                                                                                                                                                     |

| 0b                     | Prefix to denote a binary number.                                                                                                                                                                                                                          |

| REG[FIELD]             | Abbreviations or acronyms for registers or buffer descriptors appear in uppercase text. Specific bits, fields, or numeric ranges appear in brackets. For example, ICR[INIT] refers to the Force Initialization bit in the host Interface Control Register. |

| ACTIVE HIGH<br>SIGNALS | Names of active high signals appear in sans serif capital letters, as follows: TT[04], TSIZ[0–3], and DP[0–7].                                                                                                                                             |

| ACTIVE LOW<br>SIGNALS  | Signal names of active low signals appear in sans serif capital letters with an overbar, as follows: DBG, AACK, and EXT_BG[2].                                                                                                                             |

| x                      | A lowercase italicized x in a register or signal name indicates that there are multiple registers or signals with this name. For example, BRCGx refers to BRCG[1–8], and MxMR refers to the MAMR/MBMR/MCMR registers.                                      |

On the MSC8113 device, the SC140 cores are 16-bit DSP processors. The following table shows the SC140 assembly language data types. For details, see the *StarCore SC140 DSP Core Reference Manual (MNSC140CORE/D)*.

| Name                   | SC140   |

|------------------------|---------|

| Byte/Octet             | 8 bits  |

| Half Word              | 8 bits  |

| Word                   | 16 bits |

| Long/Long Word/2 Words | 32 bits |

| Quad Word/4 Words      | 64 bits |

The following table lists the SC140 C language data types recognized by the StarCore C compiler. For details, see the *StarCore SC100 C Compiler User's Manual (MNSC100CC/D)*.

| Name                 | Size    |

|----------------------|---------|

| char/unsigned char   | 8 bits  |

| short/unsigned short | 16 bits |

| int/unsigned int     | 16 bits |

MSC8113 Reference Manual, Rev. 0

Freescale Semiconductor xxiii

| Name               | Size    |

|--------------------|---------|

| fractional short   | 16 bits |

| long/unsigned long | 32 bits |

| fractional long    | 32 bits |

| pointer            | 32 bits |

### **Conventions for Registers**

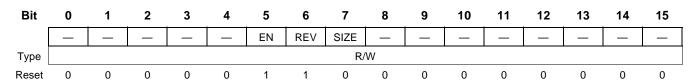

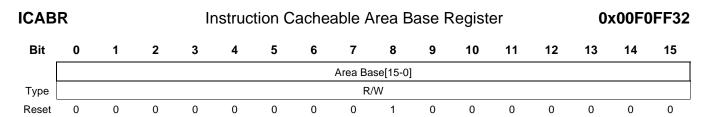

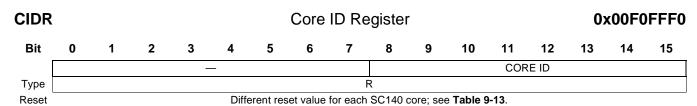

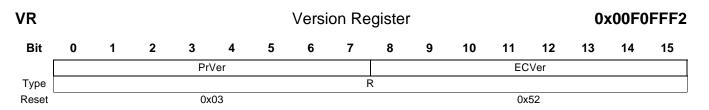

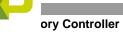

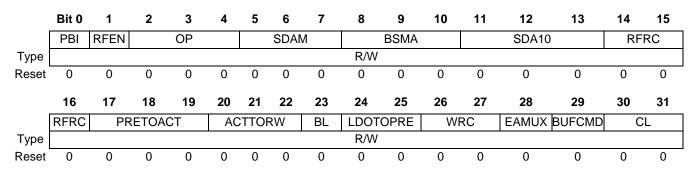

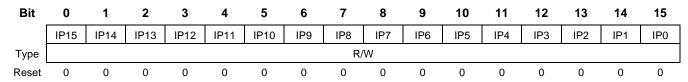

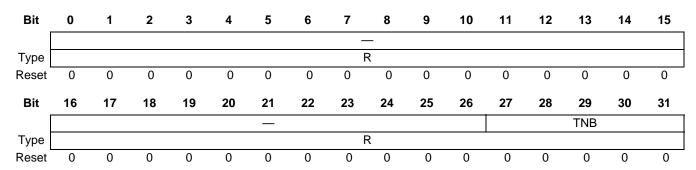

The Programming Model section of each chapter includes a register bit table for each register in that module, as well as a table describing each bit in the register. The register bit table not only shows the names and positions of the bits/bit fields but also their reset value, value after boot, and their type (Read/Write). For registers that are not changed by the system boot, no boot line is listed. The register address is shown with the register name and mnemonic. Reserved bits/fields are indicated with a long dash (—). In the PPC\_ALRH shown below, all of the bits are read/write (R/W). Other registers may include read-only (R) and write-only (W) bits. Notice that the most significant bit (MSB) is 0, or little-endian order.

| PPC_  | ALR | H        |         |    | Syste | em Bu    | ıs Arb  | itratio | n-Lev | el Re    | gister  |    |    |          |         |    |

|-------|-----|----------|---------|----|-------|----------|---------|---------|-------|----------|---------|----|----|----------|---------|----|

| Bit   | 0   | 1        | 2       | 3  | 4     | 5        | 6       | 7       | 8     | 9        | 10      | 11 | 12 | 13       | 14      | 15 |

|       |     | Priority | Field 0 |    |       | Priority | Field 1 |         |       | Priority | Field 2 |    |    | Priority | Field 3 |    |

| Туре  |     |          |         |    |       |          |         | R       | W     |          |         |    |    |          |         |    |

| Reset | 0   | 0        | 0       | 0  | 0     | 0        | 0       | 1       | 0     | 0        | 1       | 0  | 0  | 1        | 1       | 0  |

| Boot  | 1   | 1        | 0       | 1  | 1     | 0        | 1       | 0       | 0     | 1        | 0       | 1  | 0  | 1        | 0       | 0  |

| Bit   | 16  | 17       | 18      | 19 | 20    | 21       | 22      | 23      | 24    | 25       | 26      | 27 | 28 | 29       | 30      | 31 |

|       |     | Priority | Field 4 |    |       | Priority | Field 5 |         |       | Priority | Field 6 |    |    | Priority | Field 7 |    |

| Туре  |     |          |         |    |       |          |         | R       | W     |          |         |    |    |          |         |    |

| Reset | 0   | 0        | 1       | 1  | 0     | 1        | 0       | 0       | 0     | 1        | 0       | 1  | 0  | 1        | 1       | 1  |

| Boot  | 0   | 1        | 1       | 1  | 1     | 0        | 0       | 0       | 1     | 0        | 0       | 1  | 1  | 1        | 1       | 0  |

### **Organization**

Following is a summary and a brief description of the chapters of this manual:

- Chapter 1, MSC8113 Overview. Features, descriptive overview of main modules, configurations, and application examples.

- Chapter 2, SC140 Core Overview. Target markets, features, overview of development tools, descriptive overview of main modules.

- Chapter 3, External Signals. Identifies the external signals, lists signal groupings, including the number of signal connections in each group, and describes each signal within a functional group.

- Chapter 4, *System Interface Unit (SIU)*. Describes the modules and functions of the SIU, which controls system start-up and initialization as well as operation, protection, and the external 60x-compatible system bus.

- Chapter 5, *Reset*. Covers reset sources, causes, and configurations; gives examples of different reset configuration scenarios, including systems with multiple MSC8113s.

- Chapter 6, *Boot Program*. Describes the bootloader program, which loads and executes source code that initializes the MSC8113 after it completes a reset sequence and programs its registers for the required mode of operation. This chapter covers selection of bootloader modes, normal sequence of events for bootloading a source program, and booting in a multi-processor environment.

- Chapter 7, *Clocks*. Contains an overview of the MSC8113 clock module. For complete clock information, refer to the *MSC8113 Technical Data* sheet. The data sheet is available in PDF format on the Freescale web site listed on the back cover of this manual.

- Chapter 8, *Memory Map*. Defines the address spaces for all MSC8113 modules; includes cross references to all registers discussed.

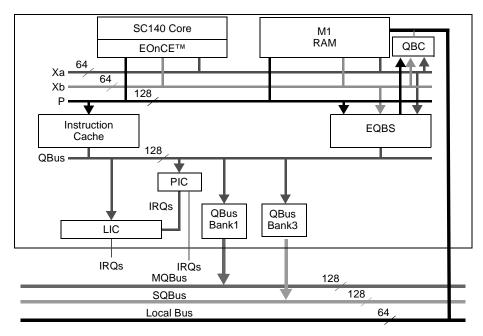

- Chapter 9, *Extended Core*. Describes the structure of the extended core, which includes the SC140 core, its internal memory (M1), the extended QBus structure (EQBS), the Instruction Cache (ICache), the programmable interrupt controller (PIC), and the local interrupt controller (LIC).

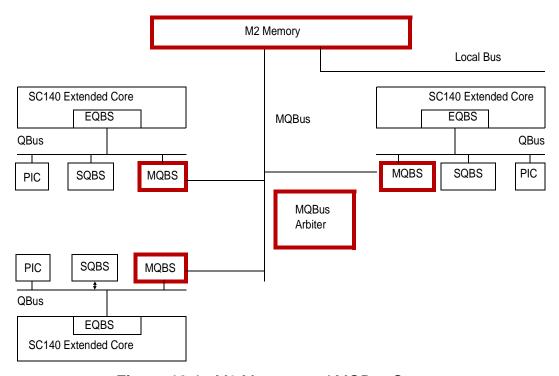

- Chapter 10, *MQBus and M2 Memory*. Describes how the MQBus supports a multi-core environment by allowing all three SC140 cores to share the M2 memory through the MQBus. The MQBus ensures a low miss ratio for SC140 ICache accesses.

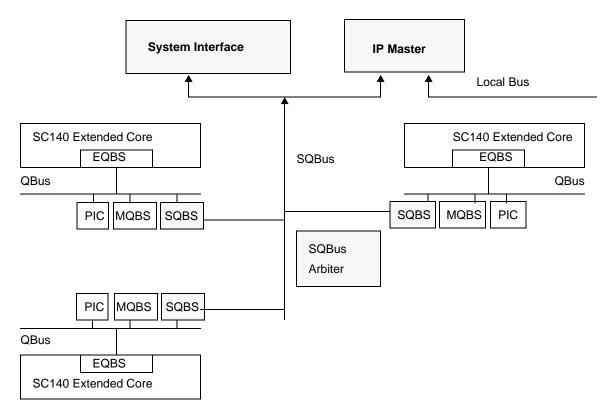

- Chapter 11, *SQBus*. Explains the structure and function of the SQBus, which is available to all SC140 cores to fetch program code from external memory on the system bus.

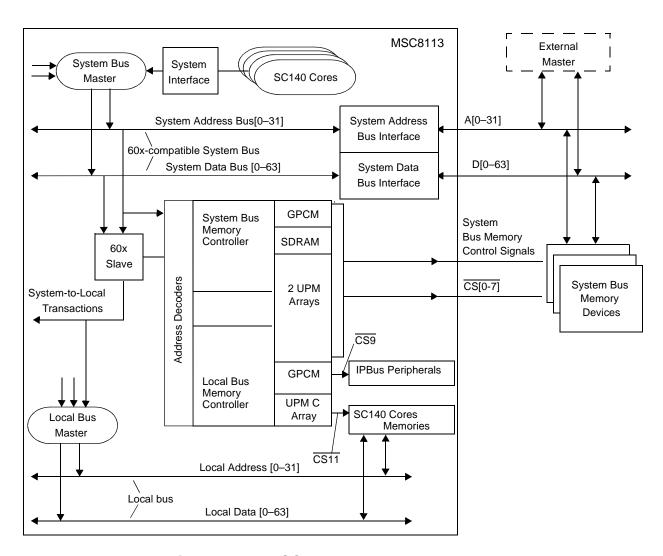

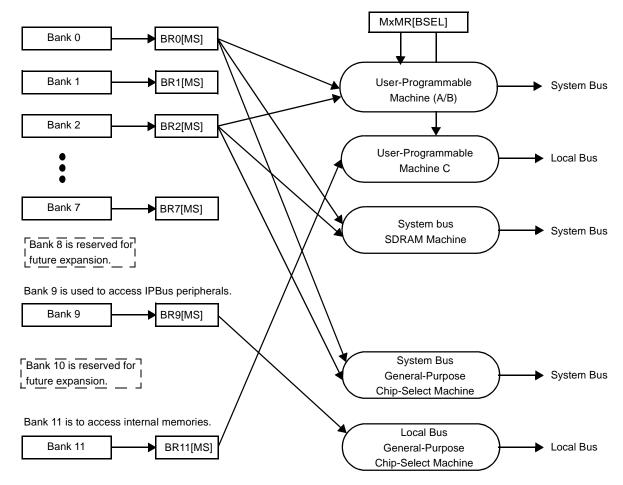

- Chapter 12, *Memory Controller*. Covers the features and basic architecture of the memory controller, which is part of the system interface unit (SIU). The memory controller provides an interface to internal DSP memory and DSP peripherals residing on the internal local bus and also to external memory and peripheral devices on the external 60x-compatible system bus. In addition to features and basic architecture, this chapter extensively covers the three basic machines that compose the memory controller: synchronous DRAM machine (SDRAM), general-purpose chip-select machine (GPCM), and the user-programmable machines (UPMs).

- Chapter 13, *System Bus*. Discusses the system bus, which is a 60x-compatible bus that provides flexible support for the on-chip SC140 cores as well as other internal and external 60x-compatible bus masters.

- Chapter 14, *Direct Slave Interface (DSI)*. Discusses the DSI host interface, which is a 32/64-bit wide, full-duplex, double-buffered, parallel port that can directly connect to the data bus of a host processor. The DSI supports a variety of buses and provides glueless connection with a number of industry-standard microcomputers, microprocessors, and DSPs.

Freescale Semiconductor xxv

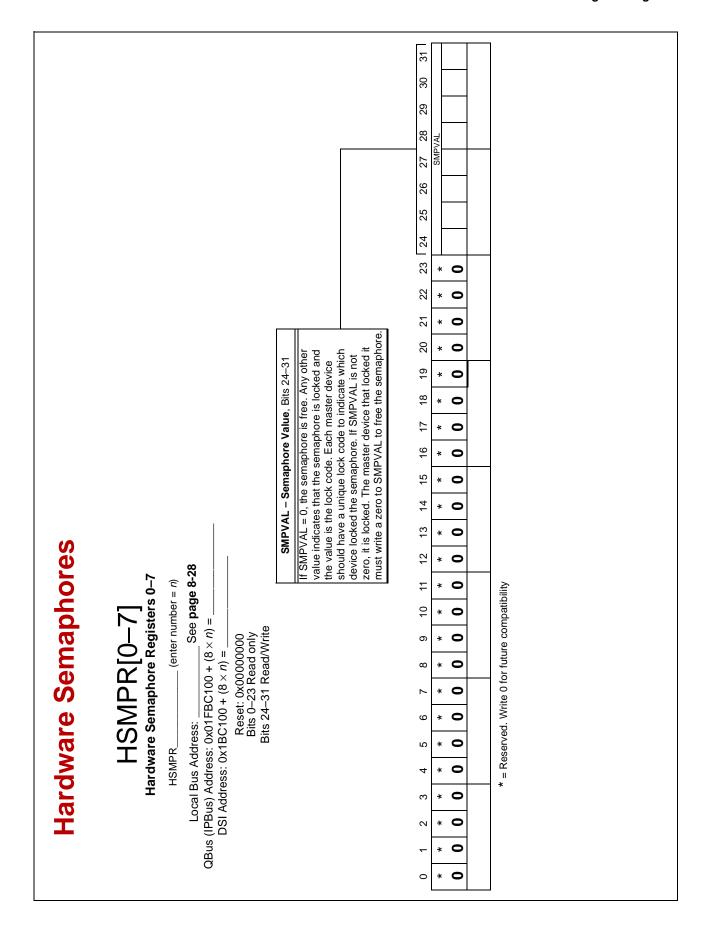

- Chapter 15, *Hardware Semaphores*. Describes the function and programming of the hardware semaphores, which control resource sharing.

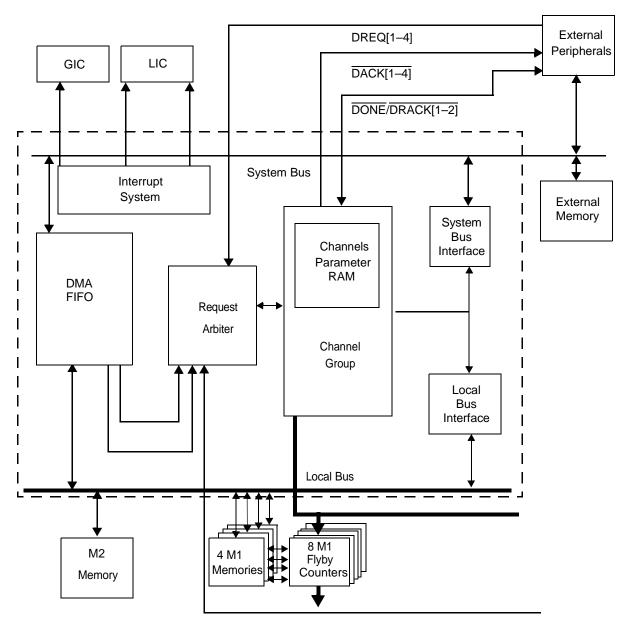

- Chapter 16, *Direct Memory Access (DMA) Controller*. Describes the different DMA operating modes, transfer types, and buffer types. The chapter also gives procedures for programming different types of transfers. The multi-channel DMA controller includes hardware support for up to 16 time-multiplexed channels including buffer alignment, connects to both the system bus and the local bus, and functions as a bridge between both buses. The DMA controller supports flyby transactions on either bus. and enables hot swaps between channels, by using time-multiplexed channels that impose no cost in clock cycles.

- Chapter 17, *Interrupt Processing*. Discusses the three interrupt controllers that provide maximum flexibility in handling MSC8113 interrupts, enabling interrupts to be handled by the SC140 core internally, by an external host, or by a combination of the two; also discusses source priority schemes.

- Chapter 18, *Debugging*. Includes aspects of the JTAG implementation that are specific to the SC140 and should be used with the supporting IEEE® Std. 1149.1<sup>TM</sup> documentation. The discussion covers the items that the standard requires to be defined and provides additional information specific to the MSC8113 implementation.

- Chapter 19, *Internal Peripheral Bus (IPBus)*. Describes the internal peripheral buss (IPBus), the devices that connect to it, energy management capabilities for devices on the bus (Stop modes), and the programming model.

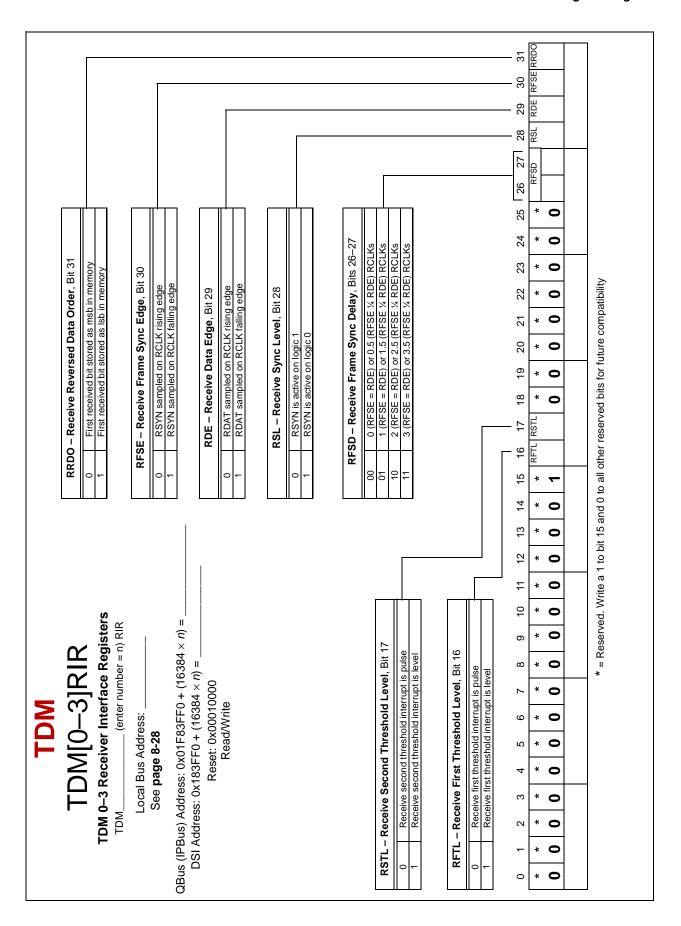

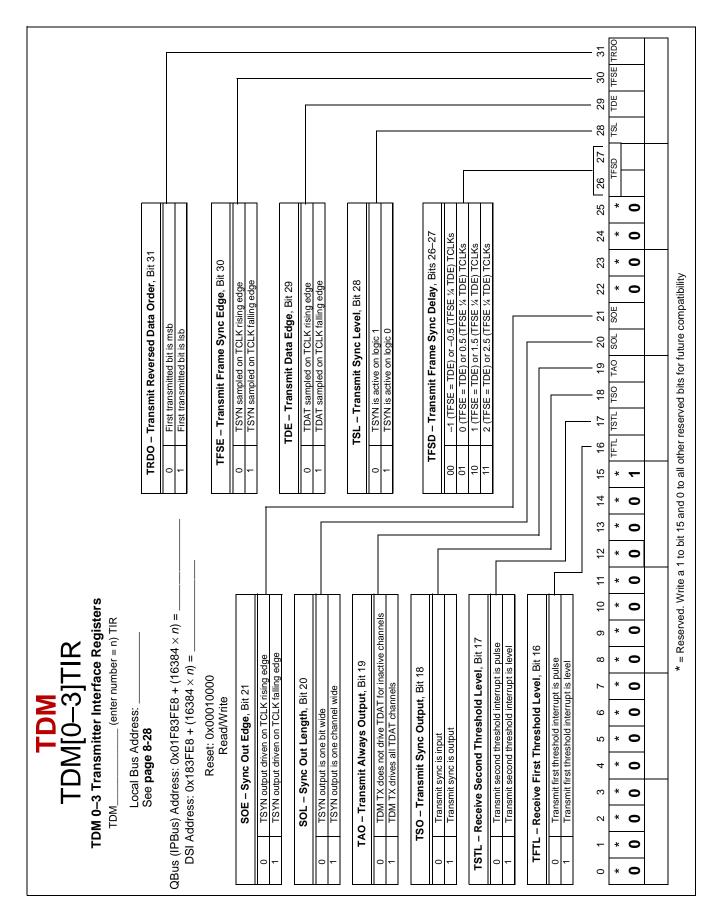

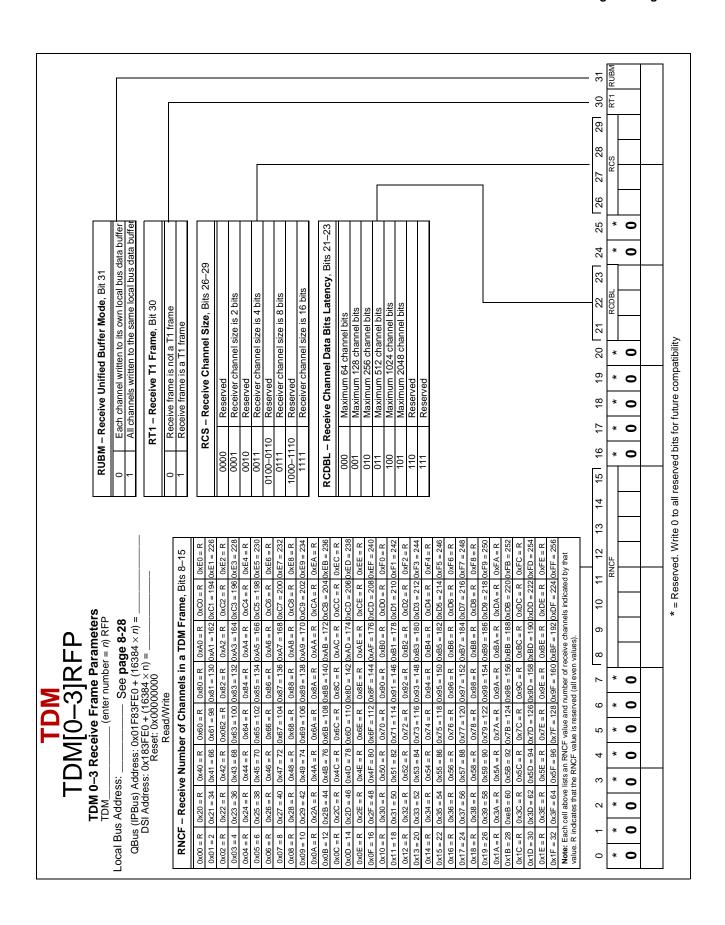

- Chapter 20, TDM Interface. Describes the four TDM interfaces. Each can handle up to 256 channels. The interfaces support the serial bus rate and format for most standard TDM buses, including T1 and E1 highways, pulse-code modulation (PCM) highway, and the ISDN buses in both basic and primary rates.

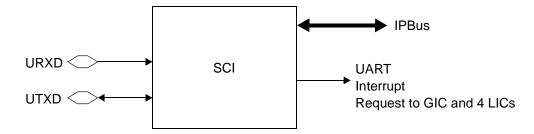

- **Chapter 21,** *UART*. Describes the UART interface, which is a full-duplex serial port used to communicate with other devices.

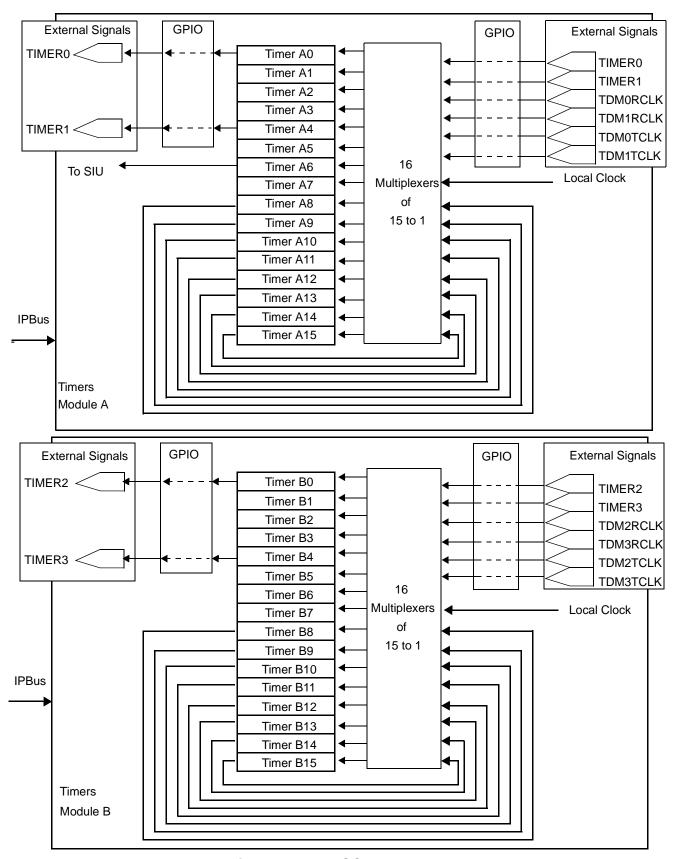

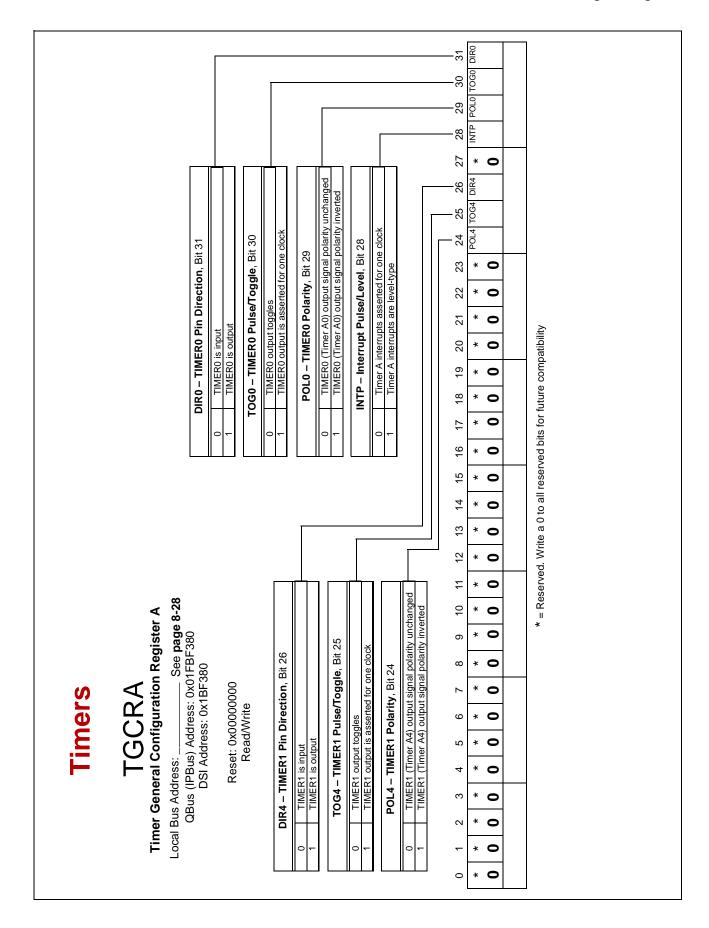

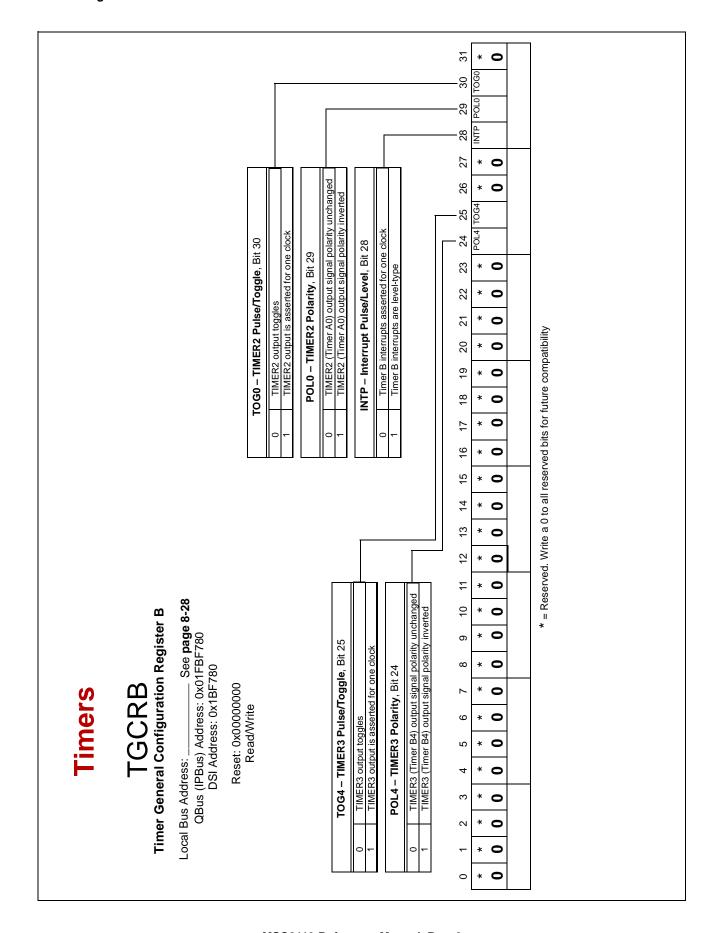

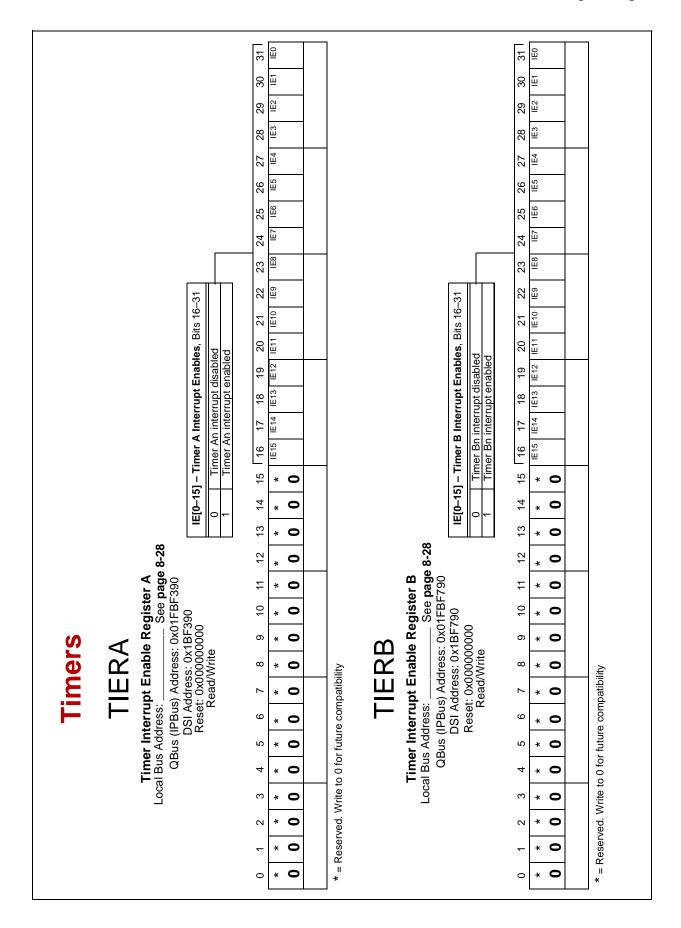

- Chapter 22, *Timers* Discusses the 32 identical 16-bit general-purpose timers residing in two timer modules (A and B) that each have their set of configuration registers.

- Chapter 23, *GPIO*. Discusses the thirty-two GPIO signals. Each pin is multiplexed with a TDM, UART, or timer signal and can be configured as an input or output or a dedicated peripheral pin. Part of the pins can be configured as open-drain (that is, the pin can be configured in a wired-OR configuration on the board). The pin drives a zero voltage but tri-states when driving a high voltage.

- Chapter 24, *I*<sup>2</sup>*C Software Module*. Describes the I<sup>2</sup>C interface. which allows the MSC8113 to boot from a serial EEPROM device.

- Chapter 25, *Ethernet Controller*. Discusses the Ethernet controller, which supports three modes of operation: MII, RMII, and SMII.

xxvi Freescale Semiconductor

#### **■** Appendixes:

- Appendix A, Programming Reference.

- Appendix B, MSC8113 Dictionary.

- Appendix C, MSC8113 Boot Code.

#### Other MSC8113 Documentation

You can find the following documents on the Freescale Semiconductor web site listed on the back cover of this manual.

- *MSC8113 Technical Data sheet (MSC8113)*. Details the signals, AC/DC characteristics, PLL/DLL performance issues, clock configuration and signal characteristics, package and pinout, and electrical design considerations of the MSC8113 device.

- *Application Notes*. Cover various programming topics related to the StarCore DSP core and the MSC8113 device.

# **Further Reading**

■ *StarCore SC140 DSP Core Reference Manual*. Covers the SC140 core architecture, control registers, phase lock loop (PLL), clock registers, hardware debug capabilities (EOnCE), program control, and instruction set.

# **MSC8113 Overview**

1

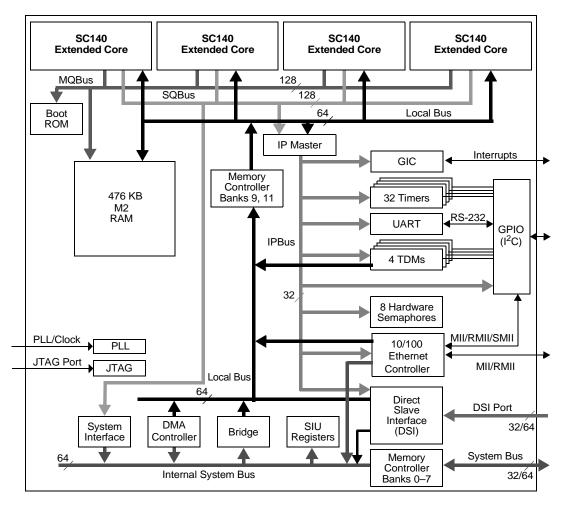

The MSC8113 device is a highly integrated DSP that combines three StarCore SC140 cores with large internal memory spaces, an extended core, and several industry-standard peripherals and external interfaces to target highly computational DSP network and communication applications. The device is optimized for high-bandwidth wireless transcoding and a high-density packet telephony DSP farm, as well as high-bandwidth base station applications. The MSC8113 delivers enhanced performance while maintaining low power dissipation and greatly reducing overall system cost.

Each SC140 core has four ALUs that provide performance of up to 1600 DSP million multiply and accumulate commands per second (MMACS) using an internal 400 MHz clock. The MSC8113 three-core device therefore delivers a total performance of up to 4800 DSP MMACS.

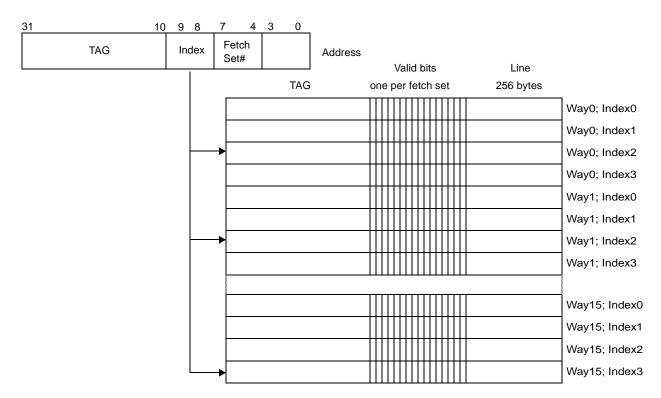

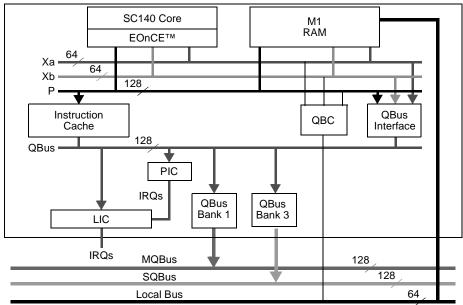

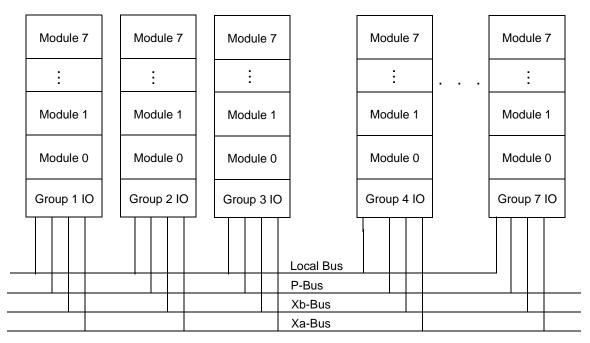

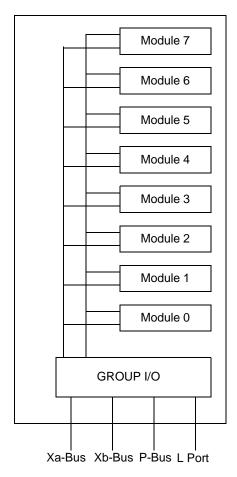

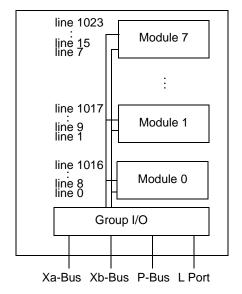

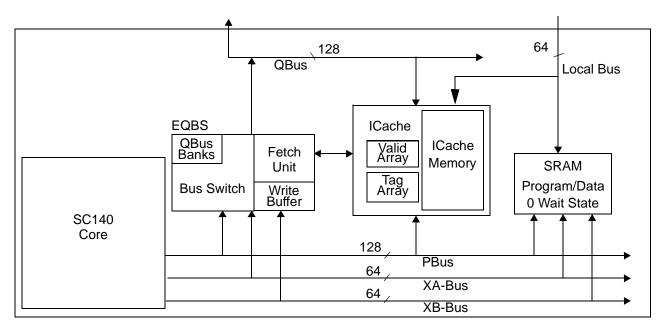

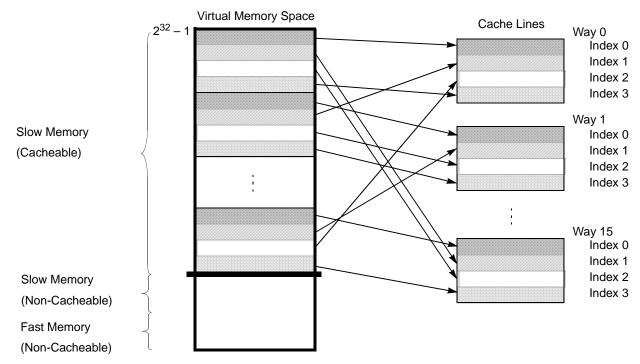

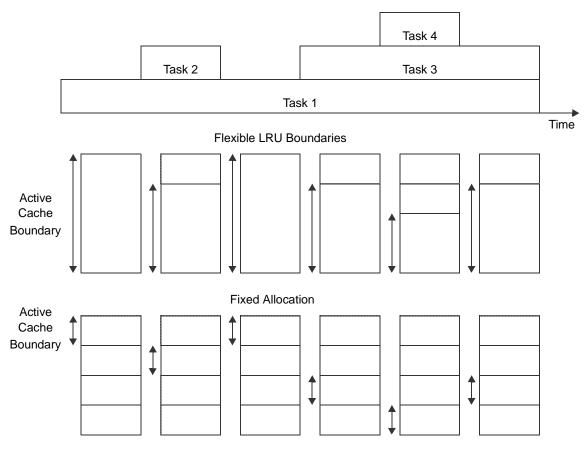

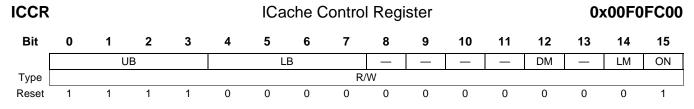

Each core is part of an extended core that includes a level-1 224 KB internal memory (M1) for program and data storage, a 16 KB 16-way instruction cache (ICache), a fetch unit for the ICache, and a 4-entry write buffer queue for boosting core performance. Each extended core also includes a programmable interrupt controller (PIC), a local interrupt controller (LIC), and debugging registers in an Enhanced On-Chip Emulation (EOnCE) module and JTAG TAP controller. All the extended cores share an internal 476 KB level-2 memory (M2) and a general interrupt controller (GIC).

The external interfaces and peripherals include a system and local bus managed by a system interface unit (SIU) and memory controller, a 32/64-bit direct slave interface (DSI) port, four 256-channel TDM interfaces, a serial universal asynchronous receiver/transmitter (UART), timers, an Ethernet interface that can operate in any of three modes (MII, RMII, or SMII), an I<sup>2</sup>C interface to allow booting from a serial EEPROM, and general-purpose input/output (GPIO) ports. The MSC8113 device is backward-compatible with the MSC8102; that is, it can replace a MSC8102 device and execute the same code with no modifications.

Freescale Semiconductor 1-1

# 1.1 Features

The tables in this section list the features of the MSC8113 device.

Table 1-1. Extended SC140 Cores and Core Memories

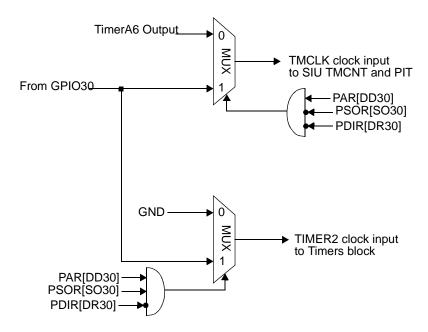

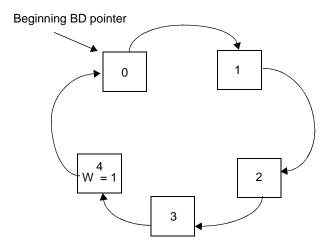

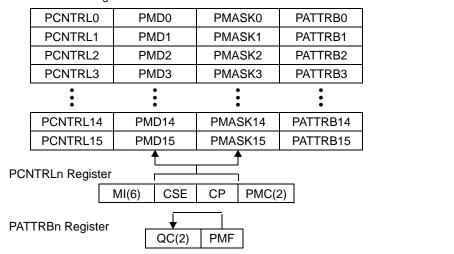

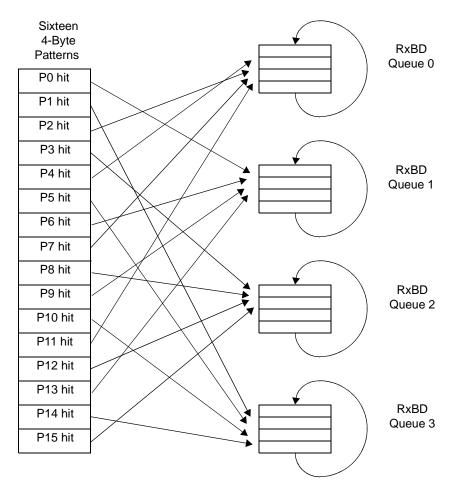

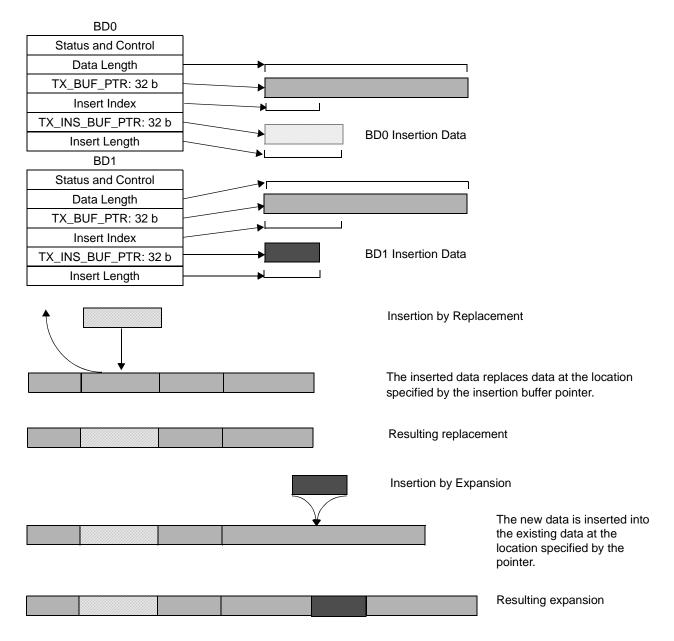

| Feature                                 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |