ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005

# MC68SZ328 Integrated Processor

Reference Manual

MC68SZ328RM/D Rev. 1.3, 3/2004

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005

#### HOW TO REACH US:

#### SUSA/EUROPE/LOCATIONS NOT LISTED:

Motorola Literature Distribution

P.O. Box 5405, Denver, Colorado 80217

1-800-521-6274 or 480-768-2130

#### JAPAN:

Motorola Japan Ltd.; SPS, Technical Information Center, 3-20-1, Minami-Azabu, Minato-ku, Tokyo 106-8573, Japan 81-3-3440-3569

#### **≪ASIA/PACIFIC:**

Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre, u.2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong

#### HOME PAGE:

http://motorola.com/semiconductors

Information in this document is provided solely to enable system and software implementers to use Motorola products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

This product has been designed for use in "Commercial" applications. Please see a description below:

"Commercial": Typically 5 year applications — personal computers, PDA's, portable telecom products, consumer electronics, etc.

For questions, please contact a Motorola sales representative.

Motorola and the Stylized M Logo are registered in the U.S. Patent and Trademark Office. All other product or service names are the property of their respective owners. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© Motorola, Inc. 2004

ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005

# **Contents**

| Abou                                                 | t This Book                                                                                                                       |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|                                                      | AudiencexxxixRevision HistoryxxxixOrganizationxlSuggested ReadingxliiConventionsxliiDefinitions, Acronyms, and Abbreviationsxliii |

| Chap<br>Introd                                       | ter 1<br>duction                                                                                                                  |

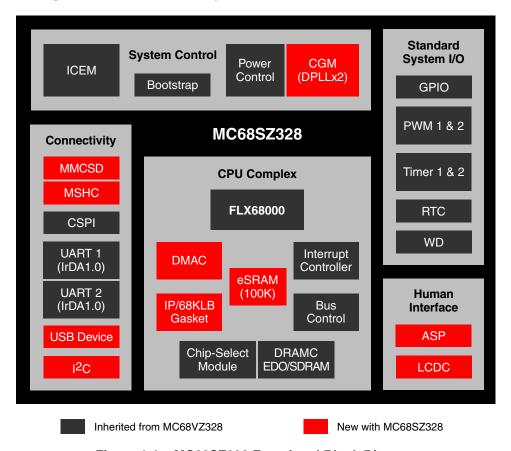

| 1.1<br>1.2<br>1.3                                    | Block Diagram                                                                                                                     |

| Chap<br>Signa                                        | ter 2<br>al Descriptions                                                                                                          |

| 2.1                                                  | Signal Descriptions by Function                                                                                                   |

| Chap<br>FLX6                                         | ter 3<br>8000 Core                                                                                                                |

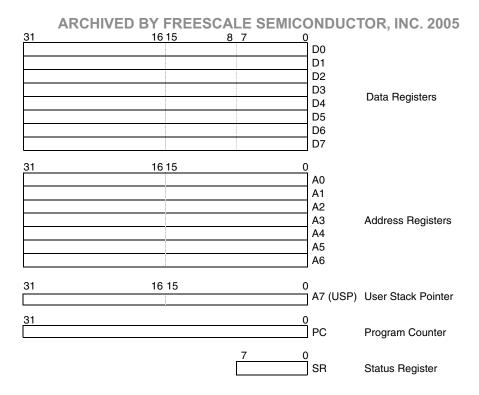

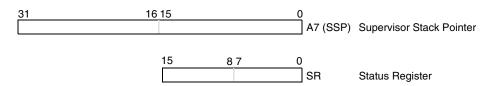

| 3.1<br>3.2<br>3.3                                    | Core Programming Model3-1Data and Address Modes3-2FLX68000 Instruction Set3-3                                                     |

| Chap<br>Memo                                         | ter 4<br>ory Map                                                                                                                  |

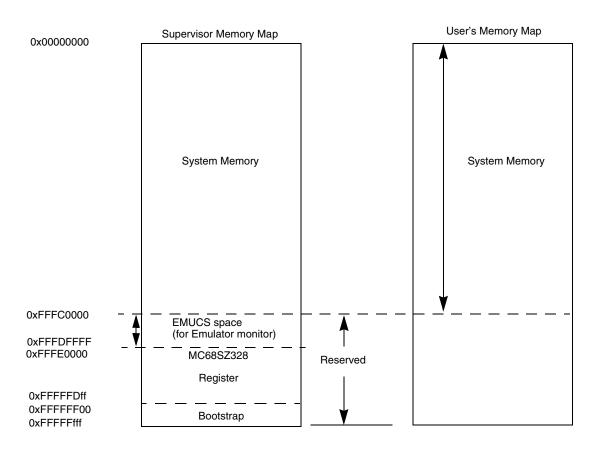

| 4.1                                                  | Programmer's Memory Map                                                                                                           |

| Chap<br>Clock                                        | ter 5<br>c Generation Module and Power Control Module                                                                             |

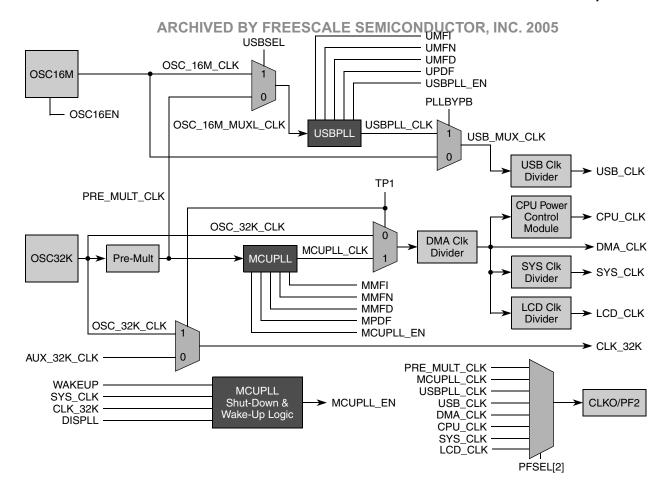

| 5.1<br>5.2<br>5.2.1<br>5.2.1.1<br>5.2.1.2<br>5.2.1.3 | USB Clock (48 MHz)                                                                                                                |

| 5.3     | Power Management/VED BY FREESCALE SEMICONDUCTOR, INC. 2005 | 5-7  |

|---------|------------------------------------------------------------|------|

| 5.3.1   | MCUPLL Clock Control                                       | 5-7  |

| 5.3.2   | USBPLL Clock Control                                       | 5-8  |

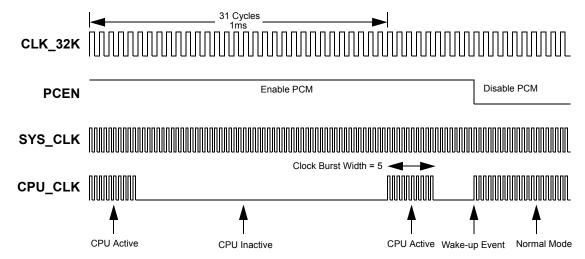

| 5.3.3   | CPU Clock Control                                          | 5-8  |

| 5.3.3.1 |                                                            |      |

| 5.3.4   | CPU Power Control and DMA Controller                       | 5-9  |

| 5.4     | Programming Model                                          | 5-10 |

| 5.4.1   | PLL Control Register                                       |      |

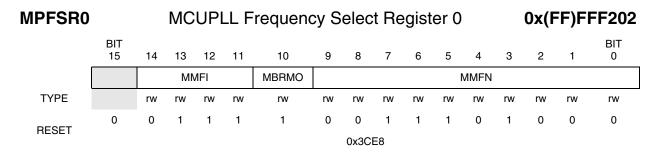

| 5.4.2   | MCUPLL Frequency Select Register 0                         |      |

| 5.4.3   | MCUPLL Frequency Select Register 1                         |      |

| 5.4.4   | USBPLL Frequency Select Register 0                         |      |

| 5.4.5   | USBPLL Frequency Select Register 1                         |      |

| 5.4.6   | CPU Power Control Register                                 |      |

| 5.4.7   | Clock Sources Control Register                             | 5-15 |

| Ob      | Jan C                                                      |      |

| Chap    | em Control                                                 |      |

| Syste   |                                                            |      |

| 6.1     | System Control Operation                                   | 6-1  |

| 6.1.1   | Bus Monitors and Watchdog Timers                           |      |

| 6.2     | Programming Model                                          |      |

| 6.2.1   | System Control Register                                    |      |

| 6.2.2   | Peripheral Control Register                                |      |

| 6.2.3   | ID Register                                                |      |

| 6.2.4   | I/O Drive Control Register                                 | 6-5  |

|         |                                                            |      |

| Chap    |                                                            |      |

| Cnip.   | -Select Module                                             |      |

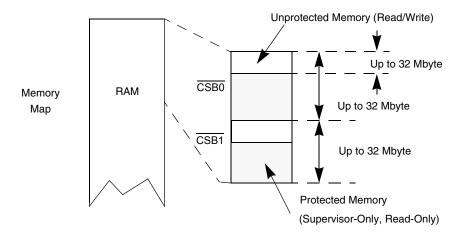

| 7.1     | Overview                                                   | 7-1  |

| 7.2     | Chip-Select Operation                                      |      |

| 7.2.1   | Memory Protection                                          |      |

| 7.2.2   | Programmable Data Bus Size                                 |      |

| 7.2.3   | Overlapping Chip-Select Registers                          | 7-4  |

| 7.3     | Programming Model                                          |      |

| 7.3.1   | Chip-Select Group Base Address Registers                   | 7-4  |

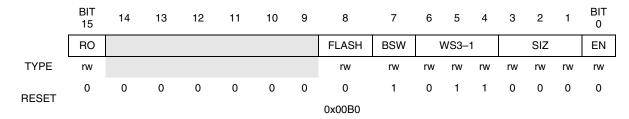

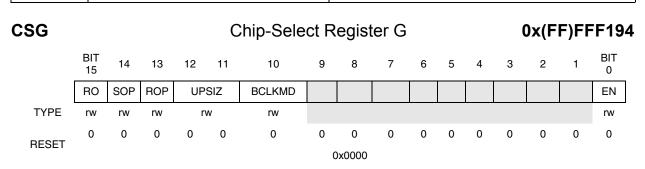

| 7.3.2   | Chip-Select Registers                                      | 7-7  |

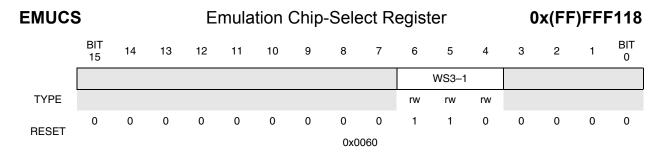

| 7.3.3   | Emulation Chip-Select Register                             | 7-20 |

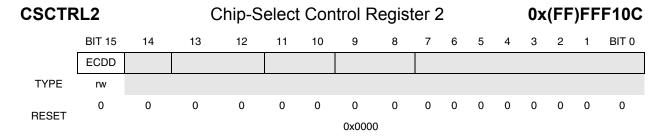

| 7.3.4   | Chip-Select Control Register 1                             |      |

| 7.3.5   | Chip-Select Control Register 2                             | 7-23 |

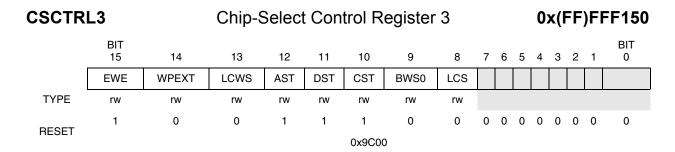

| 7.3.6   | Chip-Select Control Register 3                             |      |

| ٥:      |                                                            |      |

| Chap    | M Controller                                               |      |

| DKAI    | M Controller                                               |      |

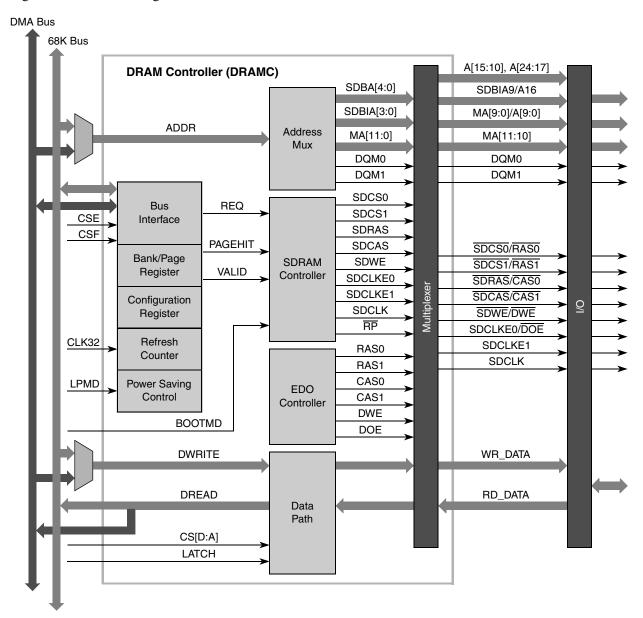

| 8.1     | DRAM Controller Features                                   | 8-1  |

| 8.2     | General Architecture.                                      |      |

| 8.3     | Block Diagram                                              |      |

| 8.4            | External Interface HIVED BY FREESCALE SEMICONDUCTOR, INC. 2005 | 8-3  |

|----------------|----------------------------------------------------------------|------|

| 8.5            | Address Multiplexing                                           | 8-4  |

| 8.6            | Programming Model                                              | 8-5  |

| 8.6.1          | Secondary Control Register                                     | 8-6  |

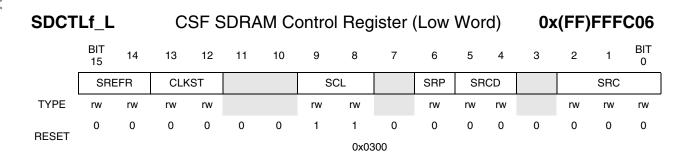

| 8.6.2          | SDRAM Control Registers                                        | 8-7  |

| 8.6.2.1        | SDRAM Controller Operating Mode                                | 8-10 |

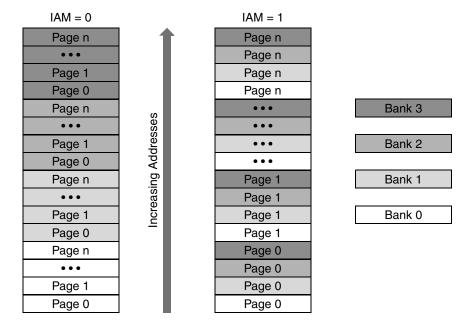

| 8.6.2.2        | SDRAM Interleaved Address Mode                                 | 8-11 |

| 8.6.3          | EDO Control Registers                                          | 8-12 |

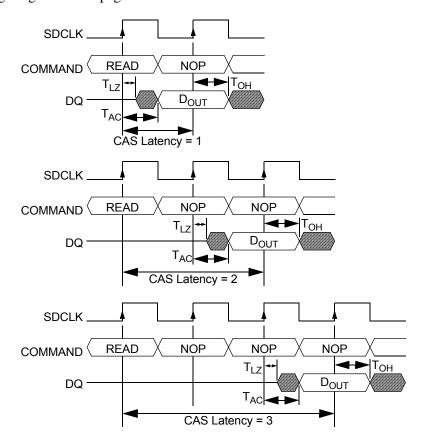

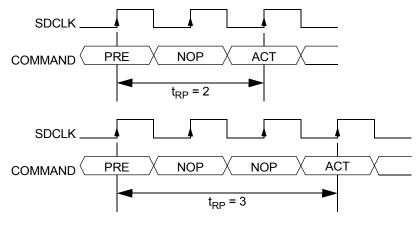

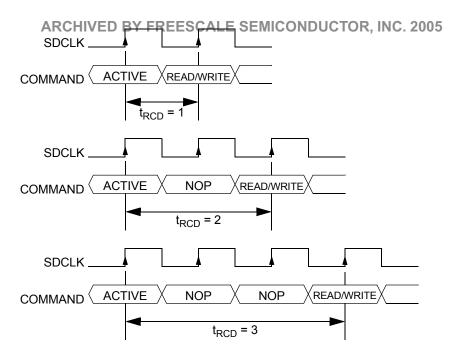

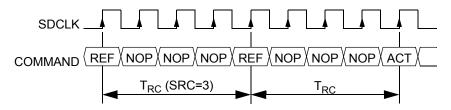

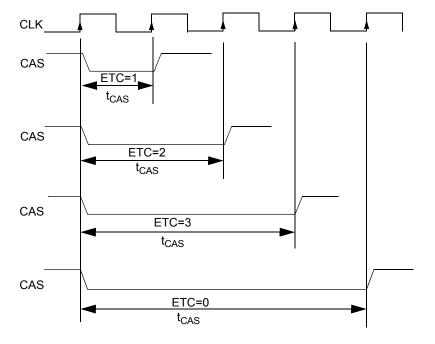

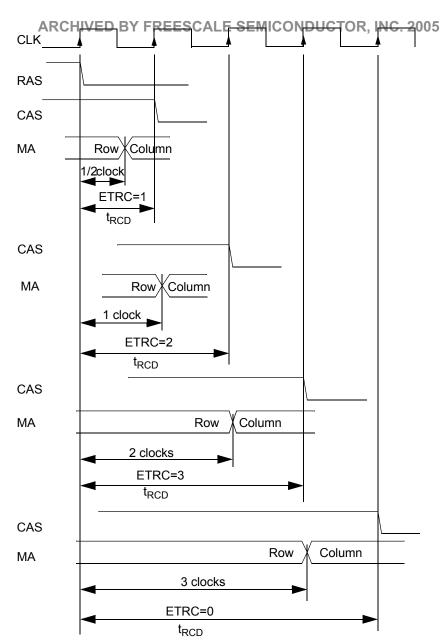

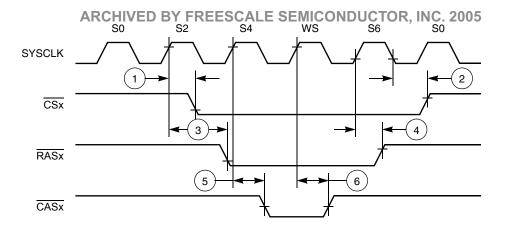

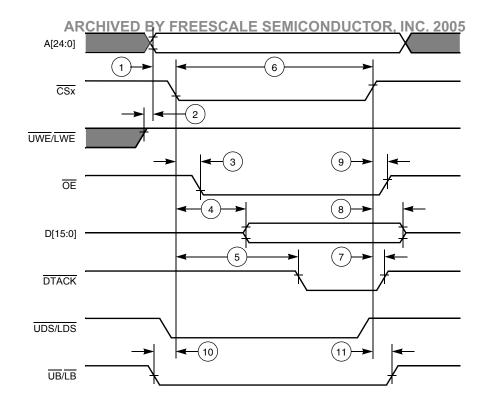

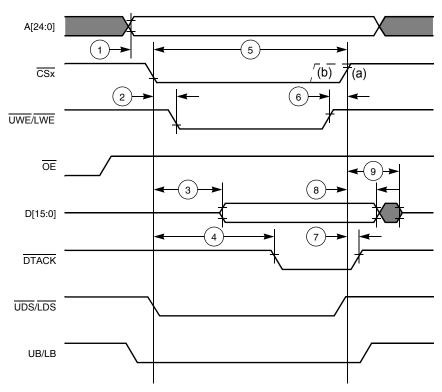

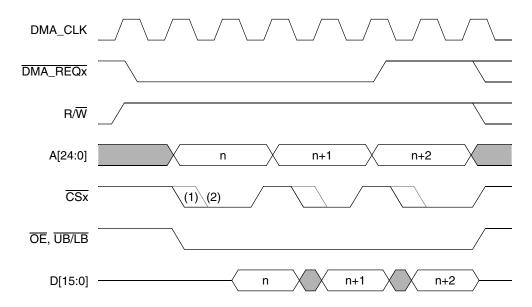

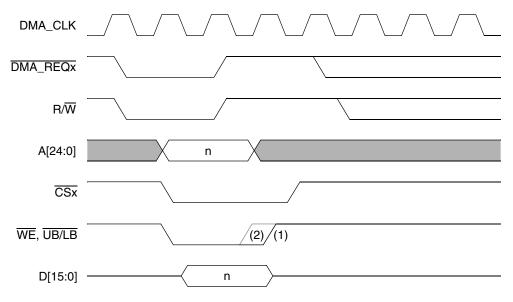

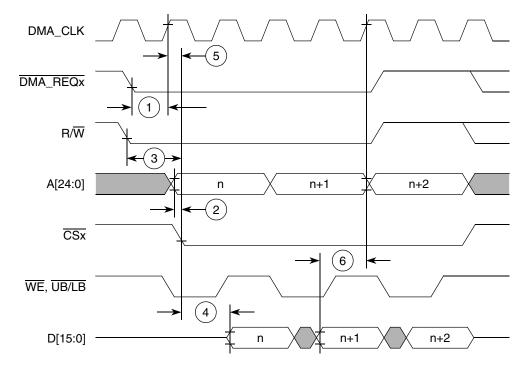

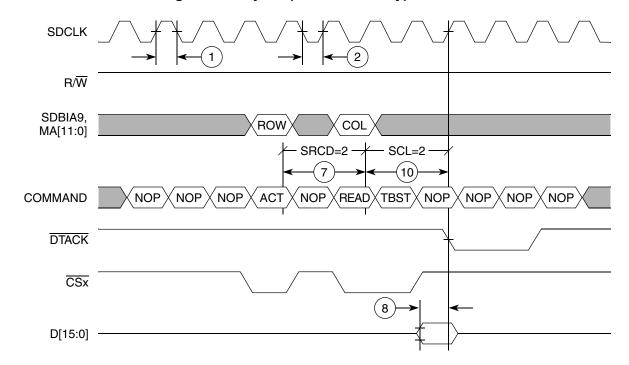

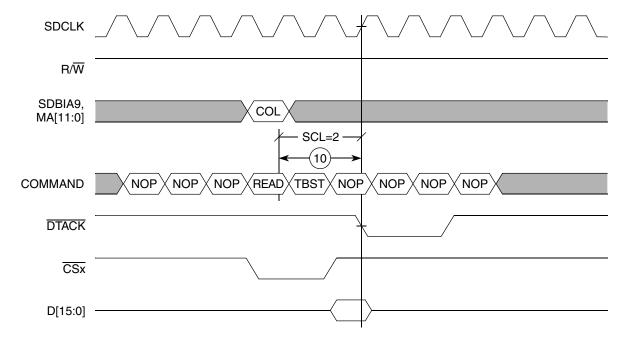

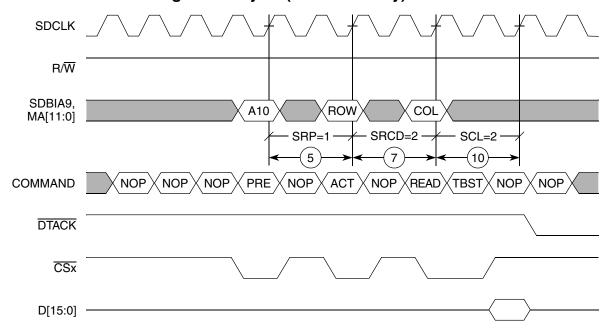

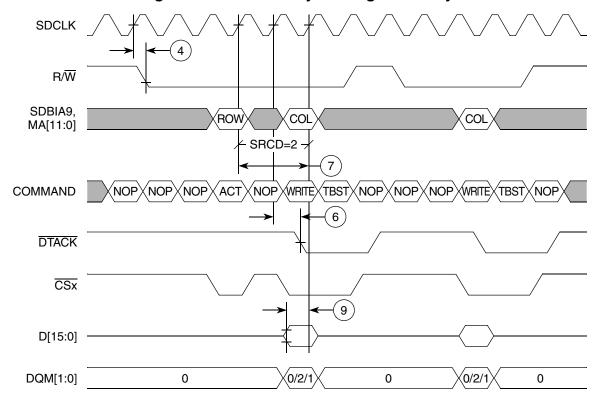

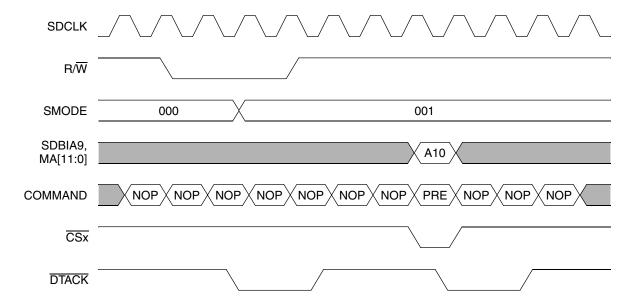

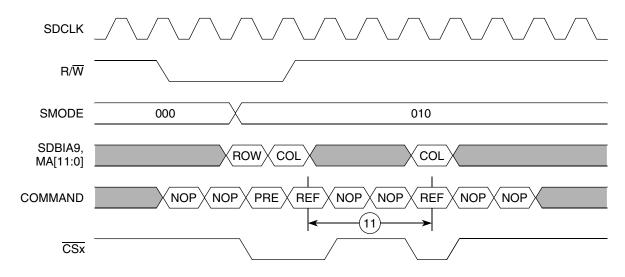

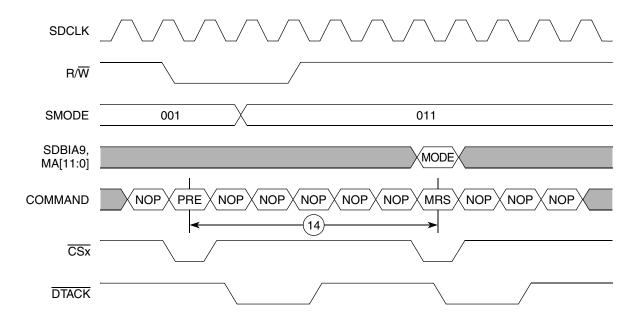

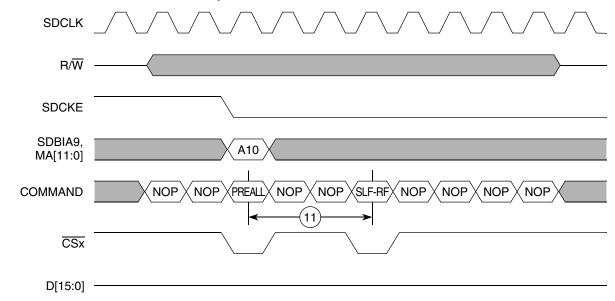

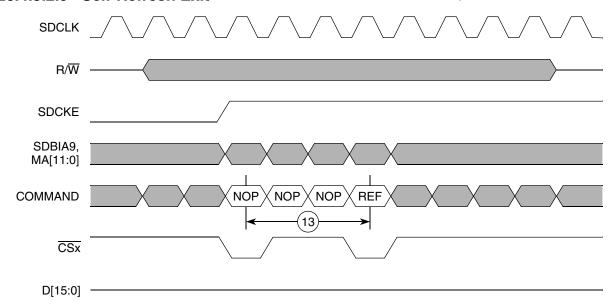

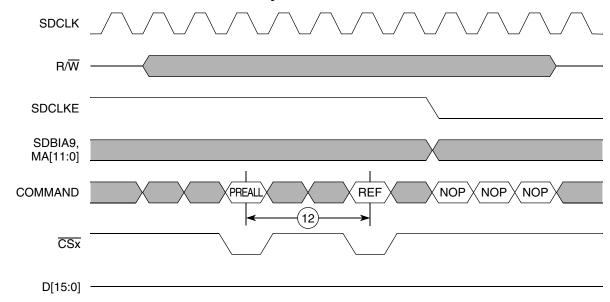

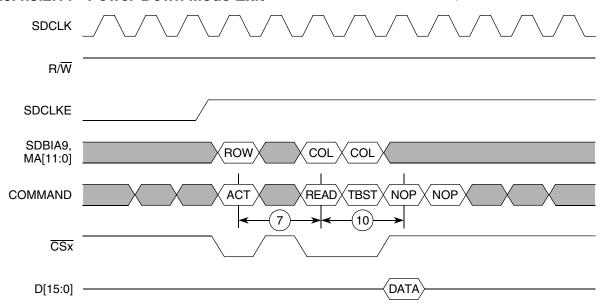

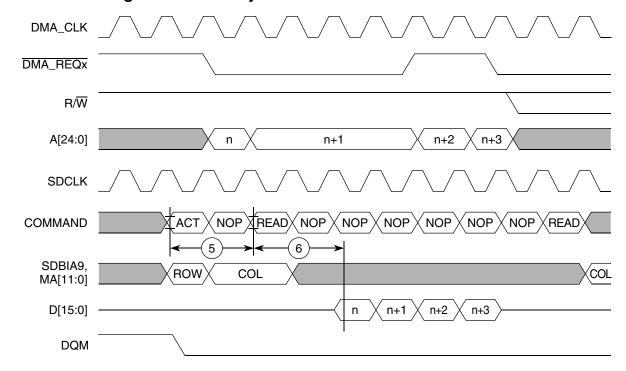

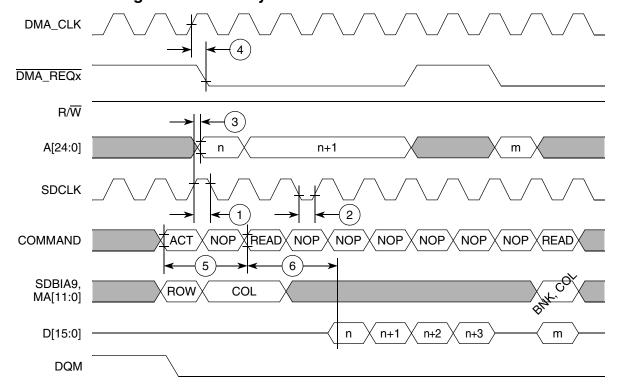

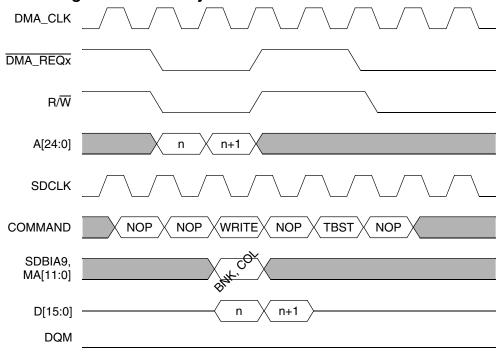

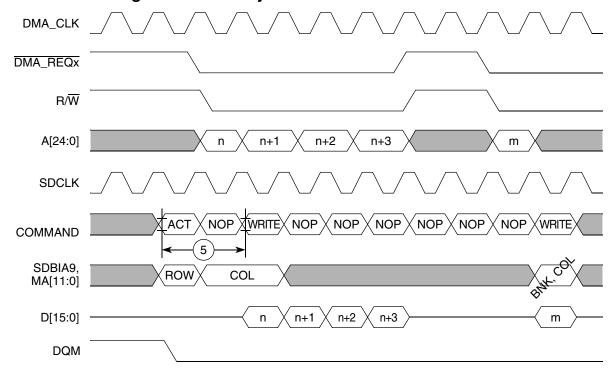

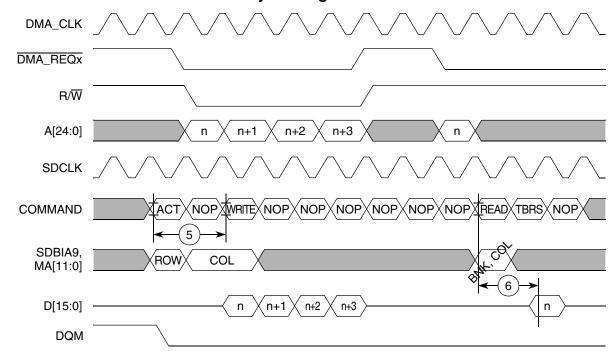

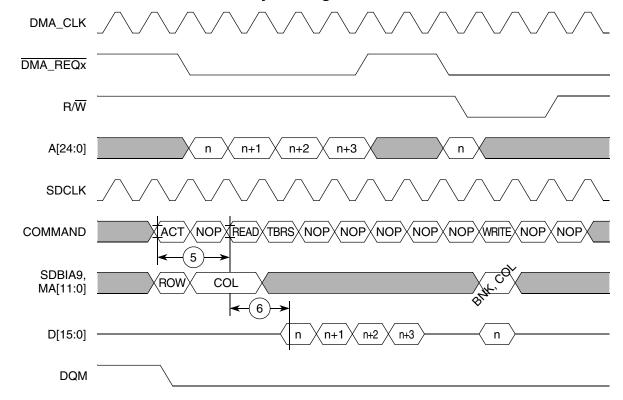

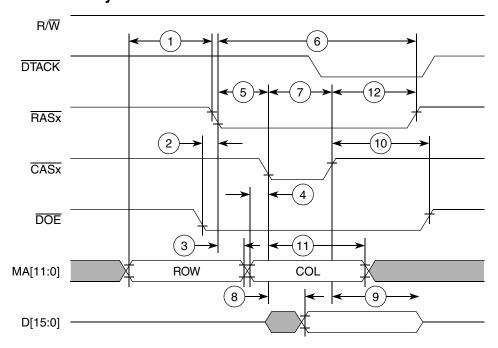

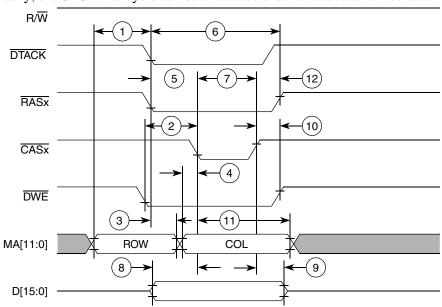

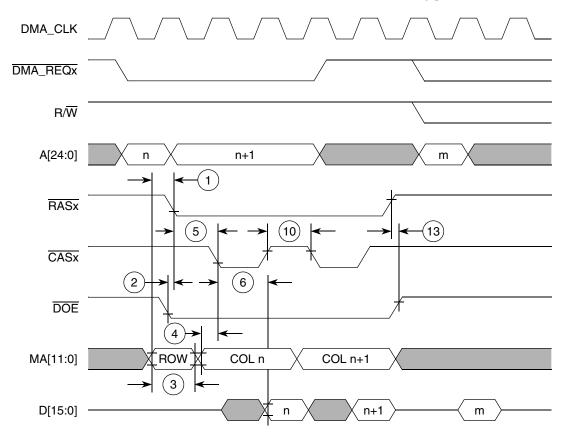

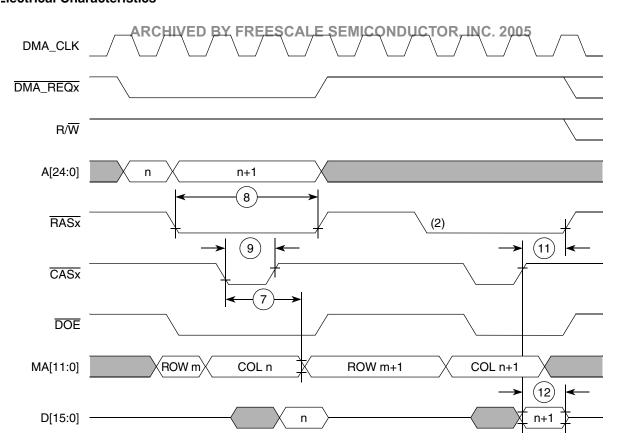

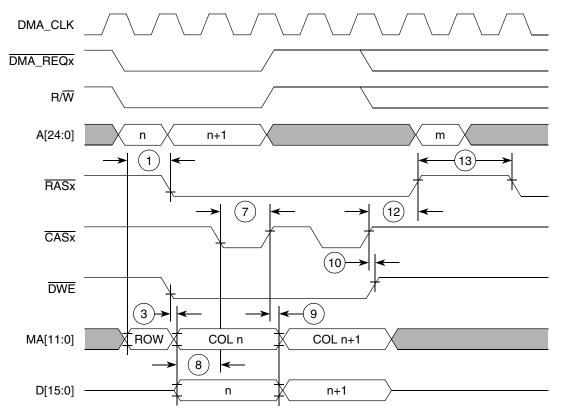

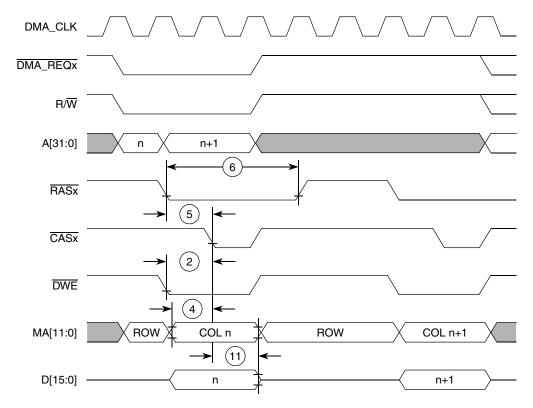

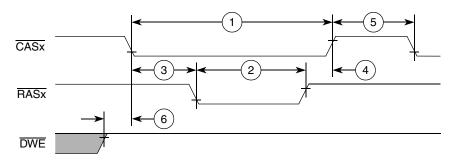

| 8.6.4          | Timing Diagrams                                                | 8-15 |

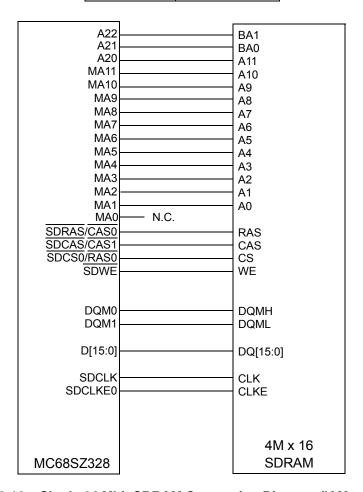

| 8.7            | Application Examples                                           | 8-18 |

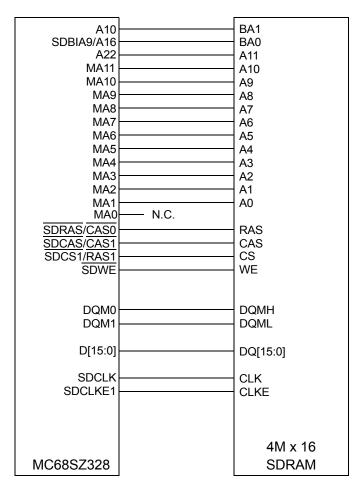

| 8.7.1          | Single 64 Mbit SDRAM (IAM=0, CSE)                              | 8-19 |

| 8.7.2          | Single 64 Mbit SDRAM (IAM=1, CSF)                              | 8-21 |

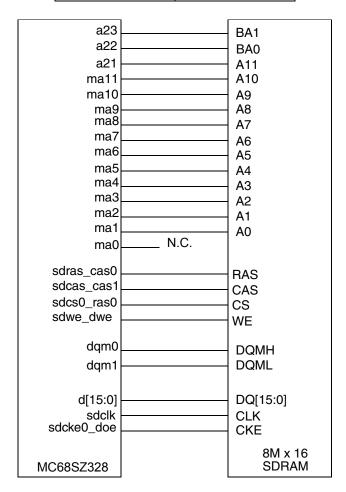

| 8.7.3          | Single 128 Mbit SDRAM (IAM=1, CSF)                             | 8-23 |

| 8.7.4          | Single 128 Mbit SDRAM (IAM=0, CSE)                             | 8-25 |

| 8.7.5          | Single 256 Mbit SDRAM (IAM=1, CSE)                             | 8-27 |

| 8.7.6          | Single 256 Mbit SDRAM (IAM=0, CSE)                             | 8-29 |

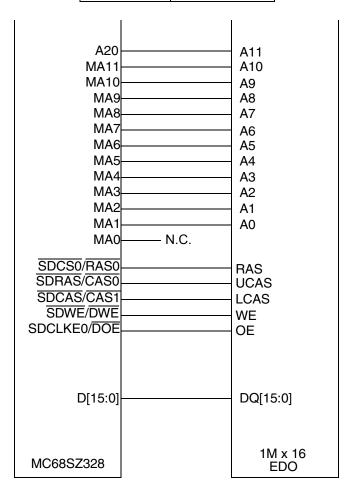

| 8.7.7          | Single 16 Mbit EDO (CSE)                                       |      |

|                |                                                                |      |

| Chap           |                                                                |      |

| DMA            | Controller                                                     |      |

| 0.1            | Easterna                                                       | 0.1  |

| 9.1            | Features                                                       |      |

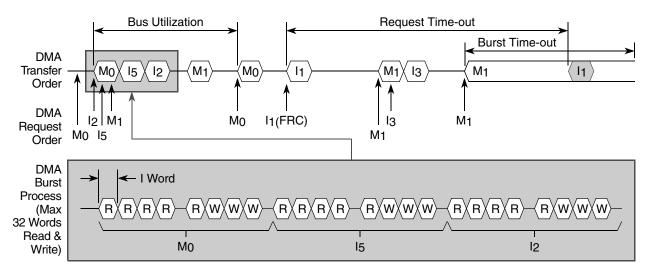

| 9.1.1          | DMAC Organization in MC68SZ328                                 |      |

| 9.2<br>9.2.1   | DMAC Signal Description                                        |      |

| 9.2.1          | DMAC Signal Description                                        |      |

| 9.3.1          | External DMA Request Pins                                      |      |

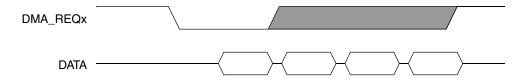

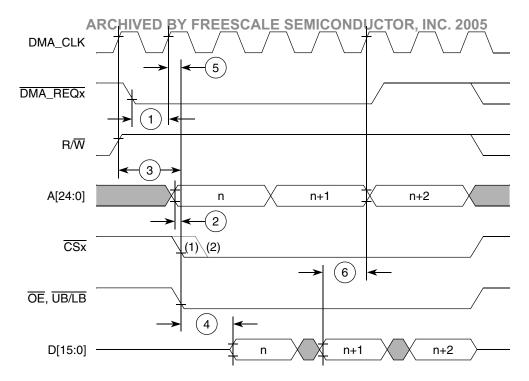

| 9.3.1          | DMA Request and Transfer                                       |      |

| 9.4            | Block Transfer Functions Using Memory Channels 0 and 1         |      |

| 9.5<br>9.6     |                                                                |      |

| 9.6.1          | DMAC General Registers                                         |      |

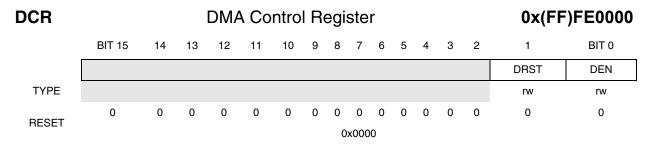

| 9.6.1          | DMA Control Register                                           |      |

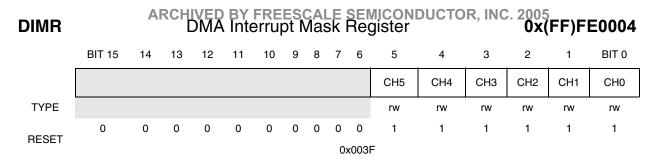

|                | DMA Interment Mock Projector                                   |      |

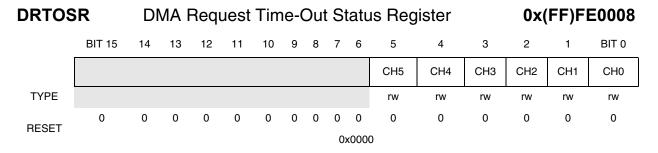

| 9.6.3          | DMA Burst Time Out Status Register                             |      |

| 9.6.4<br>9.6.5 | DMA Bagyast Time Out Status Register                           |      |

| 9.6.6          | DMA Request Time-Out Status Register                           |      |

| 9.0.0          | DMA Burst Time-Out Control Register                            |      |

| 9.7<br>9.7.1   | Memory Channel Source Address Register                         |      |

| 9.7.1          | ·                                                              |      |

| 9.7.2          | Memory Channel Count Register                                  |      |

| 9.7.3<br>9.7.4 | Memory Channel Count Register                                  |      |

| 9.7.4          | , c                                                            |      |

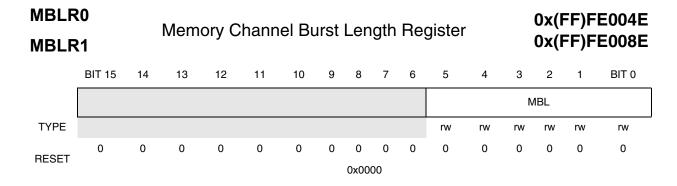

|                | Memory Channel Burst Length Register                           |      |

| 9.7.6          | Memory Channel Bus Utilization Control Register                |      |

| 9.7.7          | Block Length Register                                          |      |

| 9.7.8          | Source Block Separation Distance Register                      |      |

| 9.7.9          | Memory Channel External DMA Request Time-Out Register          |      |

| 9.7.10         | Destination Block Separation Distance Register                 |      |

| 9.8            | I/O Channels (Channels 2–5) Registers                          | 9-20 |

| 9.8.1   | I/O Channer Memory Address Register SEMICONDUCTOR, INC. 2005 | . 9-20 |

|---------|--------------------------------------------------------------|--------|

| 9.8.2   | I/O Channel Peripheral Address Register                      | . 9-21 |

| 9.8.3   | I/O Channel Count Register                                   | . 9-22 |

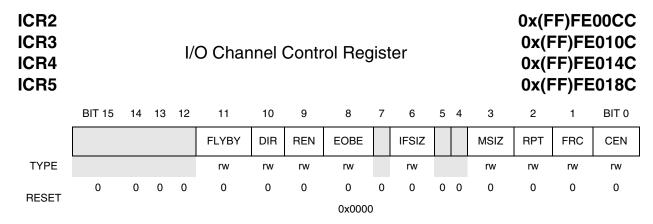

| 9.8.4   | I/O Channel Control Register                                 | . 9-23 |

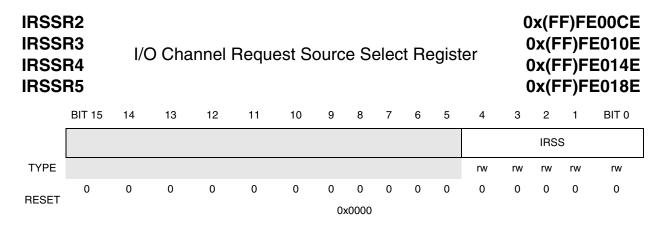

| 9.8.5   | I/O Channel Request Source Select Register                   | . 9-25 |

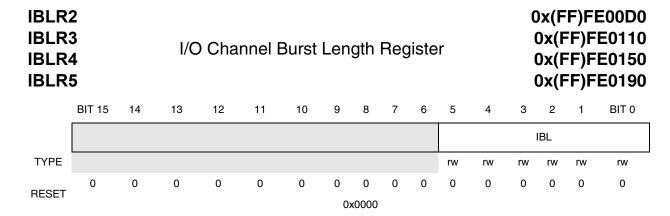

| 9.8.6   | I/O Channel Burst Length Register                            | . 9-25 |

| 9.8.7   | I/O Channel DMA Request Time-Out Register                    | . 9-27 |

| 9.9     | DMAC Register Addresses                                      | . 9-28 |

| 9.10    | DMA Request Table                                            | . 9-30 |

| Chan    | ter 10                                                       |        |

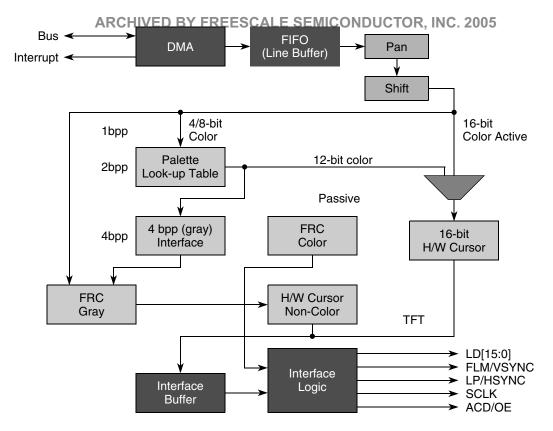

|         | Controller                                                   |        |

| 10.1    | Features                                                     | 10-1   |

| 10.2    | Operation                                                    |        |

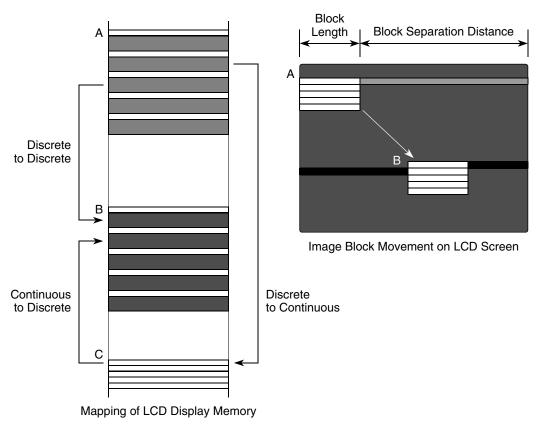

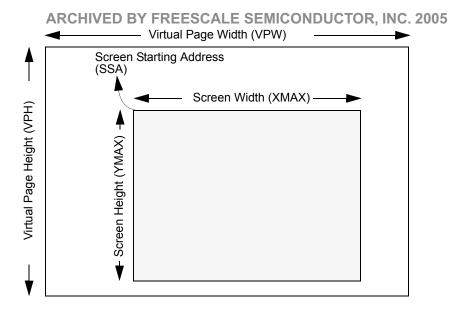

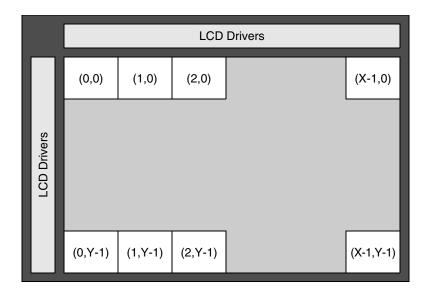

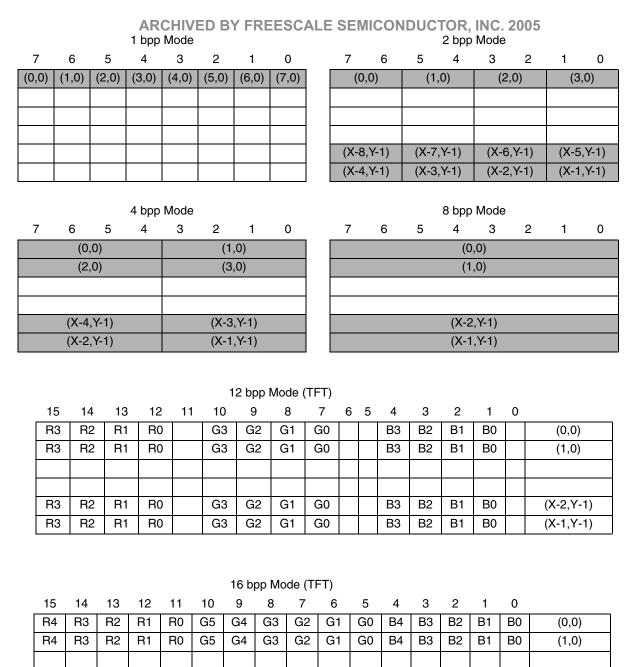

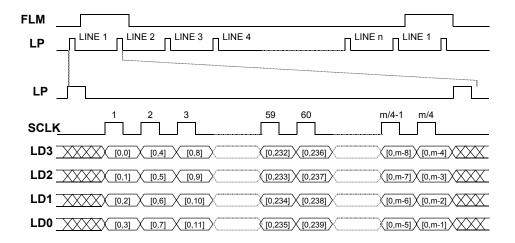

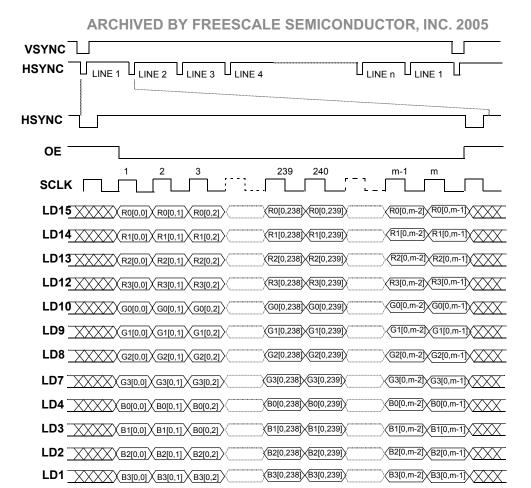

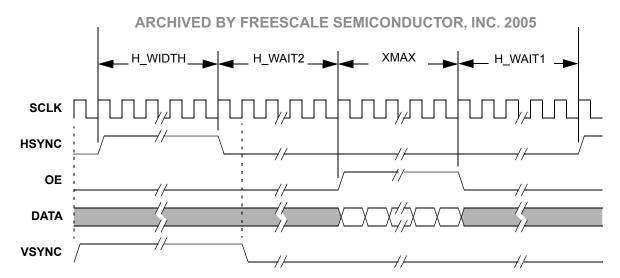

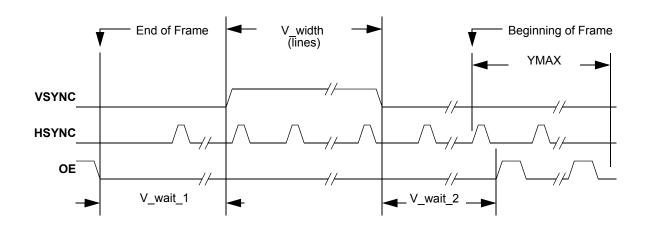

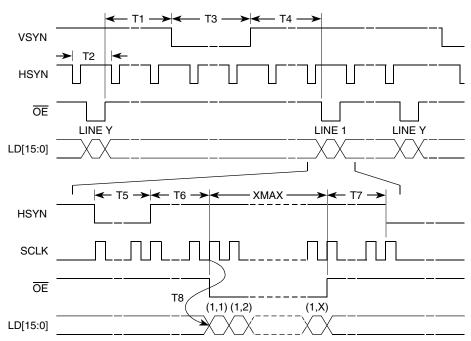

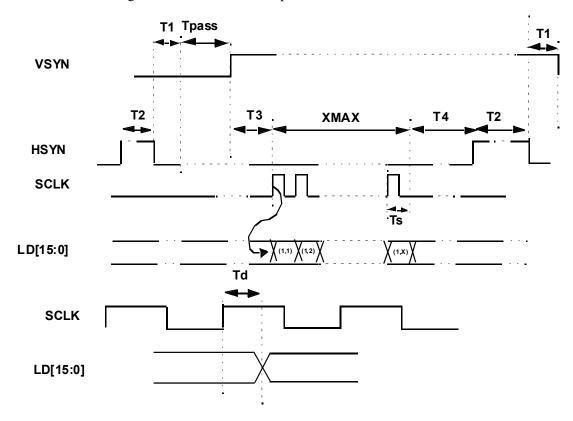

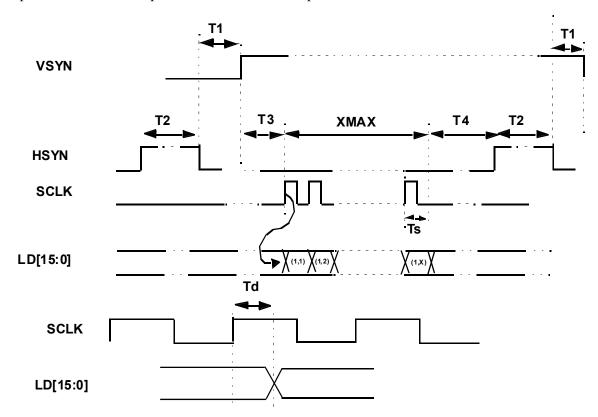

| 10.2.1  | LCD Screen Format                                            |        |

| 10.2.2  | Panning                                                      |        |

| 10.2.3  | Display Data Mapping                                         |        |

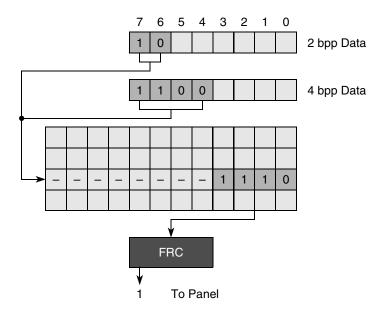

| 10.2.4  | Gray-Scale Operation                                         |        |

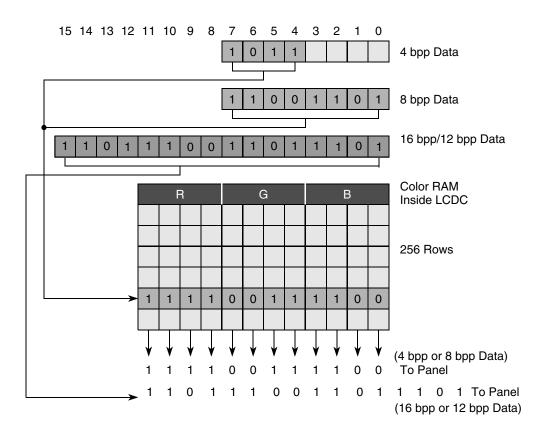

| 10.2.5  | Color Generation.                                            |        |

| 10.2.6  | Frame Rate Modulation Control (FRC)                          |        |

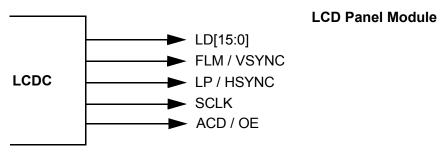

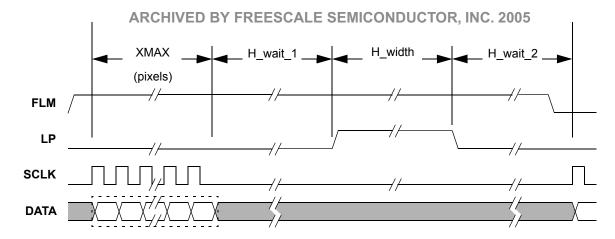

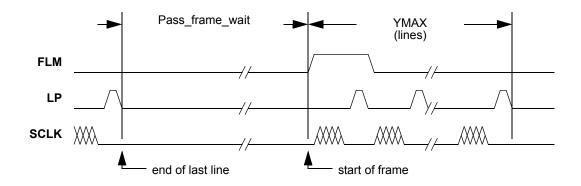

| 10.2.7  | Panel Interface Signals and Timing                           |        |

| 10.2.7. |                                                              |        |

| 10.2.7. | S .                                                          |        |

| 10.2.7. | 8, , , , , , , , , , , , , , , , , , ,                       |        |

| 10.2.7. | $\mathcal{E}$                                                |        |

| 10.3    | Programming Model                                            |        |

| 10.3.1  | LCD Screen Start Address Register                            |        |

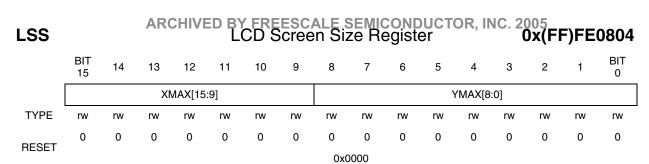

| 10.3.2  | LCD Screen Size Register                                     |        |

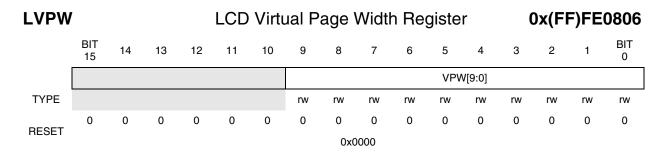

| 10.3.3  | LCD Virtual Page Width Register                              |        |

| 10.3.4  | LCD Panel Configuration Registers                            |        |

| 10.3.5  | LCD Horizontal Configuration Registers                       |        |

| 10.3.6  | LCD Vertical Configuration Registers                         |        |

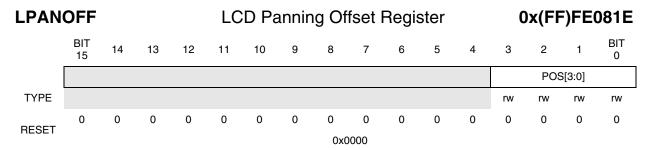

| 10.3.7  | LCD Panning Offset Register                                  |        |

| 10.3.8  | LCD Cursor X Position Register                               |        |

| 10.3.9  | LCD Cursor Y Position Register                               |        |

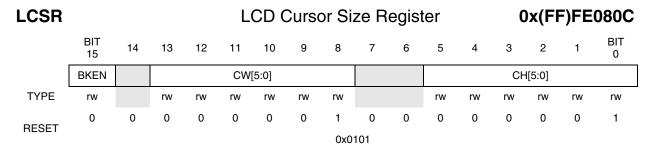

| 10.3.10 |                                                              |        |

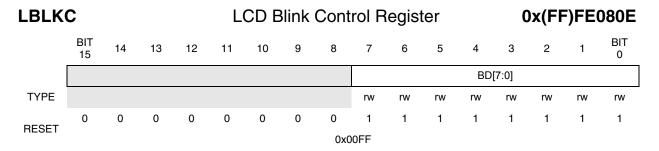

| 10.3.11 | · · · · · · · · · · · · · · · · · · ·                        |        |

| 10.3.12 |                                                              |        |

| 10.3.13 |                                                              |        |

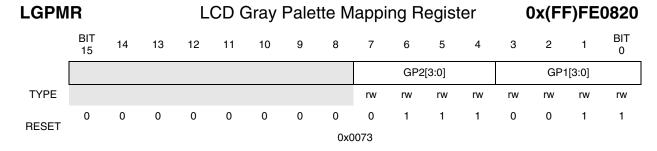

| 10.3.14 |                                                              |        |

| 10.3.15 | <u>e</u>                                                     |        |

| 10.3.16 | <u> </u>                                                     |        |

| 10.3.17 | C                                                            |        |

| 10.3.18 |                                                              |        |

| 10.3.19 |                                                              |        |

| 10.3.19 |                                                              |        |

| 10.3.19 | P.2 Four Bits/Pixel Gray-Scale Mode                          | 10-33  |

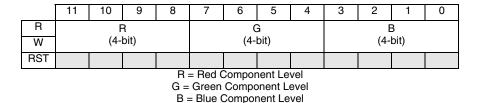

| 10.3.19.3 Fou                      | ır BiRAPİXEFPaRSYVETMATERCOLFORMULGONDUÇTOR, INC. 2005 | 10-33                    |

|------------------------------------|--------------------------------------------------------|--------------------------|

| 10.3.19.4 Eig                      | ht Bits/Pixel Passive Matrix Color Mode                | 10-33                    |

| 10.3.19.5 Fou                      | rr Bits/Pixel Active Matrix Color Mode                 | 10-34                    |

| 10.3.19.6 Eig                      | ht Bits/Pixel Active Matrix Color Mode                 | 10-34                    |

| 10.3.19.7 Two                      | elve/Sixteen Bits/Pixel Active Matrix Color Mode       | 10-34                    |

|                                    |                                                        |                          |

| Chapter 11                         | Duranan                                                |                          |

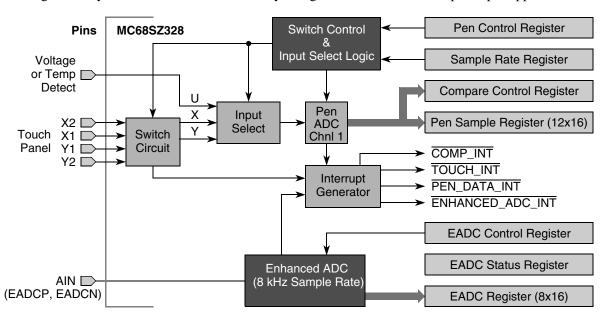

| Analog Signal                      | Processor                                              |                          |

| 11.1 Features                      |                                                        | 11-1                     |

|                                    | tion                                                   |                          |

| _                                  | Circuit                                                |                          |

| 11.2.2 Switch                      | Control and Input Select Logic                         | 11-2                     |

| 11.2.3 Input S                     | elect                                                  | 11-2                     |

|                                    | ed ADC                                                 |                          |

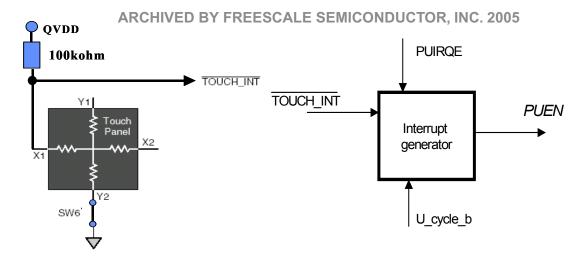

| 11.2.5 Interrup                    | ot Generator                                           | 11-3                     |

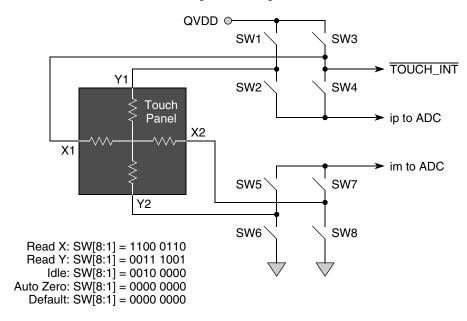

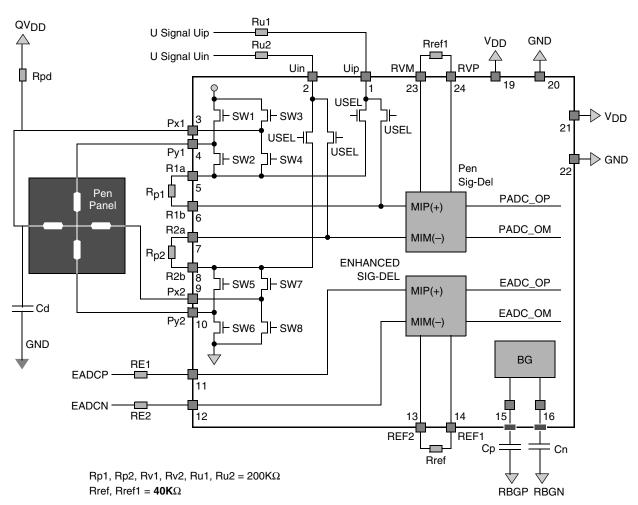

| 11.3 Touch Pane                    | el Switching Circuit Operation                         | 11-4                     |

| 11.4 Pen ADC (                     | Operation                                              | 11-4                     |

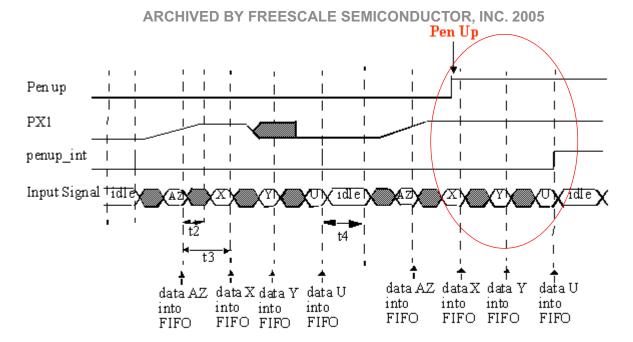

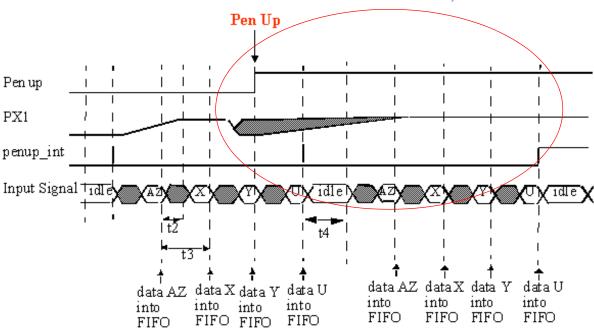

|                                    | p Detection Method                                     |                          |

| 11.5.1 Discard                     | ling Sample Data Before Pen Up Event                   | 11-8                     |

|                                    | Zero Switch Configuration                              |                          |

|                                    | Calibration Configuration                              |                          |

|                                    | ADC Operation                                          |                          |

| •                                  | ng Model                                               |                          |

|                                    | ontrol Register                                        |                          |

|                                    | D Sample Rate Control Register                         |                          |

|                                    | re Control Register                                    |                          |

|                                    | ot Control Register                                    |                          |

|                                    | ot/Error Status Register                               |                          |

|                                    | FO Pointer Register                                    |                          |

|                                    | mple FIFO Register                                     |                          |

|                                    | ed ADC Register                                        |                          |

|                                    | ed ADC Control Register                                |                          |

|                                    | Divide Register                                        |                          |

| 11.9.11 Enhanc                     | ed ADC FIR Coefficients RAM Register                   | 11-22                    |

| Chapter 12                         |                                                        |                          |

| General-Purpo                      | se Timers                                              |                          |

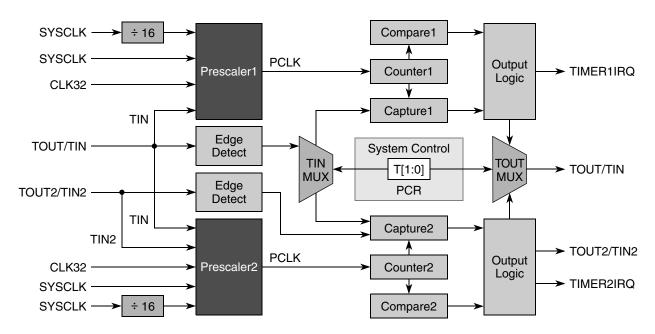

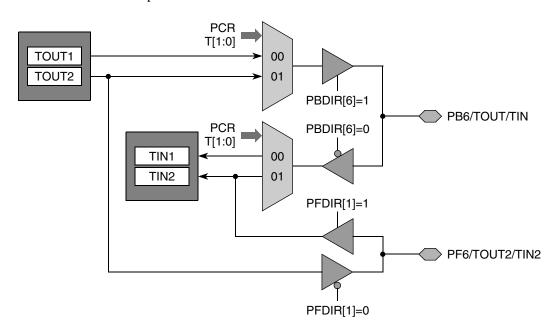

| 12.1 On anation                    |                                                        | 12.2                     |

|                                    | tinlarina                                              |                          |

|                                    | tiplexingction                                         |                          |

|                                    |                                                        |                          |

|                                    | Configuration                                          |                          |

|                                    | re and Capture Using Cascaded Timers                   |                          |

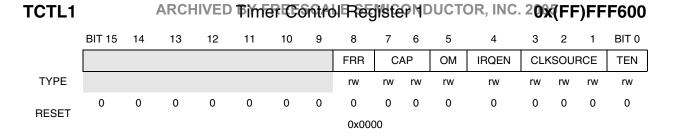

| _                                  | ng Model                                               |                          |

| 12.4.1 Programmi<br>12.4.1 Timer ( | Control Registers                                      | 12 <del>-4</del><br>12.7 |

|                                    | Prescaler Registers                                    |                          |

| 12.7.2 IIIICI I                    | . resource registers                                   | 12-0                     |

| 12.4.3 | Timer Compare Registers FREESCALE SEMICONDUCTOR, INC. 2005. | 12-7  |

|--------|-------------------------------------------------------------|-------|

| 12.4.4 | Timer Capture Registers                                     | 12-8  |

| 12.4.5 | Timer Counter Registers                                     | 12-9  |

| 12.4.6 | Timer Status Register                                       | 12-10 |

|        |                                                             |       |

|        | ter 13                                                      |       |

| Real-  | Time Clock                                                  |       |

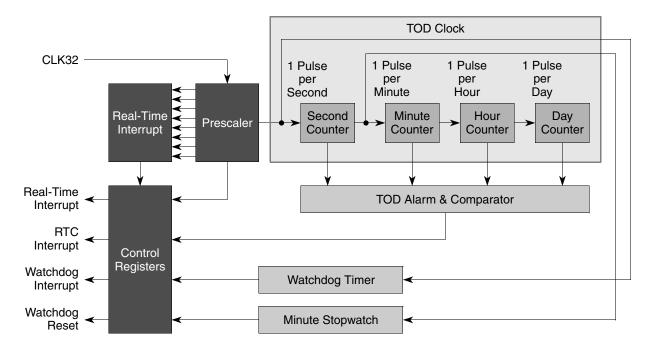

| 13.1   | Operation                                                   | 13-2  |

| 13.1.1 | Prescaler                                                   | 13-2  |

| 13.1.2 | Time-of-Day Counter                                         | 13-2  |

| 13.1.3 | Alarm                                                       |       |

| 13.1.4 | Watchdog Timer                                              | 13-3  |

| 13.1.5 | Real-Time Interrupt Timer                                   | 13-3  |

| 13.1.6 | Minute Stopwatch                                            |       |

| 13.2   | Programming Model                                           | 13-4  |

| 13.2.1 | RTC Time of Day Register                                    | 13-4  |

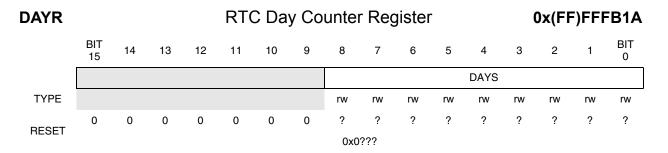

| 13.2.2 | RTC Day Counter Register                                    | 13-5  |

| 13.2.3 | RTC Alarm Register                                          | 13-5  |

| 13.2.4 | RTC Day Alarm Register                                      | 13-6  |

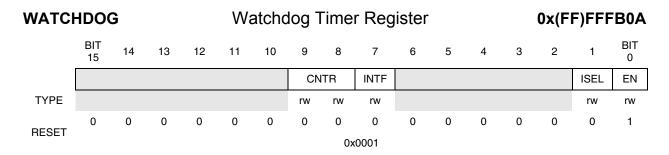

| 13.2.5 | Watchdog Timer Register                                     |       |

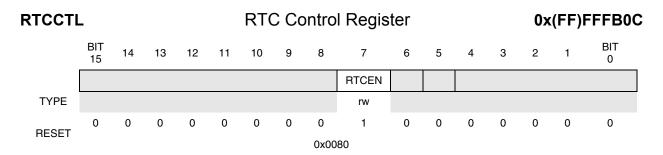

| 13.2.6 | RTC Control Register                                        |       |

| 13.2.7 | RTC Interrupt Status Register                               | 13-8  |

| 13.2.8 | RTC Interrupt Enable Register                               | 13-11 |

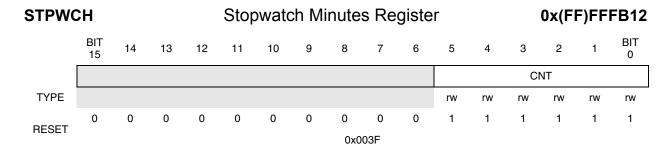

| 13.2.9 | Stopwatch Minutes Register                                  | 13-13 |

| 01     |                                                             |       |

|        | ter 14<br>-Width Modulator 1 and 2                          |       |

| ruise  |                                                             |       |

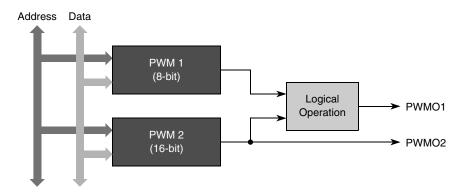

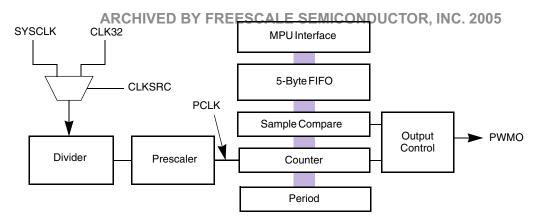

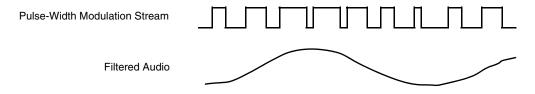

| 14.1   | Introduction to PWMs                                        | 14-1  |

| 14.1.1 | PWM 1                                                       | 14-1  |

| 14.1.2 | PWM 1 Clock Signals                                         | 14-2  |

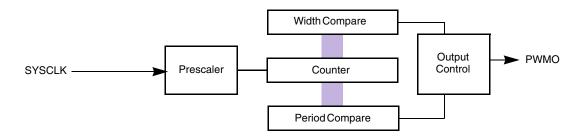

| 14.1.3 | PWM 2                                                       | 14-2  |

| 14.2   | PWM Operation                                               | 14-3  |

| 14.2.1 | Playback Mode                                               | 14-3  |

| 14.2.2 | Tone Mode                                                   | 14-3  |

| 14.2.3 | D/A Mode                                                    | 14-3  |

| 14.3   | Programming Model                                           | 14-4  |

| 14.3.1 | PWM 1 Control Register                                      | 14-4  |

| 14.3.2 | PWM 1 Sample Register                                       | 14-6  |

| 14.3.3 | PWM 1 Period Register                                       |       |

| 14.3.4 | PWM 1 Counter Register                                      | 14-7  |

| 14.3.5 | PWM 2 Control Register                                      | 14-8  |

| 14.3.6 | PWM 2 Period Register                                       | 14-9  |

| 14.3.7 | PWM 2 Pulse Width Control Register                          |       |

| 14.3.8 | PWM 2 Counter Register                                      | 14-10 |

### Freescale Semiconductor, Inc.

# **Chapter 15** ARCHIVED BY FREESCALE SEMICONDUCTOR, INC. 2005 Interrupt Controller

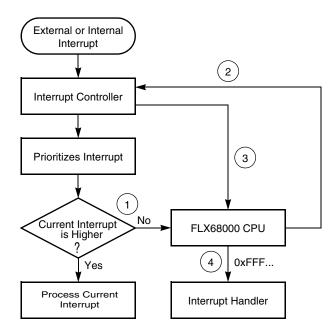

| 15.1             | Interrupt Processing                 |        |

|------------------|--------------------------------------|--------|

| 15.2             | Exception Vectors                    |        |

| 15.3             | Reset                                |        |

| 15.4             | Interrupt Controller Operation       |        |

| 15.4.1           | Interrupt Priority Processing        |        |

| 15.4.2           | Interrupt Vectors                    |        |

| 15.5             | Vector Generation.                   |        |

| 15.6             | System Wakeup Interrupts             |        |

| 15.7             | MMCSD/MS Interrupt                   |        |

| 15.8             | Programming Model                    |        |

| 15.8.1           | Interrupt Vector Register            |        |

| 15.8.2           | Interrupt Control Register           |        |

| 15.8.3           | Interrupt Mask Register              |        |

| 15.8.4           | Interrupt Status Register            |        |

| 15.8.5           | Interrupt Pending Register           |        |

| 15.8.6           | Interrupt Level Register             | 15-21  |

| <b>O</b> la a sa | Lau 40                               |        |

|                  | ter 16                               |        |

| Gene             | ral Purpose I/O Module               |        |

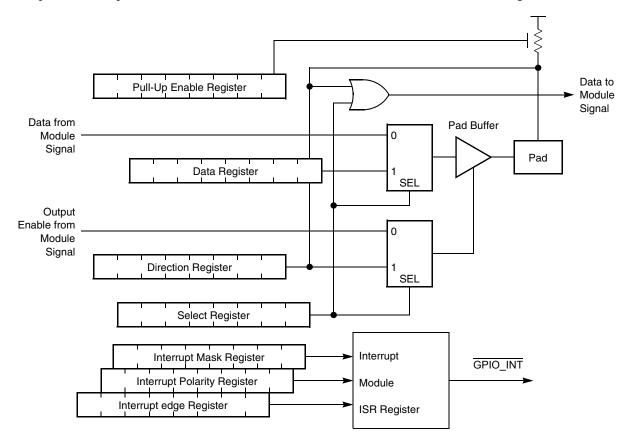

| 16.1             | Port Configuration                   | . 16-2 |

| 16.2             | Status of I/O Ports During Reset     |        |

| 16.3             | I/O Port Operation                   | . 16-4 |

| 16.3.1           | Data Flow from the I/O Module        | . 16-5 |

| 16.3.2           | Data Flow to the I/O Module          | . 16-5 |

| 16.3.3           | Operating a Port as GPIO             | . 16-5 |

| 16.3.4           | Port Pull-Up and Pull-Down Resistors |        |

| 16.4             | Programming Model                    | . 16-6 |

| 16.4.1           | Port B Registers                     | . 16-6 |

| 16.4.1.          | 1 Port B Direction Register          | . 16-6 |

| 16.4.1.          | Port B Data Register                 | . 16-7 |

| 16.4.1.          | Port B Dedicated I/O Functions       | . 16-7 |

| 16.4.1.          | 8                                    |        |

| 16.4.1.          |                                      |        |

| 16.4.2           | Port C Registers                     |        |

| 16.4.2.          | <b>.</b>                             |        |

| 16.4.2.          | $\epsilon$                           |        |

| 16.4.2.          |                                      |        |

| 16.4.2.          |                                      |        |

| 16.4.2.          | $\boldsymbol{c}$                     |        |

| 16.4.3           | Port D Registers                     |        |

| 16.4.3.          | $\boldsymbol{\mathcal{E}}$           |        |

| 16.4.3.          | $\mathcal{E}$                        |        |

| 16.4.3.          |                                      |        |

| 16.4.3.          | 4 Port D Pull-Up Enable Register     | 16-14  |

| 16.4.3.5  | Port DASGEONE GISTER FREESCALE SEMICONDUCTOR, INC. 2005 | 16-14 |

|-----------|---------------------------------------------------------|-------|

| 16.4.3.6  | Port D Interrupt Mask Register                          |       |

| 16.4.3.7  | Port D Interrupt Status Register                        | 16-15 |

| 16.4.3.8  | Port D Interrupt Edge Register                          | 16-16 |

| 16.4.3.9  | Port D Interrupt Polarity Register                      |       |

| 16.4.4    | Port E Registers                                        |       |

| 16.4.4.1  | Port E Direction Register                               |       |

| 16.4.4.2  | Port E Data Register                                    | 16-17 |

| 16.4.4.3  | Port E Dedicated I/O Functions                          | 16-18 |

| 16.4.4.4  | Port E Pull-Up Enable Register                          | 16-18 |

| 16.4.4.5  | Port E Select Register                                  | 16-19 |

| 16.4.4.6  | Port E Interrupt Mask Register                          | 16-19 |

| 16.4.4.7  | Port E Interrupt Status Register                        | 16-20 |

| 16.4.4.8  | Port E Interrupt Edge Register                          | 16-20 |

| 16.4.4.9  | Port E Interrupt Polarity Register                      | 16-21 |

| 16.4.5    | Port F Registers                                        | 16-21 |

| 16.4.5.1  | Port F Direction Register                               | 16-22 |

| 16.4.5.2  | Port F Data Register                                    | 16-22 |

| 16.4.5.3  | Port F Dedicated I/O Functions                          | 16-23 |

| 16.4.5.4  | Port F Pull-Up Enable Register                          | 16-24 |

| 16.4.5.5  | Port F Select Register                                  |       |

| 16.4.5.6  | Port F Interrupt Mask Register                          |       |

| 16.4.5.7  | Port F Interrupt Status Register                        | 16-25 |

| 16.4.5.8  | Port F Interrupt Edge Register                          |       |

| 16.4.5.9  | Port F Interrupt Polarity Register                      |       |

| 16.4.6    | Port G Registers                                        |       |

| 16.4.6.1  | Port G Direction Register                               | 16-27 |

| 16.4.6.2  | Port G Data Register                                    | 16-27 |

| 16.4.6.3  | Port G Dedicated I/O Functions                          | 16-28 |

| 16.4.6.4  | Port G Operational Considerations                       | 16-28 |

| 16.4.6.5  | Port G Pull-Up Enable Register                          | 16-29 |

| 16.4.6.6  | Port G Select Register                                  |       |

| 16.4.6.7  | Port G Interrupt Mask Register                          | 16-30 |

| 16.4.6.8  | Port G Interrupt Status Register                        | 16-30 |

| 16.4.6.9  | Port G Interrupt Edge Register                          |       |

| 16.4.6.10 | Port G Interrupt Polarity Register                      | 16-31 |

| 16.4.7    | Port J Registers                                        | 16-32 |

| 16.4.7.1  | Port J Direction Register                               |       |

| 16.4.7.2  | Port J Data Register                                    | 16-33 |

| 16.4.7.3  | Port J Dedicated I/O Functions                          |       |

| 16.4.7.4  | Port J Pull-Up Enable Register                          |       |

| 16.4.7.5  | Port J Select Register                                  |       |

| 16.4.7.6  | Port J Interrupt Mask Register                          |       |

| 16.4.7.7  | Port J Interrupt Status Register                        | 16-35 |

| 16.4.7.8  | Port J Interrupt Edge Register                          | 16-36 |

| 16.4.7.9  | Port J Interrupt Polarity Register                      |       |

| 16.4.8    | Port K Registers                                        |       |

| 16.4.8.1  | Port KADGE CHIOTOR SISTER ESCALE SEMICONDUCTOR, INC. 2005 | 16-37 |

|-----------|-----------------------------------------------------------|-------|

| 16.4.8.2  | Port K Data Register                                      | 16-37 |

| 16.4.8.3  | Port K Dedicated I/O Functions                            | 16-38 |

| 16.4.8.4  | Port K Pull-Up Enable Register                            | 16-39 |

| 16.4.8.5  | Port K Select Register                                    |       |

| 16.4.8.6  | Port K Interrupt Mask Register                            |       |

| 16.4.8.7  | Port K Interrupt Status Register                          |       |

| 16.4.8.8  | Port K Interrupt Edge Register                            |       |

| 16.4.8.9  | Port K Interrupt Polarity Register                        |       |

| 16.4.9    | Port M Registers                                          |       |

| 16.4.9.1  | Port M Direction Register                                 |       |

| 16.4.9.2  | Port M Data Register                                      | 16-43 |

| 16.4.9.3  | Port M Dedicated I/O Functions                            | 16-43 |

| 16.4.9.4  | Port M Pull-Up Enable Register                            | 16-44 |

| 16.4.9.5  | Port M Select Register                                    | 16-45 |

| 16.4.9.6  | Port M Interrupt Mask Register                            | 16-45 |

| 16.4.9.7  | Port M Interrupt Status Register                          | 16-46 |

| 16.4.9.8  | Port M Interrupt Edge Register                            | 16-46 |

| 16.4.9.9  | Port M Interrupt Polarity Register                        | 16-47 |

| 16.4.10   | Port N Registers                                          | 16-47 |

| 16.4.10.1 | Port N Direction Register                                 | 16-48 |

| 16.4.10.2 | Port N Data Register                                      | 16-48 |

| 16.4.10.3 | Port N Dedicated I/O Functions                            | 16-49 |

| 16.4.10.4 | Port N Pull-Up Enable Register                            | 16-49 |

| 16.4.10.5 | Port N Select Register                                    | 16-50 |

| 16.4.10.6 | Port N Interrupt Mask Register                            | 16-50 |

| 16.4.10.7 | Port N Interrupt Status Register                          | 16-51 |

| 16.4.10.8 | Port N Interrupt Edge Register                            | 16-51 |

| 16.4.10.9 | Port N Interrupt Polarity Register                        | 16-52 |

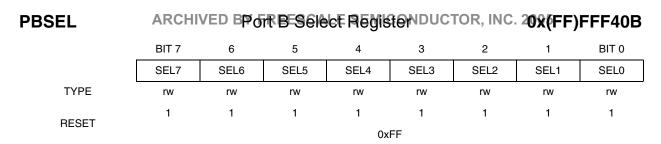

| 16.4.11   | Port P Registers                                          |       |

| 16.4.11.1 | Port P Direction Register                                 | 16-53 |

| 16.4.11.2 | Port P Data Register                                      | 16-53 |

| 16.4.11.3 | Port P Dedicated I/O Functions                            | 16-54 |

| 16.4.11.4 | Port P Pull-Up Enable Register                            |       |

| 16.4.11.5 | Port P Select Register                                    |       |

| 16.4.11.6 | Port P Interrupt Mask Register                            |       |

| 16.4.11.7 | Port P Interrupt Status Register                          | 16-56 |

| 16.4.11.8 | Port P Interrupt Edge Register                            |       |

| 16.4.11.9 | Port P Interrupt Polarity Register                        |       |

| 16.4.12   | Port R Registers                                          |       |

| 16.4.12.1 | Port R Direction Register                                 |       |

| 16.4.12.2 | Port R Data Register                                      |       |

| 16.4.12.3 | Port R Dedicated I/O Functions                            |       |

| 16.4.12.4 | Port R Pull-Up/Pull-Down Enable Register                  |       |

| 16.4.12.5 | Port R Select Register                                    |       |

| 16.4.12.6 | Port R Interrupt Mask Register                            |       |

| 16.4.12.7 | Port R Interrupt Status Register                          | 16-61 |

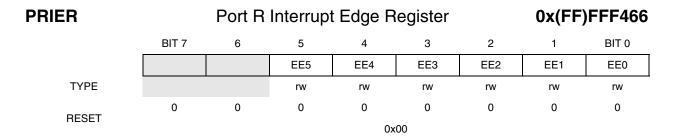

| 16.4.12.8            | Port RAMerrupt Edge Registe CALE SEMICONDUCTOR, INC. 2005 | 16-61 |

|----------------------|-----------------------------------------------------------|-------|

| 16.4.12.9            | Port R Interrupt Polarity Register                        | 16-62 |

| 011                  | 49                                                        |       |

| Chapte               | r 17<br>edia Card/Secure Digital Host Controller          |       |

| Wattille             | edia Card/Secure Digital Host Controller                  |       |

|                      | eatures                                                   |       |

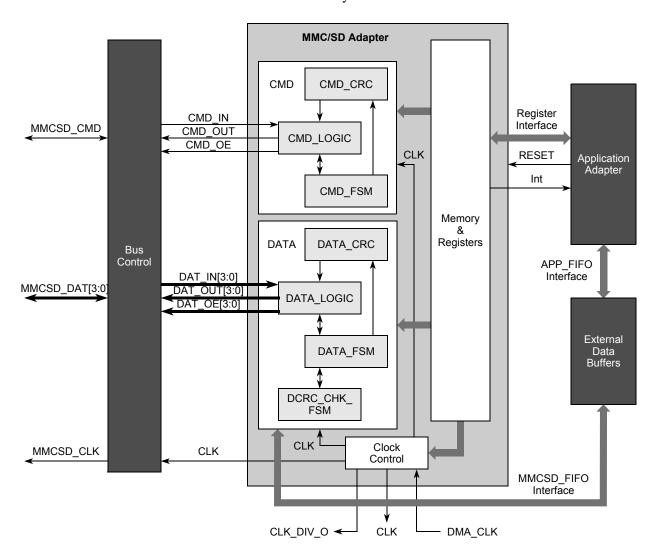

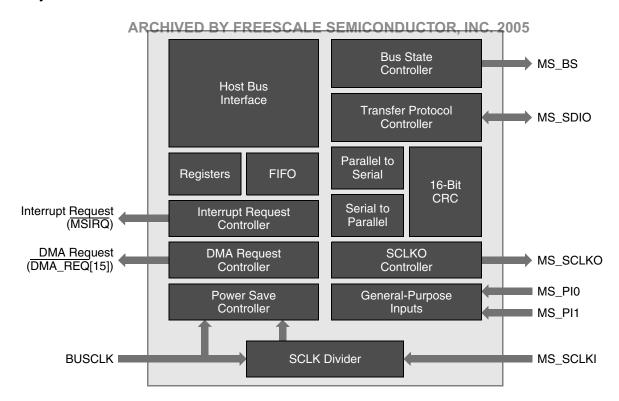

|                      | lock Diagram                                              |       |

|                      | MC/SD Host Controller Interface                           |       |

| 17.3.1               | Signal Description.                                       |       |

| 17.3.2               | MMC/SD Host Controller Interface I/O Multiplexing         |       |

|                      | unctional Blocks                                          |       |

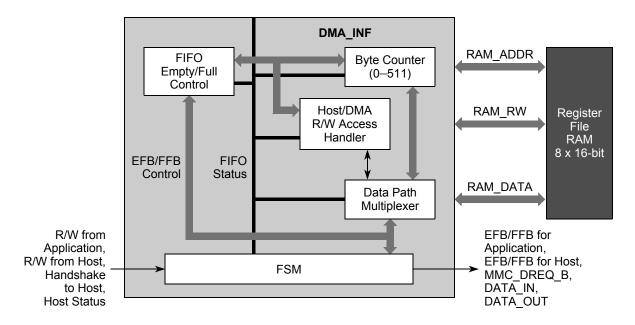

| 17.4.1               | FIFO and DMA Interface                                    |       |

| 17.4.2               | Card Error Detection                                      |       |

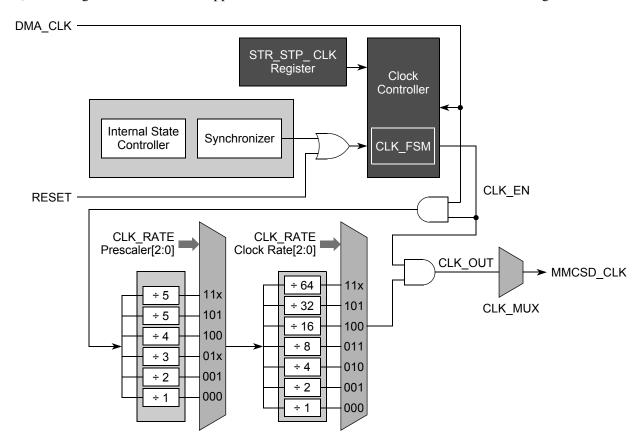

| 17.4.3               | System Clock Control                                      |       |

| 17.4.4               | MMC/SD Host Controller Interrupt Operation                |       |

|                      | unctional Example of MMC/SD Communication                 |       |

| 17.5.1               | Card Identification Mode                                  |       |

| 17.5.1.1             | Reset                                                     |       |

| 17.5.1.2             | Voltage Validation                                        |       |

| 17.5.1.3             | Card Registry                                             |       |

| 17.5.2               | Data Transfer Mode                                        |       |

| 17.5.2.1             | Block Access: Block Write and Block Read                  |       |

| 17.5.2.2             | Stream Access: Stream Write and Stream Read               |       |

| 17.5.2.3             | Erase: Group Erase and Sector Erase                       |       |

| 17.5.3               | Protection Management                                     |       |

| 17.5.3.1             | Card Internal Write Protection                            |       |

| 17.5.3.2             | Mechanical Write Protect Switch                           |       |

| 17.5.3.3             | Password Protection                                       |       |

| 17.5.4               | Card Status                                               |       |

| 17.5.5               | I/O Control (Interrupt Mode)                              |       |

| 17.5.6               | Application-Specific Command Handling                     |       |

|                      | ommands for MMC/SD                                        |       |

|                      | rogramming Model                                          |       |

| 17.7.1               | MMC/SD Host Register Set                                  |       |

| 17.7.2               | Register Descriptions                                     |       |

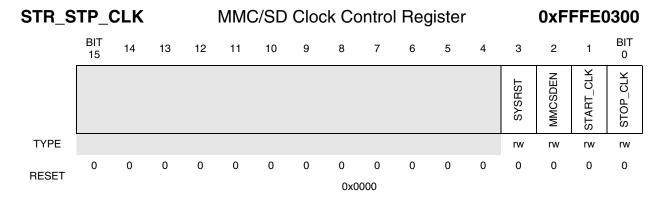

| 17.7.2.1             | MMC/SD Clock Control Register                             |       |

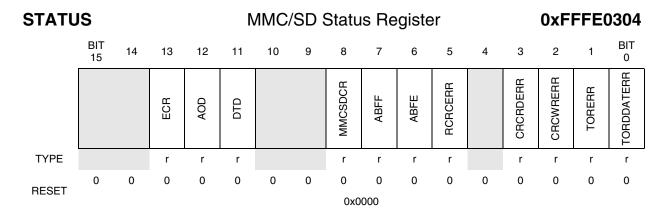

| 17.7.2.2             | MMC/SD Status Register                                    |       |

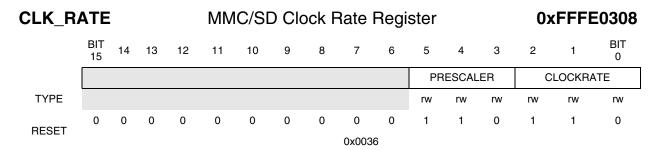

| 17.7.2.3<br>17.7.2.4 | MMC/SD Clock Rate Register                                |       |

| 17.7.2.4             | MMC/SD Response Time Out Register                         |       |

|                      | MMC/SD Response Time-Out Register                         |       |

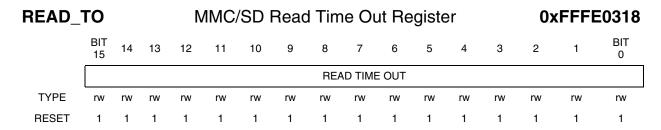

| 17.7.2.6<br>17.7.2.7 | MMC/SD Read Time-Out Register                             |       |

| 17.7.2.7             | MMC/SD Number of Blocks Pagister                          |       |

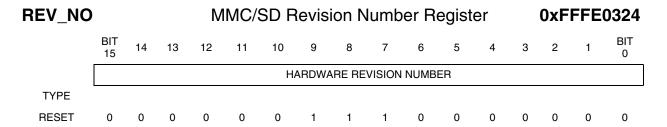

| 17.7.2.8             | MMC/SD Payision Number Pagister                           |       |

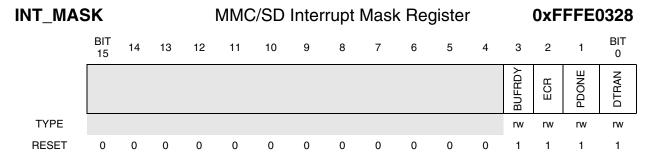

| 17.7.2.9             | MMC/SD Interrupt Mosk Pagister                            |       |

| 17.7.2.10            | MMC/SD Interrupt Mask Register                            |       |

| 17.7.2.11            | <u>-</u>                                                  |       |

| 11.1.4.14            | MINICISE INGINE AUGUNE REGISTER                           | 17-34 |

| 17.7.2.13 | MMC/SDC Howep Arguinent Register SEMICONDUCTOR, INC. 2005 | 17-34 |

|-----------|-----------------------------------------------------------|-------|

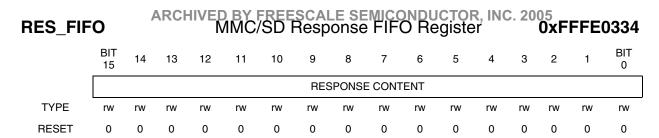

| 17.7.2.14 | MMC/SD Response FIFO Register                             |       |

| 17.7.2.15 | MMC/SD Buffer Access Register                             | 17-35 |

| 17.7.2.16 | MMC/SD Buffer Partial Full Register                       | 17-35 |

|           | <u> </u>                                                  |       |

| Chapter   | 18<br>Stick Host Controller                               |       |

| welliol y | Suck Host Controller                                      |       |

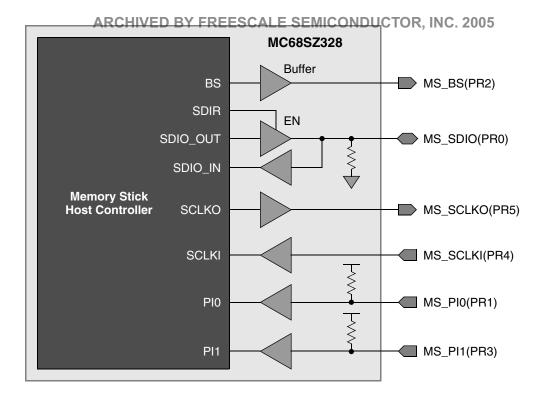

|           | ock Diagram                                               | 18-1  |

| 18.2 M    | emory Stick Interface                                     | 18-2  |

| 18.2.1    | Signal Descriptions                                       |       |

| 18.2.2    | Memory Stick Interface I/O Multiplexing                   |       |

|           | peration                                                  |       |

| 18.3.1    | Data FIFO Operation                                       | 18-5  |

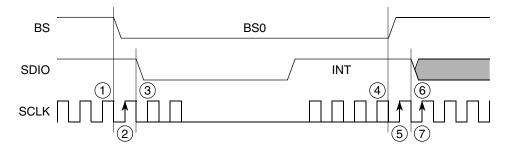

| 18.3.2    | Bus State Control Operation                               | 18-6  |

| 18.3.3    | MSHC Interrupt Operation                                  | 18-6  |

| 18.3.3.1  | Interrupt Sources                                         |       |

| 18.3.3.2  | SDIO Interrupt Operation                                  |       |

| 18.3.4    | Reset Operation                                           | 18-8  |

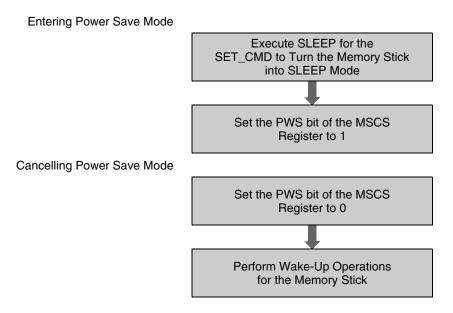

| 18.3.5    | Power Save Mode Operation                                 |       |

| 18.3.5.1  | Register Access During Power Save Mode                    | 18-9  |

| 18.3.5.2  | Register Access while MSHC Module is Disabled             | 18-10 |

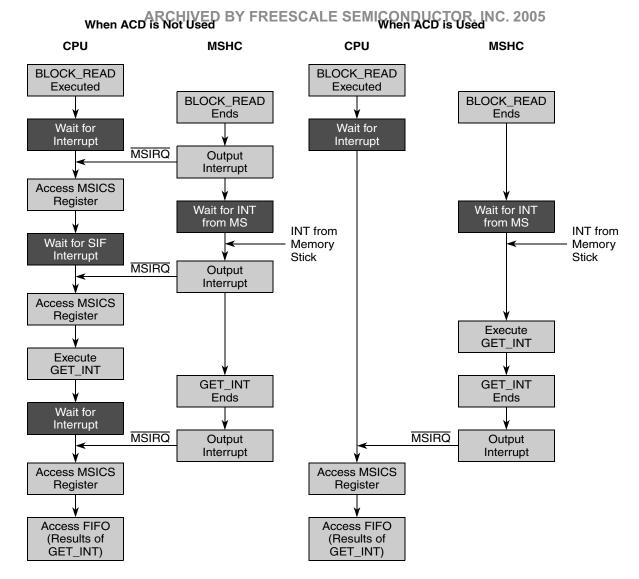

| 18.3.6    | Auto Command Function                                     |       |

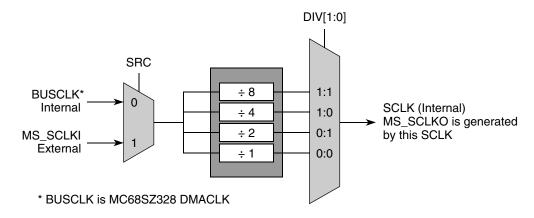

| 18.3.7    | Serial Clock Divider Operation                            |       |

| 18.3.8    | MC68SZ328 System-Level DMA Transfer Operation             |       |

| 18.4 Pr   | ogramming Model                                           | 18-13 |

| 18.4.1    | Memory Stick Host Register Set Summary                    |       |

| 18.4.2    | Memory Stick Command Register                             |       |

| 18.4.3    | Memory Stick Control/Status Register                      |       |

| 18.4.4    | Memory Stick Transmit FIFO Data Register                  |       |

| 18.4.5    | Memory Stick Receive FIFO Data Register                   |       |

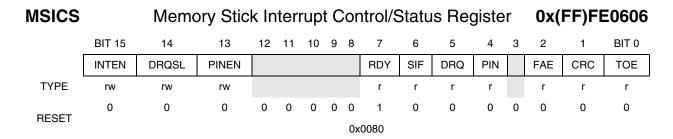

| 18.4.6    | Memory Stick Interrupt Control/Status Register            |       |

| 18.4.7    | Memory Stick Parallel Port Control/Data Register          | 18-21 |

| 18.4.8    | Memory Stick Control 2 Register                           |       |

| 18.4.9    | Memory Stick Auto Command Register                        | 18-23 |

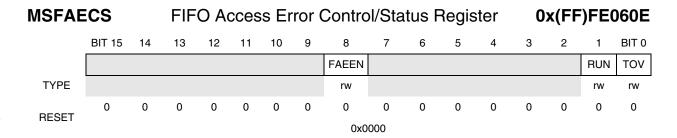

| 18.4.10   | FIFO Access Error Control/Status Register                 |       |

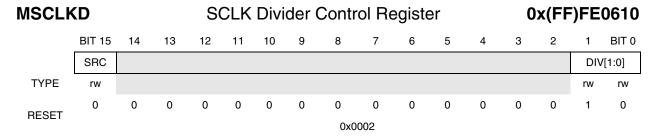

| 18.4.11   | SCLK Divider Control Register                             |       |

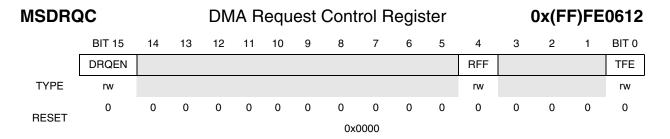

| 18.4.12   | DMA Request Control Register                              |       |

| 18.5 Pr   | ogrammer's Reference                                      |       |

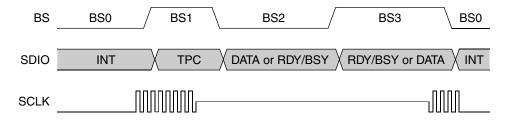

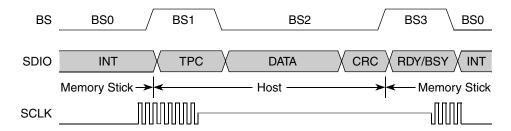

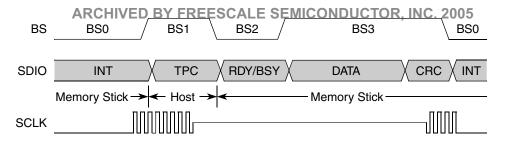

| 18.5.1    | Memory Stick Serial Interface Overview                    |       |

| 18.5.2    | Protocol                                                  |       |

| 18.5.2.1  | Write Packets                                             |       |

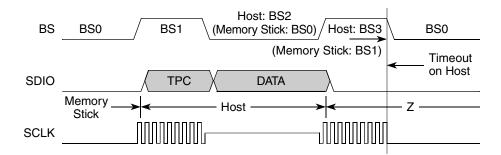

| 18.5.2.2  | Read Packets                                              |       |

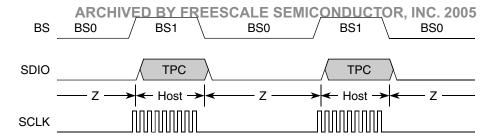

| 18.5.3    | Transfer Protocol Command (TPC)                           | 18-29 |

| 18.5.4    | Protocol Errors                                           |       |

| 18.5.4.1  | Overview                                                  | 18-30 |

| 18.5.4.2  | Two State Access Mode Error Factors                       | 18-32 |

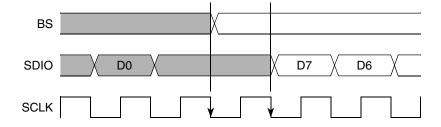

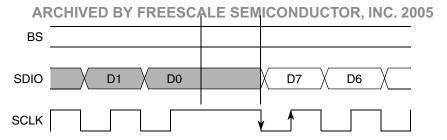

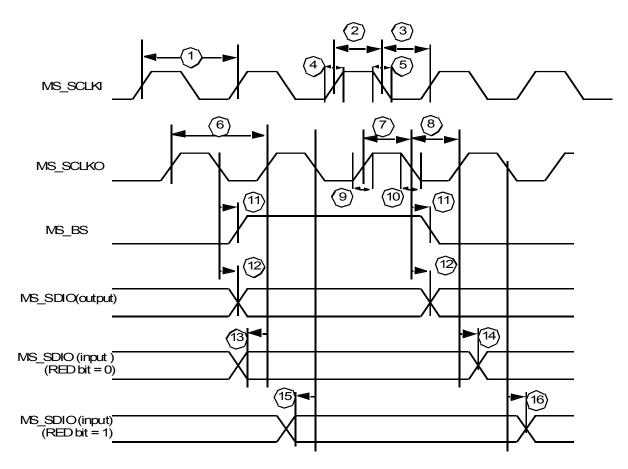

| 18.5.5    | Signal Timing                                             | 18-32 |

|           |                                                           |       |

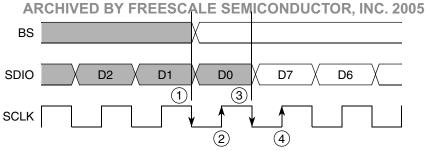

| 18.5.5.1 Timin@RCHIVED.BY.FREESCALE.SEMICONDUCTOR, INC. 2005   | . 18-32 |

|----------------------------------------------------------------|---------|

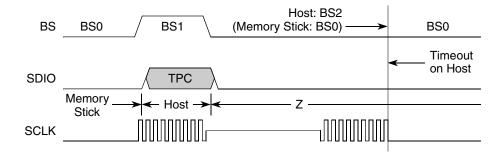

| 18.5.5.2 Bus State Extension                                   |         |

| 18.5.5.3 Data Transfer Extension                               | . 18-33 |

| Charter 10                                                     |         |

| Chapter 19 Universal Asynchronous Receiver/Transmitter 1 and 2 |         |

| ·                                                              |         |

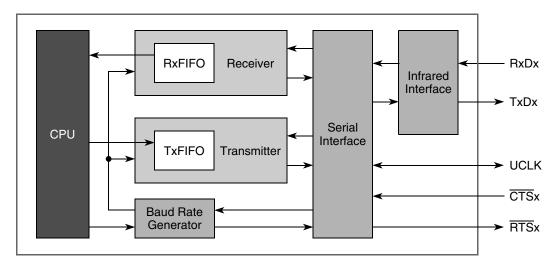

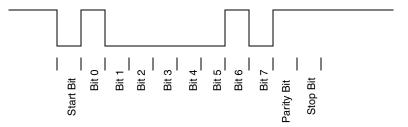

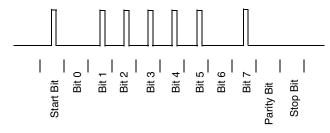

| 19.1 Introduction to the UARTs                                 |         |

| 19.2 Serial Operation                                          |         |

| 19.2.1 NRZ Mode                                                |         |

| 19.2.2 IrDA Mode                                               |         |

| 19.2.3 Serial Interface Signals                                |         |

| 19.3 UART Operation.                                           |         |

| 19.3.1 Transmitter Operation                                   |         |

| 19.3.1.1 Tx FIFO Buffer Operation                              |         |

| 19.3.1.2 CTS Signal Operation                                  |         |

| 19.3.2 Receiver Operation                                      |         |

| 19.3.2.1 Rx FIFO Buffer Operation                              |         |

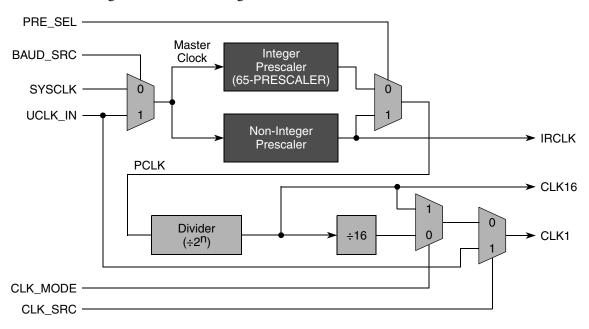

| 19.3.3 Baud Rate Generator Operation                           |         |

| 19.3.3.1 Divider                                               |         |

| 19.3.3.2 Non-Integer Prescaler                                 |         |

| 19.3.3.3 Integer Prescaler                                     |         |

| 19.4 UART Direct Memory Access Operation                       |         |

| 19.4.1 DMA Configuration Options                               |         |

| 19.4.2 DMA Configuration Procedure                             |         |

| 19.5 Programming Model                                         |         |

| 19.5.1 UART 1 Status/Control Register                          |         |

| 19.5.2 UART 1 Baud Control Register                            |         |

| 19.5.3 UART 1 Receiver Register                                |         |

| 19.5.4 UART 1 Transmitter Register                             |         |

| 19.5.5 UART 1 Miscellaneous Register                           |         |

| 19.5.6 UART 1 Non-Integer Prescaler Register                   |         |

| 19.5.7 UART 1 FIFO Level Marker Interrupt Register             |         |

| 19.5.8 UART 2 Status/Control Register                          |         |

| 19.5.9 UART 2 Baud Control Register                            |         |

| 19.5.10 UART 2 Receiver Register                               |         |

| 19.5.11 UART 2 Transmitter Register                            |         |

| 19.5.12 UART 2 Miscellaneous Register                          |         |

| 19.5.13 UART 2 Non-Integer Prescaler Register                  |         |

| 19.5.14 UART2 FIFO Level Marker Interrupt Register             |         |

| 19.6 UART Register Set                                         | . 19-31 |

| Chapter 20                                                     |         |

| Configurable Serial Peripheral Interface                       |         |

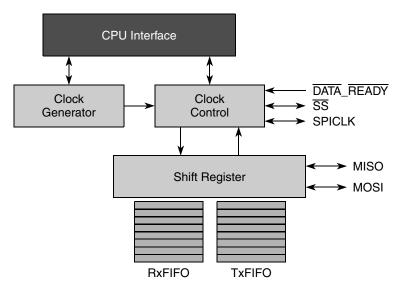

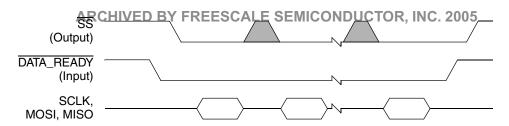

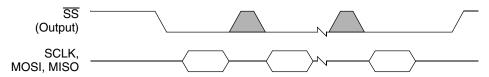

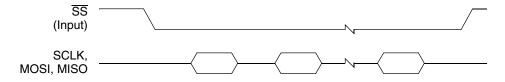

| 20.1 CSPI Overview                                             | 20-1    |

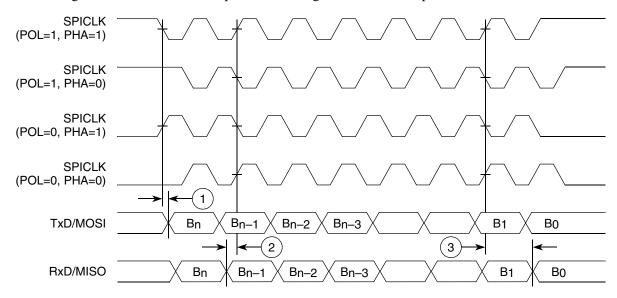

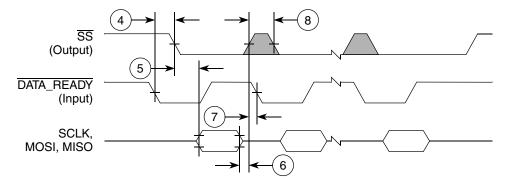

| 20.2 CSPI Operation                                            | 20-2    |

| 20.2.1 Using CSPI as Master                                    | 20-2    |

|                                                                |         |

| 20.2.2  | Using CSPRasisnate BY FREESCALE SEMICONDUCTOR, INC. 2005 | 20-2  |

|---------|----------------------------------------------------------|-------|

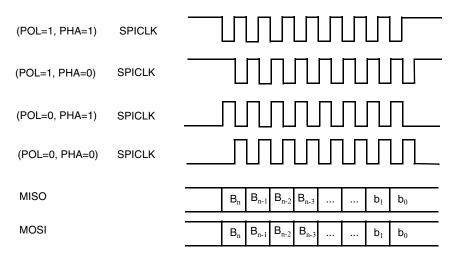

| 20.2.3  | CSPI Phase and Polarity Configurations                   | 20-2  |

| 20.2.4  | SPI Signals                                              | 20-3  |

| 20.3    | CSPI Programming Model                                   |       |

| 20.3.1  | CSPI Receive Data Register                               |       |

| 20.3.2  | CSPI Transmit Data Register                              |       |

| 20.3.3  | CSPI Control/Status Register                             |       |

| 20.3.4  | CSPI Interrupt Control/Status Register                   |       |

| 20.3.5  | CSPI Test Register                                       |       |

| 20.3.6  | e                                                        |       |

| 20.3.0  | CSPI Sample Period Control Register                      |       |

| 20.3.7  | DMA Control Register                                     | 20-11 |

| Chap    | ter 21                                                   |       |

|         | Device Module                                            |       |

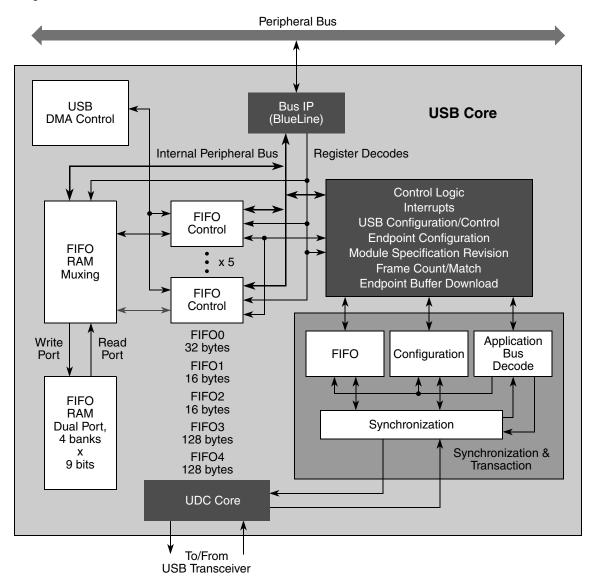

| 21.1    | Introduction                                             | 21-1  |

| 21.2    | Features                                                 | 21-1  |

| 21.3    | Module Components                                        |       |

| 21.3.1  | Universal Serial Bus Device Controller Core (UDC)        |       |

| 21.3.2  | Synchronization and Transaction Decoder                  |       |

| 21.3.3  | Endpoint FIFO Architecture                               |       |

| 21.3.4  | Control Logic                                            |       |

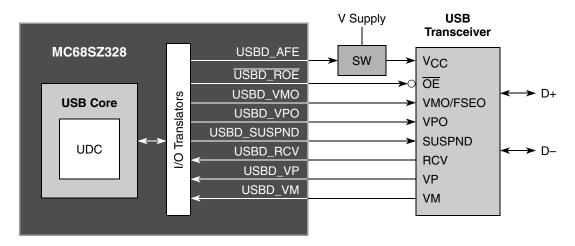

| 21.3.4  | USB Transceiver Interface                                |       |

| 21.4.1  | Signal Description.                                      |       |

| 21.4.1  | Interrupt Services                                       |       |

| 21.5.1  | USB General Interrupts                                   |       |

| 21.5.1  | <u> </u>                                                 |       |

| 21.5.2  | Endpoint Interrupts                                      |       |

| 21.5.5  | Interrupts, Missed Interrupts, and the USB               |       |

|         | Programming Model                                        |       |

| 21.6.1  | USB Register Set Summary                                 |       |

| 21.6.2  | Register Descriptions                                    |       |

| 21.6.2. |                                                          |       |

| 21.6.2. | = 002 Spoonioni itolonise i tume el itogistori           |       |

| 21.6.2. | $\boldsymbol{c}$                                         |       |

| 21.6.2. | $\epsilon$                                               |       |

| 21.6.2. | $\varepsilon$                                            |       |

| 21.6.2. | $\mathcal{E}$                                            |       |

| 21.6.2. |                                                          |       |

| 21.6.2. |                                                          |       |

| 21.6.2. | $\mathcal{C}$                                            |       |

| 21.6.2. |                                                          |       |

| 21.6.2. | i E                                                      |       |

| 21.6.2. |                                                          |       |

| 21.6.2. | USB Endpoint n Interrupt Mask Register                   | 21-26 |

| 21.6.2. | 14 USB Endpoint n FIFO Data Register                     | 21-27 |

| 21.6.2. | USB Endpoint n FIFO Status Register                      | 21-28 |

| 21.6.2. | •                                                        |       |

| 21.6.2. |                                                          |       |

|         | -                                                        |       |

| 21.6.2.18                | USB Entipoint Filast Write France Pointer Register TOR, INC. 2005 | 21-33 |

|--------------------------|-------------------------------------------------------------------|-------|

| 21.6.2.19                | USB Endpoint n FIFO Alarm Register                                | 21-34 |

| 21.6.2.20                | USB Endpoint n FIFO Read Pointer Register                         | 21-35 |

| 21.6.2.21                | USB Endpoint n FIFO Write Pointer Register                        |       |

| 21.7 Pro                 | grammer's Reference                                               |       |

| 21.7.1                   | Device Initialization                                             |       |

| 21.7.2                   | Configuration Download                                            |       |

| 21.7.3                   | USB Endpoint to FIFO Mapping                                      |       |

| 21.7.3.1                 | USB Interrupt Register                                            |       |

| 21.7.3.2                 | Endpoint Registers                                                |       |

| 21.7.3.3                 | Enable the Device                                                 |       |

| 21.7.4                   | Exception Handling                                                |       |

| 21.7.4.1                 | Unable to Complete Device Request                                 |       |

| 21.7.4.2                 | Aborted Device Request                                            |       |

| 21.7.4.3                 | Unable to Fill or Empty FIFO Due to Temporary Problem             |       |

| 21.7.4.4                 | Catastrophic Error                                                |       |

|                          | a Transfer Operations                                             |       |

| 21.8.1                   | USB Packets                                                       |       |

| 21.8.1.1                 | Short Packets.                                                    |       |

| 21.8.1.2                 | Sending Packets                                                   |       |

| 21.8.1.2                 | Receiving Packets                                                 |       |

| 21.8.1.3                 |                                                                   |       |

| 21.8.1.4                 | Programming the FIFO Controller                                   |       |

|                          | USB Transfers                                                     |       |

| 21.8.2.1<br>21.8.2.2     | Data Transfers to the Host                                        |       |

|                          | Data Transfers to the Device                                      |       |

|                          | tet Operation                                                     |       |

| 21.9.1                   | Hard Reset.                                                       |       |

| 21.9.2                   | USB Software Reset                                                |       |

| 21.9.3                   | UDC Reset                                                         |       |

| 21.9.4                   | USB Reset Signalling                                              | 21-46 |

| Observator               | 00                                                                |       |

| Chapter I <sup>2</sup> C | 22                                                                |       |

| I-C                      |                                                                   |       |

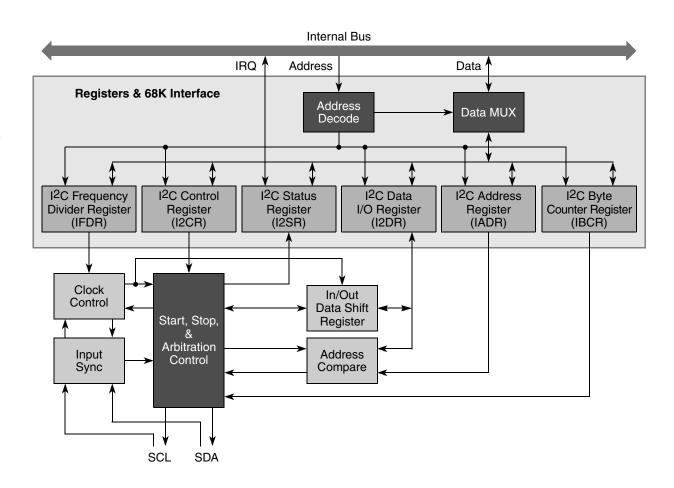

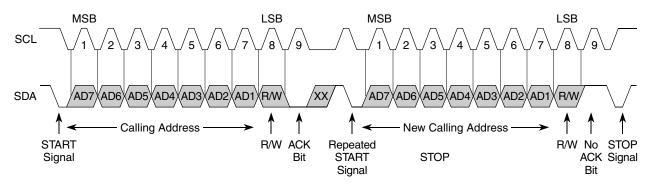

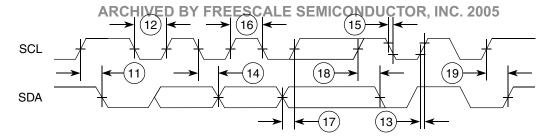

| 22.1 Ove                 | erview                                                            | 22-1  |

|                          | Features                                                          |       |

| •                        | System Configuration.                                             |       |

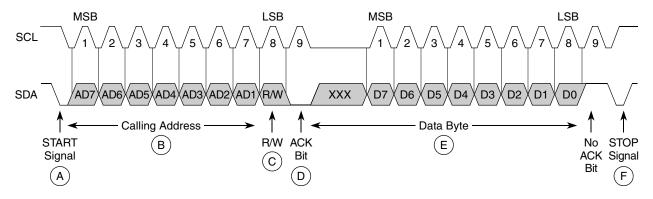

| _                        | Protocol                                                          |       |

| 22.4.1                   | Arbitration Procedure                                             |       |

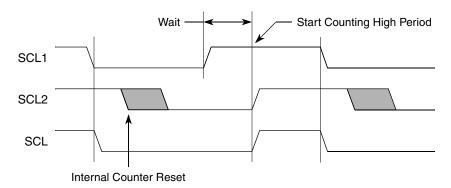

| 22.4.2                   | Clock Synchronization                                             |       |

| 22.4.3                   | Handshaking                                                       |       |

| 22.4.4                   | Clock Stretching                                                  |       |

|                          | gramming Modelgramming Model                                      |       |

|                          |                                                                   |       |

|                          | I <sup>2</sup> C Address Register (IADR)                          |       |

|                          | I <sup>2</sup> C Frequency Divider Register (IFDR)                |       |

|                          | I <sup>2</sup> C Control Register (I2CR)                          |       |

| 22.5.4                   | I <sup>2</sup> C Status Register (I2SR)                           |       |

| 22.5.5                   | I <sup>2</sup> C Data I/O Register (I2DR)                         | 22-11 |

| 22.5.6 I <sup>2</sup> C Byte Countel/Register (TBCR) ALE SEMICONDUCTOR, INC. 2005                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 22-11                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

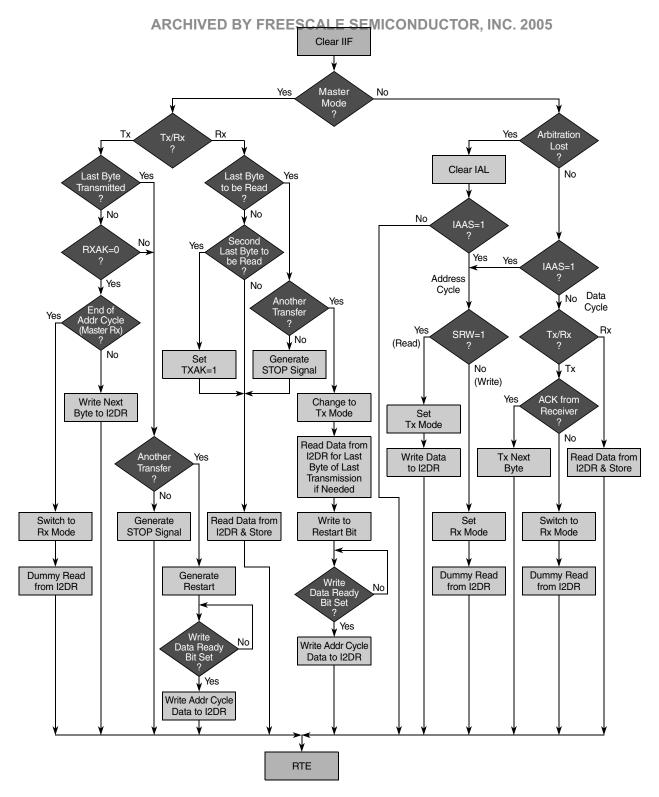

| 22.6 I <sup>2</sup> C Programming Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                      |

| 22.6.1 Initialization Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                      |

| 22.6.2 Generation of START                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 22-12                                                                                |

| 22.6.3 Post-Transfer Software Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22-12                                                                                |

| 22.6.4 Generation of STOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                      |

| 22.6.5 Generation of Repeated START                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                      |

| 22.6.6 Slave Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 22-13                                                                                |

| 22.6.7 Arbitration Lost                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                      |

| Chapter 23 Bootstrap Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                      |

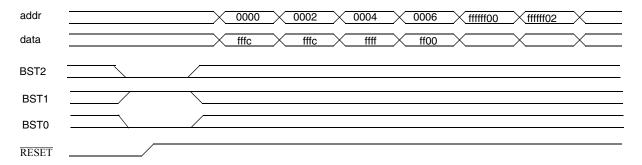

| 23.1 Bootstrap Mode Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                      |

| 23.1.1 Entering Bootstrap Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                      |

| 23.1.2 Bootstrap Record Types and Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                      |

| 23.1.2.1 Execution B-Record                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                      |

| 23.1.2.2 Data B-Record                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                      |

| 23.1.3 Setting Up the RS-232 Terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                      |

| 23.1.4 Changing the Speed of Communication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23-3                                                                                 |

| 23.1.5 Application Programming Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23-4                                                                                 |

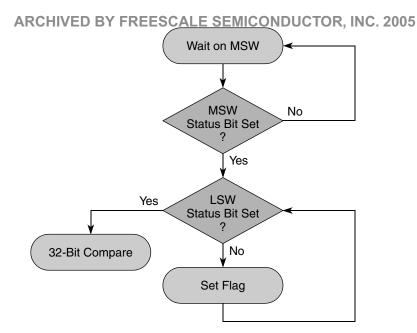

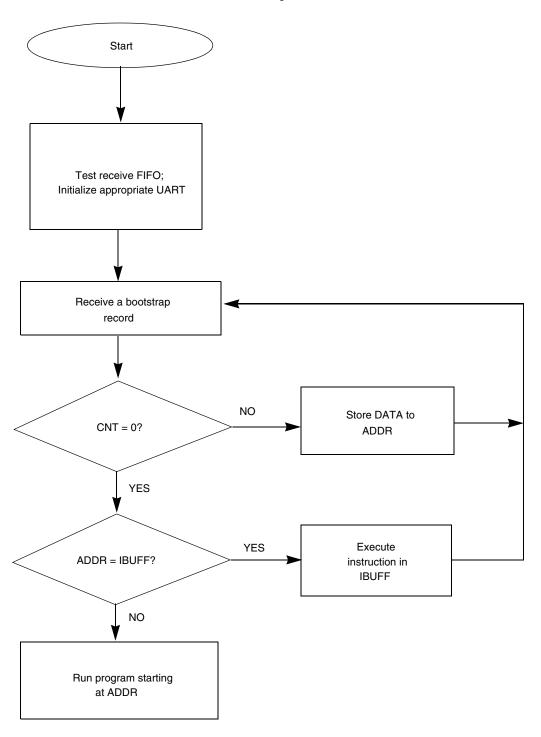

| 23.2 Bootloader Flowchart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 23-5                                                                                 |