# **C-5 Network Processor Architecture Guide**

C-5 NP Do Release

C-Port Corporation 120 Water Street N. Andover, MA 01845

www.cportcorp.com

**Copyright** © **2001 C-Port Corporation.** All rights reserved. No part of this documentation may be reproduced in any form or by any means or used to make any derivative work (such as translation, transformation, or adaptation) without written permission from C-Port Corporation.

C-Port Corporation reserves the right to revise this documentation and to make changes in content from time to time without obligation on the part of C-Port Corporation to provide notification of such revision or change.

C-Port Corporation provides this documentation without warranty, term, or condition of any kind, either implied or expressed, including, but not limited to, the implied warranties, terms or conditions of merchantability, satisfactory quality, and fitness for a particular purpose. C-Port may make improvements or changes in the product(s) and/or the program(s) described in this documentation at any time.

Unless otherwise indicated, C-Port registered trademarks are registered in the United States and may or may not be registered in other countries.

C-5, C-Port, the C-Port logo, and C-Ware are trademarks of C-Port Corporation.

#### Other Trademarks

Adobe and Acrobat are registered trademarks of Adobe Systems, Inc. DigitalDNA and The Heart of Smart are trademarks and Motorola is a registered trademark of Motorola, Inc. Microsoft, Windows, and Windows NT are registered trademarks of Microsoft Corporation. MIPS is a trademark of MIPS Technologies, Inc. Pentium is a registered trademark of Intel Corporation. PowerPC is a trademark of International Business Machines Corporation and used under license therefrom. Solaris is a trademark of Sun Microsystems, Inc. VxWorks, Tornado, and Wind River Systems are registered trademarks or service marks of Wind River Systems, Inc. TeraChannel is a registered trademark of Power X Networks, Inc.PRIZMA-E and PRIZMA-EP are trademarks of IBM, Inc. All other company and product names may be trademarks of their respective companies.

#### **Document Part Number and Publication Date**

Part Number: C5NPD0-AG/D

May 31, 2001

### **Contents**

| About This Guide                       |    |

|----------------------------------------|----|

| Guide Overview                         | 35 |

| Using C-Port Electronic Documents      |    |

| Guide Conventions                      |    |

| Revision History                       |    |

| Related User Documentation             |    |

| Introduction                           |    |

| Chapter Overview                       |    |

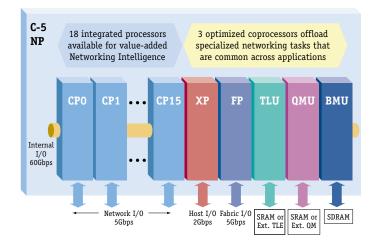

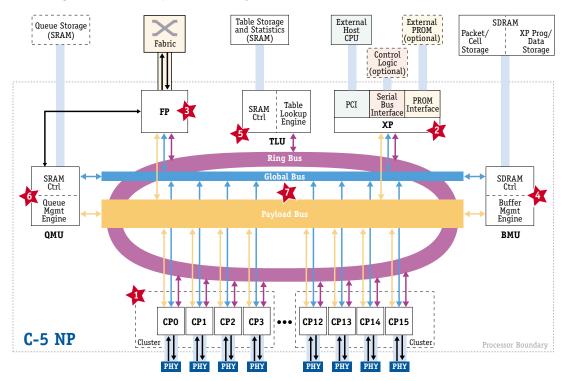

| C-5 NP Architecture Overview           | 42 |

| Highly-Integrated Architecture         | 42 |

| C-5 NP Modes of Operation              | 43 |

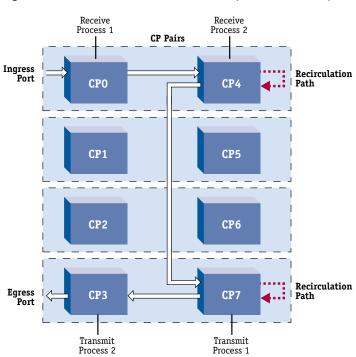

| Single Channel Mode                    | 43 |

| Pipeline Channel Mode                  | 43 |

| Aggregate Channel Mode                 | 43 |

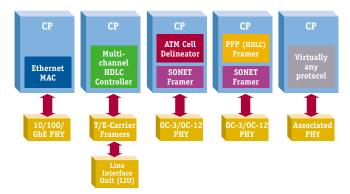

| C-5 NP Supported Interfaces            | 43 |

| Major Components of the C-5 NP         | 44 |

| C-5 NP Interconnect Components         | 45 |

| Other Supported Features               | 45 |

| C-5 NP Block Diagram and Flow Process  | 46 |

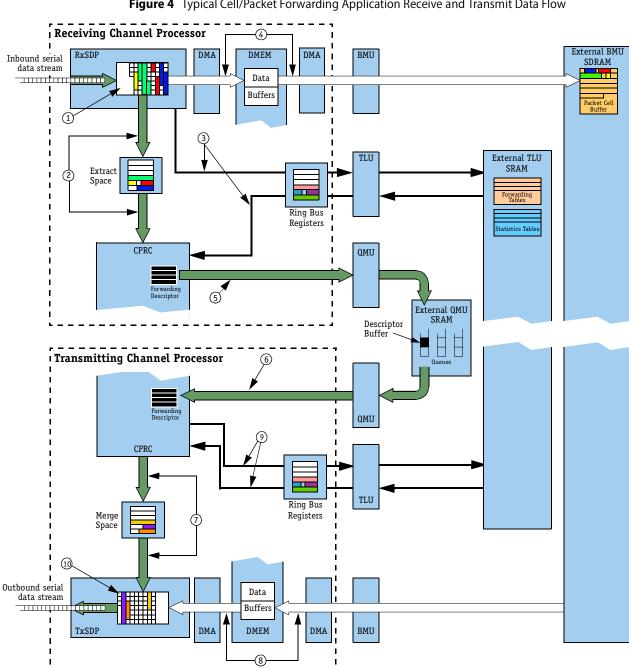

| Cell and Packet Forwarding Overview    | 47 |

| Receiving Packets                      | 47 |

| Transmitting Packets                   | 48 |

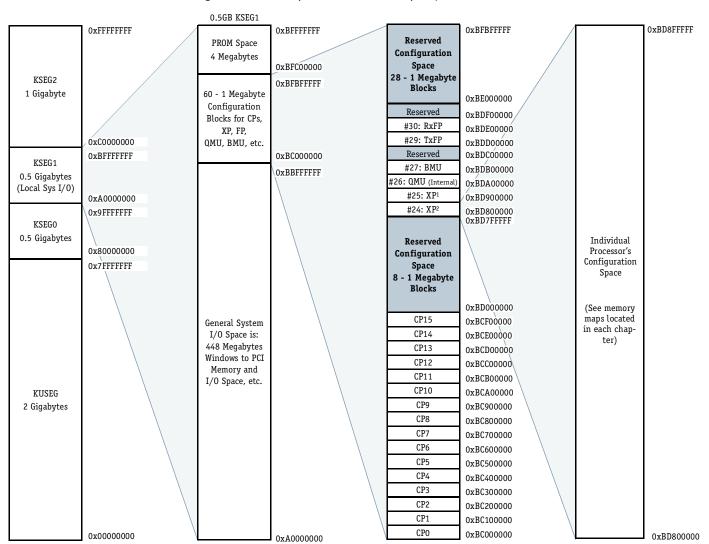

| C-5 NP Address Mapping                 |    |

| Configuration Register Definitions     |    |

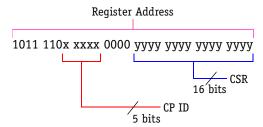

| Processor Base Address Offsets         | 52 |

| Configuration Register Address Offsets | 53 |

|                                        |    |

| Chapter 2 | Channel Processors                                               |      |

|-----------|------------------------------------------------------------------|------|

|           | Chapter Overview                                                 | . 55 |

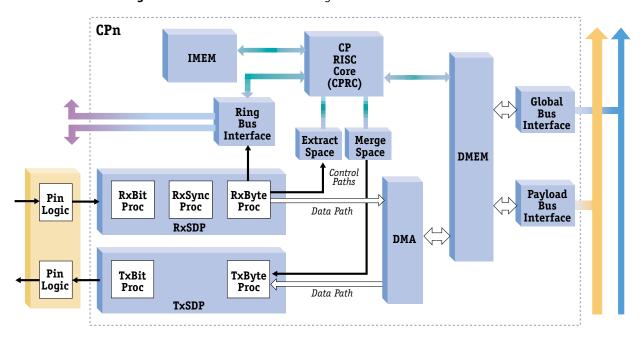

|           | Channel Processors (CPs) Overview                                | . 56 |

|           | CP Major Components                                              | . 56 |

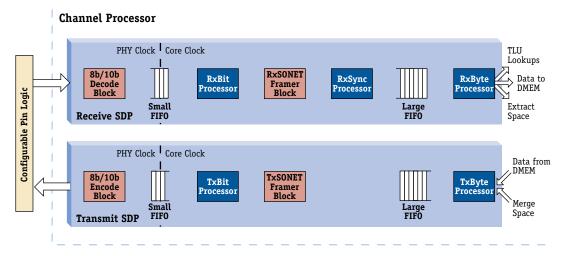

|           | Serial Data Processors (SDPs) Overview                           | . 58 |

|           | Supported External Interfaces                                    | . 58 |

|           | SDPs Functions                                                   | . 59 |

|           | SDPs Major Components                                            | . 61 |

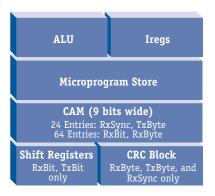

|           | Common Components of the Programmable Processors                 | . 62 |

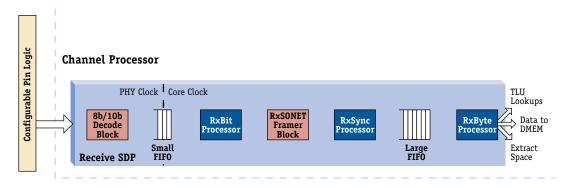

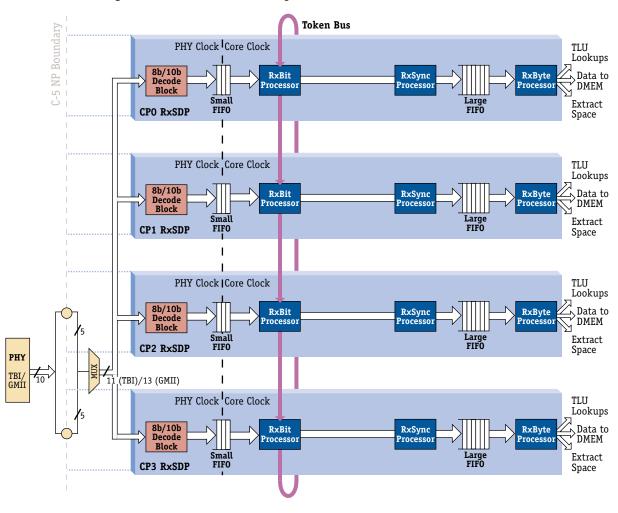

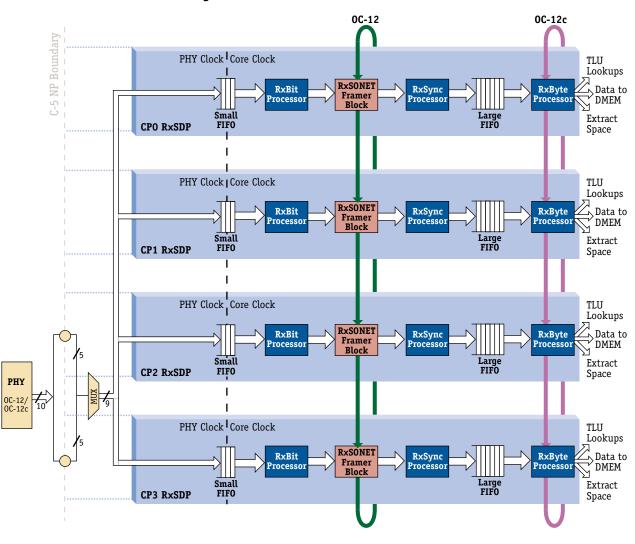

|           | RxSDP Detail Operations                                          | . 64 |

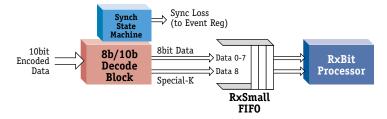

|           | 8b/10b Decode Configurable Logic Block                           | . 64 |

|           | RxSmallFIFO Configurable Logic Block                             | . 65 |

|           | RxBit Programmable Processor                                     | . 65 |

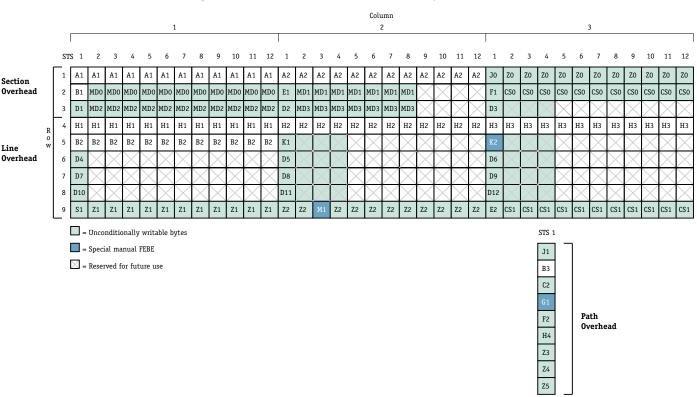

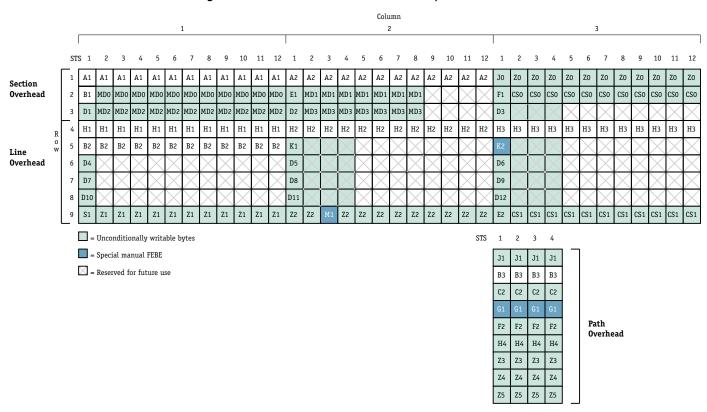

|           | RxSONET Framer Configurable Logic Block                          | . 66 |

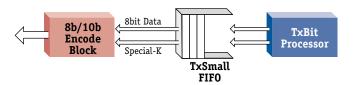

|           | RxSync Programmable Processor                                    | . 66 |

|           | RxLargeFIFO Configurable Logic Block                             | . 67 |

|           | RxByte Programmable Processor                                    | . 67 |

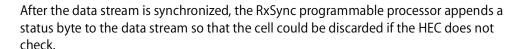

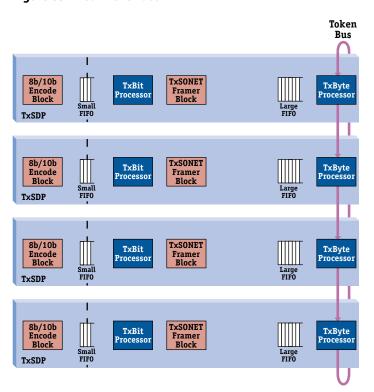

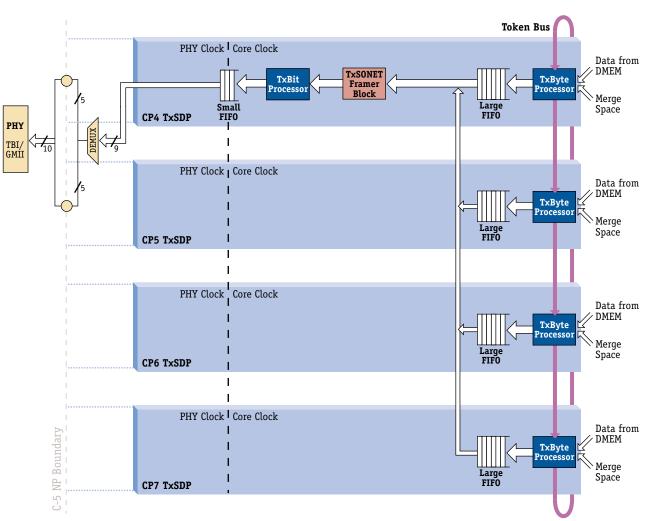

|           | TxSDP Detail Operations                                          | . 68 |

|           | TxByte Programmable Processor                                    | . 68 |

|           | TxLargeFIFO Configurable Logic Block and Options                 | . 69 |

|           | Automatic Idle Cell and PPP Flag Insertion Option                | . 69 |

|           | Transmit FIFO High Water Mark Option                             | . 69 |

|           | TxSONET Framer Configurable Logic Block                          | . 70 |

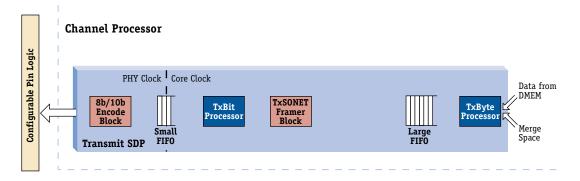

|           | TxBit Programmable Processor                                     | . 71 |

|           | TxSmallFIFO Configurable Logic Block                             | . 71 |

|           | 8b/10b Encode Configurable Logic Block                           | . 72 |

|           | Configuration for Recirculation Operations Using RxSDP and TxSDP | . 72 |

|           | CP RISC (CPRC) Overview                                          | . 75 |

|           | RISC Instruction Set Supported                                   | . 75 |

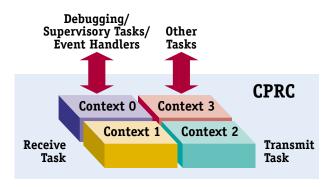

|           | Fast Context Switching Configuration Using the CPRC              | . 77 |

|           | Fast Context Switching Detail Operations                         | . 78 |

|           | Interrupts                                                       | . 79 |

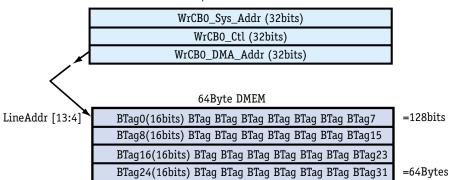

|           | CP Memory (IMEM and DMEM)                                        | . 80 |

|           | Instruction Memory (IMEM)                                        | . 80 |

|           | Data Memory (DMEM)                                               | . 81 |

|           | CP Memory Interface Transactions                                 | . 82 |

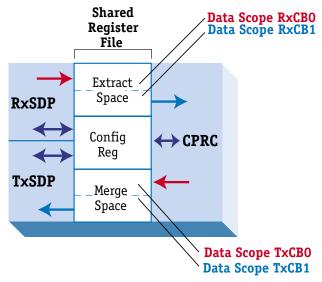

|           | DataScope Purpose                                                | . 85 |

|           |                                                                  |      |

|           | CP Configuration Space                                        | 87  |

|-----------|---------------------------------------------------------------|-----|

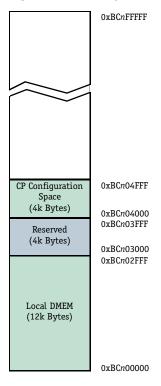

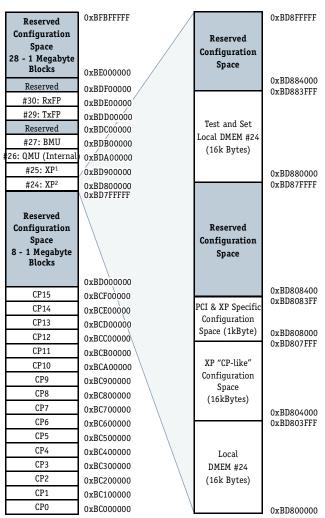

|           | Address Mapping of the CPs                                    | 87  |

|           | Understanding CP Functions                                    | 89  |

|           | Extract Space                                                 | 89  |

|           | Merge Space                                                   | 90  |

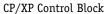

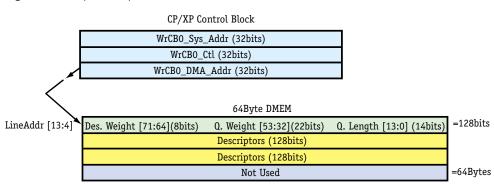

|           | Control Block Registers                                       |     |

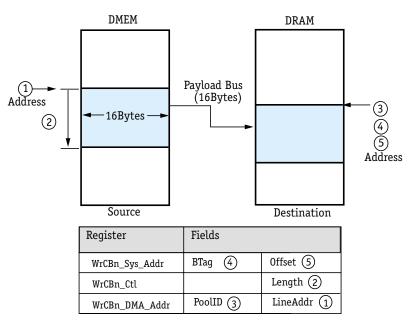

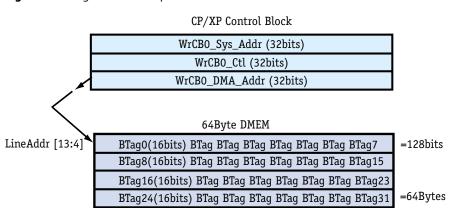

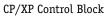

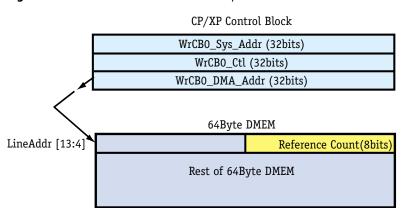

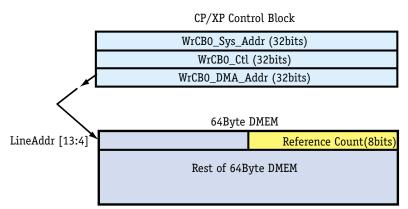

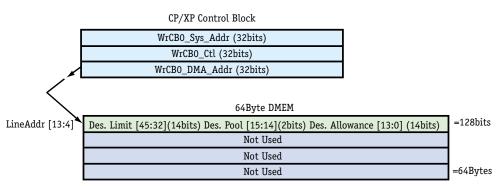

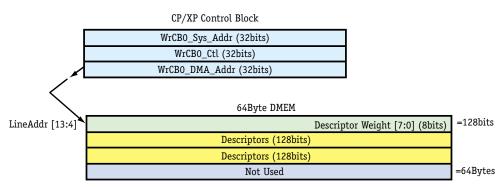

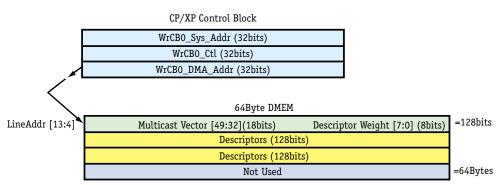

|           | Write Control Blocks (WrCB0_, WrCB1_)                         |     |

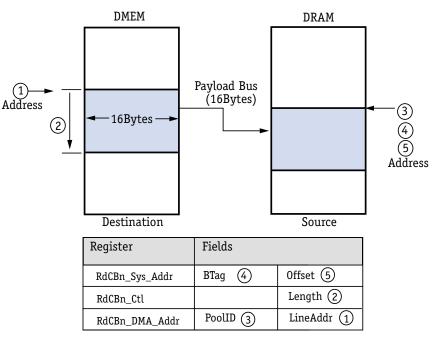

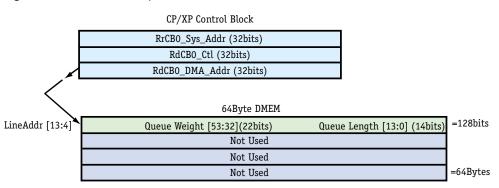

|           | Read Control Blocks (RdCB0_, RdCB1_)                          |     |

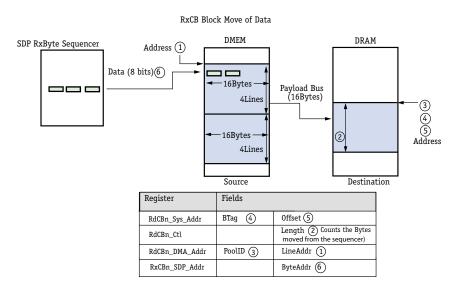

|           | SDP RxByte Processor Receive Control Blocks (RxCB0_, RxCB1_)  |     |

|           | SDP TxByte Processor Transmit Control Block (TxCB0_, TxCB1_)  |     |

|           | Ring Bus Registers                                            |     |

|           | Ring Bus Transmit (Tx) Messages Registers                     |     |

|           | Ring Bus (Rx) Receive Message Registers                       |     |

|           | Ring Bus Receive (Rx) Response Registers                      |     |

|           | SDP Control and Status Registers                              |     |

|           | Miscellaneous Control Registers                               |     |

|           | Event Registers                                               |     |

|           | Interrupt Access                                              |     |

|           | Queue Status Registers                                        | 113 |

|           | Cycle Counter                                                 | 114 |

|           | Event Timer                                                   | 114 |

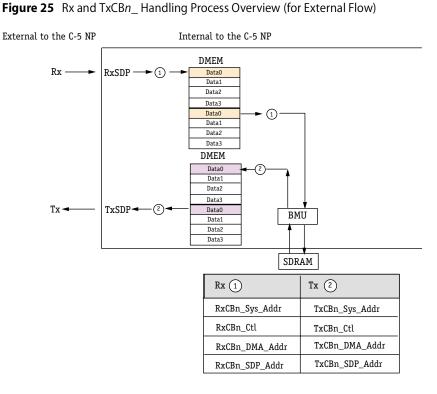

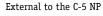

|           | Understanding Block Moves of Data                             | 115 |

|           | External Handling Overview                                    | 115 |

|           | Internal Handling Overview                                    | 116 |

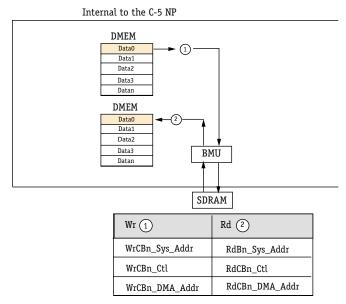

|           | Using Multi-Use Control Blocks to Achieve Different Functions | 117 |

|           |                                                               |     |

| CHAPTER 3 | Executive Processor                                           |     |

|           | Chapter Overview                                              |     |

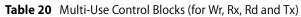

|           | Executive Processor (XP) Overview                             |     |

|           | XP Major Components                                           |     |

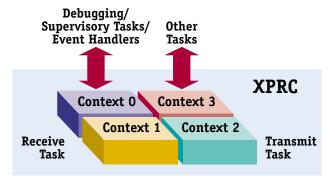

|           | XP RISC (XPRC) Overview                                       |     |

|           | XPRC Instruction Set                                          |     |

|           | XPRC Registers                                                |     |

|           | Context Switching                                             |     |

|           | Interrupts                                                    |     |

|           | Hardware Programming Resources                                |     |

|           | Event Registers                                               |     |

|           | XP Memory (IMEM and DMEM)                                     | 130 |

|           | Instruction Memory                                            | 130 |

| Data Memory                                    | 130 |

|------------------------------------------------|-----|

| SDRAM                                          | 130 |

| IROM                                           | 131 |

| XP Supported Interfaces                        | 132 |

| PCI Bus Interface                              | 132 |

| PCI Access to C-5 NP Physical Address Space    | 133 |

| C-5 NP Access to PCI Address Space             | 133 |

| PCI Registers                                  | 134 |

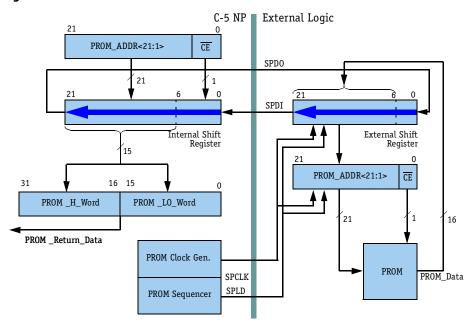

| PROM Interface                                 | 134 |

| Serial Bus Interface                           | 136 |

| C-5 NP Interface Options for Initialization    | 137 |

| Using the PCI Interface Initialization Option  | 137 |

| Using the PROM Interface Initialization Option | 137 |

| Other XP Interfaces                            | 138 |

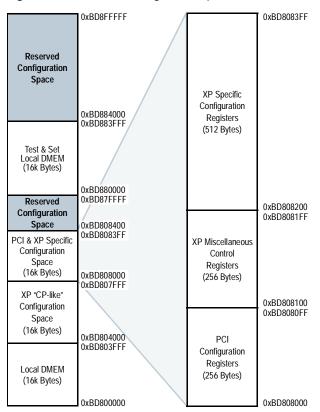

| XP Configuration Space                         | 140 |

|                                                |     |

| Fabric Processor                               |     |

| Chapter Overview                               | 145 |

| Fabric Processor (FP) Overview                 | 146 |

| Terminology                                    | 146 |

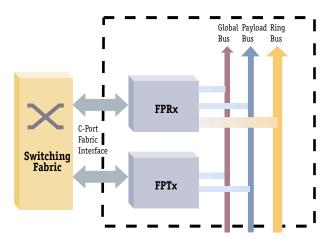

| FP Block Diagram                               | 147 |

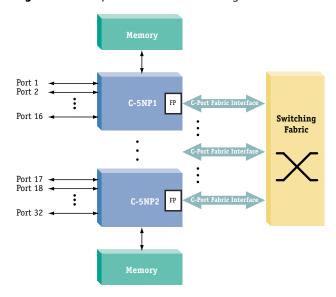

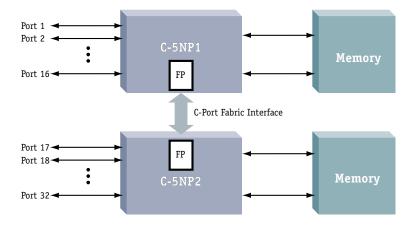

| Multiple C-5 NP Configurations                 | 147 |

| General FP specifications                      | 148 |

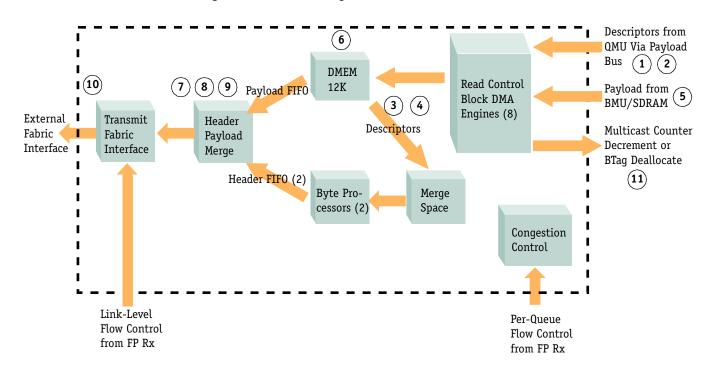

| Fabric Processor Transmit (FPTx)               | 149 |

| Transmission Sequencing                        | 151 |

| Descriptor Format                              | 152 |

| Reading the Payload                            | 153 |

| Microcode Generation of Headers                | 153 |

| FP Tx Microcoding                              | 154 |

| External test conditions                       | 154 |

| datascope                                      | 154 |

| Performance Requirement                        | 155 |

| Header Inputs                                  | 155 |

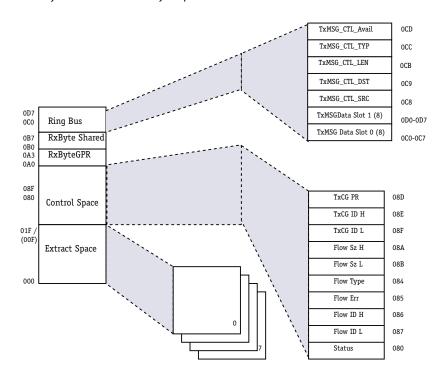

| TxByte Processor Registers                     | 156 |

| Merge Space                                    |     |

| Weighting Algorithm                            |     |

| Example 1:                                     |     |

| Example 2:                                     |     |

| Error Reporting and Interrupts                 |     |

|                                                |     |

| Descriptor (QMU) Parity Error                          | 161 |

|--------------------------------------------------------|-----|

| Buffer (BMU) Read Error                                |     |

| Write (BMU) Error                                      | 161 |

| Dequeue (QMU) Failure                                  | 162 |

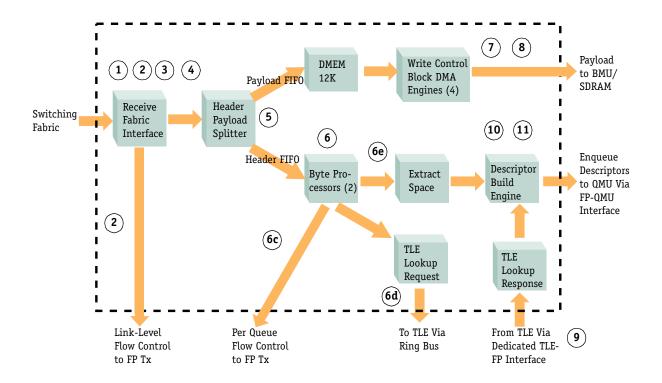

| Fabric Processor Receive (FPRx)                        | 163 |

| Header and Payload Splitting                           |     |

| Buffer Pool Configuration, BTag Allocation, and Buffer | 166 |

| Storing the Payload                                    |     |

| Microcode Processing of Headers                        | 168 |

| External Test Conditions                               | 171 |

| Datascope                                              | 172 |

| Performance Requirement                                | 172 |

| Setting Up Control Information                         | 173 |

| Writing to Extract Space                               | 174 |

| TLU Lookups                                            | 174 |

| TLU Lookup Programming Guidelines                      | 175 |

| General Purpose Registers                              | 176 |

| Discarding Segments                                    | 176 |

| Token Passing                                          | 177 |

| Rx Drop Mode                                           | 177 |

| Descriptor Build Engine Microcoding                    | 178 |

| Descriptor Build Sequence Programming                  | 178 |

| Extract and Response                                   | 178 |

| Handling TLU Errors                                    | 179 |

| Alignment                                              |     |

| Bit shift operation                                    |     |

| Enqueuing                                              |     |

| Interrupts                                             |     |

| Error Status FIFO Full                                 | 184 |

| Parity Error                                           |     |

| No BTags available on allocate                         | 184 |

| Buffer Write Errors                                    |     |

| BTag Programming Error                                 |     |

| BTag ECC Error                                         |     |

| BTag Allocation Retry Timeout                          | 184 |

| Error Handling and Statistics                          | 184 |

| Enqueue Failures                                       | 185 |

| Segment Sequencing Errors                              | 185 |

| Parity and CRC Frrors                                  | 185 |

| P Functionality                                                        | 187         |

|------------------------------------------------------------------------|-------------|

| Initialization                                                         | 187         |

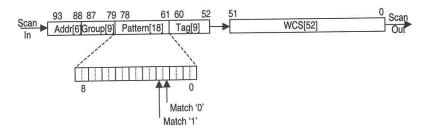

| Accessing the Tx Flow Control CAM                                      | 187         |

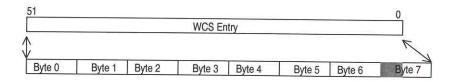

| Accessing the FP Rx Descriptor Build Engine Write Control Store (WCS), | 3yte Proces |

| sor WCSs, and Byte Processor CAMs                                      | 188         |

| Accessing the FP TxByte Processor WCSs and CAMs                        | 188         |

| Accessing FP Rx WCSs and CAMs                                          | 188         |

| Fabric to C-5 NP Link-Level Flow Control                               | 192         |

| C-5 NP to Fabric Link-Level Flow Control                               | 192         |

| Latency                                                                | 192         |

| Fabric to C-5 NP Per-Queue Flow Control                                | 193         |

| C-5 NP to Fabric Per-Queue Flow Control                                | 194         |

| Descriptor Sizes                                                       | 195         |

| CRC                                                                    | 195         |

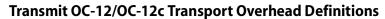

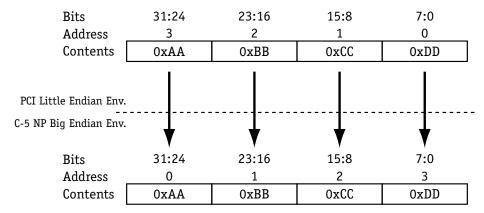

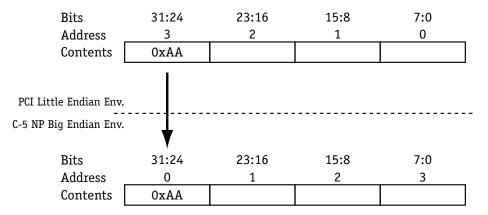

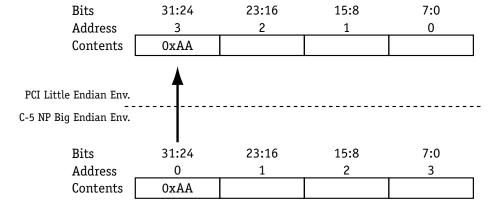

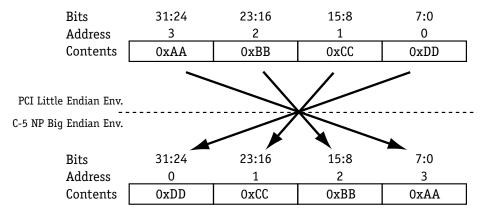

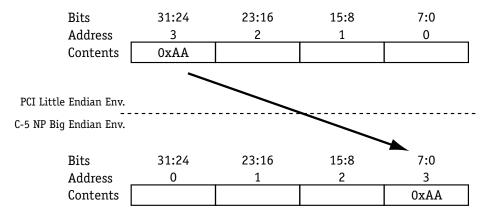

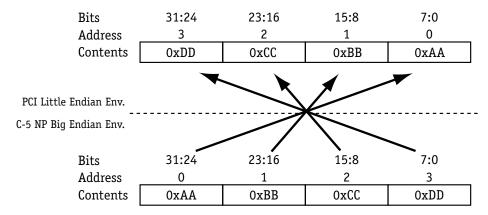

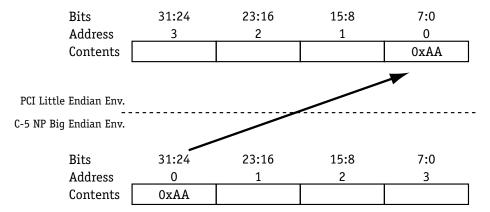

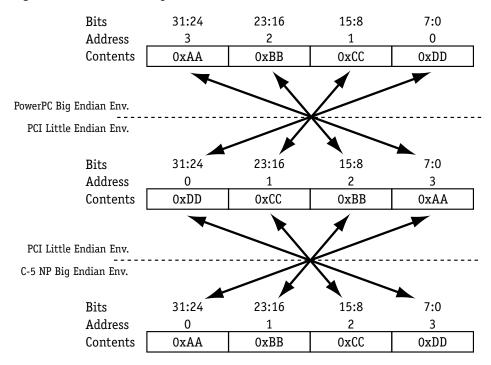

| Endianness (Byte and Bit Ordering)                                     | 195         |

| Big Endian Byte Ordering on Data Pins 31:0                             | 196         |

| Little Endian Byte Ordering on Data Pins 31:0                          | 196         |

| Debugging and Test Features                                            | 196         |

| 1. Debug MUX                                                           | 196         |

| 2. FP Rx Statistics Registers                                          | 196         |

| 3. Internal Debug State Registers                                      | 196         |

| 4. Accessing FP Memories                                               | 196         |

| Writing and Reading the Rx PDU ID CAM                                  | 197         |

| Writing and Reading the Rx Flow Table and Descriptor Memory            | 197         |

| Writing and Reading the Tx Flow Table                                  | 198         |

| Writing and Reading Merge Space                                        | 198         |

| Writing and Reading DMEMs                                              | 198         |

| Reading TLU Responses                                                  | 198         |

| abric Interface Configuration and Operation                            | 199         |

| FP Payload Bus Bandwidth                                               | 199         |

| Network Processor-to-Network Processor Operation (Back to back)        |             |

| FP Interface Modes                                                     | 199         |

| Utopia Modes                                                           | 199         |

| C-5 NP Utopia Operation                                                | 200         |

| Utopia 3                                                               | 201         |

| General Compliance                                                     | 201         |

| Control Signals                                                        | 201         |

| TxClav Specification                                                   | 202         |

| TxEnb Specification                                                    | 202         |

|           | TxSOC Specification                                                                                                                                                             | 202                      |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|           | RxClav Specification                                                                                                                                                            | 202                      |

|           | RxEnb Specification                                                                                                                                                             | 203                      |

|           | RxSOC Specification                                                                                                                                                             | 203                      |

|           | Utopia 2                                                                                                                                                                        | 203                      |

|           | General                                                                                                                                                                         | 203                      |

|           | Control signals                                                                                                                                                                 | 204                      |

|           | TxClav Specification                                                                                                                                                            | 204                      |

|           | TxEnb Specification                                                                                                                                                             | 204                      |

|           | TxSOC Specification                                                                                                                                                             | 205                      |

|           | RxClav Specification                                                                                                                                                            | 205                      |

|           | RxEnb Specification                                                                                                                                                             | 205                      |

|           | RxSOC Specification                                                                                                                                                             | 205                      |

|           | PRIZMA Mode                                                                                                                                                                     | 206                      |

|           | Configuring for PRIZMA Mode                                                                                                                                                     | 208                      |

|           | PowerX Mode                                                                                                                                                                     | 209                      |

|           | Constraints                                                                                                                                                                     | 209                      |

|           | Requirements                                                                                                                                                                    | 209                      |

|           | Byte Processor Unloading                                                                                                                                                        |                          |

|           |                                                                                                                                                                                 |                          |

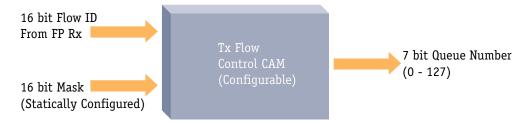

| CHAPTER 5 | Buffer Management Unit                                                                                                                                                          |                          |

|           | Chapter Overview                                                                                                                                                                | 213                      |

|           | Buffer Management Unit (BMU) Overview                                                                                                                                           | 214                      |

|           | BMU Major Components                                                                                                                                                            | 214                      |

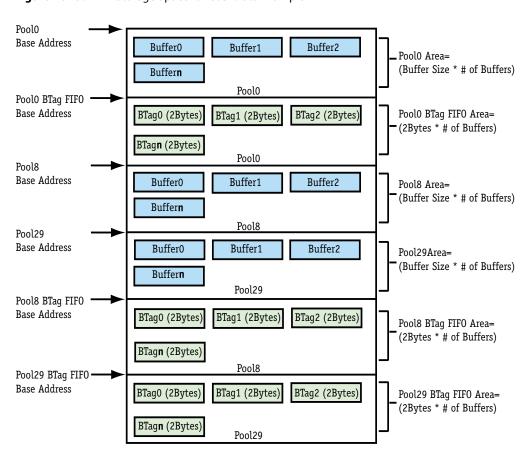

|           | BMU Physical Memory Organization                                                                                                                                                | 216                      |

|           | Out-of-Band Bits                                                                                                                                                                | 217                      |

|           | SECDED ECC Support                                                                                                                                                              | 217                      |

|           | BMU Buffer Memory Organization                                                                                                                                                  | 218                      |

|           | Buffer Pools                                                                                                                                                                    |                          |

|           |                                                                                                                                                                                 |                          |

|           | Buffers                                                                                                                                                                         | 218                      |

|           | Buffers                                                                                                                                                                         |                          |

|           | Buffers                                                                                                                                                                         | 218                      |

|           | Buffers                                                                                                                                                                         | 218<br>218               |

|           | Buffers  Buffer Tags (BTags)  Storage Space (SDRAM Partitions)  Buffer Access                                                                                                   |                          |

|           | Buffers  Buffer Tags (BTags)  Storage Space (SDRAM Partitions)  Buffer Access  Types of Transactions                                                                            | 218<br>218<br>219<br>221 |

|           | Buffers Buffer Tags (BTags) Storage Space (SDRAM Partitions) Buffer Access Types of Transactions Buffer Memory Transactions                                                     |                          |

|           | Buffers Buffer Tags (BTags) Storage Space (SDRAM Partitions) Buffer Access Types of Transactions Buffer Memory Transactions Using Wr/Rd Control Blocks for Payload Transactions |                          |

|           | Buffers Buffer Tags (BTags) Storage Space (SDRAM Partitions) Buffer Access Types of Transactions Buffer Memory Transactions                                                     |                          |

| BTag Management Transactions                        | 226 |

|-----------------------------------------------------|-----|

| BTag Transaction Functions (Operation and Examples) | 226 |

| BTag Initialization Operation                       | 226 |

| BTag Initialization Example                         | 227 |

| BTag Allocation Operation                           | 229 |

| BTag Allocation Example                             | 229 |

| BTag Deallocation Operation                         | 231 |

| BTag Deallocation Example                           | 231 |

| Multi-Use Counter (MUC) Management Transactions     |     |

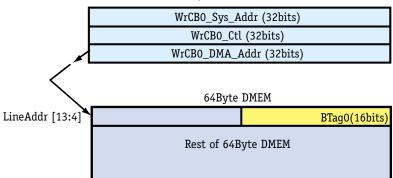

| MUC Transaction Functions (Operation and Examples)  | 234 |

| MUC Allocation Operation                            |     |

| MUC Allocation Example                              |     |

| MUC Decrement Operation                             | 236 |

| MUC Decrement Example                               |     |

| MUC Read Operation                                  | 238 |

| MUC Read Example                                    | 238 |

| BMU Configuration Space                             | 240 |

| Test and Debug Registers                            |     |

| Memory Error Reporting                              | 241 |

| ECC Test Modes                                      | 242 |

| Debug Register                                      | 242 |

| BMU Setup                                           | 243 |

|                                                     |     |

| Table Lookup Unit                                   |     |

| Chapter Overview                                    | 245 |

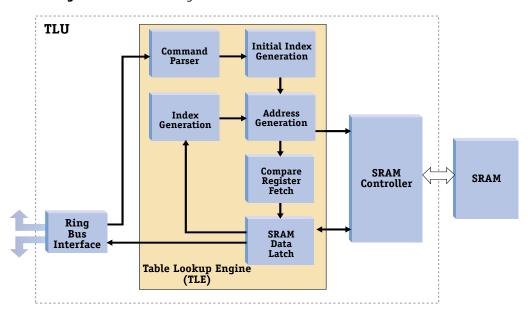

| Table Lookup Unit (TLU) Overview                    | 246 |

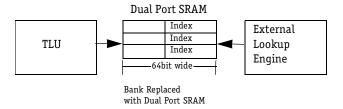

| TLU Major Components                                | 247 |

| TLU Flow Process                                    | 248 |

| TLU Flow Process Details                            | 248 |

| Ring Bus Interface and Command Parser               | 248 |

| Initial Index Generation                            | 249 |

| Address Generation                                  | 249 |

| Compare Register Fetch                              | 249 |

| SRAM Data Latch                                     | 249 |

| Index Generation                                    | 250 |

| SRAM Controller                                     | 250 |

| TLU Supported Table Types                           | 251 |

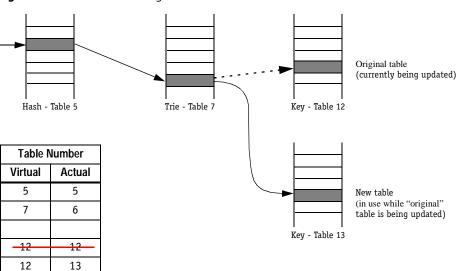

| TLU Table Mapping                                   | 253 |

| Mapping Virtual Tables to Physical Tables           | 253 |

| TLU Commands Overview                             | 255 |

|---------------------------------------------------|-----|

| TLU Command Parameters                            | 256 |

| Detail TLU Commands                               | 257 |

| Write Command                                     | 257 |

| Write Command Format                              | 258 |

| Write Command Data Alignment Rules                | 259 |

| Write Command Returned Data                       | 259 |

| Write Command Error Types                         | 259 |

| Read Command                                      | 260 |

| Read Command Format                               | 260 |

| Read Command Data Alignment Rules                 | 261 |

| Read Command Returned Data                        | 261 |

| Read Command Error Types                          | 261 |

| Find Command                                      | 262 |

| Find Command Format                               | 262 |

| Find Command Data Alignment Rules                 | 263 |

| Find Command Returned Data                        | 263 |

| Find Command Error Types                          | 263 |

| Findw Command                                     | 264 |

| Findw Command Format                              | 264 |

| Findw Command Data Alignment Rules                | 265 |

| Findw Command Returned Data                       | 265 |

| Findw Command Error Types                         | 265 |

| Findr Command                                     | 266 |

| Findr Command Format                              | 266 |

| Findr Command Data Alignment Rules                | 267 |

| Findr Command Returned Data                       | 267 |

| Findr Command Error Types                         | 267 |

| Add Command                                       | 268 |

| Add Command Format                                | 268 |

| Add Command Data Alignment Rules                  | 269 |

| Add Command Returned Data                         | 269 |

| Add Command Error Types                           | 269 |

| XOR Command                                       | 270 |

| XOR Command Format                                | 270 |

| XOR Command Data Alignment Rules                  | 271 |

| XOR Command Returned Data                         | 271 |

| XOR Command Error Types                           | 271 |

| CRC Mode (Using the Non-zero XOR Command Options) | 272 |

| CRC Mode Flow                                     | 2/3 |

|---------------------------------------------------|-----|

| CRC Mode Data Alignment Rules                     | 273 |

| CRC Mode Returned Data                            | 273 |

| CRC Mode Error Types                              | 273 |

| Write Register Command                            | 274 |

| WriteReg Command Format                           | 274 |

| WriteReg Command Data Alignment Rules             | 274 |

| WriteReg Command Returned Data                    | 274 |

| WriteReg Command Error Types                      | 274 |

| Read Register Command                             | 275 |

| ReadReg Command Format                            | 275 |

| ReadReg Command Data Alignment Rules              | 275 |

| ReadReg Command Returned Data                     | 275 |

| ReadReg Command Error Types                       | 275 |

| Echo Command                                      | 276 |

| Echo Command Format                               | 276 |

| Echo Command Data Alignment Rules                 | 276 |

| Echo Command Returned Data                        | 276 |

| Echo Command Error Types                          | 276 |

| No-Operation (NOP) Command                        | 277 |

| Data Alignment Rules for NOP Commands             | 277 |

| Returned Data for NOP Commands                    | 277 |

| Error Types for NOP Commands                      | 277 |

| TLU Configuration and Status Registers            | 278 |

| TLU Registers                                     | 278 |

| CRC-32_Checkvalue Register                        | 279 |

| CRC-32_FCS_Correction_Table_Base_Address Register | 280 |

| TLU_Statistics Register                           | 280 |

| Table_Configuration1 Register                     | 281 |

| Table_Configuration2_Lower Register               | 283 |

| Start Byte Field Usage Based on Table Type        | 283 |

| Table_Configuration2_Upper Register               | 284 |

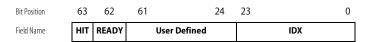

| Virtual_Table_Configuration Register              | 284 |

| Lookup_Algorithm_Configuration1 Register          | 285 |

| Lookup_Algorithm_Configuration2 Register          | 287 |

| TLU Format and Examples of Table Types            | 288 |

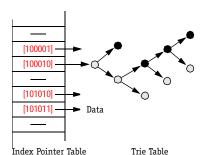

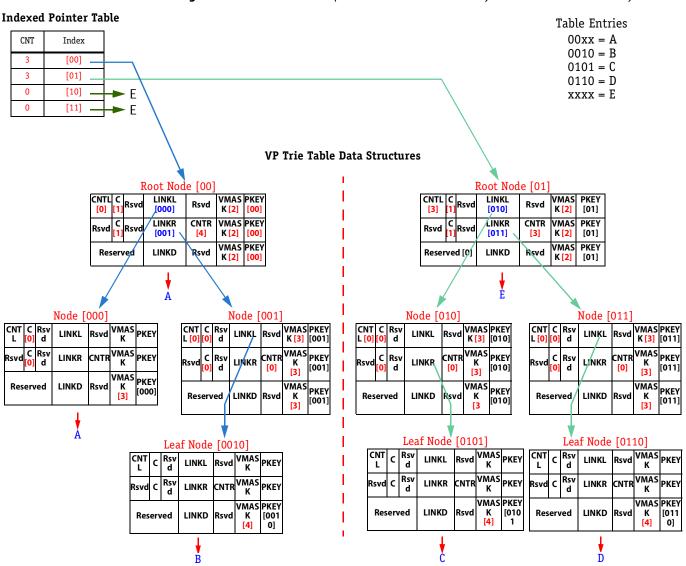

| Indexed Pointer Tables                            | 288 |

| Index Pointer Data Entry Format                   | 289 |

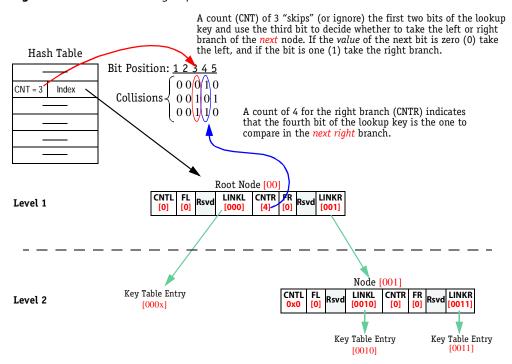

| Hash Tables                                       | 290 |

| Calculating Collisions                                    | 290 |

|-----------------------------------------------------------|-----|

| TLU Hash Function                                         | 290 |

| Hash Data Entry Format                                    | 291 |

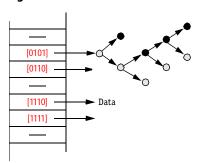

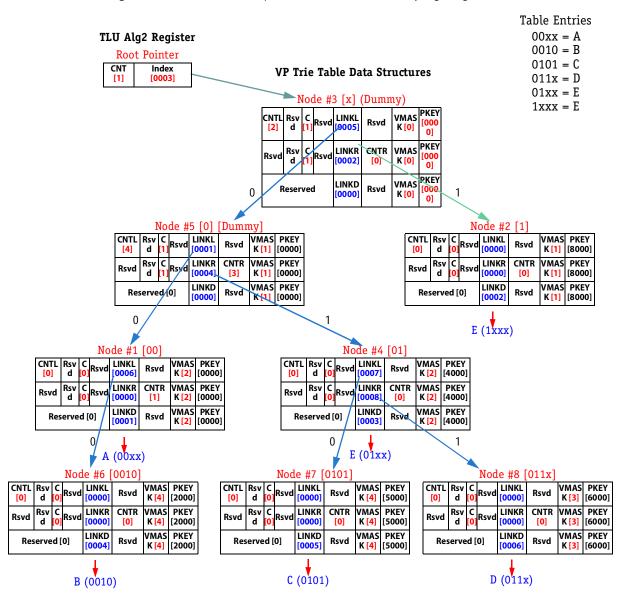

| Trie Tables                                               | 292 |

| Trie Data Entry Format                                    | 292 |

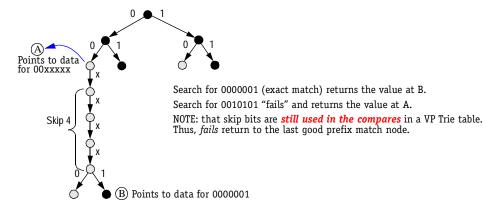

| Variable Prefix (VP) Trie Tables                          | 296 |

| Variable Prefix (VP) Tries Data Entry Format              | 297 |

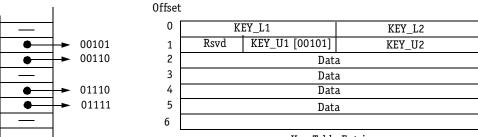

| Key Tables                                                | 301 |

| Key Data Entry Format                                     | 301 |

| Data Tables                                               | 302 |

| External Tables                                           | 302 |

| TLU Application Considerations                            | 304 |

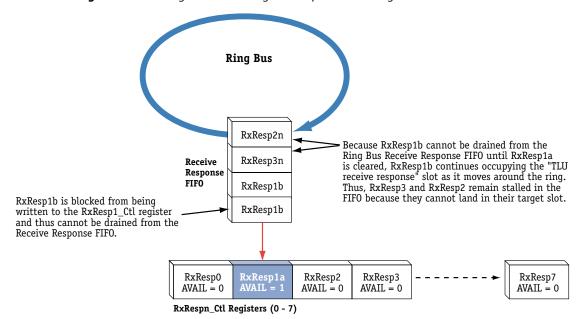

| TLU/Ring Bus Control Register Response Slot Usage         | 304 |

| TLU Performance                                           | 305 |

| Table Sizing Examples                                     |     |

| Bridge Address Table Sizing Example                       | 306 |

| IP Routing Table Sizing Example                           | 306 |

| TLU Special Applications                                  |     |

| Using the RxByte Processor for Long Lookups               | 307 |

| Long Lookup Example for an Ethernet Application           |     |

| Ethernet Application Example Implementation Notes         |     |

| Partial CRC-32 Support                                    | 310 |

| Partial CRC-32 Data Entry Format                          | 311 |

| Partial CRC-32 General Setup                              |     |

| Partial CRC-32 Rx Setup and Operation                     | 311 |

| Partial CRC-32 Tx Setup and Operation                     |     |

| · ·                                                       |     |

| Queue Management Unit                                     |     |

| Chapter Overview                                          | 314 |

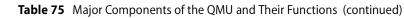

| Queue Management Unit (QMU) Overview                      |     |

| Payload Descriptors Enqueued to the QMU                   |     |

| Used-Defined Inter-processor Messages Enqueued to the QMU |     |

| QMU Major Components                                      |     |

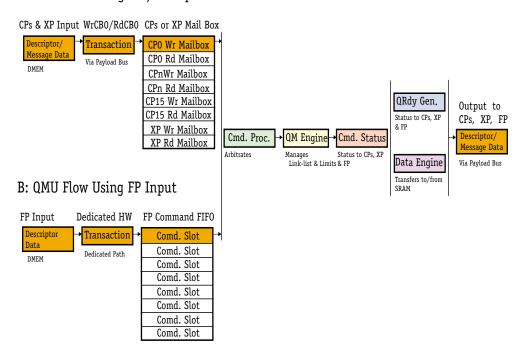

| QMU Flow Process                                          |     |

| Flow Details for CPs/XP Inputs and FP Inputs              |     |

| CPs and XP Input Flow                                     |     |

| FP Input Flow                                             |     |

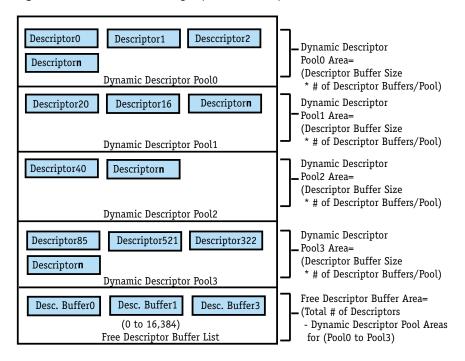

| Queue Organization                                        |     |

|                                                           | 322 |

| Descriptor Buffer                                               | 322   |

|-----------------------------------------------------------------|-------|

| Dynamic Descriptor Pools                                        | 322   |

| Dynamic Descriptor Usage Limit Pooln                            |       |

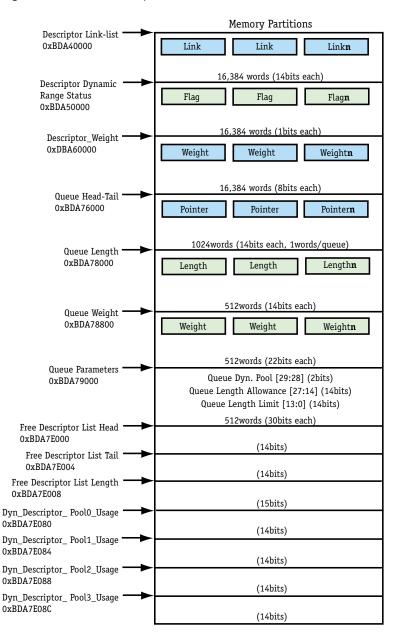

| Internal SRAM                                                   | 324   |

| QMU Variables                                                   |       |

| Queue Mapping and Parameter Characteristics                     | . 328 |

| Queue to Processor Mapping                                      | 328   |

| Queue to Processor Mapping Rules                                | 329   |

| Queue Length Allowance and Length Limit Parameters              | 330   |

| Queuing Operations                                              | . 332 |

| QMU Run Enable                                                  | 332   |

| Enqueue Operation                                               | 332   |

| Payload (Wr/Rd) Servicing Order During Enqueue Operation        | 332   |

| Causes of Enqueue Failure                                       | 333   |

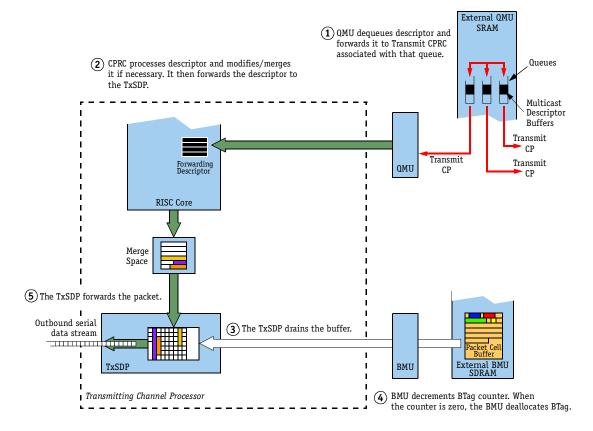

| Dequeue Operation                                               | 333   |

| Queue Servicing Policy During Dequeuing Operation               | 333   |

| Causes of Dequeue Failures                                      | 334   |

| Status Reporting                                                | 334   |

| Mailbox Availability and Status Reporting of Mailboxes          | 334   |

| Queue Status Information                                        | 335   |

| Queue Empty to Non-empty State Notification Process Information | 335   |

| Dequeue Status Information                                      | 336   |

| Buffer Management Information                                   | 336   |

| Types of Transactions                                           | . 337 |

| Queue Management Transactions                                   | . 340 |

| Queue Transaction Functions (Operation and Examples)            | 340   |

| Configure Queue Operation                                       | 340   |

| Configure Queue Example                                         | 340   |

| Queue Status Operation                                          | 342   |

| Queue Status Example                                            | 342   |

| Unicast Enqueue Operation                                       | 344   |

| Unicast Enqueue Example                                         | 344   |

| Multicast Enqueue Operation                                     | 346   |

| Multicast Enqueue Example                                       | 346   |

| Dequeue Operation                                               | 348   |

| Dequeue Example                                                 | 348   |

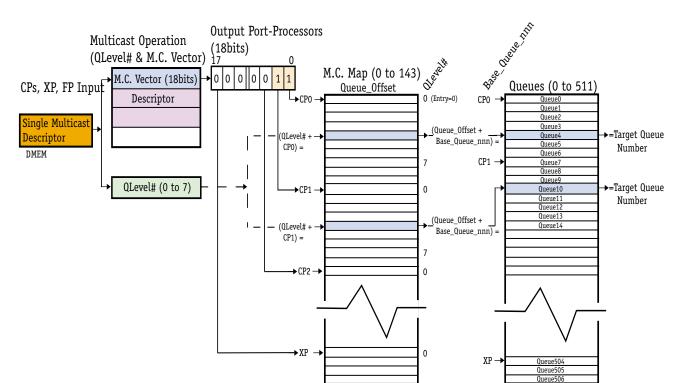

| QMU Multicast Support (Non-System Level)                        | . 350 |

| Multicast Operations Success or Failure                         | 352   |

| Multicast Operation Throughput Considerations                   | 352   |

|           | Queue Levels Supported in Multicast Operations   | 353 |

|-----------|--------------------------------------------------|-----|

|           | Multicasting to the Fabric Processor             | 354 |

|           | QMU Configuration Space                          | 355 |

|           | QMU Setup                                        | 358 |

|           | QMU Performance                                  | 360 |

|           | Execution Speed and Descriptor Size Relationship | 360 |

|           | Multicast Support (System Level)                 | 36  |

|           | Multicast Flow in the C-5 NP                     | 36  |

|           | Multicast Receive Flow Transaction Process       | 36  |

|           | Multicast Transmit Flow Transaction Process      | 363 |

| CHAPTER 8 | Internal Buses                                   |     |

|           | Chapter Overview                                 | 365 |

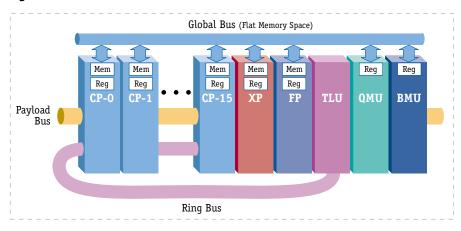

|           | Internal Buses Overview                          | 366 |

|           | Internal Buses Characteristics                   | 367 |

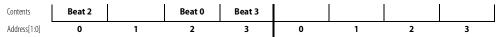

|           | Payload Bus Overview                             | 368 |

|           | Payload Bus Operation                            | 368 |

|           | Payload Bus Latency                              | 368 |

|           | Payload Bus Latency (Default Mode)               | 369 |

|           | Payload Bus Latency (FP Mode)                    | 369 |

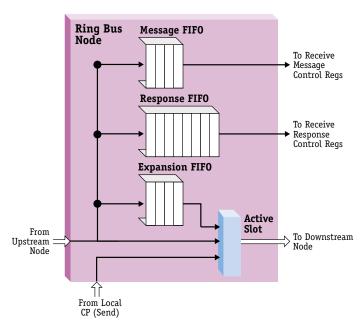

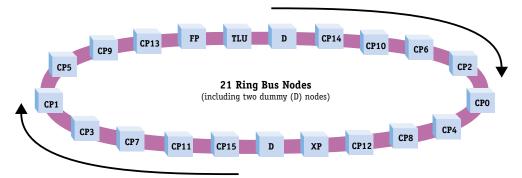

|           | Ring Bus Overview                                | 370 |

|           | Ring Bus Major Components                        | 370 |

|           | Ring Bus Node Operation                          | 37  |

|           | Sending Downstream                               | 372 |

|           | Receiving from Upstream                          | 373 |

|           | Ring Bus Latency                                 | 373 |

|           | Ring Bus Interface Registers                     | 375 |

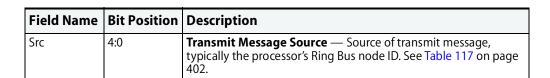

|           | Ring Bus Transmit (Tx) Message Registers         | 375 |

|           | Ring Bus (Rx) Receive Message Registers          | 375 |

|           | Ring Bus Receive (Rx) Response Registers         | 375 |

|           | Global Bus Overview                              | 376 |

APPENDIX A

| C-5 NP Registers                                                            |  |

|-----------------------------------------------------------------------------|--|

| Appendix Overview                                                           |  |

| Channel Processor (CP) Configuration Registers                              |  |

| CP Registers                                                                |  |

| CP Detailed Descriptions                                                    |  |

| RxSDP0_Ext0 to RxSDP0_Ext15 Registers (CP Rx Extract Space0 Function) 383   |  |

| TxSDP0_Merge0 to TxSDP0_Merge15 Registers (CP Tx Merge Space0 Function) 383 |  |

| RxCB0_Sys_Addr Register (CP Rx Control Block0 Function)                     |  |

| RxCB0_Ctl Register (CP Rx Control Block0 Function)                          |  |

| RxCB0_DMA_Addr Register (CP Rx Control Block0 Function)                     |  |

| RxCB0_SDP_Addr Register (CP Rx Control Block0 Function)                     |  |

| WrCB0_Sys_ Addr Register (CP Wr Control Block0 Function)                    |  |

| WrCB0_Ctl Register (CP Wr Control Block0 Function)                          |  |

| WrCB0_DMA_Addr Register (CP Wr Control Block0 Function)                     |  |

| RdCB0_Sys_Addr Register (CP Rd Control Block0 Function)                     |  |

| RdCB0_Ctl Register (CP Rd Control Block0 Function)                          |  |

| RdCB0_DMA_Addr Register (CP Rd Control Block0 Function)                     |  |

| TxCB0_Sys _Addr Register (CP Tx Control Block0 Function)                    |  |

| TxCB0_Ctl Register (CP Tx Control Block0 Function)                          |  |

| TxCB0_DMA_Addr Register (CP Tx Control Block0 Function)                     |  |

| TxCB0_SDP_Addr Register (CP Tx Control Block0 Function)                     |  |

| TxCtl0_Status Register (CP Tx Control Block0 Function)                      |  |

| TxMsg0_Ctl Register (CP Ring Bus Tx Message Control Function)               |  |

| TxMsg0_Data_H Register (CP Ring Bus Tx Message Control Function)            |  |

| TxMsg0_Data_L Register (CP Ring Bus Tx Message Control Function)            |  |

| RxResp0_Ctl Register (CP Ring Bus Rx Response Control Function)             |  |

| RxResp0_Data_H Register (CP Ring Bus Rx Response Control Function)          |  |

| RxResp0_Data_L Register (CP Ring Bus Rx Response Control Function)          |  |

| RxMsg_Ctl Register (CP Ring Bus Rx Message Control Function)                |  |

| RxMsg_FIFO Register (CP Ring Bus Rx Message Control Function)               |  |

| Rx_SONETOH0 to Rx_SONETOH31 Registers (CP SONET Rx Control Function) 408    |  |

| Tx_SONETOH0 to Tx_SONETOH31 Registers (CP SONET Tx Control Function) 408    |  |

| RxCtl_ByteSeq0 Register (CP SDP Rx Control Function)                        |  |

| RxCtl_SyncSeq Register (CP SDP Rx Control Function)                         |  |

| RxCtl_BitSeq0 Register (CP SDP Rx Control Function)                         |  |

| TxCtl_ByteSeq0 Register (CP SDP Tx Control Function)                        |  |

| TxCtl_BitSeq0 Register (CP SDP Tx Control Function)                         |  |

| CP_Mode0 Register (CP Mode Configuration Function)                          |  |

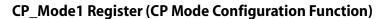

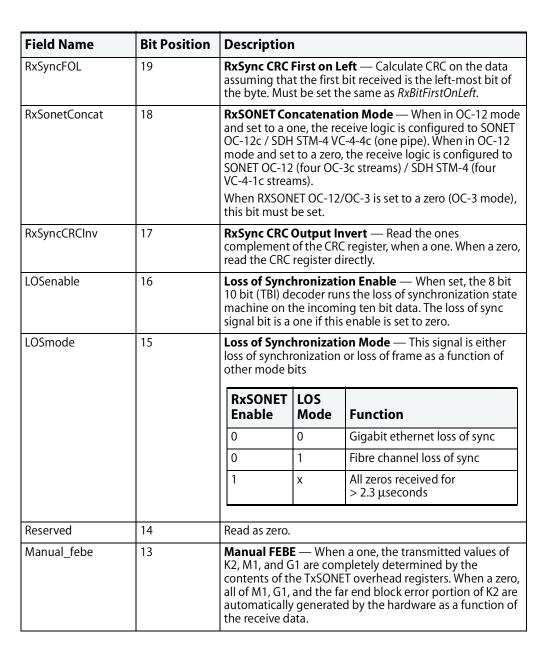

| CP_Mode1 Register (CP Mode Configuration Function)                           | 414 |

|------------------------------------------------------------------------------|-----|

| SDP_Mode2 Register (CP Mode Configuration Function)                          | 417 |

| SDP_Mode3 Register (CP Mode Configuration Function)                          | 418 |

| SDP_Mode4 Register (CP Mode Configuration Function)                          | 422 |

| SDP_Mode5 Register (CP Mode Configuration Function)                          | 424 |

| Debug_Mode Register (CP Mode Configuration Function)                         | 429 |

| PIN_Mode Register (CP Mode Configuration Function)                           | 431 |

| Queue_Status0 Register (CP Queue Status Function)                            | 433 |

| Queue_Update0 Register (CP Queue Status Function)                            | 433 |

| Event_Timer Register (CP Miscellaneous Control Function)                     | 434 |

| Cycle_Count_H Register (CP Miscellaneous Control Function)                   | 434 |

| Cycle_Count_L Register (CP Miscellaneous Control Function)                   | 434 |

| Event0 Register (CP Event and Interrupt Function)                            | 435 |

| Event1 Register (CP Event and Interrupt Function)                            | 437 |

| Event_Mask0 Register (CP Event and Interrupt Function)                       | 439 |

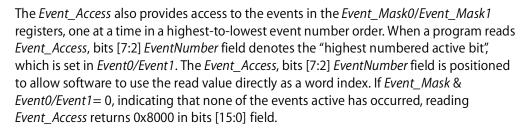

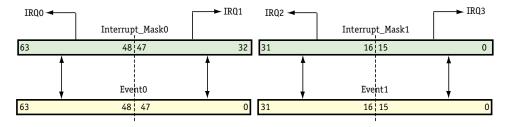

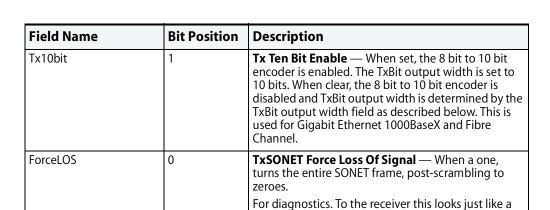

| Event_Access Register (CP Event and Interrupt Function)                      | 439 |

| Mask_Access Register (CP Event and Interrupt Function)                       | 441 |

| Interrupt_Mask0 Register (CP Event and Interrupt Function)                   | 441 |

| SONET_Event Register (CP Event and Interrupt Function)                       | 442 |

| SONET_Mask Register (CP Event and Interrupt Function)                        | 445 |

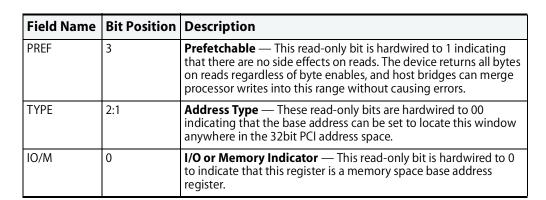

| Executive Processor (XP) Configuration Registers                             | 446 |

| XPSlot 24 Configuration Registers                                            | 446 |

| XP Detailed Descriptions                                                     | 456 |

| PCI Device ID Register (XP PCI Configuration Function)                       | 456 |

| PCI Vendor ID Register (XP PCI Configuration Function)                       | 456 |

| PCI Status Register (XP PCI Configuration Function)                          | 456 |

| PCI Command Register (XP PCI Configuration Function)                         | 458 |

| PCI Class Code Register (XP PCI Configuration Function)                      | 459 |

| PCI Revision ID Register (XP PCI Configuration Function)                     | 460 |

| PCI Header Type Register (XP PCI Configuration Function)                     | 460 |

| PCI Latency Timer Register (XP PCI Configuration Function)                   | 461 |

| PCI Inbound Memory Base Address Register0 (XP PCI Configuration Function)    | 461 |

| PCI Inbound Memory Base Address Register1 (XP PCI Configuration Function)    | 462 |

| PCI Subsystem ID Register (Read Only) (XP PCI Configuration Function)        | 463 |

| PCI Subsystem Vendor ID Register (Read Only) (XP PCI Configuration Function) |     |

| PCI Interrupt Pin Register (XP PCI Configuration Function)                   |     |

| PCI Interrupt Line Register (XP PCI Configuration Function)                  |     |

| PCI Inbound BARO Translation Register (XP PCI Configuration Function)        |     |

| PCI Inbound BAR1 Translation Register (XP PCI Configuration Function)        |     |

|         | PCI Auxiliary Control Register (XP PCI Configuration Function)           | 465 |

|---------|--------------------------------------------------------------------------|-----|

|         | PCI Subsystem ID Register (XP PCI Configuration Function)                | 465 |

|         | PCI Subsystem Vendor ID Register (XP PCI Configuration Function)         | 466 |

|         | PCI Inbound Byte Swap Control Register (XP PCI Configuration Function)   | 466 |

|         | Serial Bus Configuration Register (XP Miscellaneous Control Function)    | 467 |

|         | Serial Bus Data Register (XP Miscellaneous Control Function)             | 468 |

|         | XP to CP Interrupt Request Registers (XP Miscellaneous Control Function) | 469 |

|         | Software Warm Reset Request Register (XP Miscellaneous Control Function) | 470 |

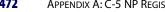

|         | Outbound PCI Base Address0 Register (XP Configuration Function)          | 471 |

|         | Outbound BARO Translation Register (XP Configuration Function)           | 472 |

|         | DMA Transmit Channel0 PCI Target Register (XP Configuration Function)    | 473 |

|         | DMA Receive Channel0 PCI Target Register (XP Configuration Function)     | 474 |

|         | DMA Receive Channel Transfer Count Register (XP Configuration Function)  | 475 |

|         | XP Miscellaneous Control Register (XP Configuration Function)            | 476 |

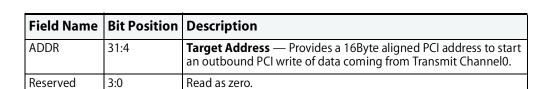

|         | XP Auxiliary Event Register (XP Configuration Function)                  | 477 |

|         | Inbound PCI Mailbox0 Register (XP Configuration Function)                | 478 |

|         | IMEM Overlay Target Address Register (XP Configuration Function)         | 479 |

|         | RxCB #25 Transfer Count Register (XP Configuration Function)             | 479 |

|         | XP Diagnostic Register (XP Configuration Function)                       | 480 |

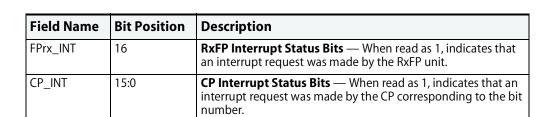

|         | PCI Outbound Byte Swap Control Register (XP Configuration Function)      | 480 |

|         | Debug Counter0 Start Value Register (XP Configuration Function)          | 482 |

|         | Debug Counter0 Control Register (XP Configuration Function)              | 483 |

|         | Debug Counter0 Current Value Register (XP Configuration Function)        | 485 |

|         | RxCtI0_Status Register (XP DMEM#24 Transfer Rx Control Block0 Function)  | 486 |

|         | TxCB0_Ctl Register (XP DMEM#24 Transfer Tx Control Block0 Function)      | 486 |

|         | TxCtl0_Status Register (XP DMEM#24 Transfer Tx Control Block0 Function)  | 487 |

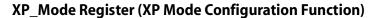

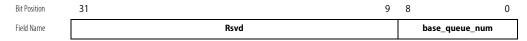

|         | XP_Mode Register (XP Mode Configuration Function)                        | 488 |

|         | XP Debug Mode Register (XP Mode Configuration Function)                  | 490 |

|         | Event0 Register (Event and Interrupt Control Function)                   | 492 |

|         | Event1 Register (Event and Interrupt Control Function)                   |     |

|         | RxCtl0_Status Register (XP DMEM#25 Transfer Control Block0 Function)     | 496 |

|         | TxCtl0_Status Register (XP DMEM#25 Transfer Control Block0 Function)     | 497 |

| Queue N | Management Unit (QMU) Configuration Registers                            | 498 |

| QM      | IU Registers                                                             | 499 |

| QM      | IU Detailed Descriptions                                                 | 501 |

|         | QMU_Run_Enable Register (QMU Enable Queue Function)                      | 501 |

|         | Base_Queue_CP0 to Base_Queue_CP15 Registers                              |     |

|         | (QMU CP's Queue Allocation Function)                                     |     |

|         | Base_Queue_FP Register (QMU FP's Queue Allocation Function)              | 502 |

|           | Base_Queue_XP Register (QMU XP's Queue Allocation Function)                               | 502 |

|-----------|-------------------------------------------------------------------------------------------|-----|

|           | Num_Descriptors Register (QMU Configuration Function)                                     | 503 |

|           | Dyn_Des_Usage_Lim_Pool0 Register (QMU Configuration Function)                             | 503 |

|           | Operation_Mode Register (QMU Configuration Function)                                      | 504 |

|           | Descriptor_Size Register (QMU Configuration Function)                                     | 504 |

|           | Config_Q_Cnt Register (QMU Statistics Function)                                           | 505 |

|           | Rd_Q_Status_Cnt Register (QMU Statistics Function)                                        | 505 |

|           | CP_Uni_Enq_Cnt Register (QMU Statistics Function)                                         | 505 |

|           | CP_Multi_Enq_Cnt Register (QMU Statistics Function)                                       | 505 |

|           | CP_Multi_Enq_Target_Cnt Register (QMU Statistics Function)                                | 505 |

|           | CP_Dequeue_Cnt Register (QMU Statistics Function)                                         |     |

|           | FP_Uni_Enq_Cnt Register (QMU Statistics Function)                                         | 505 |

|           | FP_Multi_Eng_Cnt Register (QMU Statistics Function)                                       | 505 |

|           | FP_Multi_Eng_Target_Cnt Register (QMU Statistics Function)                                | 506 |

|           | FP_Dequeue_Cnt Register (QMU Statistics Function)                                         | 506 |

|           | QMU_Idle_Cycles Register (QMU Statistics Function)                                        |     |

|           | Payload_NACK_Cnt Register (QMU Statistics Function)                                       | 506 |

|           | Global_NACK_Cnt Register (QMU Statistics Function)                                        | 506 |

|           | Payload_Read_Failures_Cnt Register (QMU Statistics Function)                              | 506 |

|           | Cmd_Processor_Err_Cnt Register (QMU Statistics Function)                                  |     |

|           | Q_Engine_Err_Cnt Register (QMU Statistics Function)                                       |     |

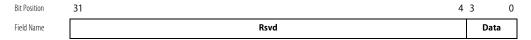

|           | Multicast_Destination0 to Multicast_Destination143 Registers (QMU Configuration           |     |

|           | Function)                                                                                 | 507 |

|           | Free_Descriptor_Buffer_List Register (QMU Status Function)                                | 510 |

|           | Dyn_Descriptor_Pool0_Usage Register (QMU Status Function)                                 | 511 |

| Buffer Ma | nagement Unit (BMU) Configuration Registers                                               | 512 |

| BMU       | Registers                                                                                 | 513 |

| BMU       | Detailed Descriptions                                                                     | 518 |

|           | PoolO Base to Pool29 Base Registers (Buffer Pool Base Address Function)                   | 518 |

|           | PoolO BTag Shift to Pool29 BTag Shift Registers (Buffer Size for a Pool Function) $\dots$ | 519 |

|           | BTag FIFO Base0 to BTag FIFO Base29 Registers (BTag FIFO Base Address Function).          | 520 |

|           | Num BTags0 to Num BTags29 Registers (Number of BTags in a Pool Function)                  | 520 |

|           | Memory Size Register (Miscellaneous Function)                                             |     |

|           | SDRAM Config Register (Miscellaneous Function)                                            | 522 |

|           | Single ECC Errors Register (Miscellaneous Function)                                       | 523 |

|           | ECC Enable and Test Enable Register (Miscellaneous Function)                              |     |

|           | Debug Config Register (Miscellaneous Function)                                            |     |

|           | Wr_Mem_Violation_Hi Register (Miscellaneous Function)                                     | 525 |

|           | Wr. Mem. Violation. Lo Begister (Miscellaneous Function)                                  |     |

| abric Processor (FP) Configuration Registers                                | 526 |

|-----------------------------------------------------------------------------|-----|

| FP Registers                                                                | 526 |

| FP Detailed Descriptions                                                    | 530 |

| TxFP_Enable Register (FP Tx Enable Function)                                | 530 |

| TxFI_Configuration Register (FP Tx Configuration Function)                  | 530 |

| TxDescInfo Register (FP Tx Configuration Function)                          | 532 |

| TxDM_Header/Payload Delimiter Register (FP Tx Configuration Function) .     | 532 |

| TxQueueWeight_Configuration Register (FP Tx Configuration Function) $\dots$ | 533 |

| TxSysConfig Register (FP Tx Configuration Function)                         | 534 |

| TxFI_CRC Register (FP Tx Configuration)                                     | 534 |

| TxFCE_Configuration Register (FP Tx Configuration Function)                 | 535 |

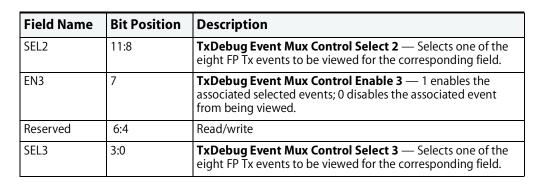

| TxDebugMux_Control Register (FP Tx DeBug Function)                          | 537 |

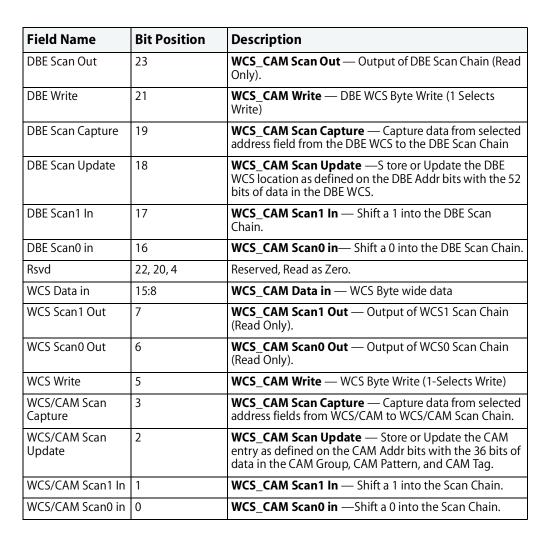

| TxWCS_CAM (WCS_CAM Function)                                                | 539 |

| TxFlowTbl Register (FP Tx DeBug Function)                                   | 540 |

| TxFlowTblDL Register (FP Tx DeBug Function)                                 | 540 |

| TxFlowTbIDH Register (FP Tx DeBug Function)                                 | 541 |

| TxFlowCam Register (FP Tx DeBug Function)                                   | 541 |

| TxMergeAddr (FPTx Debug Function)                                           |     |

| TxMergeData (FPTx Debug Function)                                           | 543 |

| TxFDP_Mrg0 - TxFDP_Mrg63                                                    |     |

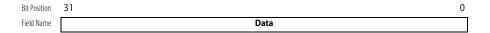

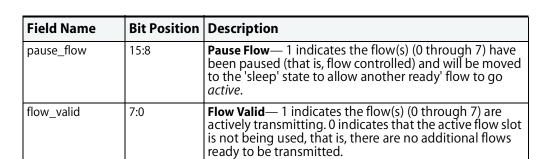

| TxIdleData Register (FP Tx Configuration Function)                          | 544 |

| TxFDP_CTL0 Register (TxByte General Purpose Function)                       | 544 |

| TxFDP_CTL1 Register (TxByte General Purpose Function)                       | 545 |

| TxDebug_Internal_State Register (FP Tx DeBug Function)                      | 545 |

| RxStatus0 Register (FP RxByte Processor Function)                           | 546 |

| RxFlowSeg0 Register (FP RxByte Processor Function)                          |     |

| RxFlowSz0 Register (FP Rx Byte Processor Function)                          | 547 |

| RxTxCgs0 Register (FP Rx Byte Processor Function)                           |     |

| RxStatus1 Register (FP RxByte Processor Function)                           |     |

| RxFlowSeg1 Register (FP RxByte Processor Function)                          |     |

| RxFlowSz1 Register (FP RxByte Processor Function)                           | 550 |

| RxTxCgs1 Register (FP RxByte Processor Function)                            |     |

| RxEnable_Configuration Register (FP Rx Enable Function)                     | 551 |

| RxFI_Configuration Register (FP Rx Configuration Function)                  |     |

| RxDS_Header_Change1 Register (FP Rx Configuration Function)                 |     |

| RxDS_Header_Change2 Register (FP Rx Configuration Function)                 |     |

| RxDS_Header/Payload_Delimiter0 Register (FP Rx Configuration Function)      |     |

| RxDS Header/Payload Delimiter1 Register (FP Rx Configuration Function) .    |     |

| RxDS_Header/Payload_Delimiter2 Register (FP Rx Configuration Function)      |     |

| RxDS_Configuration Register (FP Rx Configuration Function)                  | 555 |

APPENDIX B

| RxFCE_Configuration0 Register (FP Rx Configuration Function) | 559 |

|--------------------------------------------------------------|-----|

| RxFCE_Configuration1 Register (FP Rx Configuration Function) | 561 |

| RxFCE_Configuration2 Register (FP Rx Configuration Function) | 562 |

| Buffer Pools                                                 | 562 |

| Pool0_CFG0 Register (FP Rx Pool Configuration Function)      | 563 |

| Pool0_CFG1 Register (FP Rx Pool Configuration Function)      | 564 |

| FDP_RxByte_Shared0 Register (FP Rx Shared Function)          | 565 |

| FDP_RxByte_Shared1 Register (FP Rx Shared Function)          | 565 |

| RxFP_Interrupt_Event Register (FP Rx Interrupt Function)     | 566 |

| RxFP_Interrupt_Enable Register (FP Rx Interrupt Function)    | 567 |

| RxFP_Debug_Event_Mux_Control (FP Rx DeBug Function)          | 567 |

| RxMemory_Address Register (FP Rx DeBug Function)             | 570 |

| RxMemory_Data Register (FP Rx DeBug Function)                | 570 |

| RxPDU_ID_CAM Register (FP Rx DeBug Function)                 | 570 |

| RxFP_Statistics Registers (FP Rx Statistics Function)        | 572 |

| RxDebug_Internal_State Register (FP Rx Statistics Function)  | 573 |

|                                                              |     |

| Using Aggregate Mode                                         |     |

| Appendix Overview                                            | 577 |

| Purpose of the C-5 NP Channel Aggregate Mode                 |     |

| Aggregate Mode Requirements on the C-5 NP                    |     |

| Packet/Cell Ordering Handling for Rx in Aggregate Mode       |     |

| Hardware Receive Tokens                                      |     |

| Software Receive Tokens                                      | 580 |

| Packet/Cell Ordering Handling for Tx in Aggregate Mode       | 581 |

| Hardware Transmit Tokens                                     | 581 |

| Software Transmit Tokens                                     | 581 |

| Clock Distribution in Aggregate Mode                         | 583 |

| Aggregate Mode Application Examples                          | 583 |

| Gigabit Ethernet and FibreChannel Applications               | 583 |

| PHY Connectivity                                             | 583 |

| SDP Components                                               | 584 |

| 8b/10b Decode Block                                          | 584 |

| RxBit Processor                                              | 584 |

| RxSync and RxByte Processors                                 | 584 |

|                                                              |     |

RxFI\_CRC Register (FP Rx Configuration Function) .......556 RxWCS\_CAM Register (RxWCS\_CAM Function) .......557 RxByte0 General Purpose Configuration Register (FP Rx Configuration Function) .... 559 RxByte1 General Purpose Configuration Register (FP Rx Configuration Function) .... 559 APPENDIX C

| T. D. +- D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| TxByte Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                |

| TxBit Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                |

| 8b/10b Encode Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 586                                                                                            |

| Implementation Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 588                                                                                            |

| Non-blocking Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 588                                                                                            |

| Blocking Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 588                                                                                            |

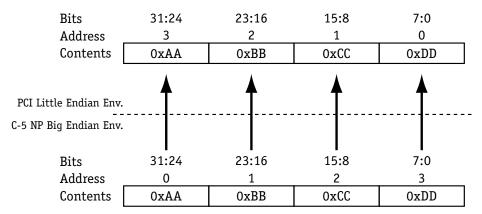

| OC-12 and OC-12c Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 589                                                                                            |

| PHY Connectivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 589                                                                                            |

| SDP Components                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 589                                                                                            |

| RxBit Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 589                                                                                            |

| RxSONET Framer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 589                                                                                            |

| RxSync Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 590                                                                                            |

| RxByte Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 590                                                                                            |

| TxByte Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 591                                                                                            |