# PF5300; PF5301; PF5302

# 12 A / 8 A / 15 A core supply regulators with AVP and watchdog Rev. 6 — 13 November 2025 Pr

**Product data sheet**

#### **Document information**

| Information | Content                                                                                                                                                                                                                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | Safety, SBC, automotive, low power, ASIL D, industrial                                                                                                                                                                                                                                                 |

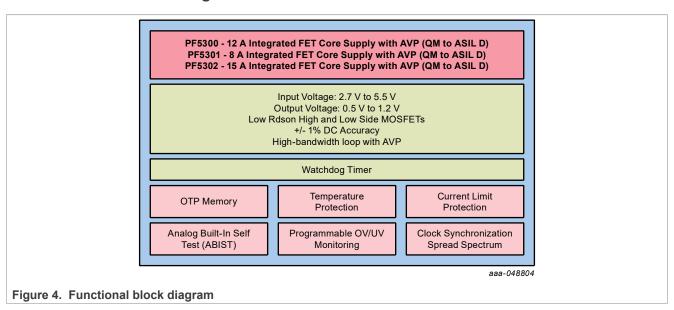

| Abstract    | The PF5300, PF5301, and PF5302 integrate high-performance buck converters, 12 A, 8 A, and 15 A, respectively, to power high-end automotive and industrial processors. With adaptive voltage positioning and a high-bandwidth loop, they offer transient regulation to minimize capacitor requirements. |

# 1 Overview

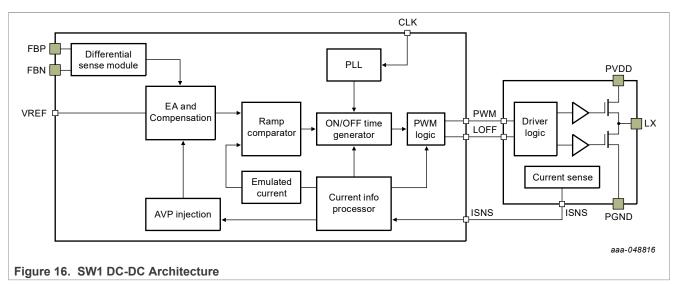

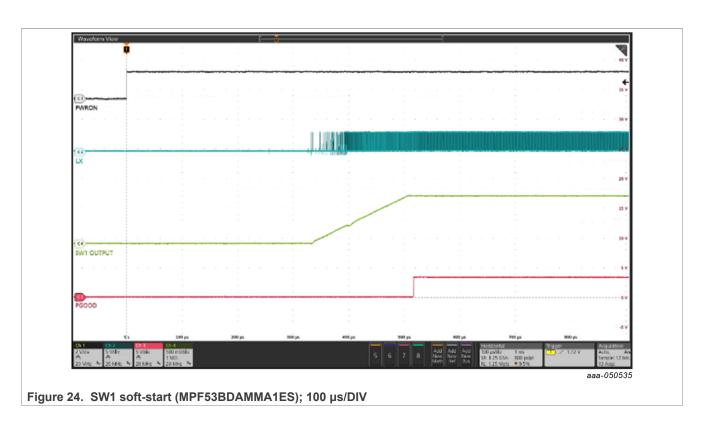

The PF5300, PF5301, and PF5302 integrate high-performance buck converters, 12 A, 8 A, and 15 A, respectively, to power high-end automotive and industrial processors.

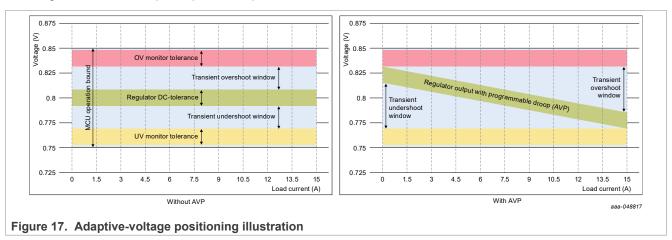

With adaptive-voltage positioning and a high-bandwidth loop, they offer transient regulation to minimize capacitor requirements.

Clock synchronization and spread-spectrum features reduce EMC issues in the system. The PF5300/PF5301/PF5302 can operate as standalone point-of-load regulator ICs or as companion chips to a larger PMIC.

Built-in one-time programmable (OTP) memory stores key startup configurations, drastically reducing external components. Regulator parameters are adjustable through high-speed I<sup>2</sup>C after startup, offering flexibility for different system states.

PF5300/PF5301/PF5302 have been developed to comply with the ISO 26262 automotive safety specification. They include configurable feature sets to fit in or support applications with safety levels up to ASIL D.

To simplify, PF5300 is used in this document to refer to PF5300, PF5301, and PF5302. Unless explicitly mentioned, references to PF5300 include PF5301 and PF5302.

#### 2 Features

The PF5300/PF5301/PF5302 integrate a high-performance 12 A / 8 A /15 A buck converter to power high-end automotive and industrial processors.

- · High-performance core buck regulator

- 12 A, 5 V<sub>IN</sub> buck regulator internal FETs (PF5300)

- 8 A, 5 V<sub>IN</sub> buck regulator internal FETs (PF5301)

- 15 A, 5 V<sub>IN</sub> buck regulator internal FETs (PF5302)

- 2.7 V to 5.5 V input range

- 0.5 V to 1.2 V output range

- High efficiency

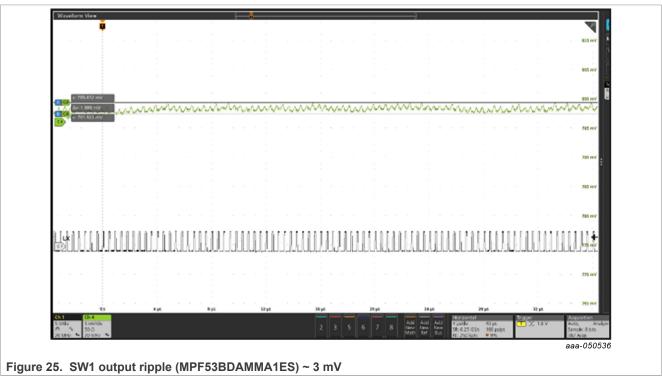

- ±1 % output accuracy

- 2 MHz to 3 MHz switching frequency

- Dynamic voltage scaling

- Programmable adaptive-voltage positioning (AVP) (droop)

- 1.5 µA quiescent current in OFF mode

- Fast startup time (< 500 μs)

- · OTP memory for device configuration

- · Overtemperature protection

- · Safety features

- Available in ASIL D, ASIL B, and QM variations

- Watchdog timer

- 1 % OV/UV monitoring

- PGOOD output

- Analog built-in self-test

- Automotive AEC-Q100 qualified and extended industrial versions available

- Rated from -40 °C to 150 °C Tj

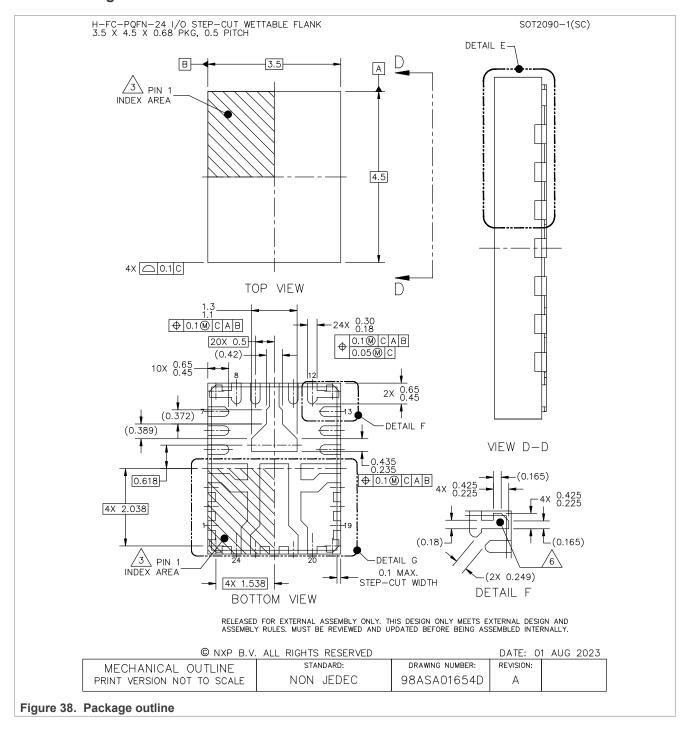

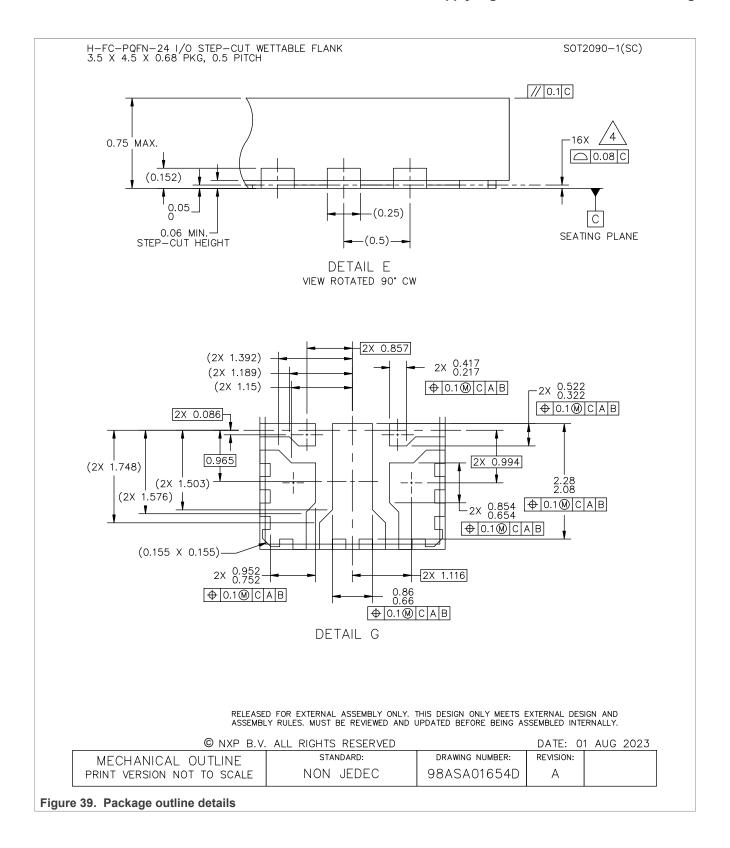

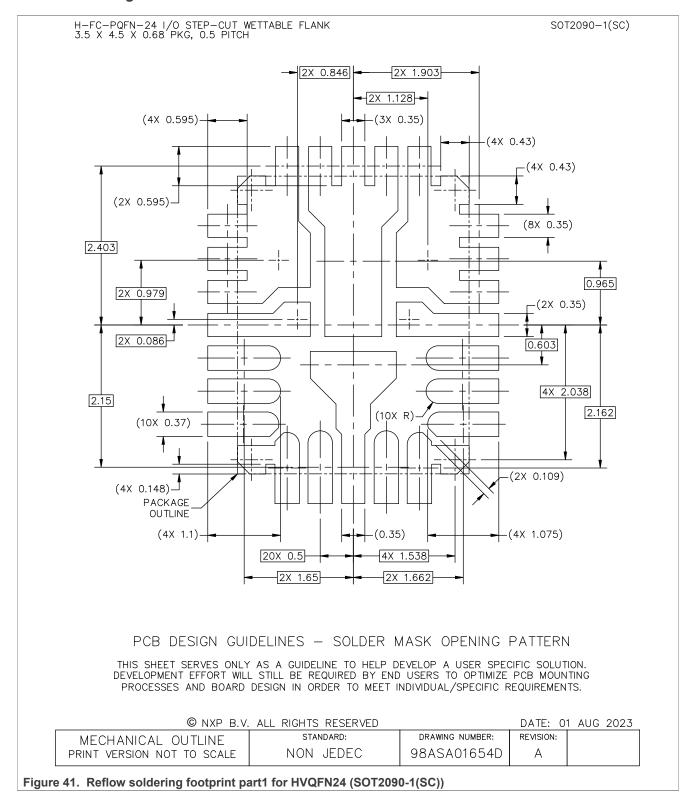

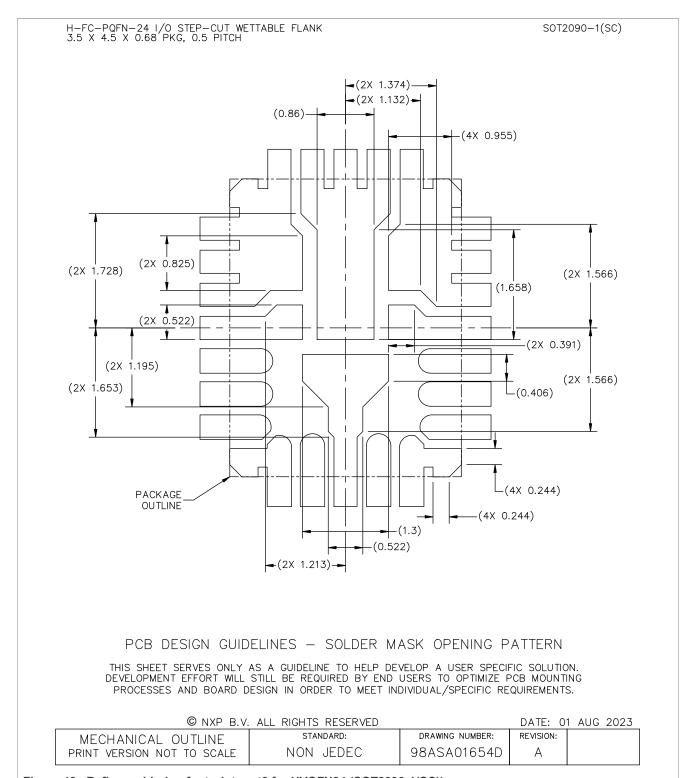

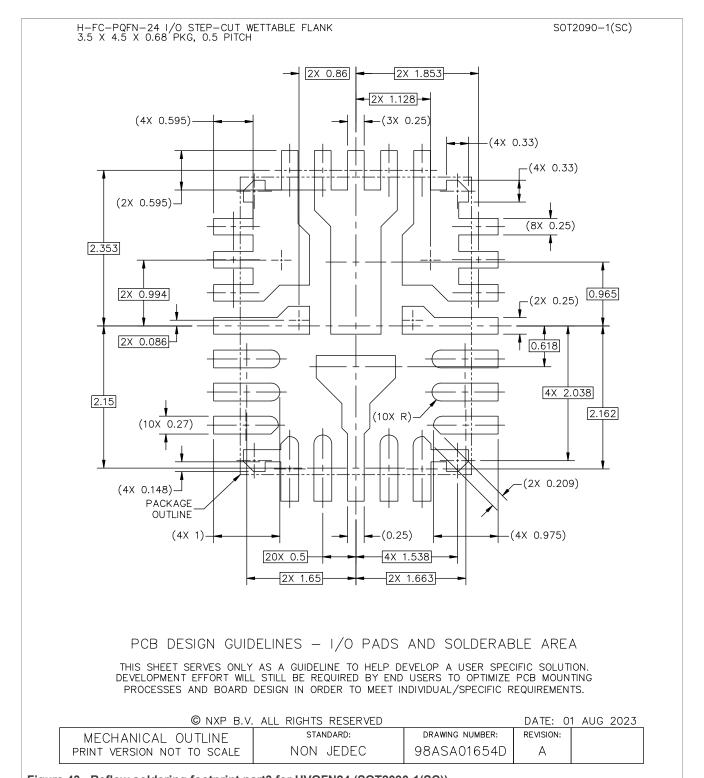

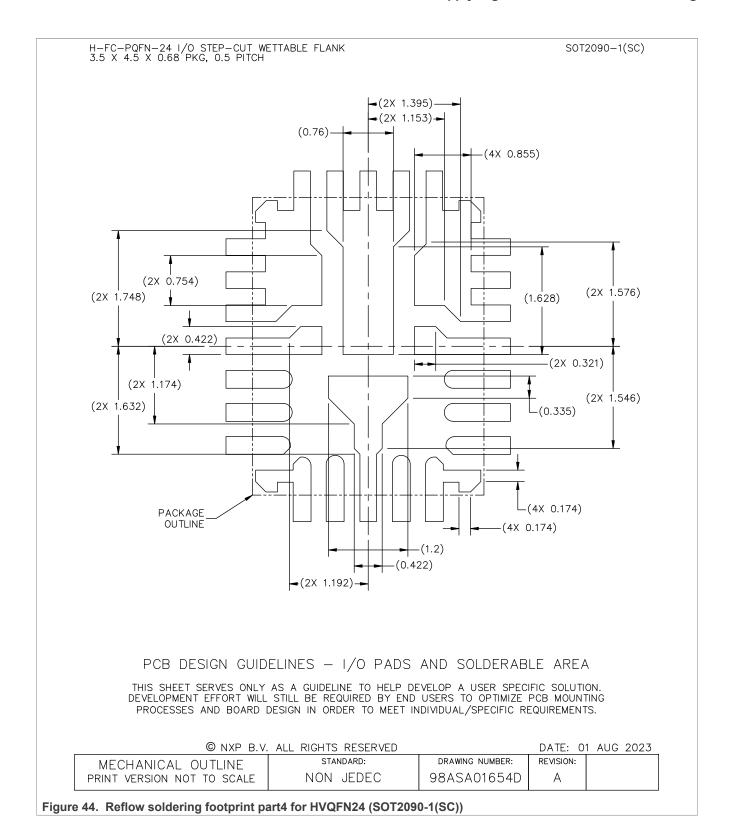

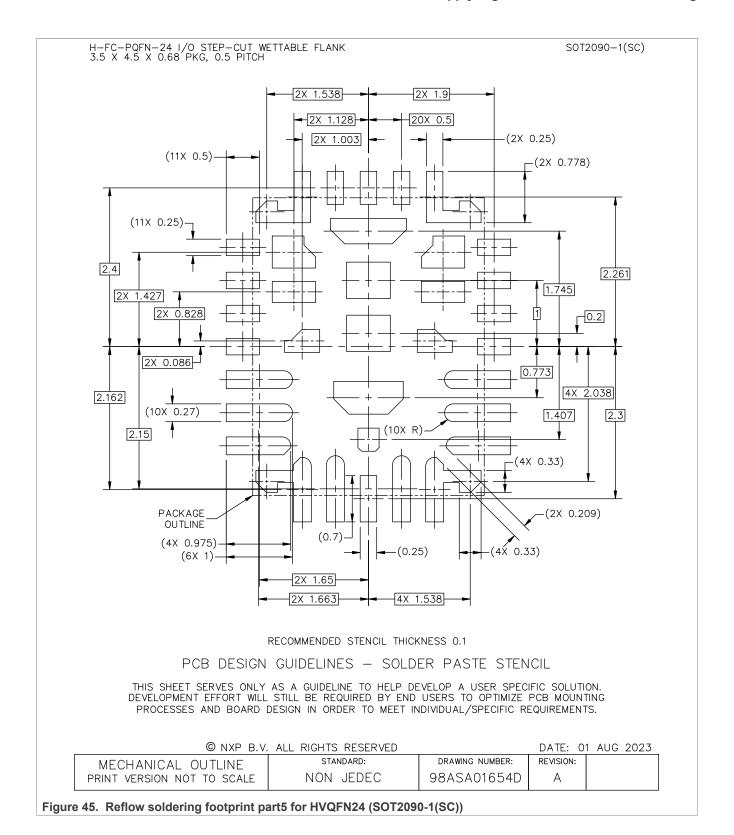

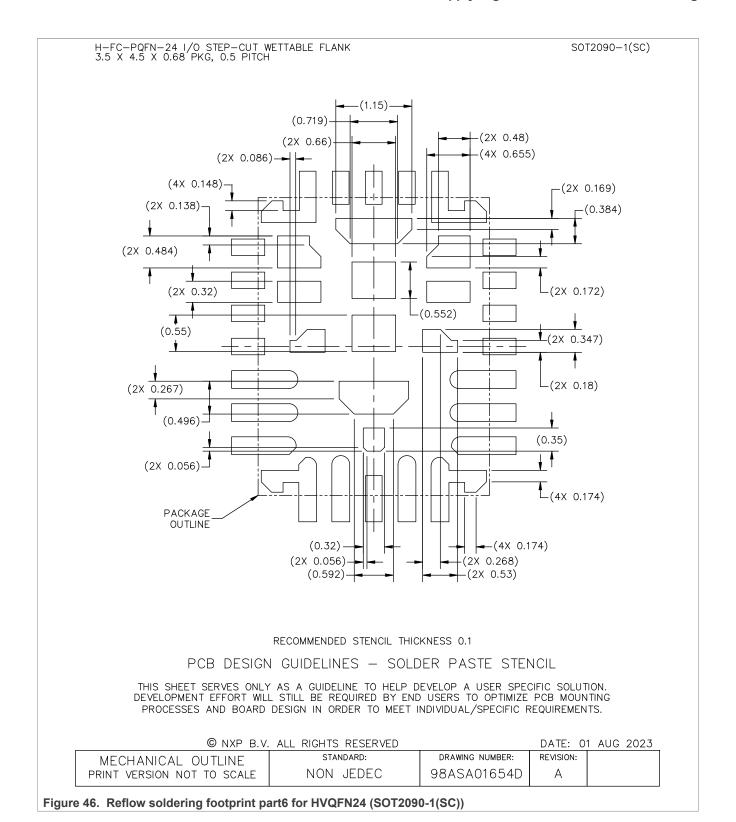

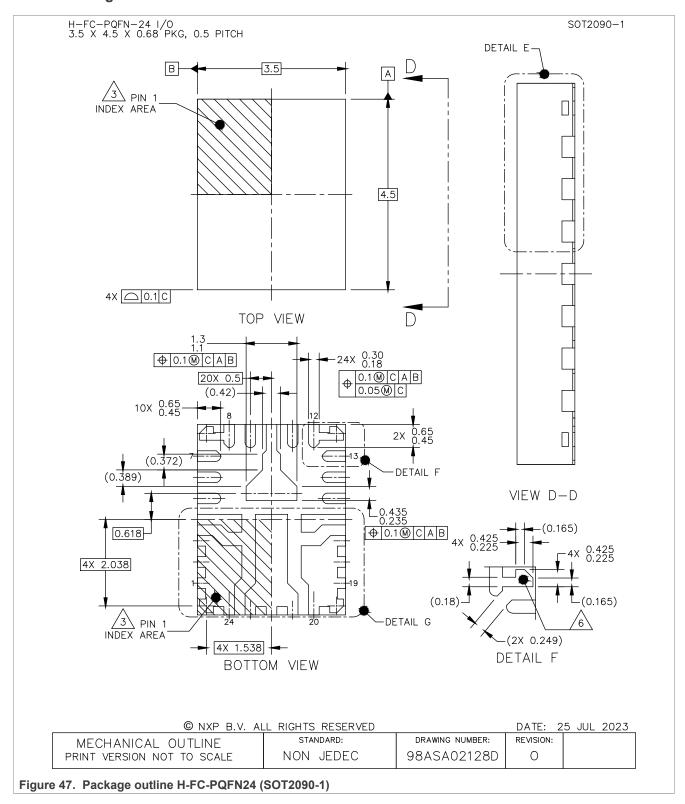

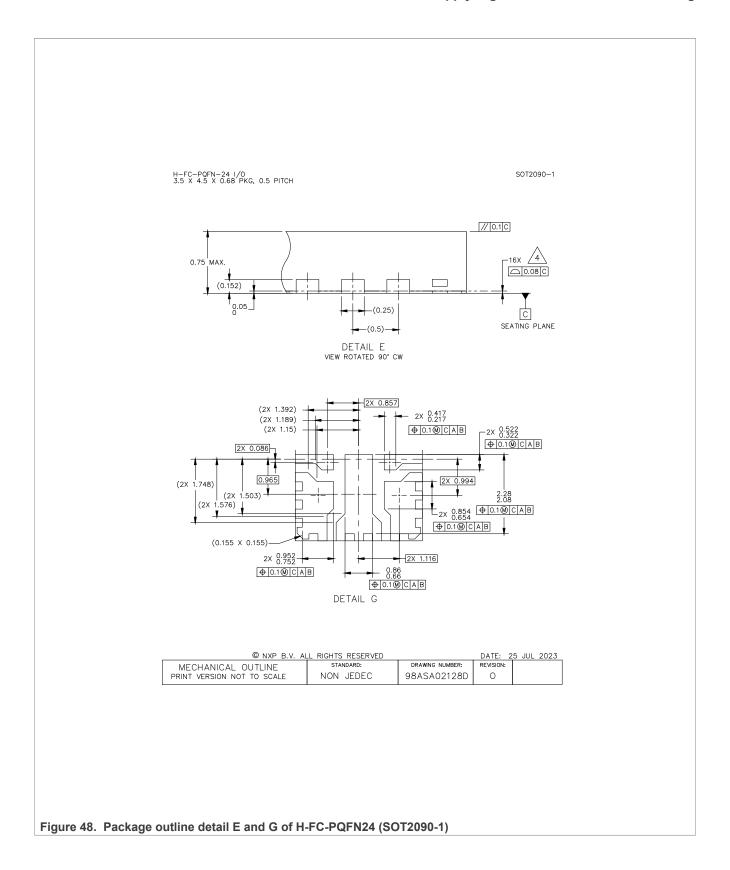

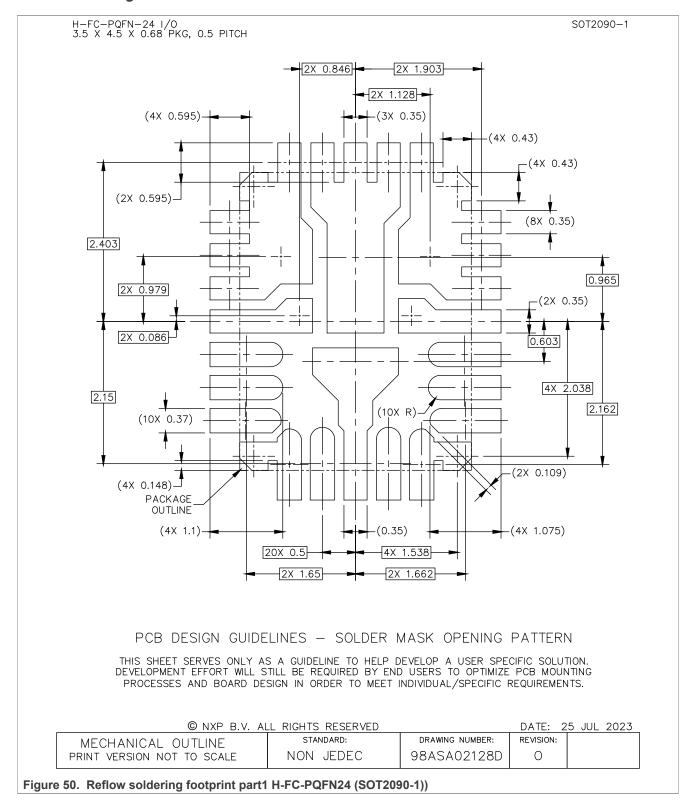

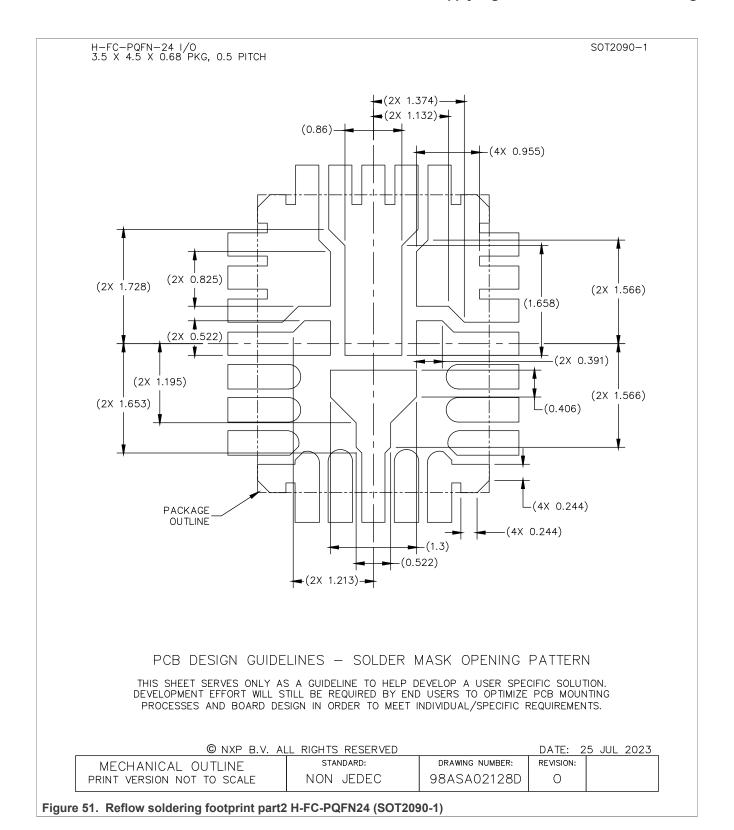

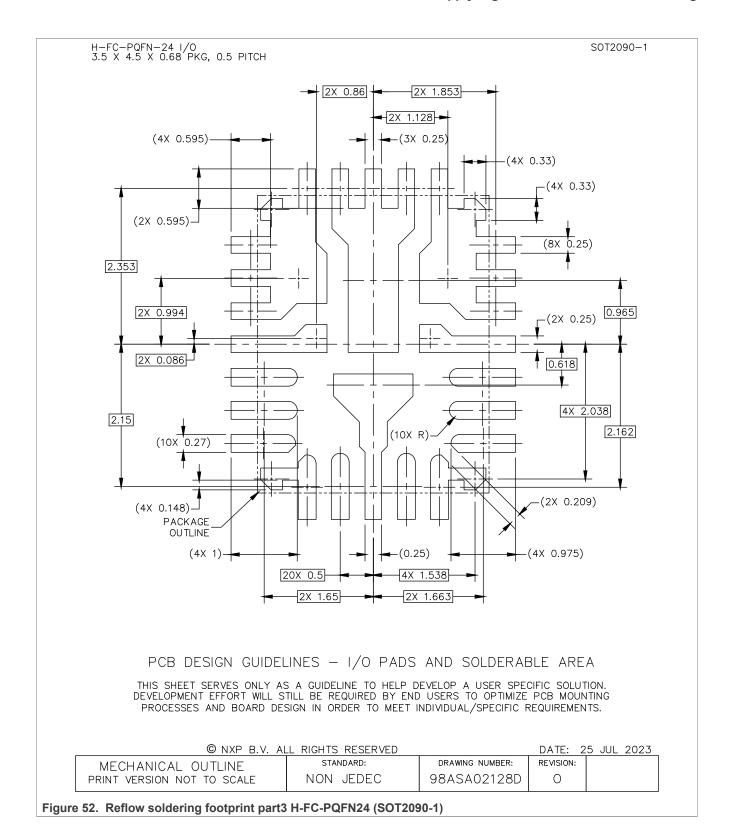

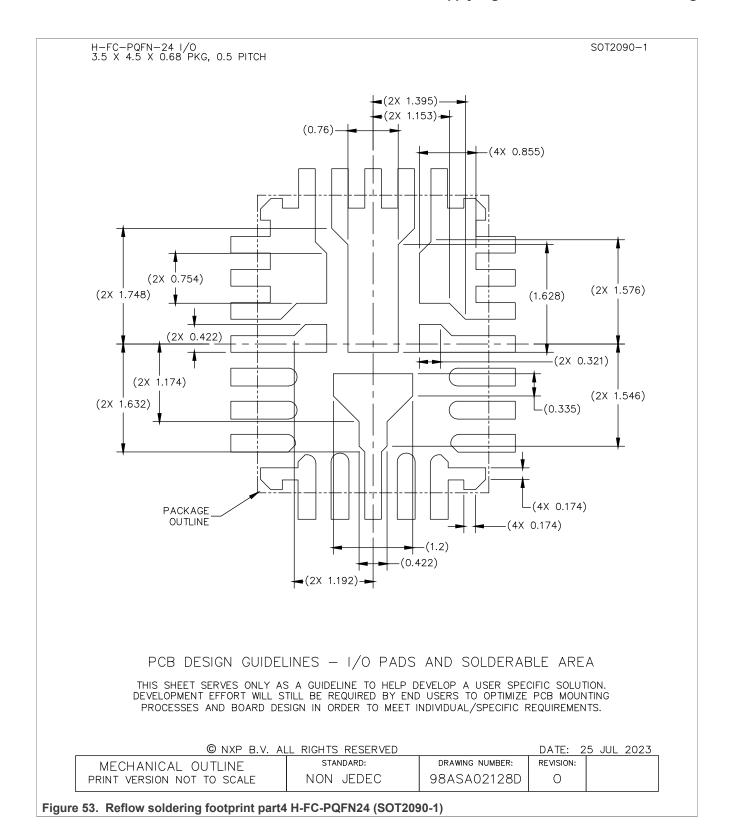

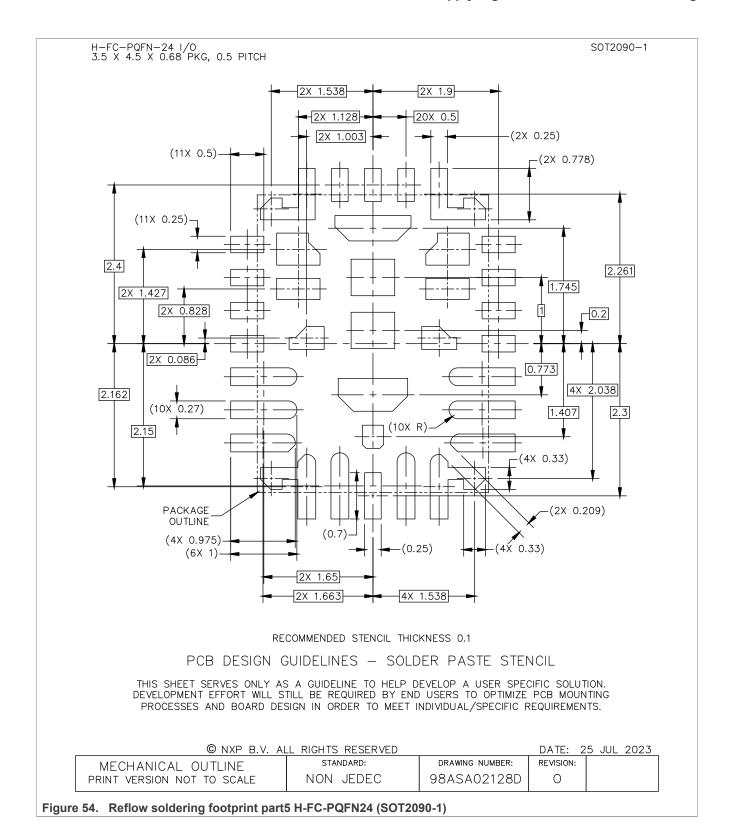

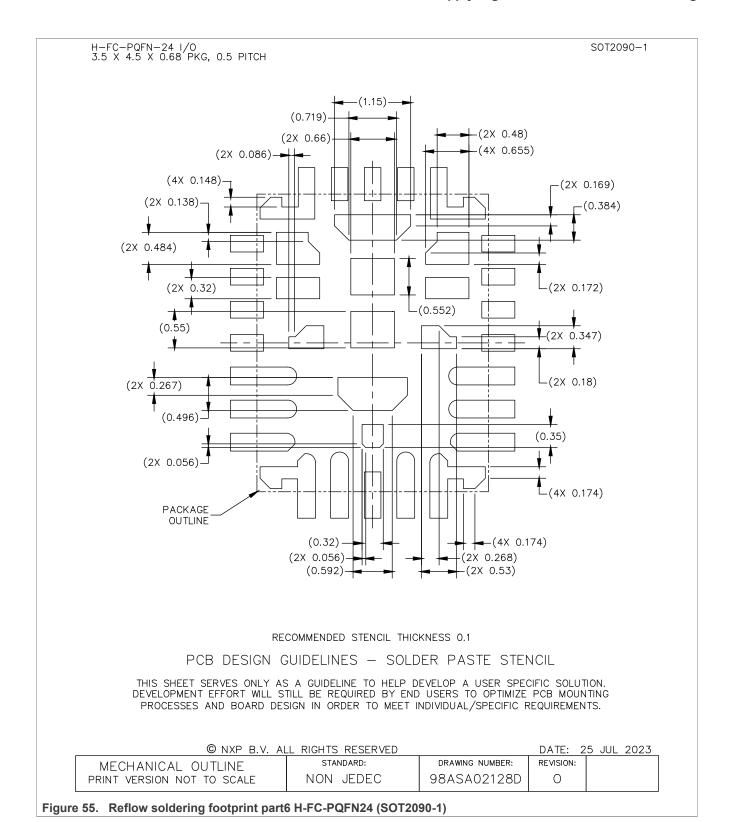

- 3.5 mm x 4.5 mm WF-QFN package

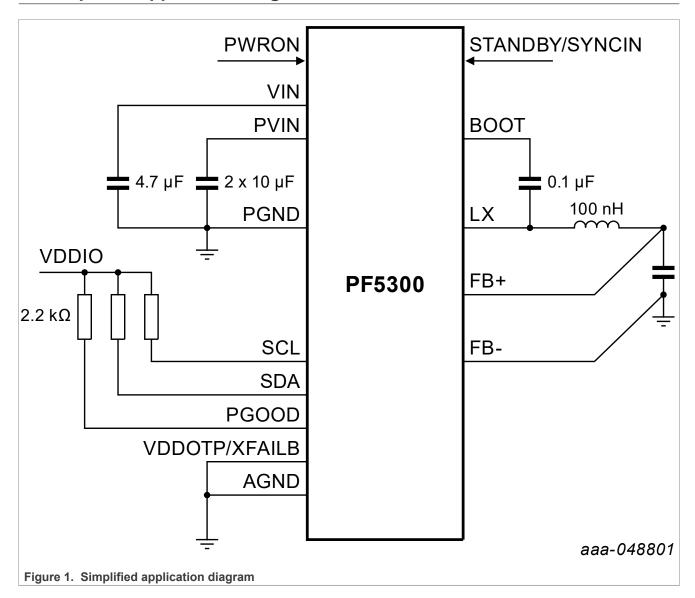

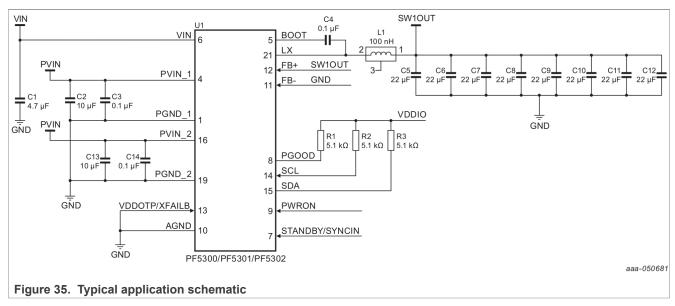

# 3 Simplified application diagram

# **Ordering information**

Table 1. Ordering information

| Part number <sup>[1]</sup>    | Current capability | Application | Pack                                             | rage          |  |

|-------------------------------|--------------------|-------------|--------------------------------------------------|---------------|--|

| Part Humber                   | Current Capability | Application | Description                                      | Version       |  |

| MPF53BDAMMA1ES <sup>[2]</sup> |                    |             |                                                  |               |  |

| MPF5300AMMA0ES <sup>[3]</sup> |                    |             |                                                  |               |  |

| MPF5300AMBA0ES <sup>[4]</sup> | 12A                |             |                                                  |               |  |

| MPF5300AMDA0ES <sup>[5]</sup> | IZA                |             |                                                  |               |  |

| MPF5300AMMALES <sup>[6]</sup> |                    |             | HWQFN24, thermal                                 |               |  |

| MPF5300AMMAMES <sup>[6]</sup> |                    |             | enhanced, very-                                  |               |  |

| MPF5301AMMA0ES <sup>[3]</sup> | 8A                 | Automotive  | very thin quad flat package, no leads,           | SOT2090-1(SC) |  |

| MPF5301AMBA0ES <sup>[4]</sup> |                    | Automotive  | 24 terminals, step-cut<br>wettable flank, 0.5 mm | 3012090-1(30) |  |

| MPF5301AMDA0ES <sup>[5]</sup> |                    | DA          | pitch, 3.5 mm x 4.5                              |               |  |

| MPF5301AMMABES <sup>[6]</sup> |                    |             | mm x 0.68 mm body                                |               |  |

| MPF5302AMMA0ES <sup>[3]</sup> |                    |             |                                                  |               |  |

| MPF5302AMBA0ES <sup>[4]</sup> | 15A                |             |                                                  |               |  |

| MPF5302AMDA0ES <sup>[5]</sup> | IDA                |             |                                                  |               |  |

| MPF5302AMMAAES <sup>[6]</sup> |                    |             |                                                  |               |  |

| MPF5300AVNA0EP <sup>[3]</sup> | 12A                |             | H-FC-PQFN24,                                     |               |  |

| MPF5301AVNA0EP <sup>[3]</sup> | 9.4                |             | thermal enhanced - flip chip - plastic           |               |  |

| MPF5301AVNABEP <sup>[6]</sup> | 8A                 | Industrial  | quad flat non-lead,                              | SOT2090-1     |  |

| MPF5302AVNA0EP <sup>[3]</sup> | 150                |             | 24 terminals, 0.5 mm<br>pitch, 3.5 mm x 4.5      |               |  |

| MPF5302AVNAAEP <sup>[6]</sup> | 15A                |             | mm x 0.68 mm body                                |               |  |

- To order parts in tape and reel, add R2 suffix to the part number.

- Safety grade: QM, pre-programmed for S32G3 application to be paired with VR5510.

- Safety grade: QM, non-programmed device. [3]

- Safety grade: ASIL B, non-programmed device. Safety grade: ASIL D, non-programmed device.

- Safety grade: QM, programmed device.

OTP emulation and programming performed by the customer is allowed during engineering development using NXP's latest graphical user interface and socketed evaluation board.

Customer is not allowed to perform OTP programming for production purposes. Only NXP or a recommended third party are allowed to program the device for production purposes.

# **Applications**

- · Automotive infotainment, gateway, domain controllers

- · High-end consumer and industrial

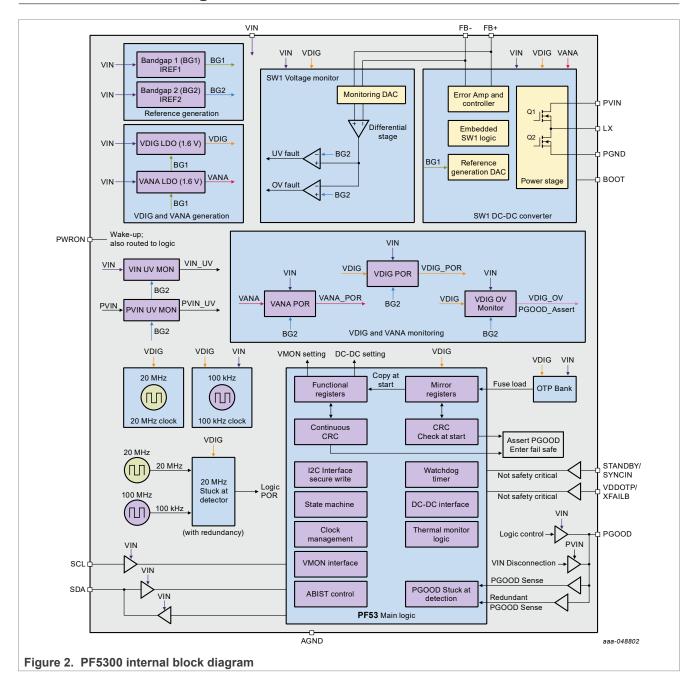

# 6 Internal block diagram

# 7 Pinning information

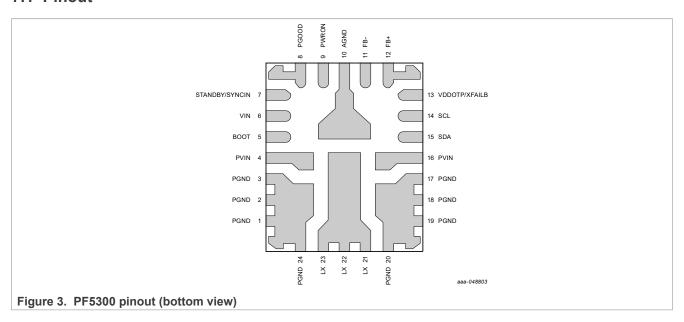

# 7.1 Pinout

# 7.2 Pin descriptions

Table 2. Pin descriptions

| Pin number     | Pin name           | Description                                                                                                                                         | Minimum<br>operating<br>voltage (V) | Maximum operating voltage (V) |

|----------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------|

| 1-3, 17-20, 24 | PGND               | Power ground of buck converter. Connect to ground plane including top layer.                                                                        | -0.3                                | 0.3                           |

| 4, 16          | PVIN               | PVIN input to buck converter. Bypass with 0.1 μF and 10 μF on either side with the shortest possible loop distance between corresponding PGND pins. | -0.3                                | 5.5                           |

| 5              | воот               | Bootstrap pin for high-side gate drive. Connect 0.1 μF from BOOT to LX pin.                                                                         | (LX - 0.3 V)                        | (LX + 5.5 V)                  |

| 6              | VIN                | Gate drive input. Connect to gate drive supply (preferably 5.0 V). Bypass with 4.7 µF capacitor.                                                    | -0.3                                | 5.5                           |

| 7              | STANDBY/<br>SYNCIN | External clock synchronization input. Connect to ground if not used. Optionally used as STANDBY input to enter Low-power mode at the system level.  | -0.3                                | 5.5                           |

| 8              | PGOOD              | Open-drain PGOOD output. Pull up to external pullup voltage via 4.7 kΩ resistor.                                                                    | -0.3                                | 5.5                           |

| 9              | PWRON              | Enable input. 1.8 V logic accepted. Also used to enter Debug mode when pulled up to 8 V prior to startup.                                           | -0.3                                | 9                             |

| 10             | AGND               | Analog ground of IC. Connect to ground plane using a via.                                                                                           | -0.3                                | 0.3                           |

| 11             | FB-                | Differential amplifier negative input. Connect to negative (ground) end of output voltage.                                                          | -0.3                                | 5.5                           |

Table 2. Pin descriptions...continued

| Pin number | Pin name          | Description                                                                                                                                                                                                                                                                                | Minimum<br>operating<br>voltage (V) | Maximum operating voltage (V) |

|------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------|

| 12         | FB+               | Differential amplifier positive input. Connect to positive end of output voltage. Route FB+ and FB- in parallel on the PCB to reduce differential noise.                                                                                                                                   | -0.3                                | 5.5                           |

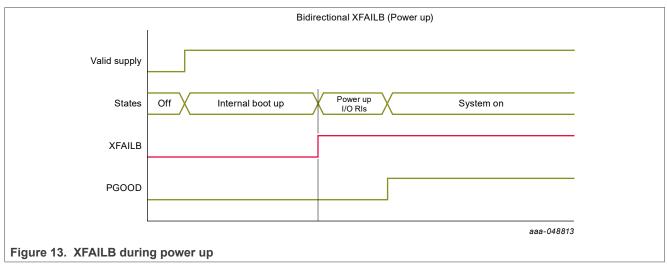

| 13         | VDDOTP/<br>XFAILB | VDDOTP used to program OTP memory and enter Fuse Emulation mode. Optional use as XFAILB pin to communicate with other NXP PF PMICs. Connect to ground in application if XFAILB function is not used. Pull up to XFAILB bus voltage with a 4.7 k $\Omega$ resistor if the function is used. | -0.3                                | 9                             |

| 14         | SCL               | I <sup>2</sup> C clock input. Pull up to external I/O voltage.                                                                                                                                                                                                                             | -0.3                                | 5.5                           |

| 15         | SDA               | I <sup>2</sup> C data line. Pull up to external I/O voltage.                                                                                                                                                                                                                               | -0.3                                | 5.5                           |

| 21-23      | LX                | Output of buck converter.                                                                                                                                                                                                                                                                  | -0.7                                | 5.5                           |

# 8 Absolute maximum ratings

Table 3. Absolute maximum ratings

| Symbol                              | Parameter                                                                                | Min          | Max        | Unit |

|-------------------------------------|------------------------------------------------------------------------------------------|--------------|------------|------|

| VIN, PVIN                           | Main input supply voltage <sup>[1]</sup>                                                 | -0.3         | 6.0        | V    |

| LX                                  | Regulator switching voltage [1]                                                          | -0.7         | 6.0        | V    |

| BOOT                                | Bootstrap voltage <sup>[1]</sup>                                                         | (LX - 0.3 V) | (LX + 6 V) | V    |

| FB+, FB-                            | Regulator feedback <sup>[1]</sup>                                                        | -0.3         | 6.0        | V    |

| PGOOD, STANDBY/<br>SYNCIN, SCL, SDA | I/O voltages [1]                                                                         | -0.3         | 6.0        | V    |

| VDDOTP/XFAILB,<br>PWRON             | OTP programming input supply voltage (VDDOTP/XFAILB), Debug entry (PWRON) <sup>[1]</sup> | -0.3         | 10         | V    |

<sup>[1]</sup> Pin reliability may be affected if system voltages are above the maximum operating range of 6.0 V for an extended period of time. To minimize system reliability impact, system must not operate above 6.0 V for more than 1800 seconds over the lifetime of the device.

# 9 Characteristics

# 9.1 ESD ratings

All ESD specifications are compliant with AEC-Q100 specification.

Table 4. ESD ratings

| Symbol   | Parameter                       | Min | Тур | Max  | Unit |

|----------|---------------------------------|-----|-----|------|------|

| VESD     | Human body model <sup>[1]</sup> | _   | _   | 2000 | V    |

| VESD     | Charge device model [1]         | _   | _   | 500  | V    |

| ILATCHUP | Latch-up current                | _   | _   | 100  | mA   |

<sup>[1]</sup> ESD testing is performed in accordance with the human body model (HBM) (CZAP = 100 pF, RZAP = 1500 Ω), and the charge device model (CDM), robotic (CZAP = 4.0 pF).

PF5300\_PF5301\_PF5302

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

## 9.2 Thermal characteristics

Table 5. Thermal characteristics

| Symbol         | Parameter                                  | Min | Тур | Max | Unit |

|----------------|--------------------------------------------|-----|-----|-----|------|

| T <sub>A</sub> | Ambient operating temperature              | -40 | _   | 125 | °C   |

| T <sub>A</sub> | Ambient operating temperature (industrial) | -40 | _   | 105 | °C   |

| Tj             | Junction temperature                       | -40 | _   | 150 | °C   |

| TST            | Storage temperature range                  | -55 | _   | 150 | °C   |

| TPPRT          | Peak package reflow temperature            | _   | _   | 260 | °C   |

Table 6. QFN24 thermal resistance and package dissipation ratings

| Rating                                                                                | Board type <sup>[1]</sup> | Symbol | Value | Unit |

|---------------------------------------------------------------------------------------|---------------------------|--------|-------|------|

| Junction to Ambient<br>Thermal Resistance <sup>[2]</sup>                              | JESD51-9, 2s2p            | RθJA   | 41.3  | °C/W |

| Junction-to-Top of<br>Package Thermal<br>Characterization<br>Parameter <sup>[2]</sup> | JESD51-9, 2s2p            | ΨЈТ    | 0.6   | °C/W |

| Junction to Case<br>Thermal Resistance <sup>[3]</sup>                                 | JESD51-9                  | RθJC   | 8.4   | °C/W |

| Junction to Ambient<br>Thermal Resistance <sup>[4]</sup>                              | Customized, 2s6p          | RθJA   | 24.8  | °C/W |

<sup>[1]</sup> Thermal test board meets JEDEC specification for this package (JESD51-9).

# 9.3 Recommended operating conditions

All parameters are specified at Ta = -40 °C to 125 °C,  $PVIN = V_{IN} = 3.3 \text{ V}$ , PWRON = 1.8 V, no load on regulator, Fsw = 2.2 MHz, typical external component values, unless otherwise noted. Typical values are specified at 25 °C, unless otherwise noted.

**Table 7. Operating Conditions**

| Symbol          | Parameter                       | Min                   | Тур  | Max  | Unit |

|-----------------|---------------------------------|-----------------------|------|------|------|

| V <sub>IN</sub> | V <sub>IN</sub> operating range | VIN <sub>UVDET</sub>  | _    | 5.5  | V    |

| PVIN            | PVIN operating range            | PVIN <sub>UVDET</sub> | _    | 5.5  | V    |

| VIN_UVDET_R     | Rising V <sub>IN</sub> UVDET    | 2.85                  | 3.00 | 3.15 | V    |

| VIN_UVDET_F     | Falling V <sub>IN</sub> UVDET   | 2.80                  | 2.90 | 3.00 | V    |

| PVIN_UVDET_R    | Rising PVIN UVDET               | 2.6                   | 2.75 | 2.9  | V    |

| PVIN_UVDET_F    | Falling PVIN UVDET              | 2.5                   | 2.6  | 2.7  | V    |

Determined in accordance to JEDEC JESD51-2A natural convection environment. Thermal resistance data in this report is solely for a thermal performance comparison of one package to another in a standardized specified environment. It is not meant to predict the performance of a package in an application-specific environment.

<sup>[3]</sup> Junction-to-Case thermal resistance determined using an isothermal cold plate. Case is defined as the bottom of the packages (exposed pad).

Simulation of PF53 on an eight-layer (2s6p = eight layers) application representative PCB. Actual performance on a given application should be simulated by the customer to optimize thermal design of the system. IcePAK, Flotherm, and 3D PF5300 simulation models are available on NXP.com.

# 10 General description

# 10.1 Functional block diagram

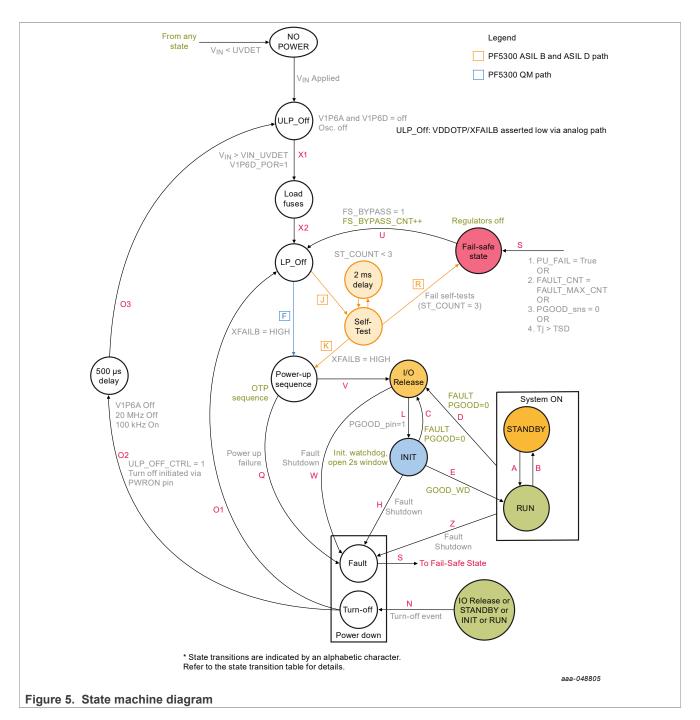

## 11 State machine

The PF5300 features a state-of-the-art state machine for a seamless processor interface. The state machine handles the IC startup, provides fault monitoring and reporting, and protects the IC and the system during fault conditions. The STATE[7:0] register provides information on the current state of the state machine. See Section 11.1 for descriptions of the states.

| Table 8. State transition table          |                                                                                       |

|------------------------------------------|---------------------------------------------------------------------------------------|

| Transition                               | Conditions                                                                            |

| Transition A Description: STANDBY to RUN | Condition 1: (STANDBY = 0 && STANDBYINV bit = 0 && (STBY_DELAY expiry if applicable)) |

| Transition A Description: STANDBY to RUN | Condition 2: (STANDBY = 1 && STANDBYINV bit = 1 && (STBY_DELAY expiry if applicable)) |

PF5300\_PF5301\_PF5302

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved. Document feedback

Table 8. State transition table...continued

| Transition                                         | Conditions                                                                                                                |

|----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Transition B Description: RUN to STANDBY           | Condition 1: (STANDBY = 1 && STANDBYINV bit = 0 && (STBY_DELAY expiry if applicable))                                     |

| Transition B Description: RUN to STANDBY           | Condition 2: (STANDBY = 0 && STANDBYINV bit = 1 && (STBY_DELAY expiry if applicable))                                     |

| Transition C Description: INIT to IO_Release       | Condition 1: PGOOD assertion (low) because of SW1 OV Fault With OTP_PGOOD_ SW1_OV = 1                                     |

| Transition C Description: INIT to IO_Release       | Condition 2: PGOOD assertion (low) because of SW1 UV Fault With OTP_PGOOD_ SW1_UV = 1                                     |

| Transition C Description: INIT to IO_Release       | Condition 3: PGOOD assertion (low) because of band gap error with OTP_PGOOD_ BG = 1                                       |

| Transition C Description: INIT to IO_Release       | Condition 4: PGOOD assertion (low) because of PGOOD stuck at 0                                                            |

| Transition C Description: INIT to IO_Release       | Condition 5: PGOOD assertion (low) because of no good watchdog refresh (if enabled) for 2 s and FAULT_CNT < FAULT_MAX_CNT |

| Transition C Description: INIT to IO_Release       | Condition 6: PGOOD assertion (low) because of PGOOD_RLS clear via I <sup>2</sup> C (PGOOD_SEQ = 0x00)                     |

| Transition D Description: System ON to IO_Release  | Condition 1: PGOOD assertion (low) because of SW1 OV fault with OTP_PGOOD_SW1_OV = 1                                      |

| Transition D Description: System ON to IO_Release  | Condition 2: PGOOD assertion (low) because of SW1 UV fault with OTP_PGOOD_ SW1_UV = 1                                     |

| Transition D Description: System ON to IO_Release  | Condition 3: PGOOD assertion (low) because of band gap error with OTP_PGOOD_ BG = 1                                       |

| Transition D Description: System ON to IO_Release  | Condition 4: PGOOD assertion (low) because of PGOOD stuck at 0                                                            |

| Transition D Description: System ON tol IO_Release | Condition 5: PGOOD assertion (low) because of WD_ERROR_CNT[3:0] >= WD_MAX_ERROR[1:0] and FAULT_CNT < FAULT_MAX_CNT        |

| Transition D Description: System ON to IO_Release  | Condition 6: PGOOD assertion (low) because of PGOOD_RLS clear via I <sup>2</sup> C (PGOOD_SEQ = 0x00)                     |

| Transition E<br>Description: INIT to RUN           | Condition 1:<br>2 s watchdog window petted with good watchdog refresh                                                     |

| Transition E<br>Description: INIT to RUN           | Condition 2. Watchdog disabled                                                                                            |

Table 8. State transition table...continued

| Transition                                                                    | Conditions                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transition F Description: LP_Off to power-up sequence (PF5300 QM Only)        | Condition 1:  PWRON = 1 (but less than debug threshold)  && PVIN > PVIN_UVDET  && Tj < TSD (If entered LP_Off via Transition U or O1. Bypass if entered LP_Off via Transition X2)  && {[(VIN < VIN_OVLO) && VIN_OVLO_SDWN = 1] OR [VIN_OVLO_SDWN = 0]}  && TRIM_NOK = 0  && OTP_NOK = 0  && VDDOTP < VDDOTP_threshold  && (OTP_XFAILB_EN = 0)                      |

| Transition F Description: LP_Off to power-up sequence (PF5300 QM Only)        | Condition 2:  PWRON = 1 (but less than debug threshold)  && PVIN > PVIN_UVDET  && Tj < TSD (If entered LP_Off via Transition U or O1. Bypass if entered LP_Off via Transition X2)  && {[(VIN < VIN_OVLO) && VIN_OVLO_SDWN = 1] OR [VIN_OVLO_SDWN = 0]}  && TRIM_NOK = 0  && OTP_NOK = 0  && VDDOTP < VDDOTP_threshold  && (OTP_XFAILB_EN = 1 && XFAILB_pin = High) |

| Transition H Description: INIT to power down (Fault)                          | Condition 1: FAULT_CNT = FAULT_MAX_CNT                                                                                                                                                                                                                                                                                                                             |

| Transition H Description: INIT to power down (Fault)                          | Condition 2:<br>Thermal shutdown Tj > TSD                                                                                                                                                                                                                                                                                                                          |

| Transition H Description: INIT to Power Down (Fault)                          | Condition 3:<br>Register Map CRC Error                                                                                                                                                                                                                                                                                                                             |

| Transition J Description: LP_Off to Self-test (PF5300 ASIL B and ASIL D Only) | Condition:  PWRON = 1 (but less than debug threshold)  && PVIN > PVIN_UVDET  && Tj < TSD (If entered LP_Off via Transition U or O1. Bypass if entered LP_Off via Transition X2)  && {[(VIN < VIN_OVLO) && VIN_OVLO_SDWN = 1] OR [VIN_OVLO_SDWN = 0]}  && TRIM_NOK = 0  && OTP_NOK = 0  && VDDOTP < VDDOTP_threshold                                                |

Table 8. State transition table...continued

| Transition                                                                               | Conditions                                                                                                                                                                             |

|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Transition K Description: Self-test to Power Up sequence (PF5300 ASIL B and ASIL D Only) | Condition 1 (assumes non-debug mode):  Pass all self-tests except ABIST (ABIST result don't care)  && (OTP_XFAILB_EN = 0)                                                              |

| Transition K Description: Self-test to power-up sequence (PF5300 ASIL B and ASIL D Only) | Condition 2 (assumes non-Debug mode):  Pass all self-tests except ABIST (ABIST result don't care)  && (OTP_XFAILB_EN = 1 && XFAILB_pin = High)                                         |

| Transition L Description: IO_Release to INIT                                             | Condition 1: PGOOD internally released and PGOOD_sns = 1 (high)                                                                                                                        |

| Transition N Description: RUN/STANDBY/INIT/IO_Release to Power Down (Turn-Off)           | Condition 1:<br>PWRON = 0                                                                                                                                                              |

| Transition N Description: RUN/STANDBY/INIT/IO_Release to Power Down (Turn-Off)           | Condition 2: PMIC_OFF = 1 && 500us_Shutdown_Timer_Expired                                                                                                                              |

| Transition N Description: RUN/STANDBY/INIT/IO_Release to Power Down (Turn-Off)           | Condition 3: VIN_OVLO_SDWN = 1 && VIN_OVLO event                                                                                                                                       |

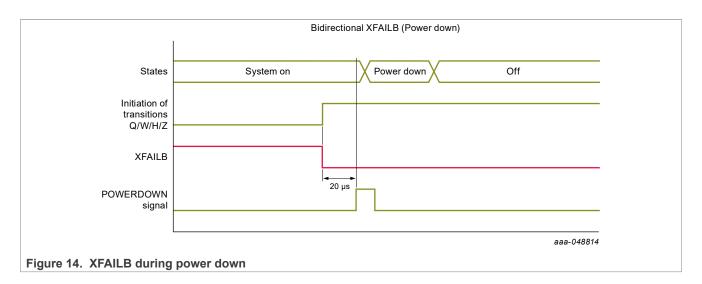

| Transition N Description: RUN/STANDBYINIT/IO_Release to Power Down (Turn-Off)            | Condition 4:  XFAILB_pin = 0 (pulled low externally; OTP_XFAILB_EN = 1)                                                                                                                |

| Transition O1 Description: Power Down (Turn-off) to LP_Off                               | Condition 1:  Power Down sequence (including OTP_PD_SEQ_DLY) finished via PMIC_OFF I <sup>2</sup> C path (ULP_OFF_CTRL = don't care)                                                   |

| Transition O1 Description: Power Down (Turn-off) to LP_Off                               | Condition 2:  Power Down sequence (including OTP_PD_SEQ_DLY) finished via VIN_OVLO path (ULP_OFF_CTRL = don't care)                                                                    |

| Transition O1 Description: Power Down (Turn-off) to LP_Off                               | Condition 3:  Power Down sequence (including OTP_PD_SEQ_DLY) initiated via PWRON = 0 path && ULP_OFF_CTRL = 0                                                                          |

| Transition O1 Description: Power Down (Turn-off) to LP_Off                               | Condition 4:  Power Down sequence (including OTP_PD_SEQ_DLY) finished via XFAILB path (ULP_OFF_CTRL = don't care)                                                                      |

| Transition O2/O3 Description: Power Down (Turn-off) to ULP_Off                           | Condition 1:  Power Down sequence (including OTP_PD_SEQ_DLY) finished via PWRON = 0 path && ULP_OFF_CTRL = 1  Note: 500 µs delay between O2 and O3 to allow discharge of V1P6A output. |

Table 8. State transition table...continued

| Table 8. State transition tablecontinued                          |                                                                                                                          |  |  |  |

|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Transition                                                        | Conditions                                                                                                               |  |  |  |

| Transition Q Description: Power Up Sequence to Power Down (Fault) | Condition 1: SW1 failure (OV/UV) during power-up sequence (if OTP_SW1_PGOOD_OV/UV = 1)                                   |  |  |  |

| Transition Q Description: Power Up Sequence to Power Down (Fault) | Condition 2: PGOOD internally asserted low and PGOOD_sns = 1 (high) for > 10 μs (to detect external stuck-at-high fault) |  |  |  |

| Transition Q Description: Power Up Sequence to Power Down (Fault) | Condition 3: Register Map CRC Error                                                                                      |  |  |  |

| Transition R Description: Self-Test to Fail-safe State            | Conditions:<br>ST_COUNT = 3 (Self-test fails 3 times)                                                                    |  |  |  |

| Transition S Description: Power Down (Fault) to Fail-safe State   | Condition 1: Power Down Sequencer (including OTP_PD_SEQ_DLY) is finished                                                 |  |  |  |

| Transition U Description: Fail-safe State to LP_Off               | Condition 1:  1. OTP_FS_BYPASS=1 && OTP_FS_BYPASS_CNT=0 && FS_BYPASS_CNT<15                                              |  |  |  |

| Transition U Description: Fail-safe State to LP_Off               | Condition 2: OTP_FS_BYPASS=1 && OTP_FS_BYPASS_CNT=1                                                                      |  |  |  |

| Transition V Description: Power Up Sequence to IO_ Release        | Condition 1: Completion of the power-up sequence according to OTP.                                                       |  |  |  |

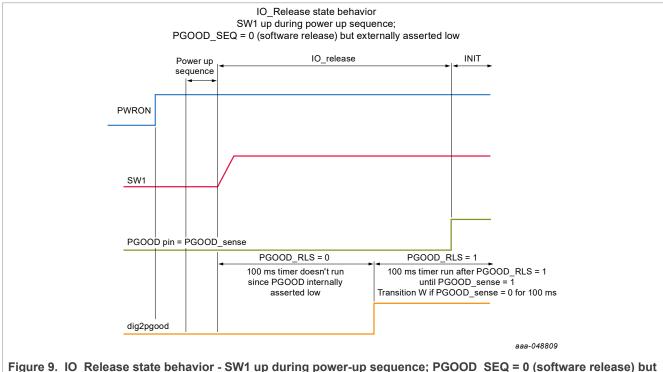

| Transition W Description: IO_Release to Power Down (Fault)        | Condition 1:  FAULT_CNT = FAULT_MAX_CNT                                                                                  |  |  |  |

| Transition W Description: IO_Release to Power Down (Fault)        | Condition 2: PGOOD internally released and PGOOD_sns = 0 (low) until 100 ms timer expires                                |  |  |  |

| Transition W Description: IO_Release to Power Down (Fault)        | Condition 3:<br>Thermal shutdown Tj > TSD                                                                                |  |  |  |

| Transition W Description:IO_Release to Power Down (Fault)         | Condition 4: Register Map CRC Error                                                                                      |  |  |  |

| Transition X1 Description: ULP_Off to LP_Off                      | Condition 1: PWRON = 1                                                                                                   |  |  |  |

| Transition X2 Description: Fuse Load to LP_OFF                    | Condition: Fuse Load complete                                                                                            |  |  |  |

| Transition Z Description: System On to Power Down (Fault)         | Condition 1: FAULT_CNT = FAULT_MAX_CNT                                                                                   |  |  |  |

| Transition Z Description: System On to Power Down (Fault)         | Condition 2:<br>Thermal shutdown Tj > TSD                                                                                |  |  |  |

| Transition Z Description: System On to Power Down (Fault)         | Condition 3: Register Map CRC Error                                                                                      |  |  |  |

## 11.1 State descriptions

## 11.1.1 ULP\_Off state

The ULP Off state is an Ultra-low Power-off mode with very low quiescent current.

When  $V_{IN}$  is applied, the device moves to this state and waits for a power-on event. In this state, the internal bias circuits are off to maintain the low Iq requirement, and only the PWRON detection circuits are enabled.

During power down, the ULP\_OFF\_CTRL bit determines the transition to the ULP\_Off state. If power down is because of PWRON going low, if the ULP\_OFF\_CTRL = 0, the state machine moves to LP\_Off directly. If ULP\_OFF\_CTRL = 1, the state machine transitions to the ULP\_Off state, where the internal regulators are off to reduce the supply current consumption.

While powering off into the ULP\_Off state results in lower quiescent current, powering off into the LP\_Off state results in faster power up.

The initial value of the ULP\_OFF\_CTRL bit is loaded from the OTP\_ULP\_OFF\_CTRL bit.

#### 11.1.2 Load fuses

During a power up from the ULP\_Off state, the fuses (for trim and OTP) are loaded into the mirror registers and the functional I<sup>2</sup>C registers.

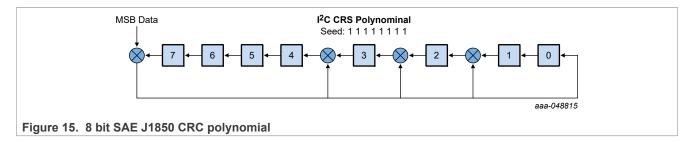

The fuse circuits have a CRC error check routine, which reports and protects against register loading errors on the mirror registers. If a register loading error is detected, the corresponding TRIM\_NOK or OTP\_NOK flag is set and the device does not power up further.

# 11.1.3 LP\_Off state

The LP\_Off state is a Low Power-off mode with current consumption higher than the ULP\_Off mode. All the internal circuits are ON in this state, and the device transitions to the power-up sequence state depending on the PWRON pin status.

During this state, if PWRON goes high, the device moves to start the power-up sequence as defined in the OTP settings. See <u>Section 15.1</u> for details on Debug entry while in LP\_Off.

When ULP\_OFF\_CTRL = 0, the device enters the LP\_Off state from IO\_Release, INIT, or System ON states when turned off.

# 11.1.4 Self-test routine (PF5300 ASIL B and ASIL D only)

When the device transitions from the LP\_Off state, it moves into the self-test routine and performs tests to verify the integrity of the internal circuits.

During the self-test routine, the following blocks are verified:

- 1. The high-speed clock circuit operates within a maximum 15 % tolerance.

- 2. The outputs of both the voltage generation band gap and the monitoring band gap are not more than 120 mV apart from each other.

- 3. A CRC is performed on the OTP mirror registers to ensure the integrity of the registers before powering up.

- 4. ABIST of SW1 OV and UV monitors

The self-test routine takes about eleven 100 kHz clock cycles (approximately 110  $\mu$ s).

To allow for varying settling times for the internal band gap and clocks, the self-test block is executed up to three times (with 2.0 ms between each test) in case of a failure. If a failure is encountered, the state machine

PF5300\_PF5301\_PF5302

PF5300; PF5301; PF5302

12 A / 8 A / 15 A core supply regulators with AVP and watchdog

proceeds to the fail-safe state. Failure of 1, 2, or 3 above is considered a self-test failure. Failure of ABIST is not considered a self-test failure.

#### 11.1.4.1 ABIST test on all voltage monitors

The SW1 OV and UV monitors are checked for functional operation during the self-test routine. This check of the voltage monitors is referred to as ABIST in this document. A failure in the ABIST test is not interpreted as a self-test failure; it only sets the corresponding ABIST flag for system information. The processor is responsible for reading the information and deciding whether it can continue with a safe operation.

Upon a successful self-test, the state machine proceeds to the power-up sequence state.

#### 11.1.5 Power-up sequence

During the power-up sequence, the PF5300 starts up per OTP programmed power-up sequence/timing.

If SW1 has an OV or UV fault at the end of the power-up sequence (if OTP\_PGOOD\_SW1\_OV or OTP\_PGOOD\_SW1\_UV = 1), the PF5300 waits for up to 2 ms to allow the output voltage to settle and continue the boot up after OV and/or UV pass. If OV/UV persists after 2 ms, it is considered a power-up failure. After a power-up failure, the state machine proceeds to the Fail-safe state via Transition Q and increments the fault counter.

During the power-up sequence, PGOOD is checked for a stuck at high fault (internally asserted low, but externally high) and Transition Q is taken if PGOOD is stuck high for more than 10 µs. See <u>Table 8</u> for full conditions. The PGOOD pin is checked for stuck-at faults continuously. See <u>Section 12.7.3</u> for details.

The PGOOD pin can also be programmed, as part of the power-up sequence, to allow controls of its release timing. See <u>Section 12.3.2</u> for details.

When PGOOD is internally released high, but externally pulled low, the FAULT\_CNT[3:0] is incremented. If it is expected that the PGOOD is externally asserted low while the PF5300 may have released it, set OTP\_FAULT\_MAX\_CNT[2:0] to > 3b'000. This is to ensure that FAULT\_CNT does not reach its maximum limit because of a systematic event.

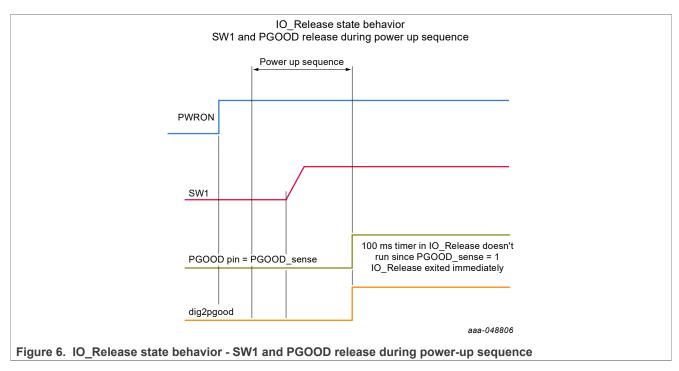

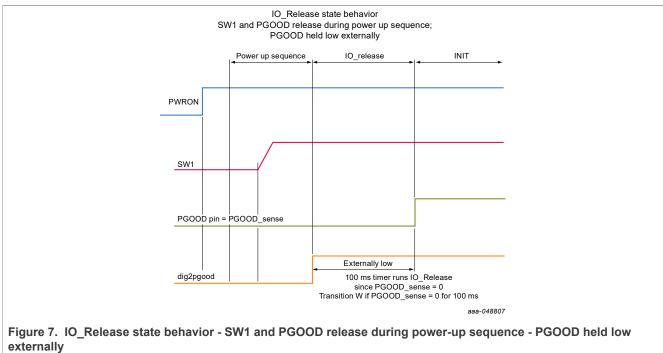

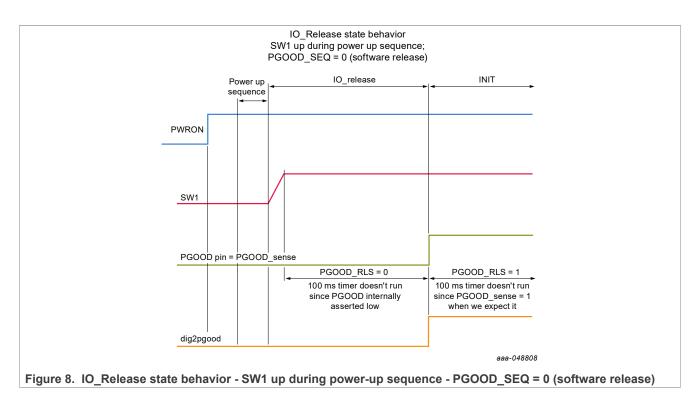

#### 11.1.6 IO\_Release state

If the Power Up state is successfully completed, the state machine transitions to the IO\_Release state. PGOOD\_sns = 1 is a condition to exit the IO\_Release state. A 100 ms timer becomes active in the IO\_Release state if PGOOD is internally released. This timer is to check whether the PGOOD pin is shorted to ground (internally released, but externally low). If a short to GND is detected for more than 100 ms, device fault shutdown is initiated. The 100 ms timer is disabled in Debug mode. Figure 6 and Figure 7 show some examples of the IO\_Release behavior.

#### 11.1.7 INIT state

externally asserted low

If the Power Up state is completed and PGOOD is released, the state machine transitions to the INIT state. In this state, the processor is expected to boot up and set up specific registers of the PMIC.

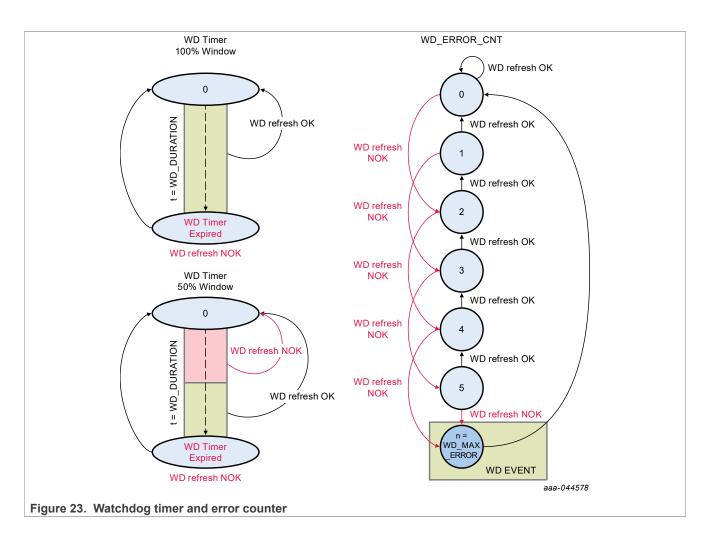

The INIT window must be closed within 2 seconds of entering the INIT state with a good watchdog refresh. Expiration of this timer (absence of good watchdog refresh) is considered to be a watchdog event and the state machine will transition to the IO Release state, assert PGOOD, and increment the fault counter.

If the watchdog is disabled, the INIT state is bypassed automatically without waiting for a refresh.

Upon state transition, the state machine exits into the System ON state.

#### 11.1.8 System ON state

The System ON state is a virtual state composed of two modes of operations: the RUN state and the STANDBY state.

#### **RUN state**

In this state, regulator-specific registers to control SW1's output voltage, operation mode and/or enable/disable state can be modified.

By default, the SW1\_VOLT[7:0] registers are loaded with the data stored in the OTP\_SW1\_VOLT[7:0] register. In the RUN state, SW1 regulates to the voltage set by SW1\_VOLT[7:0] register. The user can change the SW1 voltage dynamically by changing the SW1\_VOLT[7:0] register value.

#### **STANDBY state**

SW1 regulates the voltage set by SW1\_STBY\_VOLT[7:0] register. If the STANDBY/SYNCIN pin is configured as STANDBY pin by setting OTP\_SYNCIN\_EN = 0, the STANDBY pin can be toggled to change SW1's regulation voltage. This presents a way to dynamically change SW1's voltage that is faster than using I<sup>2</sup>C to change SW1\_VOLT[7:0] while in the RUN state.

OTP\_SW1\_DVS\_MAX[7:0] and OTP\_SW1\_DVS\_MIN[7:0] set the maximum and minimum values of the SW1\_VOLT[7:0] and SW1\_STBY\_VOLT[7:0] registers that are accepted. This is useful to prevent unintended values at the regulator output that may potentially cause harm. If the user attempts to write a value to SW1\_VOLT[7:0] or SW1\_STBY\_VOLT[7:0] beyond the OTP\_SW1\_DVS\_MAX[7:0] and OTP\_SW1\_DVS\_MIN[7:0] values, the PF5300 rejects the write attempt, and the DVS\_ERR\_I flag is set.

Once a STANDBY exit or entry event is recognized and initiated, the STANDBY pin is masked until the transition is complete. OTP\_STBY\_DLY[5:0] bits can be used to add a delay at the start of the transition when entering or exiting the STANDBY state. The delay value is (OTP\_STBY\_DELAY[5:0] \* SEQ\_TBASE[1:0]). If OTP\_STBY\_DELAY[5:0] = 0x00, no delay is added.

#### 11.1.9 Power-down state

During the Power-down state, SW1 is disabled and PGOOD is asserted low per the configured power-down sequence. The power-down sequence is programmable as defined in Section 12.4.2.

Two types of events may lead to the power-down sequence:

- 1. Non-faulty turn-off events: Depending on the ULP\_OFF\_CTRL bit, move directly into LP\_Off state or ULP\_OFF state as soon as the power-down sequence is finalized.

- 2. Turn-off events because of a PMIC fault: move to the Fail-safe transition as soon as the power-down sequence is finalized.

## 11.1.10 Fail-safe state

The Fail-safe state is a fault state where the PMIC turns off the regulator and either remains in the Fail-safe state or can be programmed to restart the power-up sequence. The transition to this state is because of any of the following PMIC faults being TRUE:

1. Power-up fault (PU FAIL)

PF5300\_PF5301\_PF5302

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

- 2. PGOOD sense fault (PG FAIL)

- 3. PGOOD short to high

- 4. FAULT\_CNT = FAULT\_MAX\_CNT (REG\_FAIL)

- 5. Junction temperature > the thermal shutdown threshold (TSD\_FAIL)

- 6. Register CRC error

The Fail-safe state provides the following status bits:

- PU\_FAIL will be set to 1 when the state machine powered down because of a power-up failure.

- PG FAIL will be set to 1 when the state machine powered down because of PGOOD failure.

- REG\_FAIL will be set to 1 when the state machine powered down because of a regulator failure (fault counter maxed out).

- TSD\_FAIL will be set to 1 when the state machine powered down because of a thermal shutdown.

The xxx\_FAIL bits will be reset to 0 when  $V_{\text{IN}}$  crosses the UVDET threshold. The processor can read the FAIL bits during the System ON states (RUN and STANDBY) or the INIT state, in order to obtain information about the previous failure, provided the state machine is able to power up successfully after such failure. The processor should clear the FAIL bits by writing a 1 to them during the System ON states (RUN and STANDBY) and INIT state, provided the state machine is able to power up successfully after such failure.

The Fail-safe state works as a safety transition during a fault or as a lock-down upon a critical device/system failure. Upon entering the Fail-safe state, the OTP\_FS\_BYPASS bit configures whether the state machine will be able to exit the state back in to the System ON states through LP\_Off, or stay in the Fail-safe state. When the OTP\_FS\_BYPASS bit = 0, the fail-safe bypass feature is disabled, and the state machine will remain in the Fail-safe state indefinitely until a power cycle takes place. When the OTP\_FS\_BYPASS bit = 1, the fail-safe bypass feature is enabled, and the state machine will be allowed to transition from the Fail-safe state to the LP\_Off state, depending on the OTP\_FS\_BYPASS\_CNT bit. The state machine will provide a fail-safe bypass counter configured by OTP\_FS\_BYPASS\_CNT bit to count the number of bypass transitions. The fail-safe bypass counter is incremented every time the transition from the Fail-safe state to the LP\_Off state happens.

When OTP\_FS\_BYPASS\_CNT bit = 0, the number of transitions allowed will be configured to 15. When OTP\_FS\_BYPASS\_CNT bit = 1, the number of transitions allowed will be infinite. When OTP\_FS\_BYPASS\_CNT bit = 0, and if the fail-safe bypass counter reaches the maximum count value of 15, the state machine will stay in the Fail-safe state.

In the Fail-safe state, the SW\_1 regulator will be disabled.

# 12 General device operation

#### **12.1 UVDET**

$V_{IN}$  and PVIN need to be above their respective UVDET thresholds for powering up the PF5300.  $V_{IN}$  falling below the  $V_{IN\_UVDET\_F}$  threshold causes the PF5300 to shut down immediately (no power down sequence) whereas PVIN falling below  $P_{VIN\_UVDET\_F}$  does not cause a shutdown.

All parameters are specified at Ta = -40 °C to 125 °C,  $PVIN = V_{IN} = 3.3 \text{ V}$ , PWRON = 1.8 V, no load on regulator, Fsw = 2.2 MHz, typical external component values, unless otherwise noted. Typical values are specified at 25 °C, unless otherwise noted.

Table 9. UVDET thresholds

| Symbol       | Symbol Parameter              |      | Тур  | Max  | Unit |

|--------------|-------------------------------|------|------|------|------|

| VIN_UVDET_R  | Rising V <sub>IN</sub> UVDET  | 2.85 | 3.00 | 3.15 | V    |

| VIN_UVDET_F  | Falling V <sub>IN</sub> UVDET | 2.80 | 2.90 | 3.00 | V    |

| PVIN_UVDET_R | Rising PVIN UVDET             | 2.6  | 2.75 | 2.9  | V    |

PF5300\_PF5301\_PF5302

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

Table 9. UVDET thresholds...continued

| Symbol       | Parameter          | Min | Тур | Max | Unit |

|--------------|--------------------|-----|-----|-----|------|

| PVIN_UVDET_F | Falling PVIN UVDET | 2.5 | 2.6 | 2.7 | V    |

#### 12.2 VIN OVLO condition

The VIN\_OVLO circuit monitors the VIN pin for an overvoltage. VIN\_OVLO\_EN = 1 enables this monitoring. PF5300 can be programmed to react to an overvoltage in two ways:

- When the VIN\_OVLO\_SDWN = 0, the VIN\_OVLO event triggers an VIN\_OVLO\_I interrupt, but does not turn

off the device

- When the VIN\_OVLO\_SDWN = 1, the VIN\_OVLO event initiates a power-down sequence

The default configuration of the VIN\_OVLO\_EN bit is set by the OTP\_VIN\_OVLO\_EN bit in OTP. Likewise, the default value of the VIN\_OVLO\_SDWN bit is set by the OTP\_VIN\_OVLO\_SDWN upon power up.

Debounce on the VIN\_OVLO comparator is programmable to 10  $\mu$ s, 100  $\mu$ s, or 1.0 ms, by the VIN\_OVLO\_DBNC[1:0] bits. The default value for the VIN\_OVLO debounce is set by the OTP VIN OVLO DBNC[1:0] bits upon power up.

All parameters are specified at Ta = -40 °C to 125 °C, PVIN =  $V_{IN}$  = 3.3 V, PWRON = 1.8 V, no load on regulator, Fsw = 2.2 MHz, typical external component values, unless otherwise noted. Typical values are specified at 25 °C, unless otherwise noted.

Table 10. VIN OVLO debounce configuration

| VIN_OVLO_DBNC[1:0] | V <sub>IN</sub> OVLO debounce value (μs) |

|--------------------|------------------------------------------|

| 00                 | 10                                       |

| 01                 | 100                                      |

| 10                 | 1000                                     |

| 11                 | Reserved                                 |

All parameters are specified at Ta = -40 °C to 125 °C,  $PVIN = V_{IN} = 3.3 \text{ V}$ , PWRON = 1.8 V, no load on regulator, Fsw = 2.2 MHz, typical external component values, unless otherwise noted. Typical values are specified at 25 °C, unless otherwise noted.

Table 11. VIN\_OVLO specifications

| Symbol       | Parameter                                                     | Min | Тур | Max | Unit |

|--------------|---------------------------------------------------------------|-----|-----|-----|------|

| VIN_OVLO     | V <sub>IN</sub> overvoltage lockout rising <sup>[1]</sup>     | 5.6 | 5.8 | 6.0 | V    |

| VIN_OVLO_HYS | V <sub>IN</sub> overvoltage lockout hysteresis <sup>[1]</sup> | 100 | 120 | 140 | mV   |

[1] Operating the device above the maximum V<sub>IN</sub> = 5.5 V for an extended period of time may degrade and cause permanent damage to the device.

#### 12.3 Power up

# 12.3.1 Power-up events

Upon a power cycle (VIN\_UVDET\_R), the device moves to the ULP\_Off state by default. PWRON = 1 is a necessary condition for further power up to load fuses and to enter the LP\_Off state. From LP\_Off, the PF5300 proceeds to Power-up based on the conditions listed in <u>Table 8</u>.

## 12.3.2 Power-up sequencing

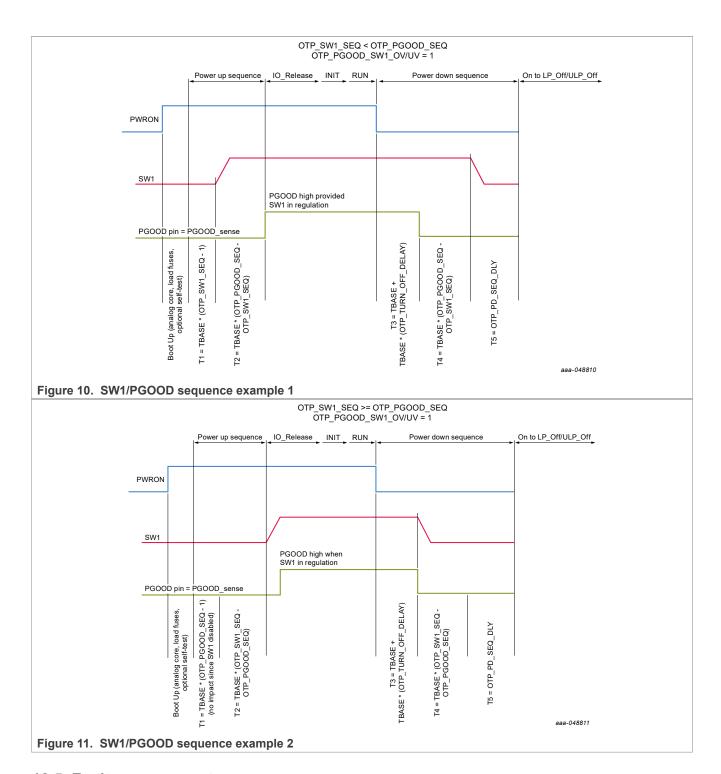

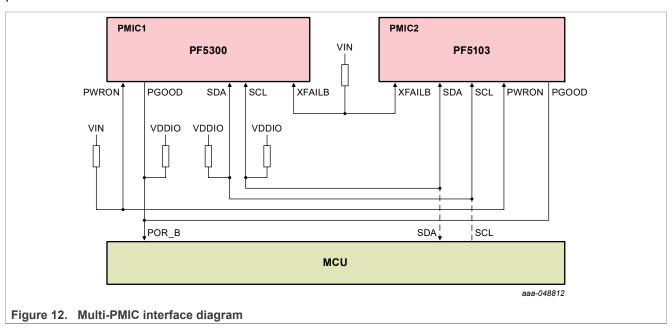

Although it has only one regulator, the PF5300 uses a power-up sequencer similar to other PF PMICs from NXP. This is useful in a multi-PMIC system where the user is trying to control power-up timing across different devices.

The power-up sequencer controls the time and order in which PGOOD and SW1 are enabled when going from the LP Off to the RUN state.

The OTP SEQ TBASE[1:0] bits set the default timebase for the power-up and power-down sequencer.

The SEQ\_TBASE[1:0] bits can be modified via I<sup>2</sup>C during the IO\_Release, INIT, and System ON states (RUN and STANDBY) in order to change the sequencer timing during RUN/STANDBY transitions, as well as the power-down sequence.

Table 12. Power-up timebase register

| OTP bits OTP_SEQ_TBASE[1:0] | Functional bits SEQ_TBASE[1:0] | Sequencer timebase (µs) |

|-----------------------------|--------------------------------|-------------------------|

| 00                          | 00                             | 100                     |

| 01                          | 01                             | 250                     |

| 10                          | 10                             | 500                     |

| 11                          | 11                             | 1000                    |

The DC-DC powers up based on the OTP\_SW1\_SEQ[5:0] setting. PGOOD is released high based on the OTP\_PGOOD\_SEQ[5:0] setting (in combination with passing PGOOD conditions as applicable). Sequence code 0x00 indicates that SW1/PGOOD are not part of the startup sequence and remain off. This is useful when the PF5300 is expected to power up via full software control. SW1\_MODE[1:0] and PGOOD\_RLS bits can be used to enable and release PGOOD, respectively. If SW1\_SEQ[5:0] is 0x00 (off) and a power-on event is present, the device waits in the IO\_Release state for software instructions to turn on SW1 and release PGOOD.

**Note:** There is no TBASE time prior to SLOT0. SLOT0 occurs immediately upon entering a power-up sequence. There is a TBASE time between SLOT0 and SLOT1, and so on.

Table 13. Power-up sequence registers

| OTP bits OTP_SW1_SEQ[5:0]/<br>OTP_PGOOD_SEQ[5:0] | Functional bits<br>SW1_SEQ[5:0]/<br>PGOOD_SEQ[5:0] | Sequence slot | Startup time (µs)                              |

|--------------------------------------------------|----------------------------------------------------|---------------|------------------------------------------------|

| 000000                                           | 000000                                             | Off           | Off                                            |

| 000001                                           | 000001                                             | 0             | SLOT0<br>(right after PWRON<br>event is valid) |

| 000010                                           | 000010                                             | 1             | SEQ_TBASE x SLOT1                              |

|                                                  |                                                    |               |                                                |

|                                                  |                                                    |               |                                                |

| ·                                                | •                                                  | •             | •                                              |

| 111111                                           | 111111                                             | 62            | SEQ_TBASE x SLOT62                             |

If  $OTP\_PGOOD\_SEQ[5:0] = 0x00$ , the default value of the  $PGOOD\_RLS = 0$ . The processor can decide to release this bit after turning on any one or all of the regulators.

When the processor sets PGOOD\_RLS = 1, then the device will release PGOOD after verifying all the signals assigned to the PGOOD monitor block.

#### 12.4 Power down

#### 12.4.1 Turn-off events

Turn-off events may be requested by the processor (non-PMIC Fault related) or because of a critical failure of the PMIC (Hard Fault condition).

Non-PF5300 failure turn-off events:

- 1. Hardware turn off: PWRON pin is pulled low

- 2. Software turn off:

- When bit PMIC OFF bit is set to 1, the 500 µs shutdown timer is started and the SDWN I bit is set

- If the 500 µs timer expires, the state machine starts a turn off event.

- If the SDWN\_I bit is cleared before the 500 µs shutdown timer is expired, the shutdown request is cleared and the shutdown event is canceled. The PMIC\_OFF bit self-clears if the SDWN\_I flag is cleared.

- 3. XFAILB event

- 4. VIN goes below VIN UVDET F (no power down sequence)

For fault conditions resulting in a turn off, see <u>Table 8</u>. The device shuts down immediately (no power-down sequence) when Tj crosses the thermal shutdown threshold rising.

After a power-down sequence is started, the PWRON pin is masked until the sequence is finished and transition to the Off/Fail-safe states is completed.

#### 12.4.2 Power-down sequencing

A post power-down delay can be programmed on OTP with the OTP\_PD\_SEQ\_DLY[2:0] bits to delay entering the Off mode after completion of Power Down. This is useful when synchronizing power-down of multiple devices in the system, or to allow sufficient time for output capacitors to discharge.

Table 14. OTP\_PD\_SEQ\_DLY[2:0] configuration

| OTP_PD_SEQ_DLY[2:0] | Post power-down delay (ms) |

|---------------------|----------------------------|

| 0b000               | 0                          |

| 0b001               | 1                          |

| 0b010               | 10                         |

| 0b011               | 50                         |

| 0b100               | 100                        |

| 0b101               | 250                        |

| 0b110               | 500                        |

| 0b111               | 1000                       |

A delay determined by the OTP\_TURN\_OFF\_DELAY[5:0] bits can be executed before turning off SW1 and PGOOD assertion (low). The delay value is (OTP\_TURN\_OFF\_DELAY[5:0] \* OTP\_SEQ\_TBASE[1:0]).

# 12.5 Fault management

Three types of faults are monitored per regulator: UV, OV, and ILIM. Faults are monitored during the power-up sequence (after soft-start complete), IO Release, INIT, and System ON state (RUN and STANDBY) states.

OV/UV faults are debounced for a programmable filter time before they are detected as a fault condition.

ILIM faults are debounced for 40 µs before they can be detected as a fault condition.

PF5300\_PF5301\_PF5302

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

Document feedback

A global fault counter is provided in FAULT\_CNT [3:0] bits. The decimal value stored in FAULT\_CNT[3:0] represents the value of the fault counter. The FAULT\_CNT[3:0] can be programmed to increment for different types of faults, with the state machine taking action if the counter value exceeds a maximum value programmed using the OTP\_FAULT\_MAX\_CNT[2:0] bits.

If the FAULT MAX CNT[2:0] is changed during System ON states, the FAULT CNT[3:0] is reset to 0x00.

For each type of fault on SW1, an option is available to increment the FAULT CNT[3:0] value.

SW1\_ILIM\_BYPASS (initial value from OTP\_SW1\_ILIM\_BYPASS), SW1\_OV\_BYPASS (initial value from OTP\_SW1\_OV\_BYPASS), or SW1\_UV\_BYPASS (initial value from OTP\_SW1\_UV\_BYPASS) control whether the FAULT\_CNT[3:0] is incremented (0) or bypassed (1) for a current limit, an overvoltage, or an undervoltage fault, respectively.

Table 15. Fault counter limit configuration

| OTP bits OTP_FAULT_<br>MAX_CNT [2:0] | Functional bits FAULT_<br>MAX_CNT [2:0] | Value |

|--------------------------------------|-----------------------------------------|-------|

| 000                                  | 000                                     | 1     |

| 001                                  | 001                                     | 2     |

| 010                                  | 010                                     | 4     |

| 011                                  | 011                                     | 6     |

| 100                                  | 100                                     | 8     |

| 101                                  | 101                                     | 10    |

| 110                                  | 110                                     | 12    |

| 111                                  | 111                                     | 15    |

If the FAULT\_CNT[3:0] = FAULT\_MAX\_CNT[2:0], the PF5300 powers down into the Fail-safe state. See <u>Table 8</u> for details. For ASIL B and ASIL D devices, the FAULT\_CNT[3:0] bits can be decremented by doing a good watchdog refresh via an I<sup>2</sup>C command. The FAULT\_CNT[3:0] can also be cleared by setting the FLT\_CNT\_CLR bit.

The FAULT\_CNT[3:0] is reset to 0 when the state machine enters the LP\_off state. Once regulators are turned off after a FAULT\_CNT[3:0] is maxed out, the device moves to the LP\_off transition if FS\_BYPASS = 1.

**Note:** Fault count could be incremented more than once for the same type of fault (regx OV, UV) if the fault persists after the voltage setpoint changes. This could be either a voltage change in the same state or voltage change during a state change between RUN and STANDBY.

Even if a specific fault is bypassed, the corresponding interrupt bit is still set.

Table 16. Fault types and the corresponding PGOOD pin responses

| Safety<br>mechanism                                     | Monitored state                                                          | Error flag           | Fault<br>counter                   | WD_<br>ERROR_CNT   | PGOOD low assertion                  | FSM state<br>transition<br>from<br>INIT and<br>System ON | Comments                                                                                      |

|---------------------------------------------------------|--------------------------------------------------------------------------|----------------------|------------------------------------|--------------------|--------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| SW1 UV                                                  |                                                                          | VMON_UV_I            | +1 if SW1_<br>UV_BYPASS<br>bit = 0 | _                  | Yes, if OTP_<br>PGOOD_<br>SW1_UV = 1 | IO_Release                                               | Fault<br>shutdown<br>from power-<br>up sequence                                               |

| SW1 OV                                                  |                                                                          | VMON_OV_I            | +1 if SW1_<br>OV_BYPASS<br>bit = 0 | _                  | Yes, if OTP_<br>PGOOD_<br>SW1_OV = 1 | IO_Release                                               | Fault<br>shutdown<br>from power-<br>up sequence                                               |

| PGOOD<br>short to high                                  | Power Up<br>Sequence,<br>IO_Release,<br>INIT, and<br>System<br>ON states | PGOOD_<br>STUCK_AT_1 | +1                                 | _                  | _                                    | _                                                        | Fault shutdown from power- up sequence and IO_ Release; No transition from INIT and System ON |

| BG1 and BG2<br>Drift apart                              |                                                                          | BG_ERR_I             | _                                  | _                  | Yes, if OTP_<br>PGOOD_<br>BG = 1     | IO_Release                                               | Self-test fail                                                                                |

| Reg map<br>CRC error<br>(OTP and<br>functional<br>bits) |                                                                          | REGMAP_<br>CRC_I     | _                                  | _                  | Yes <sup>[1]</sup>                   | _                                                        | Fault<br>shutdown                                                                             |

| CLOCK stuck monitoring                                  |                                                                          | _                    | Cleared                            | _                  | Yes                                  | _                                                        | FSM reset/<br>shutdown                                                                        |

| Bad<br>watchdog<br>refresh                              | INIT, System<br>ON states                                                | _                    | _                                  | +2 if<br>WD_EN = 1 | _                                    | _                                                        | _                                                                                             |

Table 16. Fault types and the corresponding PGOOD pin responses...continued

| Safety<br>mechanism                              | Monitored state                                                      | Error flag              | Fault<br>counter   | WD_<br>ERROR_CNT | PGOOD low assertion                              | FSM state<br>transition<br>from<br>INIT and<br>System ON | Comments                                     |

|--------------------------------------------------|----------------------------------------------------------------------|-------------------------|--------------------|------------------|--------------------------------------------------|----------------------------------------------------------|----------------------------------------------|

| Watchdog<br>event                                | INIT, System<br>ON states                                            | _                       | +1 if<br>WD_EN = 1 | _                | Yes, if<br>WD_EN = 1                             | IO_Release                                               | Fault shutdown if FAULT_CNT ≥ FAULT_ MAX_CNT |

| VIN_OV<br>(OVLO<br>monitor)                      | IO_Release,<br>INIT, and<br>System<br>ON states                      | VIN_OVLO_I              | +1                 | _                | Yes, if VIN_<br>OVLO_<br>SDWN = 1 <sup>[2]</sup> | _                                                        | Power down                                   |

| ABIST OV/<br>UV error<br>(Startup and<br>AB_RUN) | Self-test<br>state, IO_<br>Release, INIT,<br>and System<br>ON states | AB_SW1_OV,<br>AB_SW1_UV | _                  | _                | _                                                | _                                                        | _                                            |

| VIN pin disconnection                            | INIT, IO_<br>Release,<br>System<br>ON states                         | _                       | Cleared            | _                | Yes (analog safety path)                         | _                                                        | FSM reset/<br>shutdown                       |

| OTP / TRIM corrupted                             | Self-test state                                                      | OTP_NOK<br>TRIM_NOK     | _                  | _                | Yes <sup>[2]</sup>                               | _                                                        | _                                            |

| BG1 and BG2<br>drift apart                       | Self-test state                                                      | BG_ERR_I                | _                  | _                | Yes <sup>[2]</sup>                               | _                                                        | _                                            |

| CLK drift error<br>20 MHz and<br>100 kHz         | Self-test state                                                      | OSC_ERR                 | _                  | _                | Yes <sup>[2]</sup>                               | _                                                        | _                                            |

| CLOCK<br>sync error                              | INIT, System<br>ON states                                            | FSYNC_<br>FLT_I         | _                  | _                | _                                                | _                                                        | Switch to internal CLK                       |

<sup>[1]</sup> Power-down/shutdown event. PGOOD doesn't get asserted low immediately upon fault. PGOOD assertion will be handled by the state machine and the sequencer.

# 12.6 Interrupt management

The processor is notified of any interrupt through various interrupt registers. There is no explicit INTB pin in the PF5300.

The interrupt registers are composed of two types of bits to help manage all the interrupt requests in the PF5300:

- The interrupt latch XXXX\_I: This bit is set when the corresponding interrupt event occurs. It can be read at any time, and is cleared by writing a 1 to the bit.

- The sense bit XXXX\_S: If available, the sense bit provides the actual status of the signal triggering the interrupt.

<sup>[2]</sup> Startup fault. PGOOD is asserted by default as device doesn't progress to Power-up state. Not valid during Debug mode.

**Table 17. Interrupt Registers**

| Register name  | BIT7                     | BIT6                     | BIT5          | BIT4             | BIT3            | BIT2            | BIT1            | BIT0            |

|----------------|--------------------------|--------------------------|---------------|------------------|-----------------|-----------------|-----------------|-----------------|

| INT<br>STATUS1 | SDWN_I                   | BG_ERR_I                 | CRC_I         | SW1_DVS_<br>DONE | SW1_ILIM_I      | VMON_<br>UV_I   | VMON_<br>OV_I   | VIN_<br>OVLO_I  |

| INT_<br>SENSE1 | _                        | BG_ERR_S                 | _             | _                | SW1_<br>ILIM_S  | VMON_<br>UV_S   | VMON_<br>OV_S   | VIN_<br>OVLO_S  |

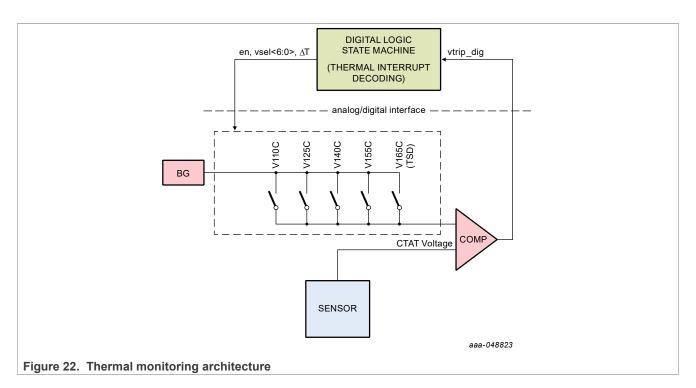

| INT<br>STATUS2 | PGOOD_<br>STUCK_<br>AT_0 | PGOOD_<br>STUCK_<br>AT_1 | DVS_<br>ERR_I | FSYNC_I          | THERM_<br>155_I | THERM_<br>140_I | THERM_<br>125_I | THERM_<br>110_I |

| INT_<br>SENSE2 | _                        | PGOOD_S                  | _             | FSYNC_S          | THERM_<br>155_S | THERM_<br>140_S | THERM_<br>125_S | THERM_<br>110_S |

# 12.7 I/O interface pins

The PF5300 is fully programmable via the I<sup>2</sup>C interface. Additional communication between the processor, PF5300, and other companion PMICs is provided by direct logic interfacing, including PGOOD, among other pins.

All parameters are specified at Ta = -40 °C to 125 °C, PVIN =  $V_{IN}$  = 3.3 V, PWRON = 1.8 V, no load on regulator, Fsw = 2.2 MHz, typical external component values, unless otherwise noted. Typical values are specified at 25 °C, unless otherwise noted.

Table 18. I/O Electrical Characteristics

| Symbol                             | Parameter                  | Min | Тур | Max | Unit |

|------------------------------------|----------------------------|-----|-----|-----|------|

| PWRON_V <sub>IL</sub>              | PWRON low input voltage    | _   | _   | 0.4 | V    |

| PWRON_V <sub>IH</sub>              | PWRON high input voltage   | 1.4 | _   | 5.5 | V    |

| STANDBY/SYNCIN_<br>V <sub>IL</sub> | STANDBY low input voltage  | _   | _   | 0.4 | V    |

| STANDBY/SYNCIN<br>_V <sub>IH</sub> | STANDBY high input voltage | 1.4 | _   | 5.5 | V    |

PF5300\_PF5301\_PF5302

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

Document feedback

Table 18. I/O Electrical Characteristics...continued

| Symbol                                                                         | Parameter                                      | Min                   | Тур | Max | Unit |

|--------------------------------------------------------------------------------|------------------------------------------------|-----------------------|-----|-----|------|

| PGOOD_V <sub>OL</sub>                                                          | PGOOD low output voltage -2.0 mA load current  | 0                     | _   | 0.4 | V    |

| XFAILB_V <sub>IL</sub>                                                         | XFAILB low input voltage                       | 0                     | _   | 0.4 | V    |

| XFAILB_V <sub>IH</sub>                                                         | XFAILB high input voltage                      | 1.4                   | _   | 5.5 | V    |

| XFAILB_V <sub>OH</sub> XFAILB high output voltage Pulled-up to V <sub>IN</sub> |                                                | V <sub>IN</sub> - 0.5 | _   | _   | V    |

| XFAILB_V <sub>OL</sub>                                                         | XFAILB low output voltage -2.0 mA load current | 0                     | _   | 0.4 | V    |

| SCL_V <sub>IL</sub>                                                            | SCL low input voltage                          | 0                     | _   | 0.4 | V    |

| SCL_V <sub>IH</sub>                                                            | SCL high input voltage                         | 1.4                   | _   | 5.5 | V    |

| SDA_V <sub>IL</sub>                                                            | SDA low input voltage                          | 0                     | _   | 0.4 | V    |

| SDA_V <sub>IH</sub>                                                            | SDA high input voltage                         | 1.4                   | _   | 5.5 | V    |

| SDA_V <sub>OH</sub>                                                            | SDA high output voltage                        | 1.4                   | _   | 5.5 | V    |

| SDA_V <sub>OL</sub>                                                            | SDA low output voltage -20 mA load current     | 0                     | _   | 0.4 | V    |

#### 12.7.1 PWRON

PWRON is an input signal to the IC that acts as a power-up event signal in the PF5300.

The PWRON pin operates in Level-sensitive mode. In this mode, the device is in one of the off modes when the PWRON pin is pulled low. Pulling the PWRON pin high is a necessary condition to generate a power-on event. The PWRON pin has a 10 µs debounce timer on the falling edge.

PWRON may be pulled up to  $V_{IN}$  with an external 10 k $\Omega$  resistor if the device is intended to come up automatically with application of  $V_{IN}$ .

#### 12.7.2 STANDBY/SYNCIN

The STANDBY/SYNCIN pin has dual functions. It is used either as the clock synchronization input (SYNCIN) or STANDBY state selection (STANDBY). The STANDBY function can be enabled when the SYNC function is disabled (OTP\_SYNCIN\_EN = 0). If not used as SYNC, this pin can be selected in OTP to be used as the STANDBY input (OTP\_SYNCIN\_EN = 1).

Table 19. STANDBY/Syncin Configuration

| OTP_SYNCIN_EN | Description                              |

|---------------|------------------------------------------|

| 0             | STANDBY/SYNCIN pin configured as STANDBY |

| 1             | STANDBY/SYNCIN pin configured as Syncin  |

STANDBY can be configured as active high or active low using the STANDBYINV bit, with default value set by the OTP\_STANDBYINV bit.

Table 20. STANDBY pin polarity control

| STANDBY (pin) | STANDBYINV (I <sup>2</sup> C bit) | STANDBY control      |

|---------------|-----------------------------------|----------------------|

| 0             | 0                                 | Not in STANDBY state |

| 0             | 1                                 | In STANDBY state     |

| 1             | 0                                 | In STANDBY state     |

| 1             | 1                                 | Not in STANDBY state |

#### 12.7.3 PGOOD

PGOOD is an open-drain output used as a PGOOD indicator pin. PGOOD can be assigned a slot in the power-up sequence (to behave like a GPO), or it can be released after SW1 is on and in regulation. PGOOD should be pulled up to 1.8 V, 3.3 V, or  $V_{\text{IN}}$  with a pullup resistor.

The PGOOD pin is driven low or asserted when the PF5300 is out of the RUN state and enters the Fail-safe state. The PGOOD pin is asserted low in the Fail-safe, ULP\_Off, and LP\_Off states.

When  $V_{IN}$  is applied, the PGOOD pin is driven low as soon as the logic is able to control, to ensure no floating condition is present on the load being controlled by this pin. PGOOD is also asserted low through an analog path if PVIN is present, but VIN is not.

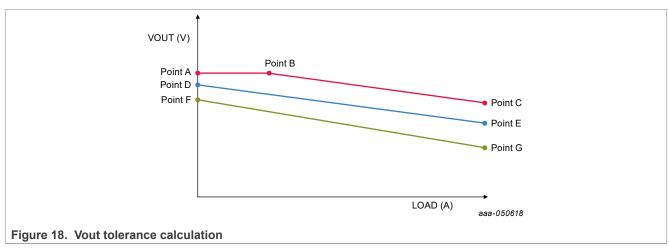

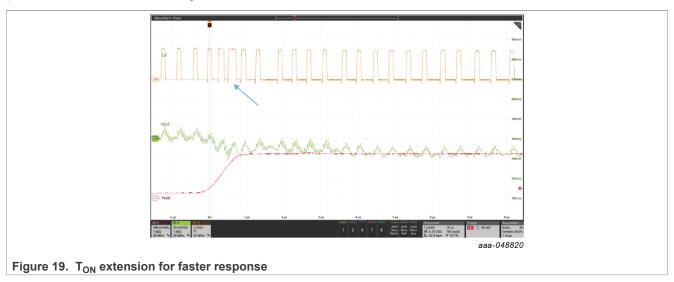

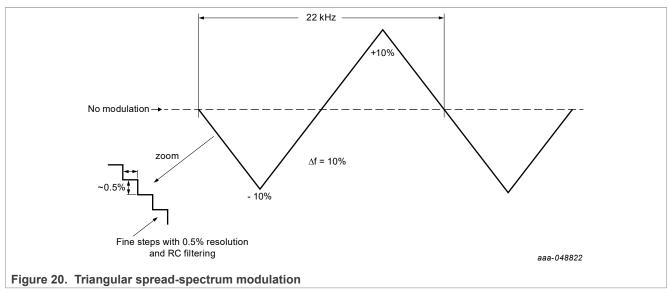

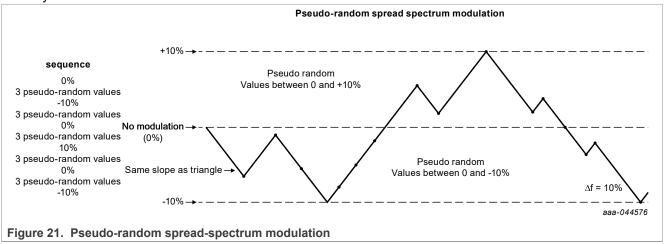

When OTP\_PGOOD\_SW1\_OV = 1, PGOOD is asserted low if an overvoltage is detected by the voltage monitor monitoring SW1. When OTP\_PGOOD\_SW1\_UV = 1, PGOOD is asserted low if an undervoltage is detected by the voltage monitor monitoring SW1. See <u>Section 13.2</u> for thresholds and debounce values. The PGOOD pin is asserted low for at least 1 ms when being asserted low for a fault. For example, even if the fault is cleared immediately upon PGOOD assertion (low), PGOOD remains asserted low for 1 ms from there on.