# **Freescale Semiconductor**

HCL TECHNOLOGIES HCL

# Multi Service Access Line Card Application Note

Preliminary Draft

Rev 1.2

**HCLMSP-AN/D**

© Freescale Semiconductor, Inc., 2004. All rights reserved.

**MSA Application Note**

# Freescale Semiconductor, Inc.

# **Table of Contents**

| ,      | Markfronton I Batama                             |     |

|--------|--------------------------------------------------|-----|

| 1      | Modification History                             |     |

| 2      | Overview Definitions, Acronyms and Abbreviations |     |

| 3<br>4 | Related Documents                                |     |

| 5      | Application Mapping                              |     |

| 6      | Network processor architecture                   |     |

| -      | 6.1 Data Paths                                   |     |

| 7      | Network processor components                     |     |

| •      | 7.1 XP                                           |     |

|        | 7.2 OAM Processing                               |     |

|        | 7.3 Statistics Management                        |     |

|        | 7.4 TDM RX (CP 0 and CP 4)                       |     |

|        | 7.5 IMA (CP 1 and CP 5)                          |     |

|        | 7.6 TDM Tx (CP 2 and CP 6)                       |     |

|        | 7.7 TDM Recirculation (CP3)                      |     |

|        | 7.8 IPv4 (CP 7)                                  |     |

|        | 7.9 Segmentation (CP 8)                          |     |

|        | 7.10 Reassembly (CP 9)                           |     |

|        | 7.11 IP QoS Classifier (CP 10)                   | 56  |

|        | 7.12 FR processing – switching (CP11)            | 63  |

|        | 7.13 MPLS (CP12)                                 |     |

|        | 7.14 MLPPP (CP 13)                               |     |

|        | 7.15 AAL1-Tx (CP 14)                             |     |

|        | 7.16 AAL-1 RX (CP 15)                            |     |

|        | 7.17 Fabric Port                                 |     |

|        | 7.18 Table Lookup Unit                           |     |

|        | 7.19 Buffer Management Unit                      |     |

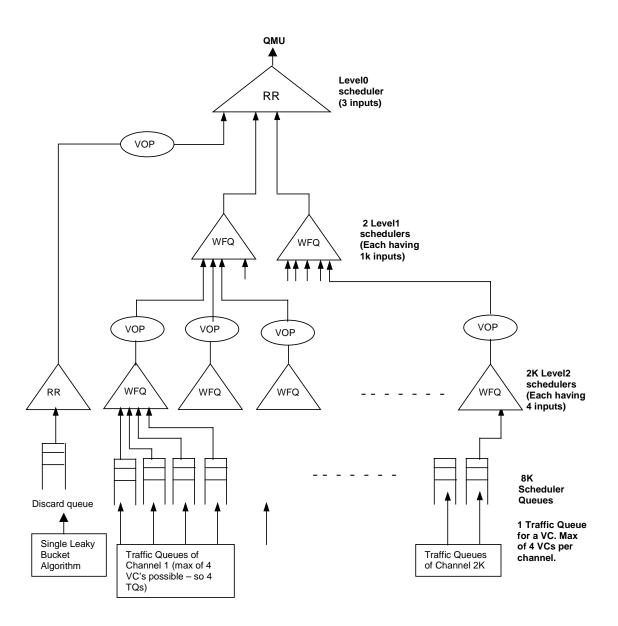

|        | 7.20 Queue Management Unit                       |     |

|        | 7.21 Q-3 configurations for CPs, XP and FP       |     |

| 8      | HOST PROCESSOR ARCHITECTURE                      |     |

| 9      | HOST PACKET I/O                                  |     |

| J      | 9.1 Resources                                    |     |

|        | 9.2 Packet Reception.                            |     |

|        | 9.3 Packet Transmission                          |     |

| 10     |                                                  |     |

|        | 10.1 Application Control                         |     |

|        | 10.2 Table Maintenance and Display               |     |

|        | 10.3 Link Configuration and Status               |     |

|        | 10.4 Channel configuration and Status            |     |

|        | 10.5 IMA Configuration and Status                |     |

|        | 10.6 PPP Configuration and Status                | 107 |

|        | 10.7 FR Configuration and Status                 | 107 |

|        | 10.8 Statistics                                  |     |

| 11     |                                                  |     |

|        | 11.1 PPP                                         |     |

|        | 11.2 ML-PPP                                      |     |

|        | 11.3 FR                                          |     |

|        | 11.4 IMA                                         |     |

|        | 11.5 ATM                                         |     |

| 12     |                                                  |     |

|        | 12.1 ML-PPP                                      | 111 |

# **MSA Application Note**

| oft Queues11                                       |

|----------------------------------------------------|

| ST API REFERENCE114                                |

| ble API114                                         |

| nk, Channel, and IMA API128                        |

| PP API131                                          |

| TM API135                                          |

| R API135                                           |

| ontrol API                                         |

| P Port API                                         |

| ) API140                                           |

| EGMENTATION141                                     |

| REASSEMBLY14 <sup>2</sup>                          |

| MPLS142                                            |

| DM RECIRCULATION143                                |

| R SWITCHING143                                     |

| endix C – Optimizations done in the application145 |

# 1 Modification History

**MSA Application Note**

|     | <u>-</u>  |                  |                     |                                                                                                                                    |  |  |  |  |

|-----|-----------|------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Rev | Date      | Author           | Department          | Changes                                                                                                                            |  |  |  |  |

| 1.0 | 06-Feb-03 | HCL Technologies | Networking          | Draft version.                                                                                                                     |  |  |  |  |

| 1.1 | 14-Feb-03 | HCL Technologies | Networking          | Additional information is<br>added on Q-3,<br>Performance<br>calculations,<br>IMEM/DMEM estimates,<br>ATM TM, IP QoS, Host<br>APIs |  |  |  |  |

| 1.2 | 14-Mar-03 | J.Bednarek       | Motorola,<br>C-Port | Changes for draft for SNDF CD                                                                                                      |  |  |  |  |

# 2 Overview

This document describers the design of a Multi Service Access (MSA) line card. The intended audiences of this document are system architects, hardware designers, software designers, testers and programmers of the line card based on the C-Port network processor family.

The reader of this document is expected to have a fair understanding of the C-3e NP architecture and the associated co-processor such as Q-3 (Traffic Management Co-processor) with the basic understanding of C-Port Family of TDM Adapters (or Twister) (Mt-21) used in the design of the MSA line card.

MSA line card application provides multiple services on different ports. It can be connected to two Twister Mt-21 chips. The twister Mt-21 chip can have 32 T1/E1 interfaces supporting upto 1K channels.(note, Mt-21 can support even higher channels, ie 2048, but in this example, we are assuming 1000 channels).

#### Feature Overview and Standards Support

This application supports the following features:

- 64 T1/E1 interfaces supporting 2K channels

- PPP / FR header processing and reassembly

- MLPPP segmentation and reassembly

- AAL1/5 segmentation and reassembly

- ATM Cell switching

- FR switching

- IPv4 Unicast Routing on all interfaces (PPP/ATM/FR)

- Multi-Protocol Label Switching (MPLS) on all interfaces

- Ingress / Egress packet processing for MPLS

- IP IntServ and DiffServ

- ATM Traffic Management 4.1

- MPLS QoS

- IMA

HCLTECHNOLOGIES HCL

**MSA Application Note**

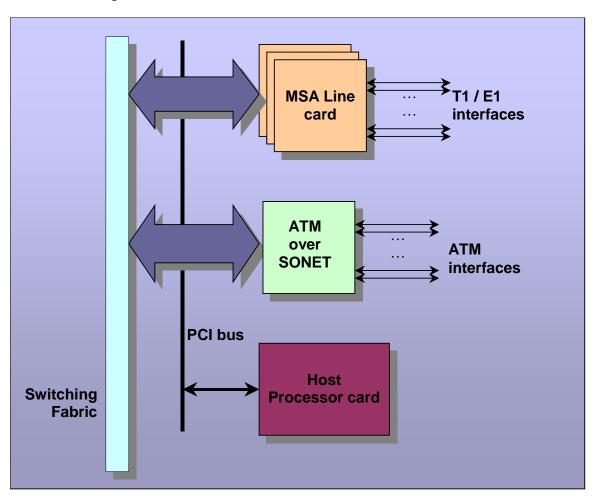

MSA line card is intended to work in a stack of MSA cards connected on the switching fabric for communication with the other MSA cards as well as line cards that terminate ATMs. The host module manages and maintains the statistics for the entire system. The communication of the host with the line cards is through the PCI interface. Figure 1 helps in understanding the intended use of the MSA line card.

Figure 1: MSA card within the access platform

**MSA Application Note**

# 3 Definitions, Acronyms and Abbreviations

| Abbreviation | Description                                |

|--------------|--------------------------------------------|

| AAL          | ATM Adaptation Layer                       |

| AAL-1        | ATM Adaptation Layer 1                     |

| ABR          | Available Bit Rate                         |

| AF           | Assured Forwarding                         |

| ARP          | Address Resolution Protocol                |

| ATM          | Asynchronous Transfer Mode                 |

| ATM TM       | ATM Traffic Management                     |

| BE           | Best effort                                |

| BOM          | Beginning of Message.                      |

| CBR          | Constant Bit Rate                          |

| CID          | Channel ID                                 |

| CIDR         | Classless Inter Domain Routing             |

| CPI          | Common Part Indicator.                     |

| CPRC         | Channel Processor RISC core.               |

| CRC          | Cyclic Redundancy Check.                   |

| DLCI         | Data Link Connection Identifier            |

| DWRR         | Dynamic Weighted Round Robin               |

| EF           | Expedited Forwarding                       |

| EOM          | End of Message.                            |

| FEC          | Forwarding Equivalence class               |

| FR           | Frame Relay                                |

| HDLC         | High Level Data Link Control               |

| HEC          | Header Error Control.                      |

| HTK          | Hash Trie Key.                             |

| ICMP         | Internet Control Message Protocol          |

| ICP          | IMA Control Protocol.                      |

| IP           | Internet Protocol                          |

| LCP          | Link Control Protocol                      |

| LLC          | Logical Link Control                       |

| LMI          | Local Management Interface                 |

| LPM          | Longest Prefix Match.                      |

| LSP          | Label switched path                        |

| MIB          | Management Information Block               |

| ML/PPP       | Multi-Link PPP                             |

| MPLS         | Multi-Protocol Label Switching             |

| MTU          | Maximum transmission Unit                  |

| NCP          | Network Control Protocol                   |

| NLPID        | Network Layer Protocol ID                  |

| OAM          | Operation, Administration and Maintenance. |

| PDU          | Protocol Data Unit.                        |

| PHB          | Per Hop Behavior                           |

| PPP          | Point to Point Protocol                    |

| QoS          | Quality Of Service                         |

#### **MSA Application Note**

| RARP Reverse Address Resolution Protocol |

|------------------------------------------|

|------------------------------------------|

| Abbreviation | Description                                        |  |  |

|--------------|----------------------------------------------------|--|--|

| RED          | Random Early Discard                               |  |  |

| RM           | Resource Management.                               |  |  |

| RR           | Round Robin                                        |  |  |

| SDU          | Service Data Unit.                                 |  |  |

| SNAP         | Subnetwork Access Protocol.                        |  |  |

| TCP          | Transport Control Protocol                         |  |  |

| TDM          | Time Division Multiplexing                         |  |  |

| TLU          | Table Lookup Unit.                                 |  |  |

| TMC          | Traffic Management Co-Processor                    |  |  |

| TOS          | Type of Service                                    |  |  |

| TTL          | Time To Live                                       |  |  |

| UUI          | User-to-User Interface.                            |  |  |

| VC           | ATM Virtual Connection                             |  |  |

| VOP          | Virtual Output Port                                |  |  |

| VP           | ATM Virtual Path                                   |  |  |

| VPCI         | Virtual Path Identifier/Virtual Channel Identifier |  |  |

| WFQ          | Weighted Fair queueing                             |  |  |

|              |                                                    |  |  |

# 4 Related Documents

This section lists down the various documents used as reference while developing this application notes.

- MSA Line card software requirement specifications from C-Port.

- Guide to C-Ware WNI Applications, CST2.2

- ATM Cell Switch Application Guide, CST 2.1.1

- RFC 791, Internet Protocol

- RFC 1332, The PPP Internet Protocol Control Protocol (IPCP)

- RFC 1471, The Definitions of Managed Objects for the Link Control Protocol of the Point-to-Point Protocol

- RFC 1473, The Definitions of Managed Objects for the IP Network Control Protocol of the Point-to-Point Protocol

- RFC 1661, The Point to Point Protocol (PPP)

- RFC 1812, Requirements for IP Version 4 Routers

- RFC 1990, The PPP Multilink Protocol (MP)

- RFC 2427, Multiprotocol Interconnect over Frame Relay

- RFC 2474, Definition of the Differentiated Services Field (DS Field) in the IPv4

- RFC 2475, An Architecture for Differentiated Services

- RFC 2597, Assured Forwarding PHB Group

#### **MSA Application Note**

- RFC 2598, An Expedited Forwarding PHB

- RFC 2702, Requirements for Traffic Engineering Over MPLS

- RFC 2684, Multi Protocol Encapsulation over ATM Adaptation Layer 5

- RFC 2697, A Single Rate Three Color Marker

- ITU I.361, B-ISDN ATM Layer Specification

- ITU I.363.1, B-ISDN ATM Adaptation Layer Specification: Type 1 AAL

- ITU I.363.5, B-ISDN ATM Adaptation Layer Specification: Type 5 AAL

- ITU I.610 B-ISDN Operation and Maintenance Principles and Functions

- ATM Forum, Inverse Multiplexing for ATM (IMA) Specification Version 1.1

- Frame Relay to ATM to 10/100 Ethernet Switch Router Application Guide, CST2.1

- C-ware Q-5 TMC API User guide Rev 00

- DiffDocQ-512003.doc Functionality Comparison Between "Old" Q-5 TMC Design and Projected Q-5 TMC FPGA

- RFC3034 –Use of Label Switching on Frame Relay Networks specification

- RFC 2702 Requirements for traffic engineering over MPLS

- RFC3270 Multi-protocol label switching support of differentiated services

- RFC 3031 Multi-protocol label switching architecture

- RFC 3032 MPLS label stack encoding

- Draft-ietf-mpls-ttl-04.txt Time to Live Processing in MPLS networks.

- RFC 3035 MPLS using LDP and ATM VC switching

# 5 Application Mapping

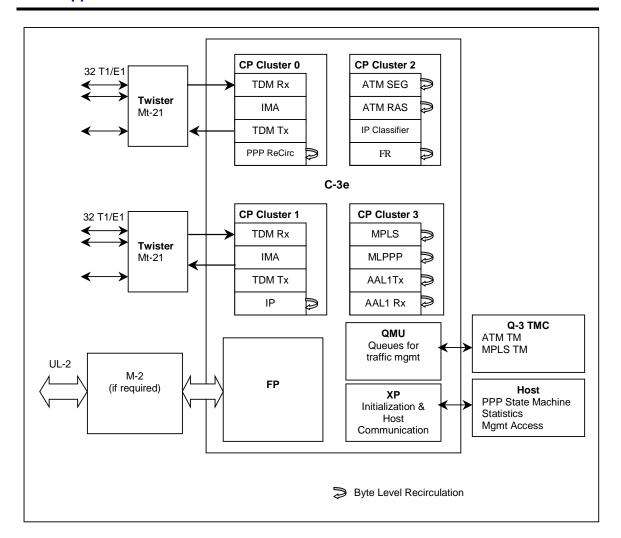

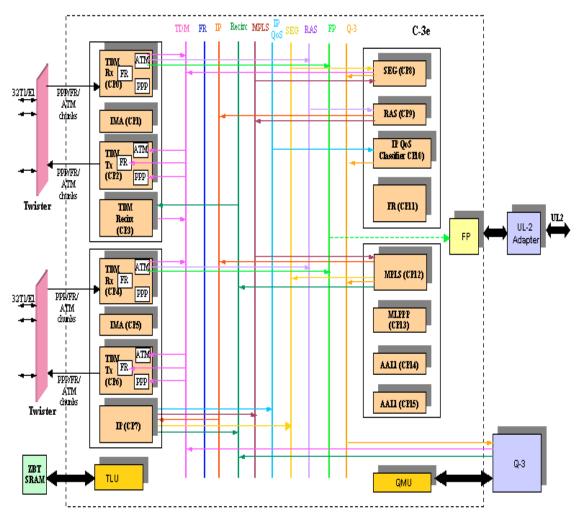

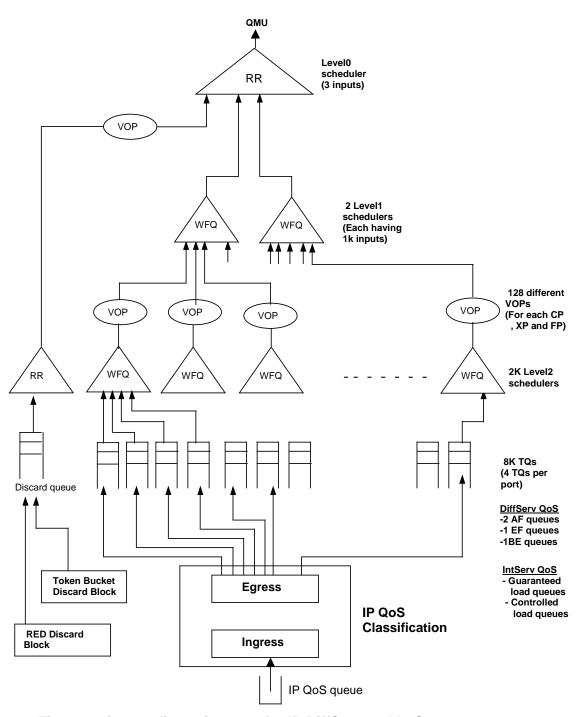

This application is comprised of many software components, each of which is divided into smaller components. The functional partitioning of the software is depicted in figure 2 with the clustering and re-circulation information. The partitioning is designed to handle 1024 channels per cluster. C-3e NP is chosen for implementing the MSA line card as the processing power of the NP and the T1/E1 line interfaces match and also Q-3 is used for managing the traffic management for IP, ATM and MPLS.

#### **MSA Application Note**

Figure 2: MSA line card functional mapping on C-3e NP

# 6 Network processor architecture

The MSA application consists of many software components. One component executes on the host and the other components execute on the various CPs within the C-3e. Each of the NP software components provides a subset of the features of the application. Mapping between software components and CPs was shown in the figure 2. The data paths between these components can be conceptualized as a group of busses. In this context, a bus is the combined use of queues and buffer memory to forward data between two components. The queue number is analogous to the address on the bus. Each of the buses implies a different buffer and descriptor format (for TDM, IP, MPLS, and so on). The traffic originating from TDM channels will be HDLC or ATM or Transparent Chunk based on the channel configuration. HDLC traffic will further be identified as FR traffic or PPP traffic.

A buffer and a buffer descriptor can specify the interface to a component. Table below lists each of the components and describes their interface. A component may have

#### **MSA Application Note**

multiple interfaces and therefore multiple entries in the table. Unless specified otherwise in the table, the port field indicates the output port and the length field indicates the number of bytes in the buffer. The various buffer formats are described in <a href="mailto:section 7.19">section 7.19</a> and the buffer descriptor formats are described in appropriate sections.

| Component    | Buffer Format                                      | Descriptor format | Comments                                                                                 |  |

|--------------|----------------------------------------------------|-------------------|------------------------------------------------------------------------------------------|--|

| TDM Rx       | BT_ATM, BT_MPLS_FR, BT_MPLS_PPP, BT_MPLS_ATM       | ATM               | Only header field required                                                               |  |

|              | BT_MPLS                                            | MPLS              |                                                                                          |  |

|              | BT_HDLC                                            | N/A               |                                                                                          |  |

|              | BT_TDM_TRANSPARENT                                 | Transparent Chunk |                                                                                          |  |

| TDM Tx       | BT_ATM                                             | ATM               | Only header field required                                                               |  |

|              | BT_HDLC                                            | N/A               |                                                                                          |  |

| IMA Tx       | BT_ATM                                             | ATM               | Port indicates outport which maps to IMA group; only header field required               |  |

| IMA Rx       | BT_IMA_CP,<br>BT_IMA_FILLER                        | OAM               | Port indicates input port                                                                |  |

|              | BT_ATM                                             | ATM               | Port indicates input port                                                                |  |

| ML PPP       | BT_HDLC,<br>BT_PPP,<br>BT_MLPPP                    | ML-PPP            | Port indicates input port; reassembly will be performed                                  |  |

|              | BT_IPV4,<br>BT_CONTEXT_STATE,<br>BT_NCP_xxx        | TDM               | Only mcClass field required; segmentation will be performed                              |  |

| IP           | BT_IPV4                                            | N/A               | Port indicates input port; IP forwarding will be performed                               |  |

|              | BT_HDLC, BT_PPP                                    | N/A               | Port indicates input port; PPP encapsulation will be removed and IP forwarding performed |  |

| FR           | BT_MPLS_FR, BT_MPLS_PPP, BT_MPLS_ATM               | MPLS              |                                                                                          |  |

|              | BT_FR                                              | FR                |                                                                                          |  |

| MPLS         | BT_MPLS_PPP, BT_MPLS_FR, BT_MPLS_IPV4, BT_MPLS_ATM | MPLS              | Buffer type identifies the egress port interface type.                                   |  |

| Segmentation | BT_IPV4                                            | Seg               | EgressQueue field is required.                                                           |  |

| Reassembly   | BT_ATM                                             | ATM               | Port indicates input port;<br>AAL-5 reassembly will be<br>performed                      |  |

| IP QoS       | BT_IPV4                                            | TDM               |                                                                                          |  |

| AAL-1 Rx     | BT_TDM_TRANSPRENT<br>BT_ATM                        | TDM<br>ATM        |                                                                                          |  |

#### **MSA Application Note**

| AAL-1 Tx | BT_TDM_TRANSPRENT | TDM |                                                           |

|----------|-------------------|-----|-----------------------------------------------------------|

|          | BT_ATM            | ATM |                                                           |

| UL-2     | BT_ATM            | ATM |                                                           |

| Host     | BT_ATM            | ATM | Port indicates the input port; only header field required |

|          | All others        | N/A | Port indicates the input port                             |

#### 6.1 Data Paths

This section explains about various data paths originating from T1/E1 interfaces, flowing through other components in the NP and going out through T1/E1 interfaces. Two Twisters (Mt-21) are supported in this application.

#### 6.1.1 Data Paths for FR frames

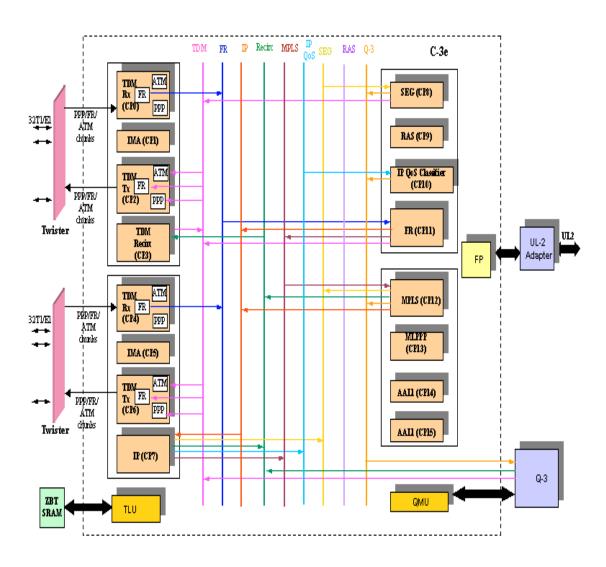

This section describes the conceptualized data flows for FR frame received in TDM RX. The FR chunks will be reassembled as FR frame in TDM RX, recirculated in other component CPs and finally transmitted as FR / PPP / AAL5 chunks via TDM Tx. The detailed flow shown in figure 3 is described as follows.

- FR frame is received as HDLC chunks in TDM RX, gets reassembled and identified as FR frame based on the channel configuration. Then it will be enqueued to FR queue for further FR processing.

- FR component performs the DLCI lookup. Based on lookup response, it will enqueue the frame into IP queue or MPLS queue. For FR switching, it will modify the FR header (with new DLCI value) and enqueue into appropriate TDM Tx queue.

- IP component dequeues the FR frame from its queue, removes the FR header and enqueues the IP packet into destination queue (TDM recirculation queue or ATM Segmentation queue or MPLS queue or IP QoS queue determined by IP lookup and port lookup result.

- MPLS removes the FR header (if it exists) from the frame, performs the label processing and then enqueues the packet to destination queue (TDM recirculation queue or ATM Segmentation queue or IP queue or Q-3 traffic queue determined by MPLS lookup result.

- ATM segmentation component will segment the IP packet into AAL5 cells, inserts

the ATM header and enqueues these cells to appropriate TDM Tx queue or to Q3 traffic queue.

- TDM recirculation component encapsulates the packet into FR or PPP frame, enqueues it to TDM Tx for final transmission over TDM channel.

- TDM Tx dequeues the HDLC frame(FR frame or PPP frame, No differentiation is made between PPP and FR frame) or ATM cells from its queue. It transmits TDM chunks of size 64 bytes. For ATM, each cell will fit into a TDM chunk. For FR or PPP, it segments the frame into TDM chunks.

- If QoS treatment is needed, packets will be enqueued to Q-3 traffic queue from IP QoS classifier or ATM Segmentation or MPLS components for applying various QoS parameters. Q-3 TMC provides marking/dropping, policing and traffic shaping for the packet based on configured traffic parameters. Q-3 TMC

HCLTECHNOLOGIES HCL

#### **MSA Application Note**

will enqueue the conformant packets into QMU queue. Non-conformant packets will either be discarded or marked.

Figure 3. Data paths for FR frames

HCL TECHNOLOGIES HCL

**MSA Application Note**

#### 6.1.2 Data Paths for PPP frames

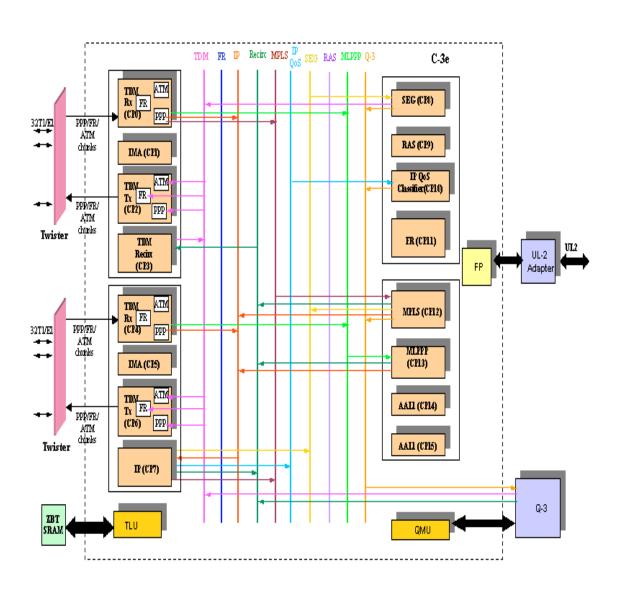

This section describes the data flow for PPP frames received in TDM RX. The PPP chunks will be reassembled as PPP frame in TDM RX, recirculated in other component CPs and finally transmitted as FR / PPP / AAL5 chunks via TDM Tx. The detailed flow shown in figure 4 is described as follows.

- PPP frame is received as HDLC chunks in TDM RX, gets reassembled and identified as PPP frame based on the channel configuration. Then it will be enqueued to IP queue or MLPPP queue or MPLS queue component based on PPP protocol field in frame.

- IP component dequeues the PPP frame from its queue, removes the PPP header and enqueues the IP packet into destination queue (TDM recirc queue or ATM Segmentation queue or MPLS queue or IP QoS queue determined by IP lookup and port lookup result.

- MPLS removes the PPP header (if it exists) from frame, performs the label processing and then enqueues the packet to destination queue (TDM recirc queue or ATM Segmentation queue or IP queue or Q-3 traffic queue (if QoS is needed)) determined by MPLS lookup result.

- MLPPP component dequeues from its queue, removes MLPPP encapsulation from the frame, and reassembles MLPPP fragments and enqueues the reassembled fragment to IP queue.

- ATM segmentation component will segment the IP packet into AAL5 cells, inserts

the ATM header and enqueues these cells to appropriate TDM Tx queue or to Q3 traffic queue.

- TDM recirculation component encapsulates the packet into FR or PPP frame, enqueues it to TDM Tx for final transmission over TDM channel.

- TDM Tx dequeues the FR frame or PPP frame or AAL5 cells from its queue. It transmits TDM chunks of size 64 bytes. For ATM, each cell will fit into a TDM chunk. For FR or PPP, it segments the frame into TDM chunks.

If QoS treatment is needed, packets will be enqueued to Q-3 traffic queue from IP QoS classifier or ATM Segmentation or MPLS components for applying various QoS parameters. Q-3 TMC provides marking/dropping, policing and traffic shaping for the packet based on configured traffic parameters. Q-3 TMC will en-queue the conformant packets into QMU queue. Non-conformant packets will either be discarded or marked.

**MSA Application Note**

Figure 4. Data paths for PPP frames

**MSA Application Note**

#### 6.1.3 Flows for ATM cells

This section describes the data flow for ATM cells received in TDM RX. The ATM cells will be recirculated in other component CPs and finally transmitted as FR / PPP / AAL5 chunks via TDM Tx. The detailed flow shown in figure 5 is described as follows.

- ATM cells are received as chunks in TDM RX. These will be enqueued to TDM Tx queue (ATM switching) or FP queue.

- AAL5 cells are enqueued into reassembly queue by TDM RX that performs the VC table lookup to send the new VPI/VCI values into the reassembly queue.

- ATM reassembly component will de-queue and reassembles the cells into AAL5 PDU. It will then be enqueued into IP queue or MPLS queue,

- IP component dequeues the reassembled AAL5 PDU from its queue, enqueues it

into destination queue (TDM recirc queue or ATM Segmentation queue or MPLS

queue or IP QoS queue (if QoS is needed)) determined by IP lookup and port

lookup result.

- MPLS performs the label processing and then enqueues the packet to destination queue (TDM recirc queue or ATM Segmentation queue or IP queue or Q-3 traffic queue (if QoS is needed)) determined by MPLS result entry.

- ATM segmentation component will segment the IP packet into AAL5 cells, modifies the AAL5 header (with new VPI/VCI) and enqueues these cells to TDM Tx queue or to Q-3 traffic queue (if QoS is needed).

- TDM recirc component encapsulates the packet into FR or PPP frame, enqueues it to TDM Tx for final transmission over TDM channel.

- TDM Tx dequeues the FR frame or PPP frame or AAL5 cells from its queue. It transmits TDM chunks of 64 bytes. For ATM, each cell will fit into a TDM chunk. For FR or PPP, it segments the frame into TDM chunks.

- If QoS is needed, packets will be enqueued to Q-3 traffic queue from IP QoS classifier or ATM Segmentation or MPLS components for applying various QoS parameters. Q-3 TMC provides marking/dropping, policing and traffic shaping for the packet based on configured traffic parameters. Q-3 TMC will en-queue the conformant packets into QMU queue. Non-conformant packets will either be discarded or marked.

Figure 5. Data paths for ATM Cells

# 7 Network processor components

This section describes each of the features of the applications in detail and explains how each component or resource within the NP is used to provide the applications' features. The Executive Processor RISC Core (XPRC) is a general-purpose processor that provides management, control, and exception processing functions. The XP controls NP boot up, configuration, and initialization of all system components.

#### **MSA Application Note**

The Channel Processors (CPs) are the components most closely associated with processing data from a physical interface. There are 16 CPs organized as four clusters, each of which contains four CPs. Each cluster performs several functions that aid in the processing of data packets.

#### 7.1 XP

The XP program is partitioned into distinct 'initialization' and 'main' executables. After loading and running the initialization executable, the main executable is loaded and overlayed on the initialization executable, reducing the IMEM used at run-time. This partitioning scheme uses the available IMEM resource to its fullest.

#### 7.1.1 Initialization Program

The initialization executable performs service initialization, configures system resources, and loads the CPs. In particular, the initialization executable does the following:

- Allocates buffer pools.

- Allocates and configures gueues.

- Configures the fabric port.

- Configures the PHY interfaces.

- Loads the CPs.

- Defers to the main XP executable program.

Arrays of parameter values are used to initialize the buffer pools and queues. The arrays are made up of macros defined in the top-level configuration file (config.h).

# 7.1.2 Main Program

The main executable completes any necessary initialization and starts the CPs before entering the main loop. In particular, the main executable does the following:

- Prints the application banner including version number

- Restores the offline table data. Offline table data is used to initialize the TLU tables without host intervention for simulation purposes.

- Initializes the CRC correction table

- Starts the CPs and enables the fabric port.

- Starts some of the SDPs

- Initializes the OAM processing component.

- Initializes the host communication component

- Enters the main loop

The main loop within the XP performs processing for OAM handling described in section "OAM processing" and host communication for updating statistics.

# 7.2 OAM Processing

OAM cells received by the TDM CPs are forwarded to the XP for processing. OAM support in the application includes the following:

Forward Performance Monitoring – Receive Monitoring

#### **MSA Application Note**

- Blocks of user cells on a limited number of VCCs (128) are monitored for errors per flow. A BIP-16 is generated for all the cell payloads for each block where the block size is configurable. The block size is defaulted to 128 cells.

- The receiver checks the parity on the received block data and compares its results with the received BIP-16. The number of errors is determined and written to a statistics counter for the indicated VC.

OAM processing uses the ATM VC table as described in section 7.18.4.

#### 7.2.1 SDP

The TDM CPs support OAM performance monitoring. The SDP processors on the CPs do the following:

#### 7.2.1.1 RxSync

The RxSync processor performs the following OAM functions:

• Determines the CRC-10 for each cell received (regardless of whether the cell is OAM or not) and forwards a pass-fail notification to the RxByte processor.

RxSync is not configurable through its control space.

#### 7.2.1.2 RxByte

The RxByte processor performs the following OAM functions:

- Determines whether an F4/F5 OAM cell has been received and indicates this in extract space.

- Writes cell payload overhead to extract space.

- Forwards CRC-10 pass/fail indication to the RC through extract space.

- Determines the BIP-16 value on each cell received and writes this value to extract space.

- Determines whether a user cell has been received and writes this information to extract space.

#### 7.2.2 RC

The RC performs higher level processing of data packets to support OAM –FPM.

#### 7.2.2.1 Initialization

During initialization, the 128 entry OAM PM table is initialized.

#### 7.2.2.2 Receive

The receive thread handles incoming data packets and performs OAM specific operations. Specifically, it does the following:

#### **MSA Application Note**

- Checks whether a received cell is on a VC where OAM FPM is being performed.

This information is stored in the ATM VC table (the oamPm field). If this cell is a user cell, it does the following:

- XORs the current value of the BIP-16 into OAM FPM table running total for all user cells.

- o Increments and masks the CurrentBlockValue (ranges from 0 to BlockSize-1).

- If the received cell is not a user cell, then the code checks whether an OAM cell has been received. If OAM but not of the type OAM FPM cell, the cell is forwarded to the XP. Otherwise, it does the following:

- Compares the CurrentBip16 value with the value received in the OAM FPM Cell. If these values are XOR-ed, the number of bits set indicates the number of errors. The number of bits set is determined through a lookup into a 16-byte table (where each byte in the table indicates the number of bits set for the index) for each nibble (oamPmErrTab). The information is used to update TotalBip16Errs counter.

#### 7.2.3 Data Structures

#### 7.2.3.1 OamPmTable

This OAM processor maintains OAM performance monitoring state information in the following data structure:

| Bytes | 0            | 1              | 2         | 3                 |  |

|-------|--------------|----------------|-----------|-------------------|--|

| 0     | TotalBip1    | TotalBip16Errs |           | CurrentBlockValue |  |

| 4     | CurrentE     | Bip16          | blockSize |                   |  |

| 8     | SegnumExpect | Pad            |           |                   |  |

- totalBip16Errs count of BIP-16 errors calculated so far

- currentBlockValue the number of the cell in the current block

- currentBip16 the value of the BIP-16 calculated so far

- blockSize the block size (in cells)

- seqNumExpect the expected sequence number to be received

- pad unused

# 7.3 Statistics Management

XPRC maintains all the statistics for the MSA applications. Periodically, XP updates host with the statistics to be available to the end user. It passes the statistics storage pointer to the CP's at initialization. CPs update the statistics maintained in XPs at run time. As XPRC has only 16kB of DMEM shared across CPs, the time for XP to update the host should depend on the amount of storage, which is needed to store the statistics.

To synchronize between CPs updating XP DMEM and XP updating host, following implementation is used:

#### **MSA Application Note**

XP maintains two banks of 8KB each in its FAR DATA section (data section which is accessible to CPs). XP keeps shuffling the pointer between these two data banks periodically, so that at the time of updating the host, CPs should access and update the other bank of 8KB.

A list of TDM statistics to be maintained on a per channel basis is as follows:

- chRxChunks Number of received chunks

- chRxPdus Number of received PDUs

- chRxBytes Number of received bytes

- chRxLenErrs Number of chunks having invalid length (e.g. short chunk, long chunk)

- chRxCrcErrs Number of chunks having invalid CRC

- chRxBip8Errs Number of chunks having BIP8 errors

- chRxInvalidErrs Number of chunks having other errors

- chRxFlowChunks Number of Flow chunks

- chRxLookupErrs Number of chunks that caused lookup failure

- chTxChunks Number of transmitted chunks

- chTxPdus Number of transmitted PDUs

- chTxBytes Number of transmitted bytes

#### List of IP statistics:

- IpInReceives Total number packets received in IP module

- IpInHdrErrors The number of input datagrams discarded due to errors in their IP headers.

- IpForwDatagrams Number of input datagrams forwarded

- IpOutPayloadErrors Number of packets discarded due to payload errors

- IpOutInvalidPortErrors Number of packets discarded because its route entry mapped to an invalid egress port.

- IpOutNoRoutes Number of IP datagrams discarded because no route could be found to transmit them to their destination

The following statistics to be provided on a per VC basis (a maximum of 2048)

- AAL5 CRC Errors

- Over Sized PDUs

- AAL5InReceives

Within the 8 KB of DMEM, the following calculation of time and number of bits to be used to hold values, is implemented:

Generally, if we assign 2 bits to store value for each statistic parameter, a total of 8Kb is not sufficient to hold all the parameters. So some of the parameters may have to be removed from this list of statistics (or) the statistics have to be provided using table support. If AAL5 statistics parameters are removed, a total of 8KB is sufficient to hold all the parameters.

Calculating time for updating the host: -

Per channel, 128 chunks to be received in one second i.e., 8K of bytes per second. If 2 bits are used for chRxChunks, then we will have to update host after every 4 chunk. That works out to be around 30 milliseconds.

# 7.4 TDM RX (CP 0 and CP 4)

CP0 and CP4 implement the TDM Rx components for the MSA application. The Channel Processors are directly connected to Twister Mt-21 from outside world. The number of channels to be supported is 2048 (1024 by each TDM Rx component). The channel may carry ATM/FR/PPP traffic. Chunk size support in this application is 64-bytes.

#### 7.4.1 RxSDP

**MSA Application Note**

The SDP receives data from Twister Mt-21 to the RC in the receive direction and from the RC to the Twister Mt-21 in the transmit direction. The chunks that will originate from Twister Mt-21 will be either ATM or HDLC chunks. During the initialization phase itself the TDM interfaces will be configured as PPP or FR. Since it is not possible to differentiate the HDLC frames as PPP or FR in the TDM RxByte, The TDM Rx CPRC will differentiate the PPP and FR chunks based on the channel ID information filled on the extract space. The channel ID will be stored in extract space by the RxByte processor. The channel configuration is stored in DMEM, which is used for identifying the protocol running on that channel. The functions provided by each of its component processors are described below.

#### 7.4.1.1 RxByte

The RxByte processor performs the following:

- Checks for recirculation mode.

- If it is in Non-recirculation mode, it receives the bytes from the RxSync processor. It also writes the previously dropped chunks counter in extract space.

- Initializes the SOP and DroppedChunks registers to 0.

- Reads chunk type, channel Id and channel type into extract space.

- Reads UserValid, HDLC chunk length, HDLC UserInd (SOP/non-SOP) into extract space for User chunks. (Chunk type will determine whether it is the user chunk or flow chunk).

- Reads the HDLC crcInd into extract space.

- For flow chunk,

- Verifies flow control chunk valid bit

- Writes flow control chunk count to extract space.

- Indicates processing complete to the CPRC.

- For user chunk, check the channel type and determine whether it is HDLC chunk or ATM chunk.

#### **HDLC** chunks

- For HDLC chunks, check whether the chunk is SOP or non-SOP.

- For SOP chunk,

- Write the first ten bytes after the TDM chunk header into the extract space. The reason for writing the ten bytes into extract space is both FR and PPP need ten bytes and eight bytes respectively to specify the header information (if the packet is a MPLS packet).

- Set L1 done so that RxCPRC can start processing based on extract space values.

#### **MSA Application Note**

- Send remaining bytes of payload of the chunk to DMEM.

- For non-SOP TDM chunk, it sets L1 done for RxCPRC and sends remaining bytes of payload of the chunk to DMEM.

- When data9 is received, it writes the chunk status code to extract space and switches scope.

#### ATM chunks

- For ATM chunks, it launches lookup into ATM VPI/VCI table for user cells. Identifies and reports OAM/RM cells. Writes the cell header to extract space also.

- Writes the ATM cell payload to extract space also.

- Sets L1 done for RxCPRC and sends remaining bytes of cell payload of the chunk to DMEM.

- When data9 is received, it writes the chunk status code to extract space and switches scope.

#### Transparent chunks

- For transparent chunks, it writes the channel id (port) to extract space.

- Set L1 done so that RxCPRC can start processing based on extract space values.

- Sends remaining bytes of payload of the chunk to DMEM.

- When data9 is received, it writes the chunk status code to extract space and switches scope.

## 7.4.2 RC (CP0 and CP4)

The TDM Rx RC performs higher level processing of chunks. The functions provided by each of its components are described below:

#### 7.4.2.1 Initialization

The TDM Rx component initializes the data structures and registers used by RC. Specifically, it does the following:

- Initializes statistics and chunk reassembly control structures

- Initializes RxSDP control space, Rx DMA control blocks and ring bus Tx registers for ATM VPI/VCI table lookups.

#### 7.4.2.2 Chunk Processing

The Rx RC handles incoming ATM cells or HDLC frames or Transparent chunks. Specifically, it does the following:

#### **HDLC Rx:**

- Waits for L1 done so that SDP has completed the header processing and put the necessary information into extract space.

- Make the pointer (chRxCCBPtr) to TDM Rx Control block in DMEM. chRxCCBPtr will depict the TDM chunks reassembly information in DMEM.

- Processes chunk based on chunk type (flow control or user) in extract space after checking for errors.

#### **MSA Application Note**

For User chunk, differentiate the HDLC frame as PPP or FR chunks based on the Channel ID filled in the extract space and the channel configuration information.

#### FR processing

- For SOM chunk,

- Allocate new buffer for reassembling the FR chunks

- Destination queue will be the FR processing queue.

- o Get the FR header information by properly interpreting the extract space.

- o Write the FR header into TDM Rx channel control block (chRxCCBPtr).

- Initiate the payload transfer from DMEM to SDRAM if no error is indicated in chunk. Update the buffer offset in TDM Rx channel control block (chRxCCBPtr) by incrementing it with chunk length.

- For non-SOM chunks, retrieve reassembly state information (buffer handle and buffer offset) from TDM Rx channel control block (chRxCCBPtr) and initiate the payload transfer from DMEM to SDRAM if no error is indicated in chunk. Also, update the buffer offset in TDM Rx channel control block (chRxCCBPtr).

- For EOM chunk, build the descriptor with buffer handle, buffer length and FR header (DLCI value). En-queue it to the FR processing queue.

#### **PPP** processing

- For SOM chunk,

- Read the 4-byte PPP header from extract space and check for the PPP protocol length. The PPP protocol may be of 1-byte or 2- byte. If the least significant bit of first protocol byte is cleared, then the protocol will be of 2 bytes.

- Set the buffer type for PPP as following based on protocol field value:

- For value 0x0021, bufferType will be BT IPV4

- For value 0x0821, bufferType will be BT MPLS

- For value 0x003d, bufferType will be BT MLPPP

- Read the 4-bytes MLheader from extract space for MLPPP.

- Allocate new buffer and determine destination queue based on buffer type. The destination queues will be IP\_QUEUE, MPLS\_QUEUE and MLPPP\_QUEUE

- Write bufferHandle, destination queue and MLheader into TDM Rx control block (ChRxCCBPtr). Buffer offset will be 0 for SOM.

- Initiate the payload transfer from DMEM to SDRAM if no error is indicated in chunk. Update the buffer offset in TDM Rx channel control block (chRxCCBPtr) by incrementing it by chunk length.

- For non-SOM chunks, retrieve reassembly state information (buffer handle and buffer offset) from TDM Rx channel control block (chRxCCBPtr) and initiate the payload transfer from DMEM to SDRAM if no error is indicated in chunk. Also update the buffer offset in TDM Rx channel control block (chRxCCBPtr).

- For EOM chunk, build the queue descriptor and en-queue it to the destination queue taken from TDM Rx channel control block (chRxCCBPtr). The port buffer

#### **MSA Application Note**

type will be filled with the concatenation of input channel Id and BT\_HDLC in the descriptor. For MPLS the inlfType\_action will be filled as MPLS\_PPP.

Gives scope back to SDP.

#### ATM Rx:

ATM Rx component in TDM Rx CP handles ATM cells. Specifically, it does the following:

- Waits for ATM VPI/VCI lookup to complete

- Lookup failure causes the cell to be dropped and a statistics counter is incremented.

- Allocates new buffer and initiates payload transfer from DMEM to SDRAM.

- Builds descriptor with forwarding information from lookup response

- Waits for payload transfer to complete.

- Determines whether OAM FPM is being performed on this VC. If so:

- For user cells, read the current BIP16 value from extract space and XOR with current value. Update OAM fields.

- For OAM FPM cells, check BIP16 and maintain count of total BIP16 errors.

- For cells other than AAL-5 or AAL-1, it launches port table lookup.

- Waits for port lookup to complete

- En-queues descriptor to egress queue or QoS queue indicated by port lookup

- For AAL-5 cells, with the lookup response from the ATM VC table, the decision is made if the AAL-5 PDU has to be MPLS switched.

- With last AAL-5 cell, fills the descriptor with the information required for MPLS processing. The reassembly module forwards this information to the MPLS processing module.

- For AAL-1 cells, build the descriptor with the following fields:

- AAL1 header from extract space

- o egress port and vcIndex from the ATM VC lookup response.

- For AAL-1 cells, set the destination gueue to AAL1Rx gueue.

- En-queues the descriptor to the destination queue

#### **Transparent chunk processing:**

This component handles transparent TDM chunks. Specifically, it does the following

- Fetch the egress port and ATM cell header from the Rx channel control block indexed by the channel Id.

- Allocates new buffer and initiates payload transfer from DMEM to SDRAM.

- Builds descriptor with AAL1 information (egress port, egress cell header).

- Waits for payload transfer to complete.

- En-queues the descriptor to AAL1Tx queue

#### 7.4.3 Data Structures

**MSA Application Note**

#### 7.4.3.1 Extract Space

```

RxByte writes information about data-grams into extract space for the RC.

typedef volatile struct {

int16u chnkType chanld;

int8u chanType:

int8u userValid;

int8u flowChunkCnt;

int8u chunkStatus;

int8u droppedChunks;

union {

struct {

CellHeader header;

int16u bip16;

int8u encodedPti;

int8u payload[48];

}atm;

struct {

int8u userInd;

int8u crcInd;

int8u chunkLength;

int32u header1;

int32u header2;

int16u header3;

}hdlc:

} proto;

} TdmExtract;

```

The explanations for the above-mentioned fields will be as follows:

- chnkType\_chanId a bitmap defined as follows:

- o b15 : chnkType specifies the chunk type( user chunk or flow chunk )

- o b14 -11: unused.

- o b10 0 : chanld specifies the input channel ID

- chanType specifies the channel type (HDLC/ATM).

- userValid specifies the user valid indicator.

- flowChunkCnt specifies the flow chunk counter.

- chunkStatus specifies the chunk status (good or bad chunk).

- droppedChunks number of dropped chunks.

- userInd user indicator (BOM/COM/EOM).

- crcInd CRC indicator (for CRC16 or CRC32 calculation).

- chunkLength specifies the chunk length.

- header1, header2, header3 HDLC header information (could be FR or PPP)

#### **MSA Application Note**

- Cell header cell header of the ATM AAL-5 cell.

- EncodedPti field to identify the ATM payload type.

- atmPayload 48 bytes of AAL-5 cells.

#### 7.4.3.2 TDM Rx Control Block

The state maintained (in DMEM) for each HDLC frame being reassembled has the following data structure:

Note: Some of the fields of this block are replaced to maintain the egress port and ATM cell header for every transparent channel configured.

| Byte Offset | 0                   | 1 | 2 | 3   |

|-------------|---------------------|---|---|-----|

| 0           | chBufHandle         |   |   |     |

| 4           | chBufOffset chDestQ |   |   | stQ |

| 16          | chMlHeader          |   |   |     |

```

typedef struct {

BsBufHandle chBufHandle;

int16u chBufOffset;

int16u chDestQ;

int32u chMlHeader;

} TdmRxCCB;

```

The explanations for the above-mentioned fields will be as follows:

- chBufHandle: specifies the handle of the reassembled buffer.

- chBufOffset: specifies the offset in the reassembled buffer.

- chDestQ: destination queue where the EOM chunk will be en-queued. This field corresponds to 'egressPort' in the case of transparent chunks.

- chMlHeader: ML header/FR header for PPP/FR respectively. This field corresponds to ATM 'cellHeader' in the case of transparent chunks.

#### 7.4.3.3 Descriptor Structure

The following is the data structure of the descriptor to be en-queued.

| Byte Offset | 0                   | 1 | 2 | 3      |

|-------------|---------------------|---|---|--------|

| 0           | bufHandle           |   |   |        |

| 4           | Length Port_bufType |   |   | ufType |

| 8           | AppData             |   |   |        |

| 12          | AppData             |   |   |        |

typedef struct {

BsBufHandle bufHandle;

int16u length;

#### **MSA Application Note**

```

port bufType;

int16u

union {

byte[8];

int8u

int16u

hword[4];

int32u

word[2];

AtmDescData

atm;

FrDescData

frameRe;

SegDescData

seg;

TdmDescData

tdm;

MIPppDescData mIPpp;

MplsDescData mpls:

Aal1TxDescData aal1Tx;

Aal1RxDescData aal1Rx;

} appData;

} DescriptorMsg;

```

The explanations for the above-mentioned fields will be as follows:

- bufHandle specifies the handle of the reassembled buffer.

- length specifies the chunk length.

- port\_bufType specifies the input port and buffer type of the next module.

- appData Application specific data (FR/PPP/ATM/Transparent TDM).

#### 7.4.3.4 Ring Bus Slots

TDM Rx CP needs to launch lookups in following tables for various packet processing:

ATM VC Table and Port Table.

ATM VC table lookup uses these slots:

- ATM VC request slot 0ATM VC response slot 0

- Port table lookup uses these slots:

- Port table request slot 1Port table response slot 4

#### 7.4.4 TDM statistics

```

typedef struct {

int16u

chRxChunks;

int16u

chRxPdus;

int16u

chRxBytes;

chRxBip8Errs;

// for ATM cells

int16u

int16u

chRxLenErrs;

chRxInvalidErrs;

int16u

int16u

chRxCrcErrs;

int16u

chRxFlowChunks;

```

#### **MSA Application Note**

```

int16u chRxLookupErrs; //for ATM cells

int16u chTxChunks;

int16u chTxPdus;

int16u chTxBytes;

} TdmStats;

```

The description of each field is given below.

```

chRxChunks – Number of received chunks

chRxPdus – Number of received PDUs

chRxBytes – Number of received bytes

chRxLenErrs – Number of chunks having invalid length (e.g. short chunk, long chunk)

chRxCrcErrs – Number of chunks having invalid CRC

chRxBip8Errs – Number of chunks having BIP8 errors

chRxInvalidErrs – Number of chunks having other errors

chRxFlowChunks – Number of Flow chunks

chRxLookupErrs – Number of chunks that caused lookup failure

chTxChunks – Number of transmitted chunks

chTxPdus – Number of transmitted PDUs

chTxBytes – Number of transmitted bytes

```

# 7.5 IMA (CP 1 and CP 5)

CP 1 and CP5 implement the IMA processing. In the transmit direction, this processor handles outgoing cells from other ATM processes and sends them in a round robin fashion among several TDM links in the IMA group. It generates ICP and filler cells and maintains the link and group state machines necessary for IMA connections. In the receive direction, the IMA processor receives cells from the TDM links and performs synchronization to reconstruct the ATM cell stream. It handles ICP and filler cells and maintains the link and group state machines necessary for IMA connections. The IMA component does not use the SDP.

#### 7.5.1 SDP

Since IMA component does not use SDP, this section is not filled in.

#### 7.5.2 RC

The component uses three threads to perform its task, namely, one Receive thread and two Transmit threads.

#### 7.5.2.1 IMA Receive

The IMA Receive thread processes cells received from the TDM links in the following manner:

- Waits for a descriptor to be available in the IMA RX queue then de-queues it.

- Determines the IMA group and link based on the input port from the descriptor.

- For ICP cells, does the following:

- o Initiates a DMA transfer of the cell payload from SDRAM to local DMEM.

#### **MSA Application Note**

- If the ICP cell is a stuffed ICP cell, it is dropped.

- Run the link state machine based on link state information from the ICP cell.

- Run the group state machine based on group state information from the ICP cell.

- Run the frame synchronization state machine.

- If frame sync, put the ICP cell in the link differential delay queue as a filler cell.

- For filler and user cells, if frame synchronization has been attained and the link is active, put the cell in the link differential delay queue.

- Uses round robin to determine which link differential delay queue of the group to service. Removes a cell from the link differential delay queue and does the following:

- o If the cell is a filler cell, it is dropped.

- If the cell is a user cell, it is en-queued to the next processing block (AAL-1, ATM TM, etc.) determined by data in the descriptor.

- Switches to the next context.

- Loops and waits for next descriptor.

#### 7.5.2.2 IMA Transmit Input

The IMA Transmit Input thread de-queues cells and puts them in the transmit soft queues in the following manner:

- Waits for a descriptor to be available in the IMA Tx queue, then de-queues it.

- Determines the IMA group based on the output port from the descriptor.

- Puts the user cell in the transmit soft queue for the group

- Switches to the next context

- Loops and waits for the next descriptor.

#### 7.5.2.3 IMA Transmit Output

The IMA Transmit Output thread runs at the group cell rate. On each tick of the group cell rate clock, the thread does the following:

- Determines the link within the group, which should receive the next cell. This is done in a round robin fashion among all active or usable links in the group.

- If it is time to send an ICP cell on the link, the group state ICP cell storage is updated for the current link and the cell is transferred to an SDRAM buffer via DMA. A descriptor is built and en-queued to the queue of the target TDM link.

- Otherwise, if the link is in the active state and a user cell is available in the transmit soft queue for the link, the descriptor for the user cell is removed from the soft queue and en-queued to the queue of the target TDM link.

- Otherwise, a filler cell is en-queued to the queue of the target TDM link.

- Updates link and group state for link and group on which the cell was just sent.

- Switches to the next context.

- Loops and waits for the next tick.

#### 7.5.3 Data Structures

The IMA component uses the following data structures to maintain state and translate data.

#### **MSA Application Note**

#### 7.5.3.1 ImaLinkState

The IMA link state structure saves state information for each of the available ATM TDM links. The structure has the following format:

| Byte Offset | 0             | 1           | 2            | 3             |

|-------------|---------------|-------------|--------------|---------------|

| 0           | Linkld        | flags       | rxState      | txState       |

| 4           | feState       | frameSync   | frameOffset  | rxFrameSeqNum |

| 8           | txFrameSeqNum | numlcpValid | numlcpErrors | numlcplnvalid |

- linkId the link ID number

- flags a bitmask defined as follows:

- o b7-5: unused

- o b4: link ID valid the received link ID is valid

- o b3: RX failure a receive failure has occurred

- b2: RX fault a receive fault has occurred

- b1: Tx fault a transmit fault has occurred

- o b0: inhibit the link is being inhibited

- rxState value of the RX link state machine

- txState value of the Tx link state machine

- feState values of the far end link state machine and defects

- frameSync value of the IMA frame synchronization state machine

- frameOffset offset within the IMA frame at which the ICP cell should appear

- rxFrameSeqNum the expected received frame sequence number

- txFrameSegNum the frame sequence number to be transmitted

- numlcpValid number of consecutive frames with valid ICP cells used in frame synchronization

- numlcpErrors number of consecutive frames with ICP error cells used in frame synchronization

- numlcpInvalid number of consecutive frames with invalid ICP cells used in frame synchronization

#### 7.5.3.2 ImaGroupState

The IMA group state structure saves state information for each of the IMA groups. The structure has the following format:

| Byte Offset | 0               | 1           | 2           | 3        |

|-------------|-----------------|-------------|-------------|----------|

| 0-11        | icpCell         |             |             |          |

| 12          | linkIdAlloc     |             |             |          |

| 16-47       | linkIdToLinkMap |             |             |          |

| 48          | frameLen        |             | state       | feState  |

| 52          | change          | rxchangenum | txChangeNum | numLinks |

| 56          | suffLinks       | flags       | rxOamLabel  | rxlmald  |

The explanation of fields are as given below:

- icpCell the ICP cell to be sent by the Tx thread

- linkIdAlloc a bitmap indicating which link IDs are in use

#### **MSA Application Note**

- linkIdToLinkMap[32] a mapping from link ID to link state storage structure

- frameLen length of IMA frame (32, 64, 128, or 256)

- state group state machine state

- feState far end group state machine state

- change flag indicating next ICP cell transmitted will have a change in it

- rxChangeNum received status and control sequence number

- txChangedNum next status and control sequence number to transmit in ICP cell

- numLinks number of active links

- suffLinks number of active links needed to leave insufficient links state

- flags a bitmap as follows:

- o b7-1: unused

- o b0: inhibit the group is being inhibited

- rxOamLabel the received OAM label in the ICP cell

- rxImald the received IMA ID in the ICP cell

#### 7.5.3.3 ImaParams

The IMA parameters structure stores information that controls behavior of the IMA unit. The host or other management agent may set these parameters. The structure has the following format:

| Byte Offset | 0     | 1    | 2     | 3   |

|-------------|-------|------|-------|-----|

| 0           | alpha | beta | gamma | pad |

- Alpha the number of consecutive invalid ICP cells that must be received before frame synchronization is lost

- Beta the number of consecutive errored ICP cells that must be received before frame synchronization is lost

- Gamma the number of consecutive valid ICP cells that must be received before frame synchronization is declared

#### 7.5.3.4 ImaPortToGroupMap

The IMA port to group map is an array of bytes MAX\_TDM\_CHANNELS (1024 per CP cluster) long. The index into the array is the port number and the value of the array elements is the group to which the port belongs. If the port does not belong to any group, the value is IMA\_INVALID\_GROUP.

#### 7.5.3.5 ImaPortToLinkMap

The IMA port to link map is an array of bytes MAX\_TDM\_CHANNELS long. The index into the array is the port number and the value of the array elements is the link state index associated with the port. This index is used to index the IMA link state structure array.

#### **7.5.3.6** Merge space

This information need not be provided because SDPs are not going to be used in IMA CP.

#### **MSA Application Note**

#### 7.5.3.7 Extract Space

This information need not be provided because SDPs are not going to be used in IMA CP.

#### 7.5.3.8 Descriptor information

Not available

#### 7.5.3.9 Ring Bus Slots

None

#### 7.5.4 Issues/Enhancements

The IMA component is placed in two CPs. This is because of the DMEM size required for IMA component.

## 7.6 TDM Tx (CP 2 and CP 6)

CP2 and CP6 implement the TDM Tx components for the MSA application.

#### 7.6.1 TxSDP

The TxSDP moves data from the RC to the Mt-21 chip. The functions provided by each of its component processors are described below.

#### 7.6.1.1 TxByte

The TxByte processor performs the following functions as part of the TDM interface:

- Reads 4 bytes of chunk header information from merge space and transmits the chunk header.

- Sets the chunk length counter.

- If channel type is HDLC, reads the payload bytes from DMEM and transmits them.

- Transmits the padding bytes (zero) in the last until chunk length counter reaches zero

- For ATM SOM chunks, reads ATM cell header from merge space adds HEC and transmits.

- For ATM OAM cells, generates CRC-10.

- For transparent chunks, read the payload bytes from DMEM and transmits them.

- Set the merge9 with the last byte.

- Switches the scope for CPRC.

#### 7.6.2 RC (CP2 and CP6)

The TDM Tx RC performs higher level processing of chunks. The functions provided by each of its components are described below:

#### 7.6.2.1 Initialization

The TDM Tx component initializes the data structures and registers used by RC. Specifically, it does the following:

Initializes statistics and chunk segmentation control structures

#### **MSA Application Note**

Initializes TxSDP control space and Tx DMA control blocks

#### 7.6.2.2 Chunk Transmit

The output thread handles outgoing cells or datagrams. Specifically, it does the following:

- Check channels in a round robin manner for credits available (chFlowChunksAvail).

- Get state information for current channel i.e. get the pointer chTxCCBPtr which

points to TDM Tx channel control block in DMEM. This control block will contain

the segmentation state information.

- If chFlowChunksAvail is true, check whether this channel is in the process of segmenting the PDU into chunks i.e. transmitting the chunks of a PDU. If it is so, the next chunk of PDU will be transmitted.

- If no segmentation is in progress, the incoming descriptor will be de-queued from its queue. Note that the descriptor would have been en-queued by

- o TDM Recirculation (CP3 for FR or PPP encapsulation)

- o FR module (CP11 for FR switching)

- ATM segmentation (CP8)

- o AAL1 Tx(CP14)

- o AAL1 Rx(CP15)

- After de-queuing, the segmentation state will be updated with the values fetched from descriptor. Segmentation state values to be updated are: Buffer Handle, Buffer offset, length and port buffer type taken from incoming descriptor. Offset will be filled as zero

- PortBufferType will be checked to determine the incoming module i.e. from which module it has come (BT\_ATM or BT\_TRANSPARENT or others) so that it will segment the PDU accordingly.

- If portBufferType is BT\_TRANSPARENT, it is a transparent chunk from AAL1 Rx CP. It fills the merge space with chanId\_chanType, chunkLength.

- If portBufferType is BT\_ATM, it is an ATM cell and hence will be switched. If portBufferType is other than BT\_ATM, the frame needs to be segmented into number of chunks based on the channel length in chTxCCBPtr.

- For segmenting into chunks, chunk length (1 64 bytes) will be calculated based on offset in ChTxCCBPtr (for first chunk, the offset will be 0). Also if chunk length is less than 64 bytes, it will set the EOM flag stating that it is the last chunk.

- The offset in chTxCCBPtr will be incremented by chunk length for the next chunk.

- It waits for the scope to be available from SDP.

- It fills the merge space with chanld\_chanType, chunkLength and userInd.

- For ATM, fills cell header also into the merge space.

- It then waits for payload transfer of previous chunk to complete.

- It initiates the payload transfer from SDRAM to DMEM for that chunk.

- For EOM chunk, it frees the buffer associated with previous chunk and resets the state information (in chTxCCBPtr) for the new PDU.

Semiconductor, Inc

#### 7.6.3 Data Structures

#### 7.6.3.1 Merge space

The RC writes information about datagrams into merge space. The data structure of merge header looks like following. typedef volatile struct {

```

int16u chanId_chanType;

int8u userChunkLength;

int8u userInd;

union {

struct {

CellHeader atmHeader;

int8u atmPayload[48];

}atm;

struct {

int8u pad1;

}hdlc;

struct {

int32u header;

int8u headerLen:

}pppRecirc;

}proto;

int8u pad[8];

} TdmMerge;

```

The explanations for the above-mentioned fields will be as follows:

- chanId\_chanType a bitmap defined as follows:

- o b15 : unused.

- o b14 4 : chanld specifies the input channel ID

- o b3-1 : chanType specifies the channel Type

(ATM/HDLC/Transparent)

- o b0 : unused.

- userChunkLength chunk length (1-64 bytes)

- userInd specifies the user chunk indicator (SOM/COM/EOM)

- atmHeader ATM Cell header

- atmPayload 48 bytes of ATM cells.

#### 7.6.3.2 TDM Tx Control Block

The state maintained (in DMEM) for segmentation on each outgoing channel is stored in the following data structure:

| Byte Offset 0 1 2 3 |

|---------------------|

|---------------------|

#### **MSA Application Note**

| 0 | chBufHandle       |     |          |  |

|---|-------------------|-----|----------|--|

| 4 | chBufOffset       |     | chLength |  |

| 8 | ChFlowChunksAvail | Pad |          |  |

The explanations for the above-mentioned fields will be as follows:

- ChBufHandle: specifies the Buffer handle that has to be transmitted.

- ChBufOffset: specifies the offset of the chunk in the buffer.

- chLength: specifies the chunk length.

- ChFlowChunksAvail: specifies the counts of credits available to each channel.

- Pad: unused.

#### 7.6.3.3 Descriptor Structure

The descriptor structure for TDM Tx is same as for TDM Rx. The structure is defined in section 7.4.3.3

#### 7.6.4 TDM Statistics

The statistics structure for TDM Tx is same as for TDM Rx. The structure is defined in section 7.4.4

# 7.7 TDM Recirculation (CP3)

CP3 is used to recirculate PPP and FR frames destined for the TDM Tx (CP2/CP6) for transmission. Its purpose is to add the PPP header or FR header in the descriptor to the PPP/FR frame before transmission.

#### 7.7.1 SDP

The SDP adds the PPP or FR header to the frame. The functions provided by each of its component processors are described below. Only RxByte and TxByte are used for this purpose.

#### 7.7.1.1 TxByte

The TxByte processor performs the following functions:

- Reads channel Id from merge space and transmits as first byte of the chunk.

- Read the Buftype from merge space. It will also differentiate between PPP and FR. If Buftype is not BT\_IP\_FR or BT\_MPLS\_FR, it will be the PPP frame.

#### **MSA Application Note**

- For PPP.

- Reads the PPP header length from merge space, then reads that many bytes from the header field in merge space and transmits these.

- For FR,

- Reads the first two bytes of FR header (that contains DLCI values) from merge space and transmits these.

- For bufferType BT\_IP\_FR, transmits out the control byte (0x00) and NLPID (0xcc) byte.

- For bufferType BT\_MPLS\_FR, construct the LLC SNAP header encapsulation bytes and transmit these bytes.

- Reads remaining payload from DMEM until data9 is observed.

- Switches scope.

#### 7.7.1.2 RxByte

The RxByte processor performs the following functions:

- Receives bytes from the TxByte processor.

- The first byte of the chunk contains the channel Id. This is written to extract space and header ready is indicated in the rxStatus register.

- All bytes are written to DMEM.

- When data9 is received, switches scope.

#### 7.7.2 RC

The RC manages the TDM recirculation. All CPs that want to transmit PPP/FR frames, en-queue their packets to the TDM recirculation CP3 so that the PPP/FR header is added to the frame before transmission.

#### 7.7.2.1 Initialization

The initialization component initializes the data structures and registers used by the RC. Specifically, it does the following:

- Initializes statistics and chunk control structures.

- Initialize SDP control space, Tx/Rx DMA control blocks. Indicate TDM RxSDP to run the recirculation portion of the code.

#### 7.7.2.2 RxCPRC

The receive component handles incoming packets from the SDP. Specifically, it does the following:

- Waits for indication of header processing completion.

- Creates descriptor with buffer handle and length.

- En-gueues packets based upon the channel Id indicated in extract space.

- Allocates buffer, sets up DMA block and gives scope back to SDP.

## **MSA Application Note**

#### 7.7.2.3 TxCPRC

The transmit component services its TDM Recirculation egress queue (all PPP or FR traffic which needs a header inserted in the frame gets en-queued here). This CP then passes chunks to the SDP. Specifically, it does the following:

- De-queues the packet descriptor from its TDM Recirculation egress queue. This

descriptor would have been en-queued by IP or MPLS channel processors.

- Waits for scope to be available from SDP.

- Gets channel Id (input port) and buffer type from the descriptor. Buffer type may be one of the following.

- o BT\_IP\_FR: if the FR frame originates from IP module

- o BT\_MPLS\_FR: if the FR frame originates from MPLS module

- o Otherwise it is the PPP frame originating from IP/MPLS module

- Determines protocol type based on buffer type.

#### PPP processing:

For the buffer type BT\_IP\_PPP and BT\_MPLS\_PPP,

- Determines the 4-byte PPP header including protocol, and calculates the header length.

- Fills the channel Id, BufType, PPP header and header length into the merge space.

#### FR processing:

For the buffer type BT\_IP\_FR and BT\_MPLS\_FR

- Fill the channel Id, BufType and FR header information (2-bytes containing DLCI) from descriptor into the merge space.

- Sets up DMA engine with buffer handle from descriptor.

- Initiates payload transfer from SDRAM to DMEM and gives scope to the SDP.

- Frees buffer from previous transmit in this scope.

#### 7.7.3 Data Structures

#### 7.7.3.1 Merge space

The merge space structure is defined below.

#### For FR

| Byte Offset | 0         | 1         | 2               | 3       |

|-------------|-----------|-----------|-----------------|---------|

| 0           | chanld_c  | hanType   | userChunkLength | userInd |

| 4           | BufType   | Fr header |                 |         |

| 12          | Fr header | Pad       |                 |         |

| 16          | Pad       |           |                 |         |

| 20          | Pad       |           |                 |         |

The explanations for the above-mentioned fields will be as follows

chanId chanType – a bitmap defined as follows:

## **MSA Application Note**

o b15 : unused.

b14 - 4 : chanId – specifies the input channel ID

b3-1 : chanType – specifies the channel Type (ATM/HDLC/Transparent)

o b0 : unused.

UserChunkLength: specifies the length of the user chunk.

UserInd: specifies the user chunk indicator (BOM/COM/EOM)

BufType: specifies the type of the buffer.

• FR header: specifies the DLCI value and the congestion control information.

Pad: unused

#### For PPP

| Byte Offset | 0          | 1                                | 2 | 3 |

|-------------|------------|----------------------------------|---|---|

| 0           | chanld_c   | chanType userChunkLength userInd |   |   |

| 4           | BufType    | PPP header                       |   |   |

| 12          | PPP header | PPPheaderLen Pad                 |   |   |

| 16          | Pad        |                                  |   |   |

| 20          | Pad        |                                  |   |   |

The explanations for the above-mentioned fields will be as follows

chanId\_chanType – a bitmap defined as follows:

o b15 : unused.

o b14 - 4 : chanld – specifies the input channel ID

o b3-1 : chanType – specifies the channel Type

(ATM/HDLC/Transparent)

o b0 : unused.

• UserChunkLength: specifies the length of the user chunk.

• UserInd: specifies the user chunk indicator (BOM/COM/EOM)

BufType: specifies the type of the buffer.

PPP header: specifies the PPP header information.

PPP headerLen: specifies the length of the PPP header.

Pad: unused

#### 7.7.3.2 Extract space

The extract space structure is defined below.

| Byte Offset | 0      | 1 | 2   | 3 |

|-------------|--------|---|-----|---|

| 0           | chanld |   | Pad |   |

The explanations for the above-mentioned fields will be as follows

ChanId: specifies the channel ID.

Pad: unused.

# MSA Application Note

## 7.7.3.3 Descriptor

The descriptor structure is same as for TDM Rx. The structure is defined in <u>section</u> 7.4.3.3.

# 7.8 IPv4 (CP 7)

CP 7 implements the IPv4 (Layer 3 forwarding) component for the MSA application.

IP routing is the process of forwarding IP frames at layer 3 based upon the IP Destination Address (IP DA). An advantage of IP routing is that it can be used between dissimilar network media types. This application covers IP routing over ATM or Frame Relay or PPP/MLPPP.

Assumptions and notes for use:

- IP header options will not be recognized.

- IP Fragmentation and reassembly not supported

- Lookup is launched on the IP DA.

- Application generates two types of ICMP messages, which are based on the events that happen in the data path:

- o ICMP Time exceeded

- ICMP destination unreachable