# AN14650

## **SmartDMA Cookbook**

Rev. 1.0 — 28 May 2025

**Application note**

#### **Document information**

| Information | Content                                                                                                                                                                                   |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords    | AN14650, SmartDMA, EZH, cookbook, MCX MCU, LPC5500                                                                                                                                        |

| Abstract    | This application note primarily introduces the internal architecture, main functions, and features of EZH or SmartDMA, and finally lists the usage and meanings of the main instructions. |

SmartDMA Cookbook

## 1 Introduction

This application note primarily introduces the internal architecture, main functions, and features of EZH or SmartDMA, and finally lists the usage and meanings of the main instructions. EZH (SmartDMA) is an NXP unit that efficiently manages repetitive and event-driven tasks, reducing the workload on Arm cores. It significantly improves system performance in input and output (I/O) handling, data processing, and real-time operations.

## 1.1 What is EZH (SmartDMA)?

EZH, also known as SmartDMA, is primarily aimed as a complementary unit to the Arm core within NXP devices.

Rather than replacing the Arm, the primary objective of EZH is to offload tasks from the Arm processor, and optimize performance and efficiency.

EZH provides significant advantages over Arm processing, specifically in:

- Fast response: It provides a quick reaction to input and output (I/O), and Boolean events.

- Efficiency at lower frequencies: It offers improved performances as EZH eliminates interrupt delays.

- Expanded instruction set: It uses a 32-bit instruction set offering broader functionality to the 16-bit thumb instruction set.

- Advanced extension: It includes built-in innovative functionalities, such as heartbeat, timer, and supervised

execution.

- Concurrent data access: It implements a dual AHB bus controller, allowing simultaneous data read and code execution.

EZH ensures that the processor maintains all advantages of Arm, enhancing its performance in specific operational tasks.

#### 1.2 Advantages of choosing EZH

EZH effectively manages repetitive and event-driven I/O operations. It significantly reduces the workload of Arm processors for essential and routine tasks. <u>Table 1</u> illustrates the advantages of EZH over Arm Cortex-M0+.

Table 1. Comparison between EZH and Arm Cortex-M0+

| Functions             | EZH                                                                                                              | Cortex-M0+                                                                                       |

|-----------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| Architecture          | Modified Harvard architecture with dual AHB bus (Instruction and Data)                                           | Von Neuman architecture with single system bus                                                   |

| Event latency         | Bit-slice operation (no cycle penalty) for I/O event                                                             | ISR latency (15 CPU cycles with 0-waitstate memory)                                              |

| I/O access            | Register-based I/O access using 3 core registers — GPO/GPI/GPD, supported by intrinsic instructions.             | Memory-based I/O access over AHB; one extra cycle needed for load or store (LDR/STR) operations. |

| State machine         | Intrinsic instructions for state machine, E_VECTORED_HOLD                                                        |                                                                                                  |

| Determinate execution | Determinate execution with intrinsic instructions like:  E_HEART_RYTHM,E_SYNCH_ALL_TO_BEAT, and E_WAIT_FOR_BEAT. |                                                                                                  |

| Hardware circle loop  | 0-waste hardware circle loop supported by intrinsic instruction                                                  | Circle loop execution with a one cycle penalty.                                                  |

**SmartDMA Cookbook**

## 1.3 Typical EZH applications

EZH (SmartDMA) is beneficial in scenarios requiring efficient data manipulation, I/O handling, and real-time operations. The following are some typical use cases:

#### SmartDMA applications:

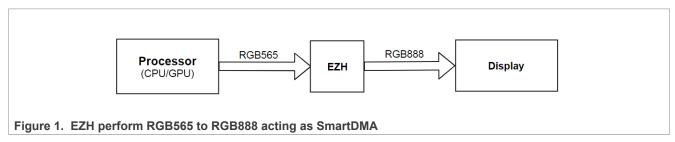

Regular DMA is limited to data movement between memory locations without a main processor involved. EZH, working as SmartDMA, can process data or convert data during data transmission. For example, it can convert RGB565 to RGB888.

There are various data formats for bitmap images; two common ones are RGB565 for 16-bits color and RGB888 for real-color. In microcontroller, RGB565 is commonly used in image processing due to its lower memory usage and less computation effort. A challenge arises when rendering RGB565 to display, as some display interfaces; especially those with 8-bit parallel interfaces like the INTEL 8080 do not support RGB565 rendering. In a legacy system, the CPU first converts the data from RGB565 to RGB888, and then the DMA transfers the converted image to the display interface. With EZH, RGB565 data can be rendered directly to the display without CPU involvement, as EZH performs the data format conversion during transmission.

#### Boolean detection and general I/O handling:

In applications like key scanning, EZH uses bit-slice operation for key detection. Its register-based I/O handling accelerates key scan response time and enhances sensitivity.

## • Protocol emulation over I/O:

EZH can be used to simulate serial bus protocols, such as USART, I2C, SPI, ISO7816, and PWM.

#### • Shift-based algorithm calculation:

EZH uses shift-based intrinsic instructions to efficiently execute algorithm operations, such as CRC and SHA.

#### • Large-scale data manipulation:

EZH can be used for data format conversion, serving as a data preprocessing engine. While processor synchronization is required sometimes, it is not a big concern for big data processing. For example, in an image-processing application, the image comes as a bitmap array. However, most algorithm must divide the image into blocks and process them sequentially using convolution or filter. During image preprocessing, EZH can convert a two-dimensional image block into a vector for further calculation, as vector calculation is accelerated in most modern processors.

#### • State machine control and streaming GPIO:

EZH is effective at controlling a state machine and streaming GPIO. It also provides powerful boolean detection, external event monitoring, and single cycle GPIO operation. These capabilities allow EZH to handle tasks ranging from simple applications like traffic light control to more complex implementations such as sophisticated I3C protocol emulation.

#### • Multiple quadrature encoders or decoder emulation over IO:

In polling mode, EZH can detect the phase A and B signals to output the direction and counter value of the encoder. It also supports two or more encoders.

**SmartDMA Cookbook**

## 2 EZH Architecture and function description

EZH acts as an AHB controller in a dual-bus system, enabling efficient data handling with minimal CPU load. It also includes bit-slice logic, lightweight processor core, and interfaces for AHB, GPIO, and interrupts, supporting quick detection and real-time control.

## 2.1 EZH in system

EZH functions as an AHB controller in the system within a dual bus architecture. The instruction bus fetches instructions, while the data bus fetches read-only data (RO) and read or write data (RW).

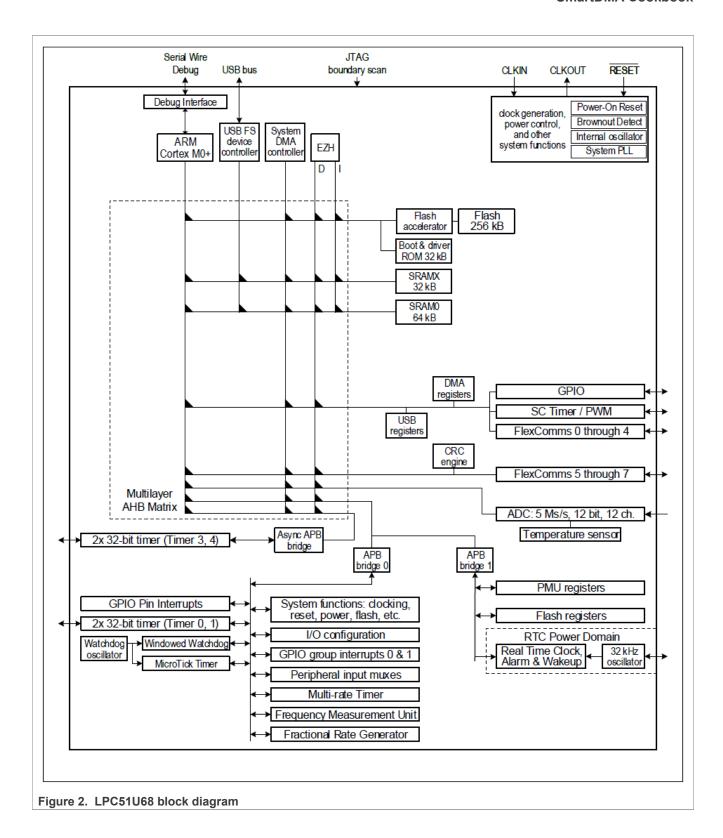

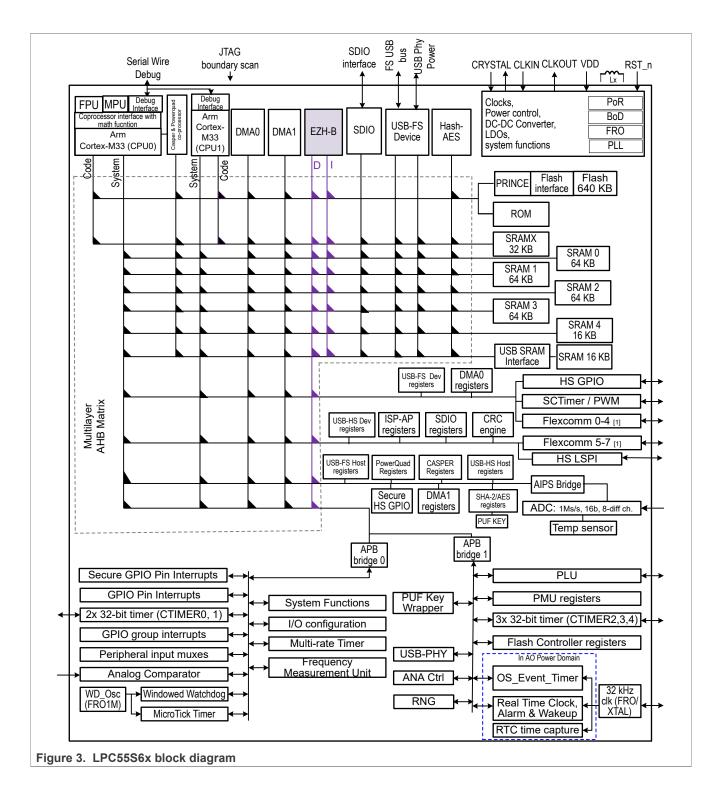

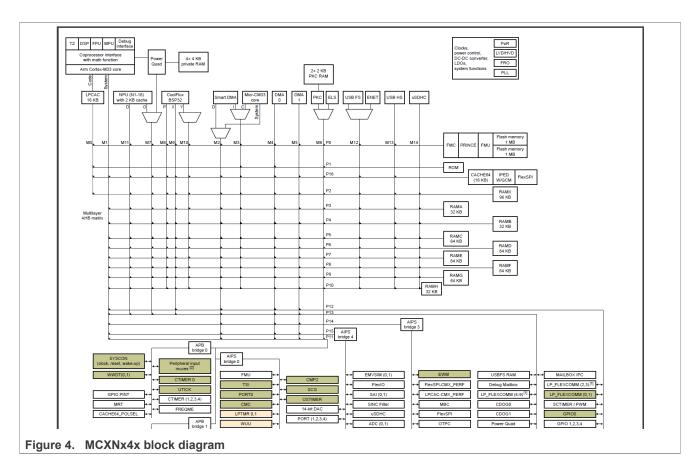

As an AHB controller device, the AHB matrix priority register in the SYSCON or SYSCTL module can prioritize EZH bus access. See the figures below: Figure 2, Figure 3, and Figure 4

**SmartDMA Cookbook**

#### **SmartDMA Cookbook**

**SmartDMA Cookbook**

#### 2.2 EZH architecture

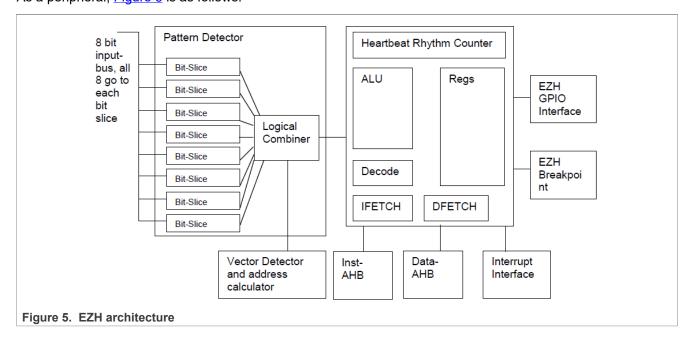

As a peripheral, Figure 5 is as follows:

**SmartDMA Cookbook**

## 3 EZH registers

EZH peripherals provide a set of control and internal registers for configuration and operation. These registers are mapped on the APB and are accessible through a defined base address specific to each supported MCU.

## 3.1 EZH peripheral registers

EZH controller registers are placed on the APB bus. <u>Table 2</u> provides the base addresses of EZH controller registers in the memory map.

Table 2. EZH controller base address

| Part number           | EZH control register base address |

|-----------------------|-----------------------------------|

| LPC5410x              | 0x4004C000                        |

| LPC54114/LPC51U68     | 0x4001D000                        |

| LPC55(S)6x/LPC55(S)2x | 0x4001D000                        |

| LPC55(S)3x            | 0x4001D000                        |

| IMXRT500              | 0x40027000                        |

| MCXNx4x/MCXN23x       | 0x40033000                        |

EZH controller registers are listed and explained in <u>Table 3</u>.

Table 3. EZH peripheral registers

| Name            | Access | Offset | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Reset<br>Value |

|-----------------|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| EZHB_BOOT       | R/W    | 0x20   | 32-bit boot address. The boot address must be aligned to a 4-byte boundary.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0x00           |

| EZHB_CTRL       | R/W    | 0x24   | <ul> <li>B31:16 - Must be set to 0xC0DE.</li> <li>B15: 5 - Reserved (must be 0).</li> <li>B4 - Must be set to 1 to enable AHB synchronization.</li> <li>B3 - Selects bufferable or nonbufferable mode for AHB write (if AHB buffer is available).</li> <li>B2 - Ignore AHB bus error. If set to 0, the AHB bus triggers an emergency.</li> <li>B1 - External flag, which influences the EX/NEX condition logic—when set to 1, it satisfies the EX condition, and when cleared to 0, it satisfies the NEX condition.</li> <li>B0 - Start bit, which acts as an ignition signal — when set, it triggers the EZH to begin executing instructions.</li> </ul> | 0x00           |

| EZHB_PC         | RO     | 0x28   | EZH program counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0x00           |

| EZHB_SP         | RO     | 0x2C   | EZH stack pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x00           |

| EZHB_BREAK_ADDR | R/W    | 0x30   | 32-bit address to EZHB_BREAK_VECT location                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0x00           |

| EZHB_BREAK_VECT | R/W    | 0x34   | User debug routine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x00           |

| EZHB_EMER_VECT  | R/W    | 0x38   | Emergency code routine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0x00           |

| EZHB_EMER_SEL   | R/W    | 0x3C   | <ul> <li>B9 - Software emergency request</li> <li>B8 - Enables the software emergency mechanism</li> <li>B7:0 - Reserved and must be written as 0.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0x00           |

SmartDMA Cookbook

Table 3. EZH peripheral registers...continued

| Name          | Access | Offset | Description                                                                                                                                                                                                                                                                                                                                                                                        | Reset<br>Value |

|---------------|--------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| EZHB_ARM2EZH  | R/W    | 0x40   | <ul> <li>B31:2 - General-purpose bits.</li> <li>B1:0 - Control the EZH interrupt trigger mechanism.</li> <li>When [1:0] == 0b10, a write operation to the EZH2ARM register triggers an interrupt to the Arm processor.</li> </ul>                                                                                                                                                                  | 0x00           |

| EZHB_EZH2ARM  | R/W    | 0x44   | B31:0 - General-purpose bits.  Writing data to the EZHB_EZH2ARM register can trigger an interrupt to the Arm processor when EZHB_ARM2  EZH[1:0] == 0b10.                                                                                                                                                                                                                                           | 0x00           |

| EZHB_PENDTRAP | R/W    | 0x48   | B31:24 - Reserved B23:16 - Pending trap enable B15:8 - Pending trap status polarity B7:0 - Pending trap request and status Note: Arm can have a 'shortcut' to control bit-slices result using pending trap registers. By default, the pending trap feature is disabled.  Example: Setting EZHB_PENDTRAP = (1 << 16)   (1 << 0); enables the pending trap for bit-slice 0 and sets its result to 1. | 0x00           |

## 3.2 EZH internal registers

All EZH registers are 32-bit as shown in <u>Table 4</u>.

Table 4. EZH internal registers

| Register | R/W | Purpose                                                                                                                                                                                                                                                                                                                                                                   |

|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R0 – R7  | RW  | General-purpose registers                                                                                                                                                                                                                                                                                                                                                 |

| GPO      | RW  | EZH GPIO output register  EZH GPIO output register bits [31:0] control the output states of EZH GPIO pins 31-0. If no PIN is configured as EZH GPIO, the register can be used as general-purpose registers.  Write 0 – Clear output bit  Write 1 – Set output bit                                                                                                         |

| GPD      | RW  | EZH GPIO direction register  EZH GPIO direction register bits [31:0] select the pin direction of EZH GPIO 31-0. If no PIN is configured as EZH GPIO, the register can be used as general-purpose registers.  1 – Output  0 – Input                                                                                                                                        |

| GPI      | RO  | EZH GPIO input register  Each bit [31:0] of the EZH GPIO input register reflects the state of EZH GPIO pins 31-0.  0 – Pin is low  1 – Pin is high                                                                                                                                                                                                                        |

| CFS      | RW  | Bit-slice source configuration register  Bits 31-8 are used for bit slice source configuration. Each bit slice is configured using 3 bits. Bit slice 0 occupies the low 3 bits [10:8], bit slice 1 occupies bits [13:11], bit slice 2 occupies bits [16:14], and so on.  Also, the lower 8 bits [7-0] of the register provide the current input status of the bit slices. |

| CFM      | RW  | Bit slice event configuration register                                                                                                                                                                                                                                                                                                                                    |

SmartDMA Cookbook

Table 4. EZH internal registers...continued

|          |     | Tegrister'scomunued                                                                                                                                                                                                                   |

|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register | R/W | Purpose                                                                                                                                                                                                                               |

|          |     | Bits 31-8 are used for bit slice event configuration. Each bit slice is configured using 3 bits. Bit slice 0 occupies the low 3 bits [10:8], bit slice 1 occupies the bits [13:11], bit slice 2 occupies the bits [16:14], and so on. |

|          |     | Each 3-bit field controls the event detection behavior of the corresponding bit slice. The possible event configurations per slice are:                                                                                               |

|          |     | • 0 – Always 1                                                                                                                                                                                                                        |

|          |     | • 1 – Sticky rising edge                                                                                                                                                                                                              |

|          |     | • 2 – Sticky falling edge                                                                                                                                                                                                             |

|          |     | • 3 – Sticky any edge                                                                                                                                                                                                                 |

|          |     | • 4 – High level                                                                                                                                                                                                                      |

|          |     | • 5 – Low level                                                                                                                                                                                                                       |

|          |     | • 6 – Always 0                                                                                                                                                                                                                        |

|          |     | • 7 – Any edge                                                                                                                                                                                                                        |

|          |     | Also, the lower 8 bits [7-0] of the register are used for bit slice output result routing, where B0 corresponds to bit slice 0, B1 corresponds to bit slice 1, and so on.                                                             |

|          |     | • 1 – Bit-slice output result is routed to a logical combiner.                                                                                                                                                                        |

|          |     | • 0 – Bit-slice result is routed to the next bit slice.                                                                                                                                                                               |

| SP       | RW  | EZH stack pointer register                                                                                                                                                                                                            |

|          |     | EZH stack pointer register must be initialized, even if the EZH stack is not actively used.                                                                                                                                           |

| PC       | RW  | EZH program counter register                                                                                                                                                                                                          |

|          |     | EZH program counter register is always positioned two instructions ahead of the instruction that is being loaded for execution.                                                                                                       |

| RA       | RW  | EZH return address register                                                                                                                                                                                                           |

|          | 1   |                                                                                                                                                                                                                                       |

Note: If some registers such as CFM, GPD, GPI are not used, they can be used as general-purpose registers.

## 4 Application guide

This section introduces the development methods and application cases of SmartDMA or EZH.

#### 4.1 EZH release

EZH mainly provides a C header file in which the machine code of EZH appears as inline assembly code through embedded C macro definition. After the user program initializes the EZH peripheral registers, EZH assembly instructions can be written in a routine to implement the function. For better execution efficiency of EZH, specify this routine to run in RAM.

#### 4.1.1 IDE support

EZH code runs on all popular tool chains—MDK-Keil, MCUXpresso, and IAR supported with code array style. Arm compiler V6 and newer versions support the latest EZH instructions.

#### 4.1.2 Project scatter file

The project scatter file can be modified to relocate EZH code to RAM. During compilation, the scatter file is set up to compile the code and store it in FLASH. When \_\_main runs, the scatter loader generated by Arm-clang copies every content marked for RAM to its final destination.

**SmartDMA Cookbook**

## 4.1.3 EZH assembly programming

EZH instruction code can be embedded in the Arm compiler through macros called EZH pseudo instructions, which make it easy to write EZH code in the C language. The same EZH code can also be compiled into a library.

#### 4.1.4 EZH controller APIs

EZH controller APIs as summarized in Table 5, provide function-level access to the EZH controller.

Table 5. EZH controller API function reference

| Function                                                                               | Description                                                                                                                                                                                                                                                                                                                                                                                                              | Parameter                              | Return value |

|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------|

| void EZH_Init(void)                                                                    | Initialize the EZH processor.<br>Enable the EZH clock by setting<br>bit 4 of EZHB_CTRL to 1 for<br>AHB synchronization.                                                                                                                                                                                                                                                                                                  | None                                   | None         |

| void EZH_Boot(void *p<br>Program, void *pPara, uint32_<br>t mask)                      | Start EZH for execution. pProgram: Pointer to EZH program start address (Must be 4-byte aligned) pPara: Pointer to EZH program parameter (Must be 4-byte aligned) uint32_t mask: Controls the behavior of EZH-Arm interaction 0 – Default EZHB_ARM2EZH_REGINT_ MASK: Writing to EZH2ARM register can trigger an EZH INT to Arm EZHB_ARM2EZH_EVENTOUT_ MASK: Writing to the EZH2ARM register can trigger an EZH event out | pProgram, pPara, and uint32_t mask     | None         |

| void EZH_Reset (void)                                                                  | Stop EZH execution.                                                                                                                                                                                                                                                                                                                                                                                                      | None                                   | None         |

| void EZH_Delnit (void)                                                                 | Disable EZH and deactive EZH clock.                                                                                                                                                                                                                                                                                                                                                                                      | None                                   | None         |

| void EZH_SetExternal<br>Flag(uint8_t flag)                                             | Set or clear the external flag in<br>the EZH Ctrl register.<br>flag: External flag to be set or<br>cleared.                                                                                                                                                                                                                                                                                                              | flag                                   | None         |

| void EZH_SetEmergency<br>Mode(void *ezh_emergency_<br>routine, uint8_t enable)         | When enabled, the EZH program jumps to the emergency routine if an emergency is triggered. ezh_emergency_routine: EZH emergency routine vector to be set. enable: Enables EZH emergency mode.                                                                                                                                                                                                                            | ezh_emergency_routine, enable          | None         |

| void EZH_TriggerEmergency<br>Mode (void)                                               | Trigger an emergency event.                                                                                                                                                                                                                                                                                                                                                                                              | None                                   | None         |

| void EZH_SetBreakpoint<br>Address (void *break_point_<br>addr, void *break_point_vect) | Set a breakpoint and enable a user debug routine. break_point_addr: 32-bit address to be swapped to EZHB_BREAK_VECT location.                                                                                                                                                                                                                                                                                            | break_point_addr, break_point_<br>vect | None         |

**SmartDMA Cookbook**

Table 5. EZH controller API function reference...continued

| Function | Description                                  | Parameter | Return value |

|----------|----------------------------------------------|-----------|--------------|

|          | break_point_vect: User debug routine vector. |           |              |

User can refer to the code examples for a better understanding of API usage.

#### 4.1.5 APIs example

These examples show how to initialize, configure, and run the EZH controller with basic API usage (use LPC55xx code as examples).

```

void EZH_Init(void)

CLOCK EnableClock(kCLOCK EzhArchB0);

LPC \overline{EZH} ARCH BO \rightarrow EZHB \overline{CTRL} = (0 \times CODE00000 | (1 < EZHB ENABLE GPISYNCH));

}

void EZH Boot(void * pProgram, void *pPara, uint32 t mask)

LPC EZH ARCH BO->EZHB ARM2EZH = ((uint32 t)pPara | mask);

LPC EZH ARCH BO->EZHB BOOT = (uint32_t) pProgram;

SYSCON->AHBMATPRIO = PRI_EZHD(1) | PRI_EZHI(1); //M6 - Inst, M7 - Data

LPC EZH ARCH BO->EZHB CTRL = 0xC0DE0011 | (0<<EZHB MASK RESP) |

(0<<EZHB ENABLE AHBBUF);

};

void EZH Deinit(void)

LPC EZH ARCH BO->EZHB CTRL = 0xC0DE0000;

CLOCK DisableClock (kCLOCK EzhArchB0);

}

void EZH Reset(void)

RESET PeripheralReset (kEZH ARCH B0 RSTn);

LPC EZH ARCH BO->EZHB CTRL = (0xC0DE00000 | (1<<EZHB ENABLE GPISYNCH));

}

void EZH SetExternalFlag(uint8 t flag)

volatile uint32 t ezh ctrl = (LPC EZH ARCH BO->EZHB CTRL & 0x0000FFFF);

if (flag == 0) {

ezh_ctrl &= ~(1 << EZHB EXTERNAL FLAG);

} else {

ezh ctrl |= (1 << EZHB EXTERNAL FLAG);

LPC EZH ARCH BO->EZHB CTRL = (0xC0DE0000 | ezh ctrl);

}

void EZH SetEmergencyMode(void *ezh emergency routine, uint8 t enable)

```

AN14650

LPC EZH ARCH BO->EZHB EMER SEL &=  $\sim (1 << 8)$ ;

LPC EZH ARCH B0->EZHB EMER VECT = (uint32 t)ezh emergency routine;

if (enable != 0) {

**SmartDMA Cookbook**

```

} else {

LPC_EZH_ARCH_B0->EZHB_EMER_VECT = (uint32_t)ezh_emergency_routine;

LPC_EZH_ARCH_B0->EZHB_EMER_SEL |= (1 << 8);

}</pre>

```

```

void EZH_TriggerEmergencyMode(void)

{

LPC_EZH_ARCH_B0->EZHB_EMER_SEL |= (1 << 9);

}</pre>

```

```

void EZH_SetBreakpointAddress(void *break_point_addr, void *break_point_vect)

{

LPC_EZH_ARCH_BO->EZHB_BREAK_ADDR = (uint32_t) break_point_addr;

LPC_EZH_ARCH_BO->EZHB_BREAK_VECT = (uint32_t) break_point_vect;

}

```

How to initialize and start the EZH for code execution:

```

EZH_Init(); //enable EZH clock and enable GPI AHB Synchronize

NVIC_EnableIRQ(IOH_IRQn); //enable interrupt of EZH

EZH_Pin_Init(); //set the pin function as EZH function

EZH_Boot(EZH_Code, &para, 0); //boot code from EZH_Code, para is parameter for EZH

```

The EZH then begins executing the code.

#### 4.1.6 EZH clock and reset

The system control module handles both clock and reset control for EZH. The EZH clock must be enabled before configuring an EZH controller and executing an EZH program.

#### 4.1.7 EZH PINMUX

EZH can access and manipulate up to 32 I/O pins when those pins are set to the 'EZH Function' in the PINMUX register. In the user manual spreadsheet, 'EZH Function' corresponds to:

- FUNC 4 on LPC5410x, LPC5411x, and LPC51U68

- FUNC 15 on LPC55(S)3x, LPC55(S)6x, and IMXRT500

- FUNC 7 on MCXNx4x

#### 4.1.8 EZH Trigger

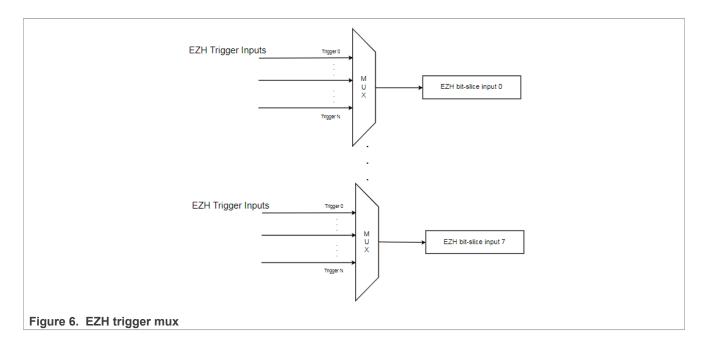

EZH has 8 bit-slices; each bit-slice can be connected to one external trigger. The INPUTMUX can be used to configure the input to each EZH bit-slice. As shown in <u>Figure 6</u>, platform-dependent triggers can be mux to EZH bit-slice input. Details about the EZH trigger mux register and the supported triggers can be found in the INPUTMUX register description.

SmartDMA Cookbook

#### 4.1.9 EZH Interrupt

Like any other interrupt service routine(ISR), the Arm interrupt for EZH can be enabled through the Arm Nested Vectored Interrupt controller (Arm NVIC). The ISR function must be added to the ISR table in the startup file. The EZH IRQ number can be found in the NVIC chapter of the user manual.

#### 4.2 Functions

This section introduces the basic functions of EZH, such as bus access, Arithmetic logic unit, Barrel shifter, Flags, and Algorithmic or branch control, among others.

#### 4.2.1 Dual bus

EZH, like other CPUs, uses a pipeline to **fetch**, **decode**, and **execute** instructions. To optimize instructions and data fetching, EZH uses a dual interface to AHB:

- Instruction bus (Inst-AHB): It is exclusively used to fetch opcodes.

- Data bus (Data-AHB): It is used for fetching any other type of data access such as literals (RO data or memory accesses) anywhere across the chip.

Unlike an Arm core, EZH fetches data literals over the Data-AHB rather than Inst-AHB. This choice brings three advantages:

- **Simplification of the program counter mechanism:** The instruction bus is consistently two instructions ahead of the decode or execution stage, streamlining pipeline operation.

- **Deterministic correlation between IFETCH and DECODE**: The predictable correlation between IFETCH and DECODE stages enables the system to avoid unnecessary pipeline flush on a branch and precisely track the number of extra opcodes fetched.

- Efficient scheduling of data accesses: By routing all data reads through the DFETCH unit, the system enables efficient scheduling of reads and writes. This ensures that data, offset, and address fetches are managed without stalling the EZH pipeline.

**SmartDMA Cookbook**

## 4.2.2 Arithmetic Logic Unit(ALU)

Arithmetic logic unit (ALU) is used for performing both arithmetic and logical operations.

- Arithmetic operations: It supports maximum signed 32-bit arithmetic operations, including addition and subtraction.

- Logic operations: It supports logic operations, such as AND, OR, and XOR, including a combination of AND followed by OR, with most operations completed within a single cycle.

The EZH architecture can perform a combination of operations - FEND/FBIT + LSR + ALU + S - in a single cycle. This allows either Preshift + ALU or Postshift execution without extra delay.

#### Note:

- If the destination is the program counter (PC), no flag can be set during an ALU.

- If a set flag ALU opcode is used with the PC as the destination, it acts as a request for a scheduled branch to the new value of the PC.

Refer to the following examples:

#### 4.2.3 Barrel shifter

The EZH barrel shifter supports shifting and rotating operations with an immediate value ranging from 0 to 31.

In cases where the shift amount operand comes from a register, the EZH supports the shift and rotate value determined by the bottom byte of a register. Depending on the shift amount, the expected outcomes for the result and the carry flag are summarized in <a href="Table 6">Table 6</a>.

Table 6. Barrel shifter operation

| Operation | How many bits to shift | Result      | Carry bit      |

|-----------|------------------------|-------------|----------------|

| LSL       | 32                     | 0           | bit0           |

| LSR       | 32                     | 0           | 0              |

| ASR       | 32                     | sign bit    | sign bit       |

| ROR       | 32                     | unchanged   | bit 31         |

| LSL       | 33 or more             | 0           | 0              |

| LSR       | 33 or more             | 0           | 0              |

| ASR       | 33 or more             | sign bit    | sign bit       |

| ROR       | 33 or more             | rotate % 32 | modulus 32-bit |

#### 4.2.4 Flip or invert

The flip or invert feature provides bits order flip and bytes order flip capabilities before an ALU operation. This allows input data to be optionally preprocessed for the algorithm without any concern of bytes order. The expected results for flip and invert operations based on different input data are summarized in <u>Table 7</u>.

**SmartDMA Cookbook**

Table 7. Flip and invert operation

| Input data | FEND (bytes order flip) | FBIT (Flip bitwise) | Invert     |

|------------|-------------------------|---------------------|------------|

| 0x01234567 | 0x67452301              | 0xE6A2C480          | 0xFEDCBA98 |

| 0x89ABCDEF | 0xEFCDAB89              | 0xF7B3D591          | 0x76543210 |

The flip and invert can be performed together with immediate load operation. Since <code>E\_LOAD\_IMM</code> only supports loading an 11-bit signed immediate, a 32-bit immediate load must be implemented using either load-then-shift operations, or load-then-invert operations (<code>E\_LOAD\_SIMM</code>, <code>E\_LOAD\_IMMN</code>, <code>E\_LOAD</code>, and <code>SIMMN</code>) plus logical OR operation.

For example, the following sequence loads the 32-bit value 0xFAC68800 into the CFS register.

#### 4.2.5 Flags

MOV, LOAD, and ALU instructions, a bit-slice event, or an external flag match can signal the EZH flag, which drives conditional execution.

The EZH flags can be described in 3 categories:

- ALU flags

- · Algorithmic or branch control flags

- · Boolean or external detection flags

## 4.2.5.1 ALU flags

ALU flags are settable using any opcode which involves an ALU operation, or a MOV operation, or a LOAD immediate value. The various ALU flags, along with their Arm equivalents and purposes, are summarized in Table 8.

Table 8. ALU flags and their purposes

| Flag | Arm equivalent | Purpose                 |

|------|----------------|-------------------------|

| EU   | <none></none>  | Execute Unconditionally |

| ZE   | EQ             | Zero                    |

| РО   | PL/GE          | Positive                |

| NE   | MI             | Negative                |

| AZ   | GT             | Above zero              |

| ZB   | LE             | Zero or below           |

| CA   | cs             | Carry set               |

| NC   | CC             | Carry not set           |

| CZ   | <none></none>  | Carry set and zero      |

The opcodes that are not capable of setting flags include any data bus read or write operations like:

• E PER WRITE

AN14650

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

SmartDMA Cookbook

• E PER READ

#### Also, the following opcodes do not set flags:

- E NOP

- E INT TRIGGER

- E GOTO

- E GOSUB

- E GPO BYTE MODIFY

- E TIGHT LOOP

- E HOLD

- E\_VECTORED\_HOLD

- E HEART RYTHM

- E SYNCH ALL TO BEAT

- E WAIT FOR BEAT

#### Example for ALU flags:

#### Note:

- If the destination is set to the PC, no flags can be set on an ALU transaction.

- When a set-flag ALU opcode is used with the destination as the PC, it requests a scheduled branch to the new value of the PC.

#### 4.2.5.2 Algorithmic or branch control

Algorithmic control and branch control use the same flag opcodes; SPO/UNS(0xa) and SNE/NZS(0x0b).

## 4.2.5.2.1 Algorithmic control

The two algorithmic flags (SPO and SNE) are secondary versions of PO and NE. However, unlike PO and NE, which get set anytime a FLAG-SET instruction is executed, the SPO and SNE flags can only be set under specific conditions. They are updated only if the opcode attempting to set them is executed with a conditional check on SPO or SNE. For example, E COND LSL ORS (SPO, R0, R0, R1, 1)

The two algorithmic flags have the following meaning:

- SPO Shift-only-when-Positive: Perform the extra operation when the top bit is 1.

- SNE Shift-only-when-Negative: Perform the extra operation when the top bit is 0.

The following example demonstrates the behavior between SPO and PO flags:

AN14650

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved

**SmartDMA Cookbook**

The following are the twofold purposes of the algorithmic flags:

- To allow the user to implement a shift-based algorithm (for example, binary multiplication), where a shift always occurs, but an ALU operation is conditionally executed based on the value of the most significant bit (MSB). These flags enable the user to ensure that the shift always takes place, while the other operation can be canceled when not required.

- To allow the user to perform other flag-based operation and later resume the algorithmic shift using the previously saved SPO/SNE flags—as long as the intermediate operations did not affect the algorithmic flags.

Consider the following example of a 16-bit x 16-bit multiplication. The highlighted line presents the core of the multiplication algorithm. In the example below, the core of the algorithm relies on the ability to conditionally perform an add operation when the MSB is high.

```

E_LDR(R0, PC, 7) // R0 load from DCD after result E_LDR(R1, PC, 7) // R1 load from DCD

E_LOAD IMM(R3, 15) // Repeat 15 times after initial iteration

E_ADD_IMM(R4, PC, 2*4) // Define end of iteration loop

E TIGHT LOOP(R4, R3) // Enable loop

E COND LSLS(SPO, RO, RO, 16) // Shift Multiplicand Left by 16

start of loop

E COND LSL ADDS (SPO, RO, R1, RO,1) // Multiply - This will execute 16

// times, shifting or shifting and

// adding depending on Multiplier

end ofloop

E \overline{STR}(PC, R0, 0)

// Write result back on top of first operand

E SUB IMM(PC, PC, 8) // while 1

result

DCD 0x0000abcd

// Multiplicand

// Multiplier

DCD 0x0000ef01

```

#### 4.2.5.2.2 Branch control

Typically, a branch flushes the instructions in the pipeline and immediately updates the program counter (PC). However, with a scheduled branch, the two instructions delay the branch, allowing execution to continue without flushing the pipeline.

The flag NZS (schedule branch when the NZ flag is set) and UNS (unconditionally schedule) are used for the scheduled branch. These flags can only be used for qualifying an E COND GOTO opcode.

In the example below, are R0, R1, R4 pushed to the stack:

```

E_COND_GOTO(UNS, ne2) // Schedule branch unconditionally

E_PUSH(R0) // Executed - Pipeline is not flushed

E_PUSH(R1) // Executed - Pipeline is not flushed

E_PUSH(R2)

ne2

E_GOTO(ne3) // Branch immediately

E_PUSH(R3) // Not executed

ne3

E_PUSH(R4)

```

**SmartDMA Cookbook**

## 4.2.5.2.3 Boolean and external detection flags

EZH allows the user to be able to monitor the state of the external condition input. This provides a way to allow the user to extend the usage of EZH by using a flag that is fed from outside the EZH. The EZH has no architectural support for directly setting or clearing this flag. However, the user can observe the external flag status in any opcode that supports conditional execution. The flags used for this purpose are:

- . EX External flag is set

- · NEX External flag is not set

Both EZH and Arm can write the EZH control register (EZHB CTRL) bit 1 to change the EZH state.

Second, the EZH architecture also allows the user to monitor the value of the Boolean monitoring logic combiner. The available flags are:

- · BS Boolean-expression set

- · NBS Not Boolean-expression set

The benefit of this feature is that it allows the user to perform Boolean monitoring on-the-fly.

There is an important aspect to consider is that if CFM and CFS registers (Boolean detector configuration registers) are being loaded from a literal fetch through the Data bus, the configuration update cannot be immediate. There is no protection mechanism in place to prevent EZH from evaluating opcodes that are conditional on BS or NBS before the configuration of the Boolean detector is fully updated.

This behavior contrasts with <code>E\_VECTORED\_HOLD</code> and <code>E\_HOLD</code>, both of which stall any detection until any outstanding reads into CFM or CFS are complete and data arrives back in the EZH.

These instructions operate by artificially holding the BS flag low as long as updates to CFM or CFS are still pending through the data bus.

Finally, if an <code>E\_HOLD</code> or <code>E\_VECTORED\_HOLD</code> is executed based on BS, there is no guarantee that the BS flag matches the actual evaluation of the <code>E\_HOLD</code> or <code>E\_VECTORED\_HOLD</code> itself. This match is only guaranteed if the inputs to the Boolean detector don't change.

For example, E COND VECTORED HOLD (BS, PC)

If the BS flag is high, in the example above, the instruction executes a vectored hold. At first glance, this appears to allow the code to jump to an active vector only if a known vector is already active. However, the risk lies in timing: if the inputs to the Boolean detector change between the time the instruction is decoded and the time it executes (typically at least one cycle later), the code can jump to a vector that is no longer valid. This can cause the code to stall, waiting for a vector that matched at decode time but has since disappeared.

## 4.2.6 GPIO

The EZH supports a 32-bit direct access to bidirectional GPIO pins, which can be programmed directly through the EZH instructions. This allows faster access as compared to using them through the system AHB bus.

GPIO is controlled through GPO and GPD. The GPI register is a read-only register.

In addition to access these registers through any EZH opcodes, there is also a dedicated opcode called <code>E\_MODIFY\_GPO\_BYTE</code>. This opcode enables simultaneous bit clearing, bit setting, and bit toggling of a mask on 8 bits of GPO in a single cycle.

#### 4.2.7 Heartbeat timer

EZH features a 16-bit down counter known as the heartbeat timer, designed to provide an efficient mechanism for scheduling tasks. It is an automatically reloadable down counter which 'beats' each time it reaches 0. The reloadable value is set using the E\_HEART\_RYTHM opcode. Any use of this opcode changes the reloadable value and updates the maximum value of the counter and starts counting down from it on the following cycle.

SmartDMA Cookbook

By default, the heartbeat count is set to 0, resulting in a 'beat' on every cycle.

Note: When the heartbeat is set to 0, the counter is clock-gated to conserve power.

The heartbeat timer can be used in the following two ways:

- Beat-based halting with E\_WAIT\_FOR\_BEAT: Using the E\_WAIT\_FOR\_BEAT instruction, the user halts execution until the next beat. This is useful for aligning task execution with regular intervals. For example, in a serial sampling, it helps to ensure that sampling occurs at deterministic timing.

- Synchronized execution mode with E\_SYNCH\_ALL\_TO\_BEAT: Alternatively, using the E\_SYNCH\_ALL\_TO\_BEAT instruction switches the EZH in an execution mode, where all instructions are executed only on heartbeat ticks. This provides multiple benefits:

- Power efficiency: As the EZH operates at a slower rate placed by the heartbeat rhythm count, it can save power when full-speed execution is not required. For example, if the EZH can complete tasks faster than needed, controlling execution speed using the heartbeat can help reduce energy consumption.

- Deterministic 'snap-to-grid execution: In this mode, the EZH stalls between beats. During this time, it

fetches and decodes the next instruction and performs any outstanding memory or data transactions. This

enables highly deterministic execution, even if the EZH is running from shared memory with another AHB

controller.

#### 4.2.8 Boolean detection (bit-slice)

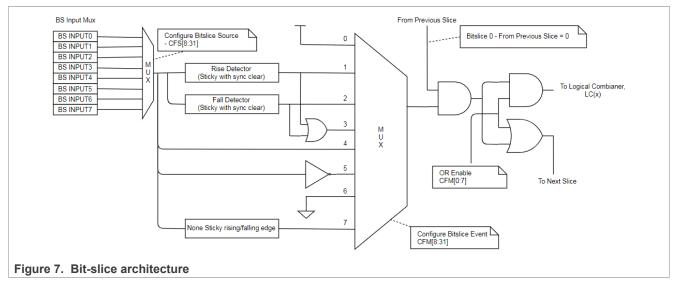

The EZH includes eight Boolean detection engines, known as bit-slice (BS) <u>Figure 7</u> shows the bit-slice architecture.

Before using a bit-slice, BS\_INPUTX must be bound to an EZH trigger using the INPUTMUX of the system. Similar to DMA triggers, the EZH trigger source can be selected from 'GPIO', 'Interrupts', or 'timer match event', depending on the device.

Each bit-slice takes one input signal from the eight available bit-slice inputs (BS\_INPUT0 to BS\_INPUT7). The configuration is set through the CFS register.

- Bits [8:31] of CFS register select the source input for each bit-slice (BS0 to BS7).

- Each bit-slice uses 3 bits for source selection.

- For example: CFS = 0x12345600 defines the mapping of input signals to the bit-slices.

SmartDMA Cookbook

Table 9. CFS configuration for bit-slice input selection

| Bit fields | BS7     | BS6     | BS5     | BS4     | BS3     | BS2     | BS1     | BS0     |

|------------|---------|---------|---------|---------|---------|---------|---------|---------|

| CFS        | 000     | 100     | 100     | 011     | 010     | 001     | 010     | 110     |

| INPUTX     | Input 0 | Input 4 | Input 4 | Input 3 | Input 2 | Input 1 | Input 2 | Input 6 |

Each bit slice can detect the following input events: 'Rising edge', 'falling edge', 'edge', 'high level', or 'low level'. There is also 'sticky' or 'nonsticky' edge detection. Sticky detection modes require the user to clear the sticky flag manually by writing to the CFM register before a new event can be detected. Table 10 defines the meaning of the event mux bits:

Table 10. Example mux bits behavior (from CFM):

| EZH CFM        | Mux output                                                                                                                                                                         |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| event mux bits |                                                                                                                                                                                    |

| 000b           | Mux output is always 1, regardless of the input signal.                                                                                                                            |

| 001b           | Mux outputs 1 when the input signal detects a rising edge. The user must clear the sticky bit manually (any write to the CFM register) for next event detection.                   |

| 010b           | Mux outputs 1 when the input signal detects a falling edge. The user must clear the sticky bit manually (any write to the CFM register) for next event detection.                  |

| 011b           | Mux outputs 1 when the input signal detects either a rising or falling edge. The user must clear the sticky bit manually (any write to the CFM register) for next event detection. |

| 100b           | Mux outputs 1 when the input signal is high.                                                                                                                                       |

| 101b           | Mux outputs 1 when the input signal is low.                                                                                                                                        |

| 110b           | Mux output is always 0, regardless of the input signal.                                                                                                                            |

| 111b           | Mux outputs 1 when the input signal detects either a rising or falling edge.                                                                                                       |

#### Each bit-slice has two outputs:

- One routes to the Logical Combiner (LC) block.

- The other connects to the next bit-slice in the chain.

The OR\_Enable flag controls the output behavior, which corresponds to bits [0:7] of the CFM register, one bit per bit-slice.

**Note:** If OR\_Enable is set for bit-slice 7, the output is routed to the Logical Combiner regardless of its configuration.

All bit-slice outputs are routed to LC, which EZH uses to determine whether the specified condition is met. By implementation, EZH continues to fetch and execute instructions until it encounters a <code>HOLD</code>, <code>VECTOR\_HOLD</code>, or <code>ACC\_VECTORED\_HOLD</code> instruction. Execution halts when the LC output evaluates to 1, according to the logic:

LC0|LC1|LC2|LC3|LC4|LC5|LC6|LC7

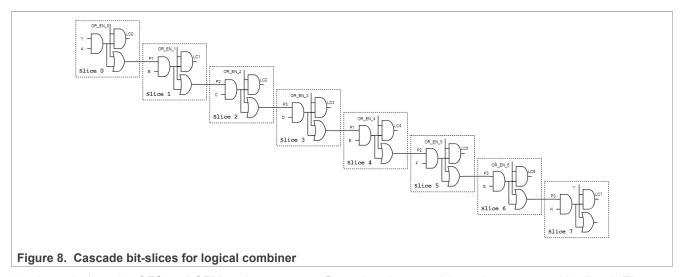

<u>Figure 8</u> illustrates how each bit-slice contributes to the LC. Each bit-slice detects a specific event (for example, BS0 detects event A, BS1 detects event B). LC0, LC1,.....,LC7 represent the outputs from bit-slices to the LC, each controlled by the corresponding OR Enable flag.

SmartDMA Cookbook

As shown below, the CFS and CFM registers are configured to detect a rising edge event on bit-slice 0. The EZH halts execution at  $E\_HOLD$ , waiting for the rising edge to occur on bit-slice 0. Once the event is detected, the EZH resumes execution and proceeds with  $E\_PUSH$  instruction.

```

E_LOAD_IMM(CFS, 0)

E_LOAD_IMM(CFM, 0x101)

...

E_HOLD

E_PUSH(R0)

```

An alternative Boolean detection feature in EZH is the <code>VECTORED\_HOLD</code> instruction. It allows simultaneous monitoring of multiple conditions without executing any instruction until a condition is met. It operates similarly to the <code>HOLD</code> instruction, with the key difference being that <code>VECTORED\_HOLD</code> halts execution until one of the logic OR terms are encountered.

Once an event is detected, EZH jumps to the corresponding vector table entry and begins execution from that address. The vector table contains eight enteries by default, and a pointer to it is passed through a register by the VECTORED\_HOLD opcode. If its output is '1', each bit-slice can call a vector. In cases where multiple bit-slices outputs '1', and their outputs are ANDed. The vector to be executed corresponds to the last bit-slice in the ANDed expression.

For example, If BS0 detects event A and BS1 detects event B, and the logical combiner is monitoring the expression ABC+D+EFGH, the lowest 8 bits in the CFM register (that is, the  $OR\_Enable$  field) must be set accordingly. Take for instance,  $OR\_Enable = 10001100b$  enables only the relevant bit-slice outputs for this condition.

The following code demonstrates how <code>VECTORED\_HOLD</code> can be used to handle an event triggered by the logical combination ABC+D+EFGH. The <code>VECTORED\_HOLD</code> opcode can be interpreted as a combination of 'HOLD + GOTO/GOSUB to vector', similar to how WFI works in Arm. This means that when a vector fires, the EZH can back up the location into its RA register. After the vector handler completes, the EZH code resumes from where it left off.

AN14650

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

SmartDMA Cookbook

```

E NOP // BS4 vector

// BS5_vector

E NOP

// BS6_vector

E NOP

E GOTO(BS7 ISR) // BS7 vector

BS2 ISR

E BSET IMM(CFM, CFM, 2)

E LOAD IMM(R2, 2)

E GOTO (bf)

BS3 ISR

E BSET IMM(CFM, CFM, 3)

E_LOAD_IMM(R2, 3)

E GOTO (bf)

BS7 ISR

E BSET IMM(CFM, CFM, 7)

E^{-}LOAD^{-}IMM(R2, 7)

bī

```

The two instructions that follow <code>E\_VECTORED\_HOLD</code> flush from the pipeline and do not execute, which adds latency to the event handler. <code>E\_ACC\_VECTORED\_HOLD</code> provides an opcode that keeps the instructions after the <code>HOLD</code> operation in the pipeline, so they execute quickly when an event happens.

$E\_ACC\_VECTORED\_HOLD$  takes an event handler vector and a mask that shows which event to accelerate. In the code below, the mask shows that bit-slice (LC2 = 1) is the event to accelerate. When this event occurs, the instructions  $E\_GOTO$  (UNS, label, and  $E\_BTOG\_IMM$  (GPO, GPO, 0) execute. If a different bit-slice event occurs, those two instructions flush from the pipeline and do not execute.

```

label

E_ACC_VECTORED_HOLD(PC,0x04)

E_GOTO(UNS,label)

E_BTOG_IMM(GPO,GPO,0)

...

Vect2

E_BTOG_IMM(GPO,GPO,0)

```

EZH also supports large vector tables. Each entry in these tables includes four instructions instead of just one. The reason for using four instructions is that a scheduled branch followed by two 'unflushed' opcodes usually uses only three instructions. This means that the large vector table entry has enough space for one more instruction, allowing a single cycle branch to the rest of the handler if needed.

See the following samples:

```

Label0

E_ACC_VECTORED HOLD LV(PC,1<<1);</pre>

IMM(GPO, GPO, 18);

//non-flushed instruction 1

E BTOG IMM (GPO, GPO, 18);

//non-flushed instruction 2

//LC1 1<sup>st</sup> opcode

E BTOG IMM(GPO, GPO, 18);

//LC1 2<sup>nd</sup> opcode

E BTOG IMM (GPO, GPO, 18);

3<sup>rd</sup> opcode

E BTOG IMM(GPO, GPO, 18);

//LC1

//LC1 4<sup>th</sup> opcode, go to label1

E GOTO(label1);

Label1

//1st opcode in longer vector

E BTOG IMM(GPO, GPO, 18);

// 2<sup>nd</sup> opcode in longer vector , go to label0

E GOTO(Label0);

```

Note:

**SmartDMA Cookbook**

- E\_ACC\_VECTORED\_HOLD\_LV, E\_ACC\_VECTORED\_HOLD, E\_ VECTORED\_HOLD\_LV, and E\_VECTORED\_HOLD, each set of four instructions takes about six cycles from the moment the trigger occurs to when holding is released.

- · Any write to the CFM and CFS clears the BS flag.

## 4.2.9 Pending trap

EZH supports a pending trap function that can latch the edge of input IO, and does not change the status until the flag is cleared. This bit change acts as a trigger source for bit-slice operations.

#### 4.2.9.1 Use case 1 (EZH pending trap status usage)

This use case helps to detect a logic level change on the pin mux input using the pending trap feature. Follow the steps to configure EZH and monitor the input transactions.

#### Steps:

- 1. Enable EZH.

- 2. Configure the pin mux to EZH.

#### Then

Bits 7-0 in EZHB\_PENDTRAP represent the logic level change of the pin mux input IO. The pending trap uses a latching logic '2' state. This means that bit 7 to 0 changes from '0' to '1' when the input IO logic changes from '0' to '1'. However, they do not change back to '0' until the bit is manually cleared, even if the input IO logic returns to '0'.

#### 4.2.9.2 Use case 2 (EZH pending trap status polarity usage)

This use case demonstrates how to configure the pending trap to detect a falling edge (from high to low) on the pin mux input by setting the polarity bits.

#### Steps:

- 1. Enable EZH.

- 2. Configure the pin mux to EZH.

- 3. Set bits 15-8 (polarity) of the EZHB\_PENDTRAP register to '0xFF'.

## Then:

Bits 7-0 in EZHB\_PENDTRAP represent the opposite logic level change of the pin mux input IO. The pending trap uses a latching logic 0 state. This means bit 7 to 0 changes from '0' to '1' when the input IO logic changes from '1' to '0'. However, they do not change back to '0' until the bit is manually cleared, even if the input IO logic returns to '0'.

#### 4.2.9.3 Use case 3 (EZH slice vector usage)

This use case explains how to configure the pending trap to trigger a slice vector-using software.

#### Steps:

- 1. Enable EZH.

- 2. Configure the pin mux to EZH.

- 3. Enable the pending trap by setting bit 23-18 in EZHB PENDTRAP to '0xFF'.

- 4. Enable the EZH interrupt.

#### Then:

AN14650 All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

**SmartDMA Cookbook**

Set the CFS and CFM registers for bit-slice functionality. When bit 7-0 in EZHB\_PENDTRAP changes from '0' to '1', it causes the slice states to match and trigger the slice vector. Under this condition, the actual IO level or edge is no longer recognized by the bit-slice. Therefore, bit 7-0 can be modified manually to trigger slice actions through software.

Table 11. Bit-slice state mapping

| Logic of bit 7-0 in EZHB_PENDTRAP | Present states to bit-slice |

|-----------------------------------|-----------------------------|

| '0'                               | Low level                   |

| '1'                               | High level                  |

| From '0' to '1'                   | Rising edge                 |

| From '1' to '0'                   | Falling edge                |

## 4.2.10 Tight loop

The EZH offers an additional branching mechanism that introduces no overhead cycles during the branch itself. This is known as the tight loop mechanism. In a traditional CPU loop, execution typically follows a decrement-compare-branch approach. That is, the loop counter (iterator) is decremented until it reaches 0, and a comparison opcode checks whether the loop can continue or exit. Once the condition is met, the branch is taken. With a tight loop, however, the EZH hardware manages the loop control internally, reducing software overhead, and improving efficiency.

The examples below show two implementations for toggling PIO\_0 sixteen times, using either the traditional decrement-compare-branch or tight loop.

Example 1: Toggle a PIO using a decrement-compare-branch mechanism.

```

E_BSET_IMM(GPO, GPO, 0) // Set PIO_0 value high

E_BSET_IMM(GPD, GPD, 0) // Set PIO_0 direction output

E_LOAD_IMM(R0, 16) // Set loop counter 16

start

E_BTOG_IMM(GPO, GPO, 0) // Toggle PIO_0

E_SUB_IMMS(R0, R0, 1) // R0 = R0 - 1

E_COND_GOTO(NZ, start) // Jump to start if non-zero flag

```

#### Example 2: Toggle a PIO using a tight loop mechanism.

Notes on tight loop usage:

- Reusable register: The registers used for tight loop setup can be reused within the loop body. For example, in the case above, R0 and R1 are used to set up a tight loop using E\_TIGHT\_LOOP (R1, R0). R0 and R1 can be rewritten without affecting loop execution.

- First instruction behavior: The instruction immediately following E\_TIGHT\_LOOP executes only once during the initial loop entry.

**SmartDMA Cookbook**

• Execution count: TIGHT LOOP executes for (1 + loop counter) times.

Performance note:

The code is designed to fetch data from SRAM (with R0 points to the memory address where data is stored). It can convert the endianness of the data, and write it to an APB peripheral register. The codeon the left uses DFETCH, executing four consecutive loads into R2, R3, R4, and R5. This approach allows EZH to operate without stalling. In contrast, the code on the right is less efficient. As R2, R3, R4, and R5 are used immediately for endianness conversion (FEND opcode) right after the load instruction, EZH must be stalled to avoid conflicts.

#### 4.2.11 Stack support and return address

The EZH contains a stack pointer (SP) register, which the user manages manually. Inherently, the hardware itself does perform automatic stack management. The software must perform any operations such as pushing or popping. The  $E\_PUSH$  and  $E\_POP$  opcodes act as wrappers for  $E\_LDR$  and  $E\_STR$  instructions. These opcodes hardcode the pointer register as SP and currently enforce an upward growing stack. However, if required, the macro definition for  $E\_PUSH$  and  $E\_POP$  can be changed in the future to allow downward stack growth.

EZH ia able to automatically back up the return address (RA)—the location from which a branch was made. If the user wants to back this return address onto the stack, the user must use the  $E_PUSH$  and  $E_POP$  opcodes.

Furthermore, by default, only <code>E\_VECTORED\_HOLD</code> and <code>E\_GOSUB</code> automatically back-up the return address into the RA register. <code>E\_VECTORED\_HOLD</code> can be configured to skip this behavior using NRA (no return address) option.

In the case of  $E\_GOSUB$ , the RA register is always overwritten, so users must explicitly preserve it if needed by stacking. With  $E\_GOTO$ , the 'L' option indicates that the return address must be saved into the RA register.

The following example demonstrates how the RA register behaves during an EZH function call using E GOSUB:

```

E_LOAD_IMM(R0, 0xDD) // R0 = 0xDD

E_GOSUB (func1) // Call sub routine func1, return address in RA

endfc

E_GOSUB(endfc) // End loop

func1

...

E_PUSH(RA) // RA stack must be preserved by user

E_GOSUB(func2) // Call sub routine func2, return address in RA

E_POP(RA) // Recover RA

E_GOTO_REG(RA) // Return to func1_caller

func2

...

E_GOTO_REG(RA) // Return to func2_caller

```

**SmartDMA Cookbook**

#### 4.2.12 Breakpoint support

The EZH supports a debug mechanism called 'Breakpoint' support. It works by providing the EZH with an address where a break must occur and the corresponding service code resides.

EZH replaces the instruction EZHB\_BREAK\_ADDR with a branch to the breakpoint vector address EZHB\_BREAK\_VECT. If the opcode is flushed, the breakpoint has no effect. It only takes effect when the opcode is about to be executed, as expected for a breakpoint.

The opcode, which is set to EZHB\_BREAK\_ADDR, cannot be executed because EZHB\_BREAK\_VECT is executed instead, unless EZHB\_BREAK\_ADDR is reset. Therefore, it is a good practice to set EZHB\_BREAK\_ADDR to an E NOP opcode, so that the breakpoint does not impact the program logic.

The following examples demonstrate how to use the EZH breakpoint. EZHB\_BREAK\_ADDR is set to an E\_NOP operation placed after E\_PUSH (R0). EZHB\_BREAK\_VECT is set to the start of the EZH\_RegistersDump routine, which serves as a debug handler. In the example, the registers, R4, R5, R6, and R7 are pushed onto the stack so their values can be viewed in the IDE. The debug routine then returns to the regular proh=gram by jumping to EZH BREAKADDR + 4, the address of the operation just after EZHB BREAK ADDR is executed.

```

asm void EZH CODE EZH SetRegisters(void)

E NOP

PER READ (R6, EZH ARM2EZH)

E LSR(R6, R6, 2)

E LSL(R6, R6, 2)

E LDR(SP, R6, 0)

E_LOAD IMM(R0, 0xC0)

E LOAD IMM(R1, 0xC1)

E_LOAD_IMM(R2, 0xC2)

E_LOAD_IMM(R3, 0xC3)

E_LOAD_IMM(R4, 0xC4)

E_LOAD_IMM(R5, 0xC5)

E LOAD IMM (R6, 0xC6)

E LOAD IMM (R7, 0xC7)

E PUSH (R0)

E NOP

// Breakpoint Address

E PUSH(R1)

E PUSH(R2)

E_PUSH(R3)

E INT TRIGGER (0)

E GOTO (end9)

```

**Note:** Avoid placing breakpoints at locations where a scheduled branch is happening. While the breakpoint functions technically, it can make it difficult for the user to trace and reconstruct the execution of the program flow accurately.

**SmartDMA Cookbook**

#### 4.2.13 Error and emergency mode

EZH supports an emergency mode designed to allow controlled shutdown of the system in response to an external emergency event or an AHB error response.

The mechanism works by the system providing the EZH with an emergency vector location. When the emergency input of the EZH goes high or an error is detected on either of the AHB buses, the program branches at the next possible instruction cycle to the emergency vector location.

It is important to note that emergency mode does not set any restrictions in terms of what can or cannot be executed. However, after emergency mode is entered, it cannot be left without resetting the EZH—either pulling the ignition line low or resetting the block. This also means that subsequent assertions of emergency or AHB error have no effect after emergency mode is already entered.

### 4.2.14 Arm or EZH interrupt

EZH can raise interrupts to the Arm processor through three different mechanisms. The Arm core can then handle these interrupts within the EZH (SmartDMA) debug routine.

- E\_INT\_TRIGGER instruction: This instruction takes one parameter, which must be any positive number greater than 0. E INT TRIGGER is one of the only opcodes that cannot be used with a condition flag.

- Handshake through EZHB\_EZH2ARM and EZHB\_ARM2EZH registers: When the EZHB\_ARM2EZH register has bit [1:0] = 0b10, any write to the EZHB EZH2ARM register can trigger an interrupt to the Arm core.

- Hijack function: EZH provides an interrupt output bus of 32 bits(or fewer than 32 outputs on some platforms), which allow EZH to emulate different peripheral toward the Cortex-M CPU. The value passed into <code>E\_INT\_TRIGGER</code> is interpreted as an interrupt bus signal to the Arm. Each bitmaps to one of the interrupts to hijack. To hijack the third interrupt, the code can be written as: <code>E\_INT\_TRIGGER(1<<3)</code>.

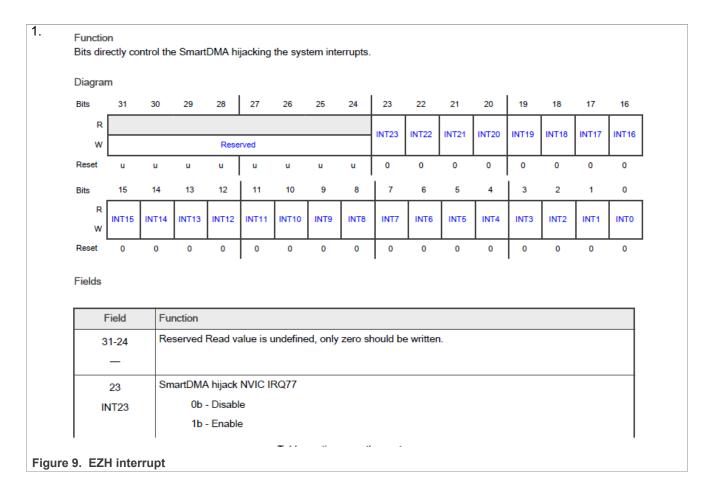

Separately, EZH also has its own interrupt slot in the NVIC, which is an OR of all bits passed into <code>E\_INT\_TRIGGER</code>. To implement this interrupt, the hijack function must be enabled in the SYSCON registers as shown in <a href="Figure 9">Figure 9</a>:

SmartDMA Cookbook

#### 4.2.15 Scheduled branch

Scheduled branching enables controlled program flow changes using either direct PC based offset jumps or label-based jump tables with predefined offsets.

#### 4.2.15.1 One method

An ALU operation where the destination register is PC can be used to implement a scheduled branch. This is possible only if the user sets the necessary flags:

For example:

```

E_ADD_IMMS(PC,PC,8) // perform a scheduled branch to a location 2 words ahead

```

**Note:** As the PC is always two instructions ahead, this results in branching four instructions ahead of the current one.

#### 4.2.15.2 Another method

Use PC based branching to implement a jump-label function:

1. Define the label offset.

AN14650

All information provided in this document is subject to legal disclaimers.

© 2025 NXP B.V. All rights reserved.

**SmartDMA Cookbook**

```

#define offset_VSYNC 1 //label 1

macro definition #define offset_pixel 2 //label 2

macro definition #define offset_end 3 //label 3

macro definition #define offset_VSYNC_fall 4//label 4

macro definition

```

2. Store the label addresses in the R7.

3. Implement the label code.

```

E_LABEL("start");

...

E_LABEL("VSYNC");

...

E_LABEL("VSYNC_F");

...

E_LABEL("pixel");

...

E_LABEL("end");

...

```

#### 4. Perform a jump-label.

Conditional scheduled jump:

```

E_MOVS(R0,R1);

E_COND_LDR(AZ,PC,R7,offset_start); // if R0 above zero, jump to start

```

Unconditional scheduled jump:

### 5 Instruction set

The following section outlines the EZH instruction set. The Section 5 provides a summary of the instructions:

Table 12. EZH instruction set summary

| No | Instruction set                | Function                                                                | Performance  |

|----|--------------------------------|-------------------------------------------------------------------------|--------------|