# AN11663 CBTL08GP053 Programmer's Guide Rev. 1 — 18 June 2015

**Application note**

#### **Document information**

| Info     | Content                                                                                                                                              |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords | USB Type-C, multiplexer, switch, USB 3.1, DP 1.3, DP++, PCIe 3.0, I <sup>2</sup> C                                                                   |

| Abstract | This document describes the application use cases and I <sup>2</sup> C programming of the CBTL08GP053 crossbar switch device for USB Type-C systems. |

#### **CBTL08GP053 Programmer's Guide**

#### **Revision history**

| Rev | Date     | Description     |

|-----|----------|-----------------|

| 1   | 20150618 | Initial release |

#### **Contact information**

For more information, please visit: <a href="http://www.nxp.com">http://www.nxp.com</a>

#### **CBTL08GP053 Programmer's Guide**

#### 1. Introduction

The CBTL08GP053 is a high performance integrated circuit (IC) capable of switching high-speed differential signals in a variety of USB Type-C systems. The CBTL08GP053 device allows a variety of system side signals to interface with USB Type-C connectors, including:

- USB 3.1

- · DisplayPort 1.3 and DP++

- PCle 3.0

- Differential AUX or single-ended signals (UART, I<sup>2</sup>C, etc.)

The CBTL08GP053 is controllable via an I<sup>2</sup>C interface and can be used with downward facing ports (DFP) or upward facing ports (UFP) in laptop and desktop PCs, tablets, smartphones, display monitors, and other peripherals or accessories containing a USB Type-C connector. All of the functionality is available in a low power and space-saving VFBGA package. Please refer to CBTL08GP053 datasheet [1] for more details.

#### 2. CBTL08GP053 description

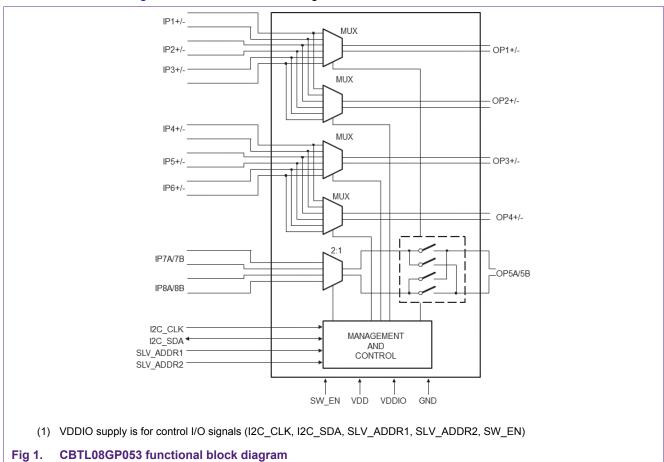

Fig 1 is the functional block diagram of the CBTL08GP053.

ANI11663

#### CBTL08GP053 Programmer's Guide

The CBTL08GP053 contains four high-speed 3:1 multiplexers to support bidirectional high-speed differential signaling up to 8 GHz. There is also a single 2:1 multiplexer with a full crossbar switch to support bidirectional differential and single-ended signals up to 750 MHz. Typically OP1 to OP5 are connected to the USB Type-C connector while IP1 to IP8 along with the I²C-bus signals (I2C\_CLK, I2C\_SDA) are connected to the local system.

#### 2.1 I<sup>2</sup>C Interface

CBTL08GP053 supports a maximum of four I<sup>2</sup>C-bus slave address options. The 7-bit address is selected through the SLV\_ADDR1 and SLV\_ADDR2 pins. <u>Table 1</u> shows the different I<sup>2</sup>C-bus device address options based on pin values.

Table 1. CBTL08GP053 slave addresses

| SLV_ADDR2 | SLV_ADDR1 | l <sup>2</sup> C-bus device address<br>(write/read) |

|-----------|-----------|-----------------------------------------------------|

| LOW       | LOW       | 0x60/0x61                                           |

| LOW       | HIGH      | 0x64/0x65                                           |

| HIGH      | LOW       | 0x68/0x69                                           |

| HIGH      | HIGH      | 0x6C/0x6D                                           |

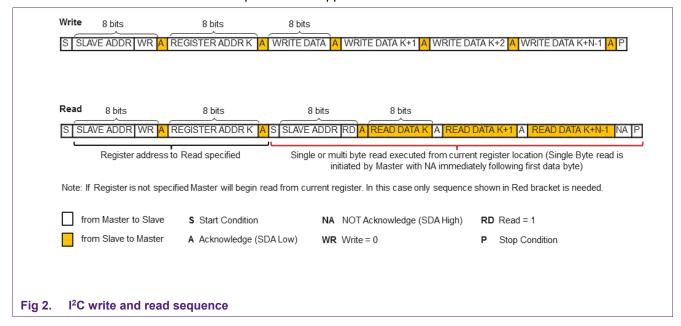

CBTL08GP053 supports data transfers at both Standard-mode (100 kHz) and Fast-mode (400 kHz) clock rates as defined in the I<sup>2</sup>C-bus specification (see <u>UM10204</u>). An example of a typical I<sup>2</sup>C write and read sequence is shown in <u>Fig 2</u>. Please refer to CBTL08GP053 datasheet for complete list of supported I<sup>2</sup>C-bus transactions.

#### 2.2 Operating modes

The register map for CBTL08GP053 is presented in <u>Table 2</u>. After power up, the default register values initialize the device in a lower power standby mode where all signal pathways are not connected (Hi-Z state). I<sup>2</sup>C write commands are then required to put

#### **CBTL08GP053 Programmer's Guide**

the device into active mode operation with a valid switch configuration for a specific customer application scenario.

Table 2. CBTL08GP053 Register Map

'R'- Read only register, 'W'-Write only register, 'RW' - Read/Write register

| Address<br>Offset | Register Name | Access | Default POR<br>Value | Bit[7]    | Bit[6] | Bit[5] | Bit[4]  | Bit[3]  | Bit[2]  | Bit[1]  | Bit[0]  |

|-------------------|---------------|--------|----------------------|-----------|--------|--------|---------|---------|---------|---------|---------|

| 0x01              | SYS_CTRL      | RW     | 0x00                 | SWITCH_EN |        |        |         |         |         |         |         |

| 0x02              | OP1_CTRL      | RW     | 0x00                 |           |        |        |         |         | IP3     | IP2     | IP1     |

| 0x03              | OP2_CTRL      | RW     | 0x00                 |           |        |        |         |         | IP3     | IP2     | IP1     |

| 0x04              | OP3_CTRL      | RW     | 0x00                 |           |        | IP6    | IP5     | IP4     |         |         |         |

| 0x05              | OP4_CTRL      | RW     | 0x00                 |           |        | IP6    | IP5     | IP4     |         |         |         |

| 0x06              | OP5_CTRL      | RW     | 0x00                 | IP8       | IP7    |        |         |         |         |         |         |

| 0x07              | CROSS5_CTRL   | RW     | 0x01                 |           |        |        |         |         |         | CROSS   | PASS    |

| 0x08              | SW_CTRL       | W      | 0x00                 |           |        | X5_SET | OP5_SET | OP4_SET | OP3_SET | OP2_SET | OP1_SET |

| 0x09              | REVISION      | R      | 0xA0                 |           |        |        | REVISIO | N ID    |         |         |         |

| 0x0A to<br>0xFF   | Reserved      | -      | -                    | RESERVED  |        |        |         |         |         |         |         |

<sup>[1]</sup> Reserved bit fields are shaded. Reads will be zeros and writes do not have any effect.

CBTL08GP053 active mode operation requires that both the SW\_EN pin be set to logical "high" voltage level and the SWITCH\_EN bit (SYS\_CTRL[7]) set to '1'. Subsequent changes to either the SW\_EN pin or the SWITCH\_EN bit will return the device to standby condition but the remaining register contents will remain unchanged. Please refer to CBTL08GP053 datasheet for start-up time (tstartup) characteristics when switching between standby and active modes of operation.

During active mode operation the customer application may want to change the switch configuration using an  $I^2C$  write command to the SW\_CTRL register. A reconfiguration time interval ( $t_{rcfg}$ ) from the final  $I^2C$  clock bit is required before the switch starts operating with the new settings.

**Note:** Usually OP1\_CTRL, OP2\_CTRL, OP3\_CTRL, OP4\_CTRL, OP5\_CTRL, and CROSS5\_CTRL should be preloaded with required and valid settings before writing to SW CTRL.

**CBTL08GP053 Programmer's Guide**

#### 3. Application Use Cases: DisplayPort Alt Mode for USB Type-C

CBTL08GP053 is ideally suited for applications where a variety of different high-speed signals have to be routed over a single connector. One major application example is using DisplayPort as an Alternate Mode for USB Type-C connectors. This specification [2] defines the connectivity between the USB Type-C receptacle pinout and DisplayPort (DP) high-speed signals along with the number of lanes and signaling rates for various scenarios. The DP Alt Mode standard also specifies the pin configurations for both downward facing ports (DFP) and upward facing ports (UFP). DFP are typically found in host systems such as laptop/desktop PCs and tablets while UFP are located in peripheral systems such as display monitors and docks. Please contact NXP for examples of application reference designs for both DFP and UFP Type-C systems.

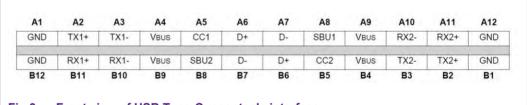

Fig 3 shows the front view of a DFP or UFP USB Type-C receptacle. There are four high-speed differential pairs (TX1+/-, TX2+/-, RX1+/-, RX2+/-) that support DP 1.3 data signaling rates. In addition SBU1 and SBU2 are lower bandwidth pathways that can be used for DP AUX signaling. USB 2.0 traffic is carried by the D+/- signals while the remaining signals (VBUS, CC1, CC2, GND) must support and be compatible with the USB Power Delivery (PD) specification [3] and Universal Serial Bus Type-C Cable and Connector Specification [4].

Fig 3. Front view of USB Type-C receptacle interface

<u>Table 3</u> lists the DP Alt Mode usage cases supported by the CBTL08GP053. Please refer to DP Alt Mode specification [2] and the CBTL08GP053 datasheet for more details.

Table 3. CBTL08GP053 for DisplayPort Alt Mode

| DP Alt Mode Pin Assignment   | USB type-C plug orientation | Number of DisplayPort lanes | USB 3.x<br>SuperSpeed |

|------------------------------|-----------------------------|-----------------------------|-----------------------|

| DFP pin Assignment C (and E) | Normal                      | 4                           | -                     |

| и                            | Flipped                     | 4                           | -                     |

| DFP pin Assignment D (and F) | Normal                      | 2                           | Active                |

| и                            | Flipped                     | 2                           | Active                |

| UFP pin Assignment C         | Normal                      | 4                           | -                     |

| и                            | Flipped                     | 4                           | -                     |

| UFP pin Assignment D         | Normal                      | 2                           | Active                |

| и                            | Flipped                     | 2                           | Active                |

| UFP pin Assignment E         | Normal                      | 4                           | -                     |

| и                            | Flipped                     | 4                           | -                     |

#### **CBTL08GP053 Programmer's Guide**

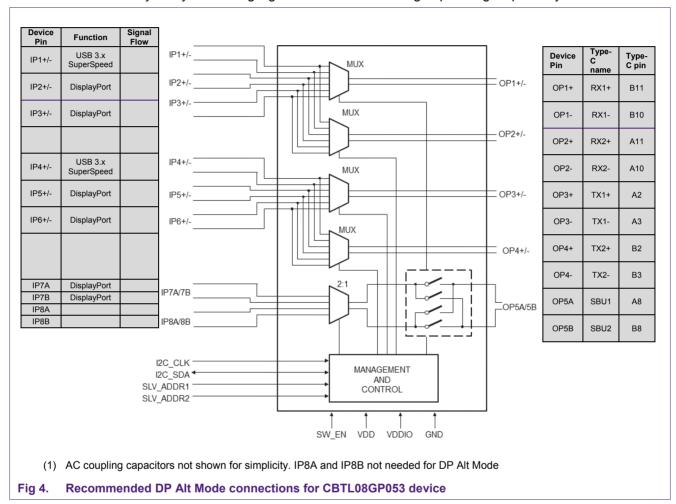

The CBTL08GP053 is a versatile high performance switch that can be used in a variety of configurations and applications. A recommended connection to support most DP Alt Mode usage cases is presented in Fig 4. The described interface between a USB Type-C receptacle and CBTL08GP053 is valid for both DFP and UFP applications. The recommended pinout maintains good signal integrity in the printed circuit board (PCB) layout by minimizing signal transitions for the high-speed signal pathways.

The various DP Alt Mode usage cases will be shown in the following sections with the associated CBTL08GP053 register maps and signal flow direction based on the above implementation. If a different connectivity is used the software and firmware should adjust the CBTL08GP053 settings accordingly. Please refer to CBTL08GP053 datasheet for more information.

#### **CBTL08GP053 Programmer's Guide**

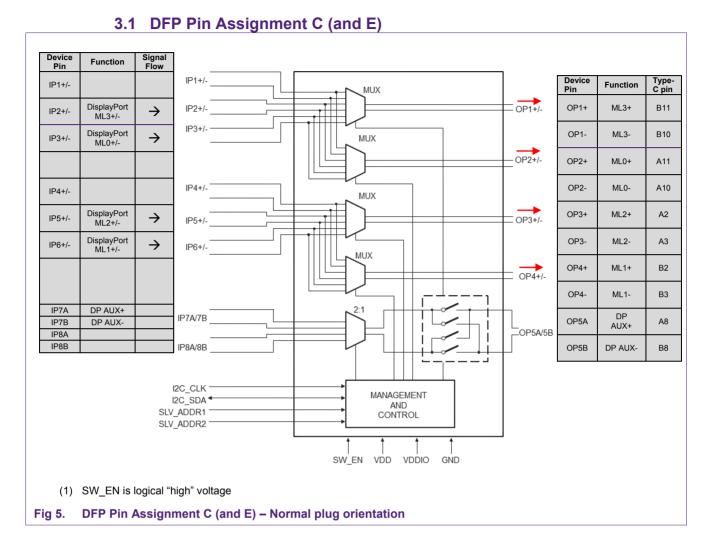

Table 4. Register Map: DFP Pin Assignment C (and E) – Normal plug orientation Reserved bit fields are shaded. Reads will be zeros and writes do not have any effect

| Address<br>Offset | Register Name | Access | Hex Value | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-------------------|---------------|--------|-----------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x01              | SYS_CTRL      | RW     | 0x80      | 1      |        |        |        |        |        |        |        |

| 0x02              | OP1_CTRL      | RW     | 0x02      |        |        |        |        |        | 0      | 1      | 0      |

| 0x03              | OP2_CTRL      | RW     | 0x04      |        |        |        |        |        | 1      | 0      | 0      |

| 0x04              | OP3_CTRL      | RW     | 0x10      |        |        | 0      | 1      | 0      |        |        |        |

| 0x05              | OP4_CTRL      | RW     | 0x20      |        |        | 1      | 0      | 0      |        |        |        |

| 0x06              | OP5_CTRL      | RW     | 0x40      | 0      | 1      |        |        |        |        |        |        |

| 0x07              | CROSS5_CTRL   | RW     | 0x01      |        |        |        |        |        |        | 0      | 1      |

| 0x08              | SW_CTRL       | W      | 0x3F      |        |        | 1      | 1      | 1      | 1      | 1      | 1      |

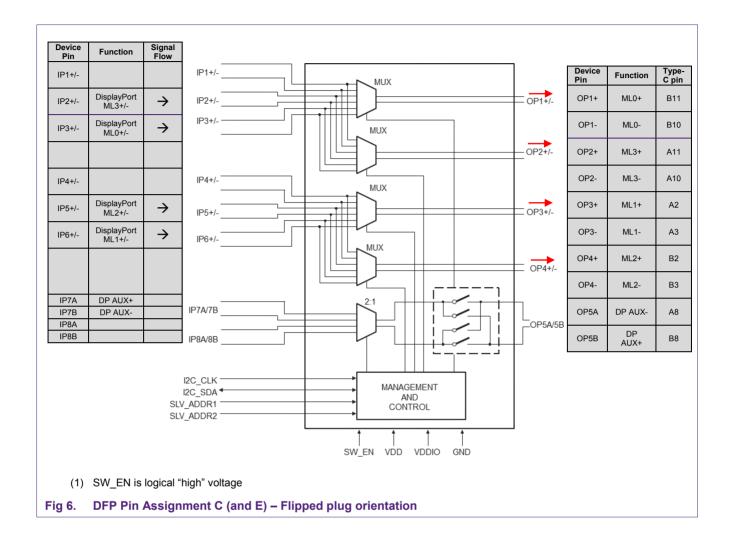

Table 5. Register Map: DFP Pin Assignment C (and E) – Flipped plug orientation Reserved bit fields are shaded. Reads will be zeros and writes do not have any effect

| Address<br>Offset | Register Name | Access | Hex Value | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-------------------|---------------|--------|-----------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x01              | SYS_CTRL      | RW     | 0x80      | 1      |        |        |        |        |        |        |        |

| 0x02              | OP1_CTRL      | RW     | 0x04      |        |        |        |        |        | 1      | 0      | 0      |

| 0x03              | OP2_CTRL      | RW     | 0x02      |        |        |        |        |        | 0      | 1      | 0      |

| 0x04              | OP3_CTRL      | RW     | 0x20      |        |        | 1      | 0      | 0      |        |        |        |

| 0x05              | OP4_CTRL      | RW     | 0x10      |        |        | 0      | 1      | 0      |        |        |        |

| 0x06              | OP5_CTRL      | RW     | 0x40      | 0      | 1      |        |        |        |        |        |        |

| 0x07              | CROSS5_CTRL   | RW     | 0x02      |        |        |        |        |        |        | 1      | 0      |

| 0x08              | SW_CTRL       | W      | 0x3F      |        |        | 1      | 1      | 1      | 1      | 1      | 1      |

#### **CBTL08GP053 Programmer's Guide**

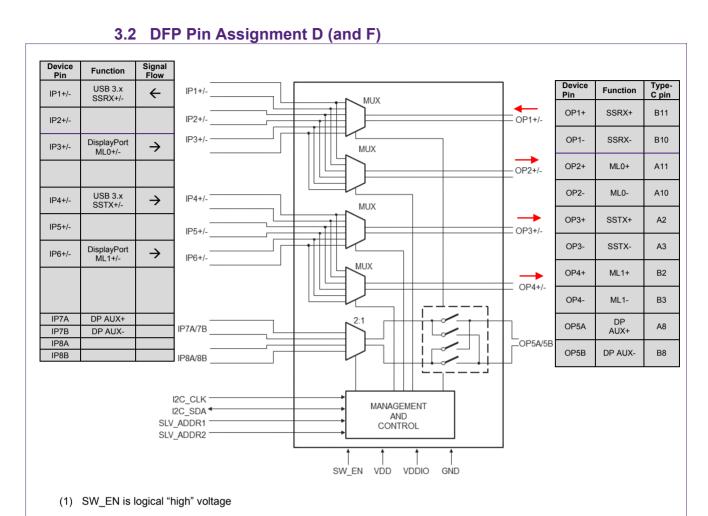

# Fig 7. DFP Pin Assignment D (and F) – Normal plug orientation

Table 6. Register Map: DFP Pin Assignment D (and F) – Normal plug orientation Reserved bit fields are shaded. Reads will be zeros and writes do not have any effect

| Address<br>Offset | Register Name | Access | Hex Value | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-------------------|---------------|--------|-----------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x01              | SYS_CTRL      | RW     | 0x80      | 1      |        |        |        |        |        |        |        |

| 0x02              | OP1_CTRL      | RW     | 0x01      |        |        |        |        |        | 0      | 0      | 1      |

| 0x03              | OP2_CTRL      | RW     | 0x04      |        |        |        |        |        | 1      | 0      | 0      |

| 0x04              | OP3_CTRL      | RW     | 0x08      |        |        | 0      | 0      | 1      |        |        |        |

| 0x05              | OP4_CTRL      | RW     | 0x20      |        |        | 1      | 0      | 0      |        |        |        |

| 0x06              | OP5_CTRL      | RW     | 0x40      | 0      | 1      |        |        |        |        |        |        |

| 0x07              | CROSS5_CTRL   | RW     | 0x01      |        |        |        |        |        |        | 0      | 1      |

| 0x08              | SW_CTRL       | W      | 0x3F      |        |        | 1      | 1      | 1      | 1      | 1      | 1      |

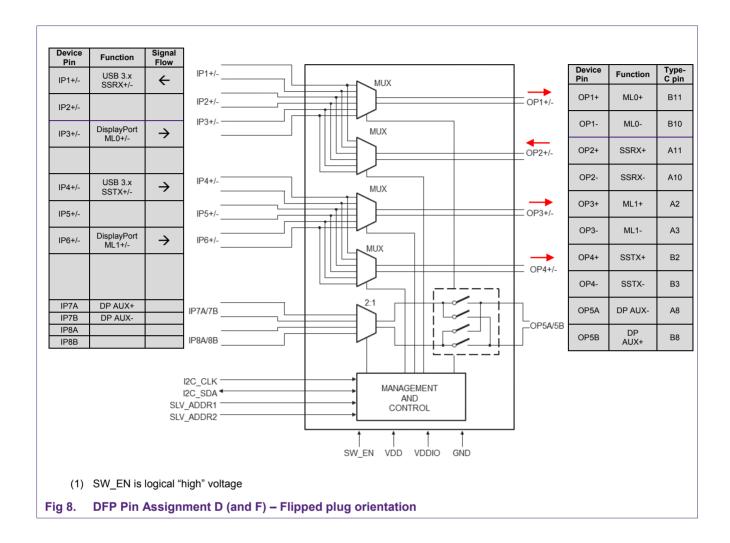

Table 7. Register Map: DFP Pin Assignment D (and F) – Flipped plug orientation Reserved bit fields are shaded. Reads will be zeros and writes do not have any effect

| Address<br>Offset | Register Name | Access | Hex Value | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-------------------|---------------|--------|-----------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x01              | SYS_CTRL      | RW     | 0x80      | 1      |        |        |        |        |        |        |        |

| 0x02              | OP1_CTRL      | RW     | 0x04      |        |        |        |        |        | 1      | 0      | 0      |

| 0x03              | OP2_CTRL      | RW     | 0x01      |        |        |        |        |        | 0      | 0      | 1      |

| 0x04              | OP3_CTRL      | RW     | 0x20      |        |        | 1      | 0      | 0      |        |        |        |

| 0x05              | OP4_CTRL      | RW     | 0x08      |        |        | 0      | 0      | 1      |        |        |        |

| 0x06              | OP5_CTRL      | RW     | 0x40      | 0      | 1      |        |        |        |        |        |        |

| 0x07              | CROSS5_CTRL   | RW     | 0x02      |        |        |        |        |        |        | 1      | 0      |

| 0x08              | SW_CTRL       | W      | 0x3F      |        |        | 1      | 1      | 1      | 1      | 1      | 1      |

#### **CBTL08GP053 Programmer's Guide**

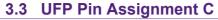

Table 8. Register Map: UFP Pin Assignment C – Normal plug orientation

Reserved bit fields are shaded. Reads will be zeros and writes do not have any effect

| Address<br>Offset | Register Name | Access | Hex Value | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-------------------|---------------|--------|-----------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x01              | SYS_CTRL      | RW     | 0x80      | 1      |        |        |        |        |        |        |        |

| 0x02              | OP1_CTRL      | RW     | 0x02      |        |        |        |        |        | 0      | 1      | 0      |

| 0x03              | OP2_CTRL      | RW     | 0x04      |        |        |        |        |        | 1      | 0      | 0      |

| 0x04              | OP3_CTRL      | RW     | 0x10      |        |        | 0      | 1      | 0      |        |        |        |

| 0x05              | OP4_CTRL      | RW     | 0x20      |        |        | 1      | 0      | 0      |        |        |        |

| 0x06              | OP5_CTRL      | RW     | 0x40      | 0      | 1      |        |        |        |        |        |        |

| 0x07              | CROSS5_CTRL   | RW     | 0x01      |        |        |        |        |        |        | 0      | 1      |

| 0x08              | SW_CTRL       | W      | 0x3F      |        |        | 1      | 1      | 1      | 1      | 1      | 1      |

AN11663 **NXP Semiconductors**

#### CBTL08GP053 Programmer's Guide

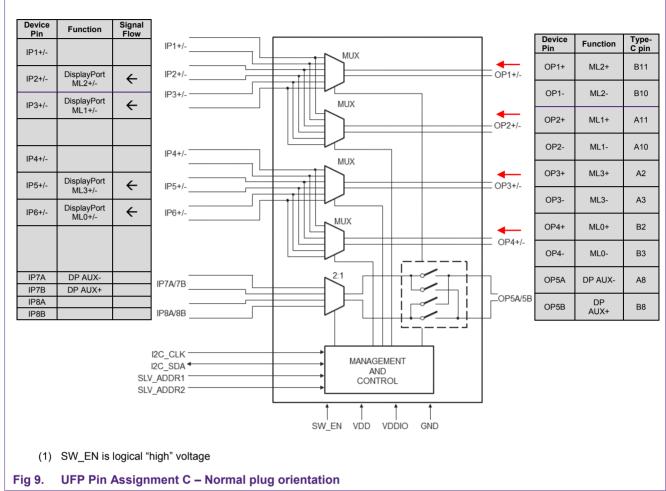

Table 9. Register Map: UFP Pin Assignment C - Flipped plug orientation

Reserved bit fields are shaded. Reads will be zeros and writes do not have any effect

| Address<br>Offset | Register Name | Access | Hex Value | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-------------------|---------------|--------|-----------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x01              | SYS_CTRL      | RW     | 0x80      | 1      |        |        |        |        |        |        |        |

| 0x02              | OP1_CTRL      | RW     | 0x04      |        |        |        |        |        | 1      | 0      | 0      |

| 0x03              | OP2_CTRL      | RW     | 0x02      |        |        |        |        |        | 0      | 1      | 0      |

| 0x04              | OP3_CTRL      | RW     | 0x20      |        |        | 1      | 0      | 0      |        |        |        |

| 0x05              | OP4_CTRL      | RW     | 0x10      |        |        | 0      | 1      | 0      |        |        |        |

| 0x06              | OP5_CTRL      | RW     | 0x40      | 0      | 1      |        |        |        |        |        |        |

| 0x07              | CROSS5_CTRL   | RW     | 0x02      |        |        |        |        |        |        | 1      | 0      |

| 80x0              | SW_CTRL       | W      | 0x3F      |        |        | 1      | 1      | 1      | 1      | 1      | 1      |

#### **CBTL08GP053 Programmer's Guide**

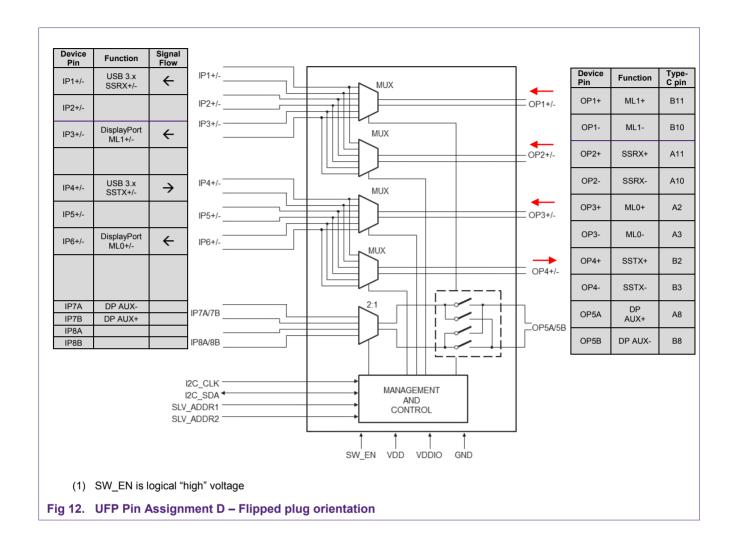

3.4 UFP Pin Assignment D

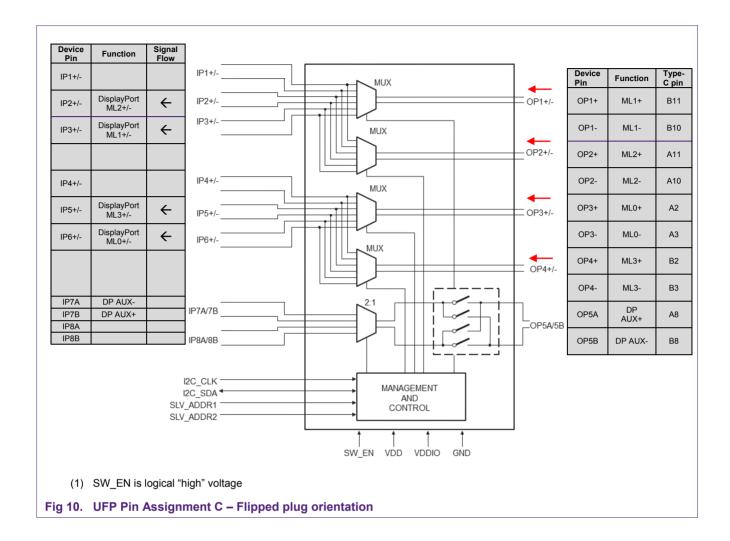

Table 10. Register Map: UFP Pin Assignment D – Normal plug orientation

Reserved bit fields are shaded. Reads will be zeros and writes do not have any effect

| Address<br>Offset | Register Name | Access | Hex Value | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-------------------|---------------|--------|-----------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x01              | SYS_CTRL      | RW     | 0x80      | 1      |        |        |        |        |        |        |        |

| 0x02              | OP1_CTRL      | RW     | 0x01      |        |        |        |        |        | 0      | 0      | 1      |

| 0x03              | OP2_CTRL      | RW     | 0x04      |        |        |        |        |        | 1      | 0      | 0      |

| 0x04              | OP3_CTRL      | RW     | 0x08      |        |        | 0      | 0      | 1      |        |        |        |

| 0x05              | OP4_CTRL      | RW     | 0x20      |        |        | 1      | 0      | 0      |        |        |        |

| 0x06              | OP5_CTRL      | RW     | 0x40      | 0      | 1      |        |        |        |        |        |        |

| 0x07              | CROSS5_CTRL   | RW     | 0x01      |        |        |        |        |        |        | 0      | 1      |

| 80x0              | SW_CTRL       | W      | 0x3F      |        |        | 1      | 1      | 1      | 1      | 1      | 1      |

Table 11. Register Map: UFP Pin Assignment D – Flipped plug orientation Reserved bit fields are shaded. Reads will be zeros and writes do not have any effect

| Address<br>Offset | Register Name | Access | Hex Value | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-------------------|---------------|--------|-----------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x01              | SYS_CTRL      | RW     | 0x80      | 1      |        |        |        |        |        |        |        |

| 0x02              | OP1_CTRL      | RW     | 0x04      |        |        |        |        |        | 1      | 0      | 0      |

| 0x03              | OP2_CTRL      | RW     | 0x01      |        |        |        |        |        | 0      | 0      | 1      |

| 0x04              | OP3_CTRL      | RW     | 0x20      |        |        | 1      | 0      | 0      |        |        |        |

| 0x05              | OP4_CTRL      | RW     | 0x08      |        |        | 0      | 0      | 1      |        |        |        |

| 0x06              | OP5_CTRL      | RW     | 0x40      | 0      | 1      |        |        |        |        |        |        |

| 0x07              | CROSS5_CTRL   | RW     | 0x02      |        |        |        |        |        |        | 1      | 0      |

| 0x08              | SW_CTRL       | W      | 0x3F      |        |        | 1      | 1      | 1      | 1      | 1      | 1      |

AN11663 **NXP Semiconductors**

#### CBTL08GP053 Programmer's Guide

#### 3.5 UFP Pin Assignment E

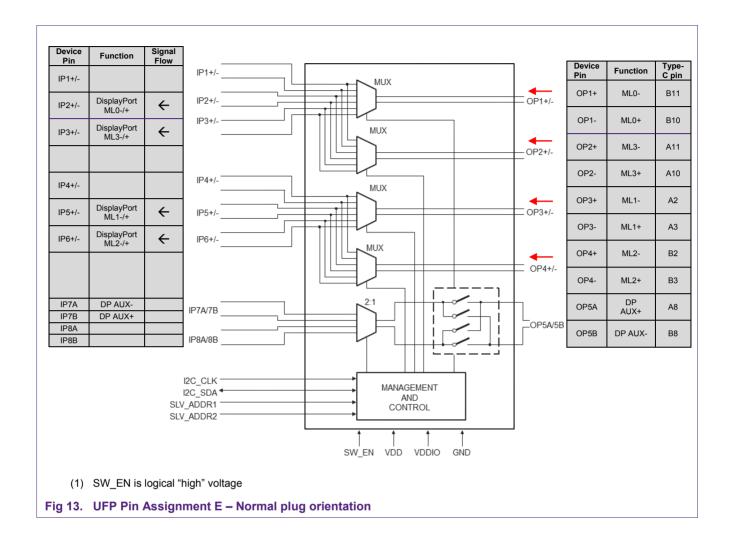

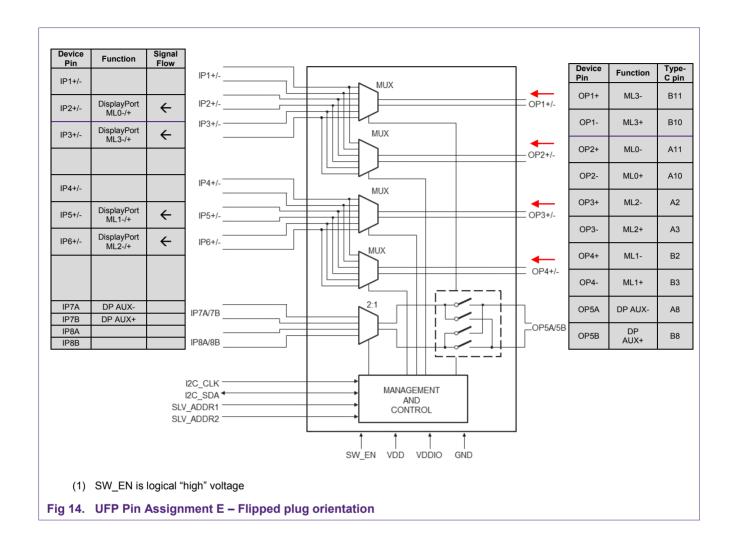

UFP Pin Assignment E is for use cases where a UFP Type-C connector in a display monitor (sink) is connected to a DisplayPort-type source connector with a passive or active cable. Such cable assemblies have unique features as defined in the DP Alt Mode specification. For example note the signal inversion of the high-speed lines when compared to other UFP pin assignments. In addition these cables will contain ACcoupling capacitors on 2 of the 4 high-speed lanes. The required pinout and signal mappings are shown in Fig 13 and Fig 14. Table 12 and Table 13 show the relevant register maps for the CBTL08GP053 respectively.

Table 12. Register Map: UFP Pin Assignment E – Normal plug orientation Reserved bit fields are shaded. Reads will be zeros and writes do not have any effect

| Address<br>Offset | Register Name | Access | Hex Value | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-------------------|---------------|--------|-----------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x01              | SYS_CTRL      | RW     | 0x80      | 1      |        |        |        |        |        |        |        |

| 0x02              | OP1_CTRL      | RW     | 0x02      |        |        |        |        |        | 0      | 1      | 0      |

| 0x03              | OP2_CTRL      | RW     | 0x04      |        |        |        |        |        | 1      | 0      | 0      |

| 0x04              | OP3_CTRL      | RW     | 0x10      |        |        | 0      | 1      | 0      |        |        |        |

| 0x05              | OP4_CTRL      | RW     | 0x20      |        |        | 1      | 0      | 0      |        |        |        |

| 0x06              | OP5_CTRL      | RW     | 0x40      | 0      | 1      |        |        |        |        |        |        |

| 0x07              | CROSS5_CTRL   | RW     | 0x02      |        |        |        |        |        |        | 1      | 0      |

| 0x08              | SW_CTRL       | W      | 0x3F      |        |        | 1      | 1      | 1      | 1      | 1      | 1      |

Table 13. Register Map: UFP Pin Assignment E – Flipped plug orientation Reserved bit fields are shaded. Reads will be zeros and writes do not have any effect

| Address<br>Offset | Register Name | Access | Hex Value | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-------------------|---------------|--------|-----------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x01              | SYS_CTRL      | RW     | 0x80      | 1      |        |        |        |        |        |        |        |

| 0x02              | OP1_CTRL      | RW     | 0x04      |        |        |        |        |        | 1      | 0      | 0      |

| 0x03              | OP2_CTRL      | RW     | 0x02      |        |        |        |        |        | 0      | 1      | 0      |

| 0x04              | OP3_CTRL      | RW     | 0x20      |        |        | 1      | 0      | 0      |        |        |        |

| 0x05              | OP4_CTRL      | RW     | 0x10      |        |        | 0      | 1      | 0      |        |        |        |

| 0x06              | OP5_CTRL      | RW     | 0x40      | 0      | 1      |        |        |        |        |        |        |

| 0x07              | CROSS5_CTRL   | RW     | 0x01      |        |        |        |        |        |        | 0      | 1      |

| 0x08              | SW_CTRL       | W      | 0x3F      |        |        | 1      | 1      | 1      | 1      | 1      | 1      |

#### CBTL08GP053 Programmer's Guide

#### 3.6 DP Alt Mode Standby Modes

Various usage cases have been presented in the previous sections to support DP Alt Mode functionality over Type-C connectors with the CBTL08GP053. There are also other configurations for the CBTL08GP053 that can be used as "safe" transition states between different DP Alt Mode pin assignments. Some possible options for DP standby modes for both DFP and UFP are presented in the following Tables. Please contact NXP for further specific implementation details.

Table 14. Safe Mode - Any plug orientation (DFP or UFP)

Reserved bit fields are shaded. Reads will be zeros and writes do not have any effect

| Address<br>Offset | Register Name | Access | Hex Value | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-------------------|---------------|--------|-----------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x01              | SYS_CTRL      | RW     | 0x80      | 1      |        |        |        |        |        |        |        |

| 0x02              | OP1_CTRL      | RW     | 0x00      |        |        |        |        |        | 0      | 0      | 0      |

| 0x03              | OP2_CTRL      | RW     | 0x00      |        |        |        |        |        | 0      | 0      | 0      |

| 0x04              | OP3_CTRL      | RW     | 0x00      |        |        | 0      | 0      | 0      |        |        |        |

| 0x05              | OP4_CTRL      | RW     | 0x00      |        |        | 0      | 0      | 0      |        |        |        |

| 0x06              | OP5_CTRL      | RW     | 0x00      | 0      | 0      |        |        |        |        |        |        |

| 0x07              | CROSS5_CTRL   | RW     | 0x00      |        |        |        |        |        |        | 0      | 0      |

| 0x08              | SW_CTRL       | W      | 0x3F      |        |        | 1      | 1      | 1      | 1      | 1      | 1      |

Table 15. USB 3x Mode – Normal plug orientation (DFP or UFP)

Reserved bit fields are shaded. Reads will be zeros and writes do not have any effect

| Address<br>Offset | Register Name | Access | Hex Value | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-------------------|---------------|--------|-----------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x01              | SYS_CTRL      | RW     | 0x80      | 1      |        |        |        |        |        |        |        |

| 0x02              | OP1_CTRL      | RW     | 0x01      |        |        |        |        |        | 0      | 0      | 1      |

| 0x03              | OP2_CTRL      | RW     | 0x00      |        |        |        |        |        | 0      | 0      | 0      |

| 0x04              | OP3_CTRL      | RW     | 0x08      |        |        | 0      | 0      | 1      |        |        |        |

| 0x05              | OP4_CTRL      | RW     | 0x00      |        |        | 0      | 0      | 0      |        |        |        |

| 0x06              | OP5_CTRL      | RW     | 0x00      | 0      | 0      |        |        |        |        |        |        |

| 0x07              | CROSS5_CTRL   | RW     | 0x00      |        |        |        |        |        |        | 0      | 0      |

| 0x08              | SW_CTRL       | W      | 0x3F      |        |        | 1      | 1      | 1      | 1      | 1      | 1      |

#### CBTL08GP053 Programmer's Guide

Table 16. USB 3x Mode – Flipped plug orientation (DFP or UFP)

Reserved bit fields are shaded. Reads will be zeros and writes do not have any effect

| Address<br>Offset | Register Name | Access | Hex Value | Bit[7] | Bit[6] | Bit[5] | Bit[4] | Bit[3] | Bit[2] | Bit[1] | Bit[0] |

|-------------------|---------------|--------|-----------|--------|--------|--------|--------|--------|--------|--------|--------|

| 0x01              | SYS_CTRL      | RW     | 0x80      | 1      |        |        |        |        |        |        |        |

| 0x02              | OP1_CTRL      | RW     | 0x00      |        |        |        |        |        | 0      | 0      | 0      |

| 0x03              | OP2_CTRL      | RW     | 0x01      |        |        |        |        |        | 0      | 0      | 1      |

| 0x04              | OP3_CTRL      | RW     | 0x00      |        |        | 0      | 0      | 0      |        |        |        |

| 0x05              | OP4_CTRL      | RW     | 0x08      |        |        | 0      | 0      | 1      |        |        |        |

| 0x06              | OP5_CTRL      | RW     | 0x00      | 0      | 0      |        |        |        |        |        |        |

| 0x07              | CROSS5_CTRL   | RW     | 0x00      |        |        |        |        |        |        | 0      | 0      |

| 0x08              | SW_CTRL       | W      | 0x3F      |        |        | 1      | 1      | 1      | 1      | 1      | 1      |

#### **CBTL08GP053 Programmer's Guide**

#### 4. References

- [1] CBTL08GP053 data sheet, NXP Semiconductors, San Jose, CA, 2015

- [2] VESA DisplayPort Alt Mode on USB Type-C Standard version 1.0, Video Electronics Standards Association, Newark, CA 2014

- [3] Universal Serial Bus Power Delivery Specification, Rev 2.0, V1.0, 11 August 2014

- [4] Universal Serial Bus Type-C Cable and Connector Specification Revision 1.1, April 3, 2015

#### CBTL08GP053 Programmer's Guide

#### 5. Legal information

#### 5.1 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

#### 5.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine

whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

#### 5.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are property of their respective owners.

#### **CBTL08GP053 Programmer's Guide**

## 6. List of figures

| Fig 1.  | CBTL08GP053 functional block diagram3                      |

|---------|------------------------------------------------------------|

| Fig 2.  | I <sup>2</sup> C write and read sequence4                  |

| Fig 3.  | Front view of USB Type-C receptacle interface 6            |

| Fig 4.  | Recommended DP Alt Mode connections for CBTL08GP053 device |

| Fig 5.  | DFP Pin Assignment C (and E) – Normal plug orientation8    |

| Fig 6.  | DFP Pin Assignment C (and E) – Flipped plug orientation9   |

| Fig 7.  | DFP Pin Assignment D (and F) – Normal plug orientation10   |

| Fig 8.  | DFP Pin Assignment D (and F) – Flipped plug orientation11  |

| Fig 9.  | UFP Pin Assignment C – Normal plug orientation12           |

| Fig 10. | UFP Pin Assignment C – Flipped plug orientation13          |

| Fig 11. | UFP Pin Assignment D – Normal plug orientation14           |

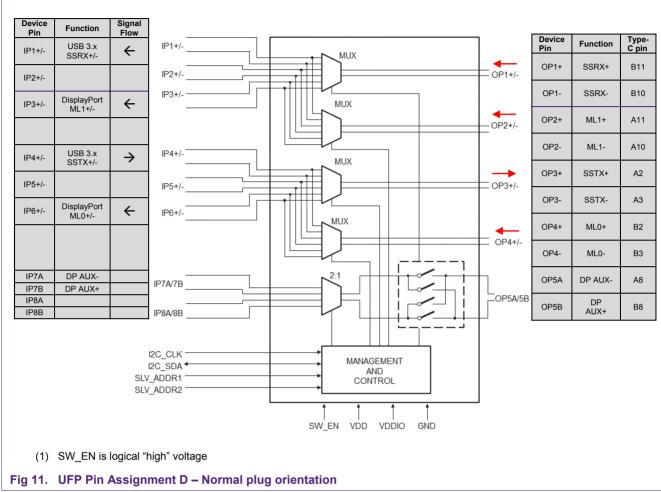

| Fig 12. | UFP Pin Assignment D – Flipped plug orientation15          |

| Fig 13. | UFP Pin Assignment E – Normal plug orientation17           |

| Fig 14. | UFP Pin Assignment E – Flipped plug orientation18          |

23 of 25

#### **CBTL08GP053 Programmer's Guide**

### 7. List of tables

| Table 1.  | CBTL08GP053 slave addresses4                                            |

|-----------|-------------------------------------------------------------------------|

| Table 2.  | CBTL08GP053 Register Map5                                               |

| Table 3.  | CBTL08GP053 for DisplayPort Alt Mode6                                   |

| Table 4.  | Register Map: DFP Pin Assignment C (and E) – Normal plug orientation8   |

| Table 5.  | Register Map: DFP Pin Assignment C (and E) – Flipped plug orientation9  |

| Table 6.  | Register Map: DFP Pin Assignment D (and F) – Normal plug orientation10  |

| Table 7.  | Register Map: DFP Pin Assignment D (and F) – Flipped plug orientation11 |

| Table 8.  | Register Map: UFP Pin Assignment C – Normal plug orientation12          |

| Table 9.  | Register Map: UFP Pin Assignment C – Flipped plug orientation           |

| Table 10. | Register Map: UFP Pin Assignment D – Normal plug orientation14          |

| Table 11. | Register Map: UFP Pin Assignment D – Flipped plug orientation           |

| Table 12. | Register Map: UFP Pin Assignment E – Normal plug orientation17          |

| Table 13. | Register Map: UFP Pin Assignment E – Flipped plug orientation18         |

| Table 14. | . •                                                                     |

| Table 15. | USB 3x Mode – Normal plug orientation (DFP or UFP)19                    |

| Table 16. | USB 3x Mode – Flipped plug orientation (DFP or UFP)20                   |

#### **CBTL08GP053 Programmer's Guide**

#### 8. Contents

| 1.  | Introduction                             | 3    |

|-----|------------------------------------------|------|

| 2.  | CBTL08GP053 description                  | 3    |

| 2.1 | I <sup>2</sup> C Interface               |      |

| 2.2 | Operating modes                          | 4    |

| 3.  | Application Use Cases: DisplayPort Alt N | lode |

|     | for USB Type-C                           |      |

| 3.1 | DFP Pin Assignment C (and E)             | 8    |

| 3.2 | DFP Pin Assignment D (and F)             | 10   |

| 3.3 | UFP Pin Assignment C                     | 12   |

| 3.4 | UFP Pin Assignment D                     | 14   |

| 3.5 | UFP Pin Assignment E                     | 16   |

| 3.6 | DP Alt Mode Standby Modes                | 19   |

| 4.  | References                               | 21   |

| 5.  | Legal information                        | 22   |

| 5.1 | Definitions                              | 22   |

| 5.2 | Disclaimers                              | 22   |

| 5.3 | Trademarks                               |      |

| 6.  | List of figures                          | 23   |

| 7.  | List of tables                           | 24   |

| 8.  | Contents                                 | 25   |

|     |                                          |      |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in the section 'Legal information'.