**AN11640** TFF1044 Application Recommendations Rev. 1 – 4 June 2015

| Document information |                                                                                                                                                                                             |  |  |  |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Info                 | Content                                                                                                                                                                                     |  |  |  |  |  |  |

| Keywords             | TFF1044, Quad LNB, Quattro LNB, DVB-S, Ku band to L-band Down Converter, FIMOD IC, Ku Band, NF, PCB                                                                                         |  |  |  |  |  |  |

| Abstract             | This application note describes how to use the TFF1044 in a typical environment, (typically in DVB-S outdoor equipment). It also lists some do's and don'ts and frequently asked questions. |  |  |  |  |  |  |

## AN11640

#### **TFF1044 Application Recommendations**

#### **Revision history**

| 1 20150604 First publication | Rev | Date     | Description       |  |

|------------------------------|-----|----------|-------------------|--|

|                              | 1   | 20150604 | First publication |  |

### **Contact information**

For more information, please visit: <u>http://www.nxp.com</u>

For sales office addresses, please send an email to: salesaddresses@nxp.com

AN11640

All information provided in this document is subject to legal disclaimers.

### 1. Introduction

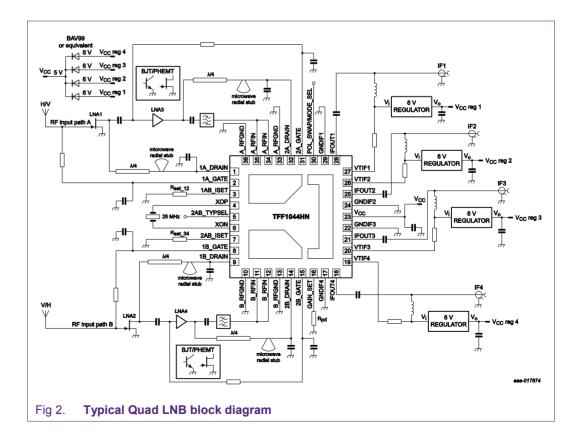

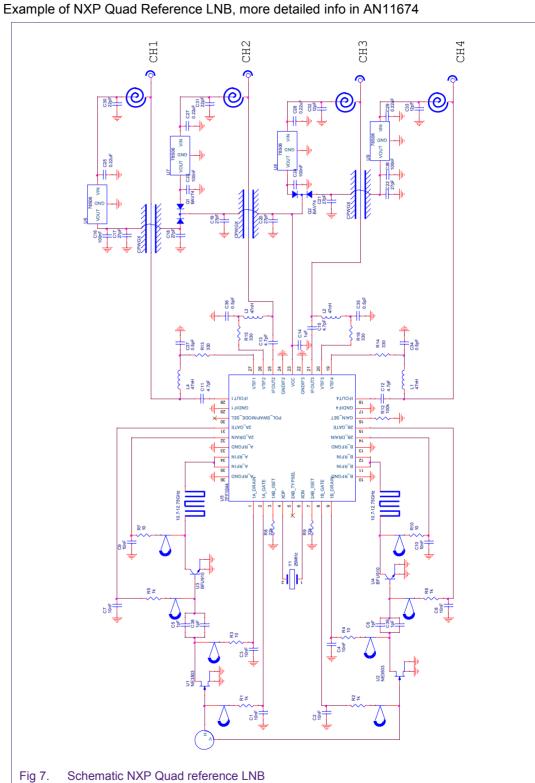

This document describes the functionality and use of TFF1044 DCV IC. It also gives some application hints and a schematic for a Quad LNB design with pHEMT first stage LNA's and SiGe second stage LNA stages.

### 2. Product Description

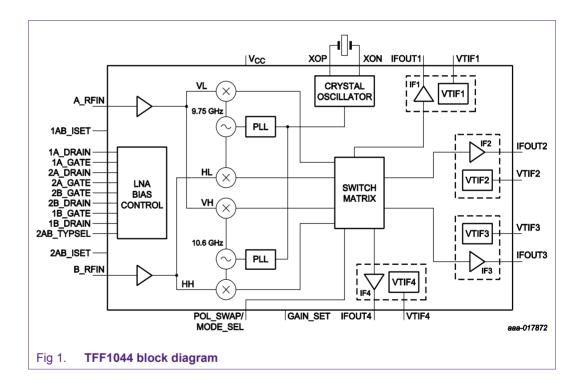

The TFF1044HN is a 10.70 GHz to 12.75 GHz Ku band down converter for use in universal quad and Quattro Low Noise Block (LNB) in satellite receiver systems. The device features two RF inputs (two polarizations) and four IF outputs (up to 4 active IF paths). It integrates bias generation and control for the external LNA stages, image rejection filtering, LO generation, down conversion mixers, IF amplifier stages, voltage and tone detection on each IF output (for polarization and band selection) and the 4 (IF channels) x 4 (2 polarizations, 2 bands) IF matrix switch.

For flexibility, the gain can be controlled in three discrete stages, the polarization of the RF inputs can be swapped and the second stage LNA biasing control can be switched from pHEMT to BJT configuration.

### 2.1 Design considerations

The TFF1044 is designed for "outdoor end-user products" such as Quad- and Quattro LNB's used for Direct-To-Home Television (DTHTV).

It can be used to create an alignment free product with two RF inputs and four IF outputs and enables Printed Circuit Board size reduction.

Apart from the TFF1044, the LNA stages, a 25 MHz crystal, voltage regulator(s) and some passive circuitry is required to complete a quad LNB.

As each device is fully functional tested TFF1044 enables significant cost reduction in the MP final test / repair process compared to discretely build quad/quattro LNB's.

Image rejection filters are integrated, depending on the required overall image rejection additional filtering may be applied.

Two RF inputs are present to convert the orthogonal polarized signals simultaneously, required LNA's are usually implemented by two cascaded stages per polarization. There is a polarization swap selection pin to enable PCB routing with optimum (none crossing) Ku band RF tracks.

The TFF1044 has selectable gain states in order to have freedom to vary the overall LNB gain. Targeted overall Conversion Gain (using two cascaded LNA stages) is 51 dB – 61 dB depending on the gain setting and applied LNA stages (pHEMT and/or SiGe RF transistor). The TFF1044 is capable of driving the bias for the LNA stages for GaAs as well as for SiGe based RF transistors. Depending on required overall NF and Gain also three cascaded stages (biasing for third stage not integrated in TFF1044) may be used.

### 2.2 Noise Figure and Gain, system level example 1

| NoiseCalc   | -              | Set Num | ber of Stages        | = 6             | Calculat               | e [F4]          |                   | Clea    | 2   | Main Mei |

|-------------|----------------|---------|----------------------|-----------------|------------------------|-----------------|-------------------|---------|-----|----------|

|             | _              | 1       | Stage 1              | Stage 2         | Stage 3                | Stage 4         | Stage 5           | Stage 6 |     |          |

| s           | tage Data      | Units   |                      |                 |                        |                 |                   |         |     |          |

| Sta         | ge Name:       |         | loss before<br>LNA 1 | LNA 1,<br>pHEMT | interstage<br>matching | LNA 2,<br>pHEMT | BPF               | TFF1044 |     |          |

| No          | ise Figure     | dB      | 0.2                  | 0.45            | 0.2                    | 0.4             | 5 1.5             | 8       |     |          |

| Ga          | n              | dB      | -0.2                 | 11.5            | -0.2                   | 11.             | 5 -1.5            | 33      |     |          |

| Du          | tput IP3       | dBm     | 100                  | 30              | 100                    | 3               | 0 100             | 15      |     |          |

| dN          | F/dTemp        | dB/°C   | 0                    | 0               | 0                      |                 | 0 0               | 0       |     |          |

| dG          | /dTemp         | dB/°C   | 0                    | 0               | 0                      | ·               | 0 0               | 0       |     |          |

| Sta         | ge Analysis:   | 1       | 0                    | 0               | 0                      |                 | 0 0               | 0       |     |          |

| NF          | (Temp corr)    | dB      | 0.20                 | 0.45            | 0.20                   | 0.4             | 5 1.50            | 8.00    |     |          |

| Ga          | in (Temp corr) | dB      | -0.20                | 11.50           | -0.20                  | 11.5            | 0 -1.50           | 33.00   |     |          |

| Inp         | ut Power       | dBm     | -60.00               | -60.20          | -48.70                 | -48.9           | 0 -37.40          | -38.90  |     |          |

| Ou          | tput Power     | dBm     | -60.20               | -48.70          | -48.90                 | -37.4           | -38.90            | -5.90   |     |          |

| dN          | IF/d NF        | dB/dB   | 0.87                 | 0.96            | 0.07                   | 0.0             | 8 0.01            | 0.05    |     |          |

| dN          | IF/d Gain      | dB/dB   | -0.13                | -0.04           | -0.04                  | -0.0            | 3 -0.03           | 0.00    |     |          |

| dif         | P3/d1P3        | dBm/dBm | 0.00                 | 0.00            | 0.00                   | 0.0             | 0 0.00            | 1.00    |     |          |

| Enter Syste | em Parameters: |         | S                    | ystem Analysis: |                        |                 |                   |         |     |          |

| Input Pov   | ver            |         | dBm                  | Gain =          | 54.10                  | dB              | Input IP3 =       |         | dBm |          |

| Analysis    | Temperature    | 25      | °C                   | Noise Figure =  | 0.85                   | dB              | Output IP3 =      |         | dBm |          |

| Noise BV    | /              |         |                      | Noise Temp =    | 62.90                  | °К              | Input IM level =  |         | dBm |          |

| Ref Temp    |                | 25      | °C                   | SNR =           | 53.12                  | dB              | Input IM level =  |         | dBC |          |

|             | sensitivity)   | 0       | dB                   | MDS =           |                        |                 | Dutput IM level = |         | dBm |          |

| Noise So    | urce (Ref)     | 290     | °K                   | Sensitivity =   |                        |                 | Dutput IM level = |         | dBC |          |

|             |                |         |                      | Noise Floor =   | -173.12 d              | Bm/Hz           | SFDR =            | 49.35   | dB  |          |

Example for 2 cascaded pHEMT LNA's, typical gain (EU) LNB:

In this Noise/Gain budget example for a 55dB Gain LNB, based on Rogers material. We assume two frequently used pHEMT devices are applied as LNA1/LNA2 stages. Gain mode for TFF1044 is medium, values applied are typical (overall typical Gain is 54 dB, NF is 0.85 dB).

### 2.3 Noise Figure and Gain, system level example 2

Example for 1<sup>st</sup> stage pHEMT, 2<sup>nd</sup> stage BJT LNA's, typical gain (EU) LNB:

|         | Application Exam    | 1       | ions Help<br>ber of Stages | = 6             | Calculat               | e IF41    |                   | Clea    | r Main Me | nu |

|---------|---------------------|---------|----------------------------|-----------------|------------------------|-----------|-------------------|---------|-----------|----|

| NoiseCa |                     |         |                            |                 |                        | 3.1       |                   |         |           |    |

|         |                     |         | Stage 1                    | Stage 2         | Stage 3                | Stage 4   | Stage 5           | Stage 6 |           |    |

|         | Stage Data          | Units   |                            |                 |                        |           |                   |         |           |    |

|         | Stage Name:         |         | loss before<br>LNA 1       | LNA 1.<br>pHEMT | interstage<br>matching | LNA 2, BJ | r BPF             | TFF1044 |           |    |

|         | Noise Figure        | dB      | 0.2                        | 0.45            | 0.2                    | 0.6       | 5 1.5             | 8       |           |    |

|         | Gain                | dB      | -0.2                       | 11.5            | -0.2                   | 1         | 3 -1.5            | 33      |           |    |

|         | Output IP3          | dBm     | 100                        | 30              | 100                    |           | 0 100             | 15      |           |    |

|         | dNF/dTemp           | dB/°C   | 0                          | 0               | 0                      |           | 0 0               | 0       | e         |    |

|         | dG/dTemp            | dB/°C   | 0                          | 0               | 0                      |           | 0 0               | 0       |           |    |

|         | Stage Analysis:     |         | 0                          | 0               | 0                      |           | 0 0               | 0       |           |    |

|         | NF (Temp corr)      | dB      | 0.20                       | 0.45            | 0.20                   | 0,6       | 5 1.50            | 8.00    |           |    |

|         | Gain (Temp corr)    | dB      | -0.20                      | 11.50           | -0.20                  | 13,0      | 0 -1.50           | 33.00   |           |    |

|         | Input Power         | dBm     | -60.00                     | -60.20          | -48.70                 | -48,9     | 0 -35.90          | -37.40  | 6         |    |

|         | Output Power        | dBm     | -60.20                     | -48.70          | -48.90                 | -35.9     | -37.40            | -4.40   |           |    |

|         | d NF/d NF           | dB/dB   | 0.88                       |                 | 0.07                   | 0,0       |                   | 0.03    |           |    |

|         | d NF/d Gain         | dB/dB   | -0.12                      |                 | -0.03                  | -0,0      |                   | 0.00    |           |    |

|         | d IP3/d IP3         | dBm/dBm | 0.00                       | 0.00            | 0.00                   | 0,0       | 0.00              | 1.00    |           |    |

| Ente    | System Parameters:  |         | S                          | ystem Analysis: |                        |           |                   |         |           |    |

| Inp     | ut Power            | -60     | dBm                        | Gain =          | 55.60                  | dB        | Input IP3 =       | -40.60  | dBm       |    |

| An      | alysis Temperature  | 25      | °C   1                     | Noise Figure =  | 0.82                   | dB        | Output IP3 =      | 15.00   | dBm       |    |

|         | se BW               | 1       | MHz                        | Noise Temp =    | 60.39                  | *K        | Input IM level =  | -98.80  | dBm       |    |

| Re      | Temperature         | 25      | °C                         | SNR =           | 53,15                  | dB        | Input IM level =  | -38.80  | dBC       |    |

|         | l (for sensitivity) | 0       | dB                         | MDS =           |                        |           | Output IM level = |         | dBm       |    |

| No      | se Source (Ref)     | 290     | °K                         | Sensitivity =   |                        |           | Output IM level = |         | dBC       |    |

|         |                     |         |                            | Noise Floor =   | -173.15 di             | 3m/Hz     | SFDR =            | 48.37   | dB        |    |

In this Noise/Gain budget example for a 55dB Gain LNB, based on Rogers material. In this Noise/Gain budget example we assume one frequently used pHEMT device as first stage cascaded by a BFU910 as 2<sup>nd</sup> LNA stage. Gain mode for TFF1044 is medium, values applied are typical (overall typical Gain is 56 dB, NF is 0.82 dB). So compared to example 1 replacing the 2<sup>nd</sup> stage LNA by SiGe BFU910 RF transistor the overall gain increased by 1.5dB while the overall Noise Figure decreases by 0.03dB!

#### 2.4 Noise Figure and Gain, system level example 3

Example for 1<sup>st</sup> stage BFU910, 2<sup>nd</sup> stage BFU910 LNA's, typical high gain LNB:

| VoiseCa | alc                 | Set Nur | nber of Stages       | = 6            | Calculate              | e [F4]   |      |                  | Clea    | r   | Main Menu [F8 |

|---------|---------------------|---------|----------------------|----------------|------------------------|----------|------|------------------|---------|-----|---------------|

|         | -                   |         | Stage 1              | Stage 2        | Stage 3                | Stage    | 4    | Stage 5          | Stage 6 |     |               |

|         | Stage Data          | Units   |                      |                |                        | -        | H    |                  |         |     |               |

|         | Stage Name:         |         | loss before<br>LNA 1 | LNA 1, BJT     | interstage<br>matching | LNA 2, E | BJT  | BPF              | TFF1044 |     |               |

|         | Noise Figure        | dB      | 0.2                  | 0.65           | 0.2                    | 0        | 0.65 | 1.5              | 8       |     |               |

|         | Gain                | dB      | -0.2                 | 13             | -0.2                   |          | 13   | -1.5             | .36     |     |               |

|         | Output IP3          | dBm     | 100                  | 30             | 100                    |          | 30   | 100              | 15      |     |               |

|         | dNF/dTemp           | dB/°C   | 0                    |                | 0                      |          | 0    | 0                | 0       |     |               |

|         | dG/dTemp            | dB/*C   | 0                    | 0              | 0                      |          | 0    | 0                | 0       |     |               |

|         | Stage Analysis:     |         | . 0                  | 0              | 0                      | -        | 0    | 0                | 0       |     |               |

|         | NF (Temp corr)      | dB      | 0.20                 | 0.65           | 0.20                   | 0        | 0.65 | 1.50             | 8.00    |     |               |

|         | Gain (Temp corr)    | dB      | -0.20                | 13.00          | -0.20                  | 13       | 3.00 | -1.50            | 36.00   |     |               |

|         | Input Power         | dBm     | -60.00               | -60.20         | -47.20                 | -47      | 7.40 | -34.40           | -35.90  |     |               |

|         | Output Power        | dBm     | -60.20               | -47.20         | -47.40                 | -34      | 4.40 | -35.90           | 0.10    |     |               |

|         | d NF/d NF           | dB/dB   | 0.85                 | 0.98           | 0.05                   | 0        | 0.06 | 0.00             | 0.02    |     |               |

|         | d NF/d Gain         | dB/dB   | -0.15                | -0.02          | -0.02                  | -0       | 0.02 | -0.01            | 0.00    |     |               |

|         | d IP3/d IP3         | dBm/dBm | 0.00                 | 0.00           | 0.00                   | 0        | 0.00 | 0.00             | 1.00    |     |               |

| Ente    | System Parameters:  |         | Sj                   | stem Analysis: |                        |          |      |                  |         |     |               |

| Inp     | ut Power            | -60     | dBm                  | Gain =         | 60.10                  | dB       | -    | Input IP3 =      | -45.10  | dBm |               |

| An      | alysis Temperature  | 25      | 1 3                  | Voise Figure = | 0.97                   | dB       |      | Output IP3 =     | 15.00   | dBm |               |

| No      | ise BW              | 1       | MHz I                | Noise Temp =   | 72.30                  | °К       | h    | nput IM level =  | -89.80  | dBm |               |

| Re      | f Temperature       | 25      | °C                   | SNR =          | 53.01                  | dB       | 1    | nput IM level =  | -29.80  | dBC |               |

| S/I     | V (for sensitivity) | 0       | dB                   | MDS =          | -113.01                | dBm      | 0.   | utput IM level = | -29.70  | dBm |               |

| No      | ise Source (Ref)    | 290     | °К                   | Sensitivity =  | -113.01                | dBm      | 0.   | utput IM level = | -29.80  | dBC |               |

|         |                     |         |                      | Noise Floor =  | -173.01 df             | 3m/Hz    |      | SFDR =           | 45.27   | dB  |               |

Fig 5. Typical high gain AppCAD example using 4 BFU910

In this Noise/Gain budget example for a 60dB Gain LNB, based on Rogers material. In this Noise/Gain budget example we assume both LNA stages are implemented by SiGe BFU910.

Please note that the biasing for two LNA stages is sourced from the TFF1044, two stages need to be biased by resistive networks (compared to pHEMT a simple network could be applied as no negative bias voltage is required).

Gain mode for TFF1044 is high, values applied are typical (overall typical Gain is 60 dB, NF is 0.97 dB).

#### **Overview of system-level examples:**

| · · · · · · · · · · · · · · · · · · · |                           |              |              |            |

|---------------------------------------|---------------------------|--------------|--------------|------------|

| 1 <sup>st</sup> stage LNA             | 2 <sup>nd</sup> stage LNA | TFF1044 gain | Expected     | Expected   |

|                                       |                           | setting      | Overall Gain | Overall NF |

| Common used<br>pHEMT                  | Common used<br>pHEMT      | medium       | 54 dB        | 0.85 dB    |

| Common used<br>pHEMT                  | NXP BFU910                | medium       | 56 dB        | 0.82 dB    |

| NXP BFU910                            | NXP BFU910                | high         | 60 dB        | 0.97 dB    |

### 3. I/O's description

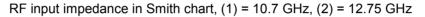

#### 3.1 RF inputs, A\_RFIN and B\_RFIN

The two RF-inputs are designed to have a characteristic impedance of 50  $\Omega$  in the Ku band, and are AC coupled. However there is a DC short to GND on both inputs (inductors used as part of the RF filtering). Therefore LNA outputs that carry DC cannot be directly connected to the A\_RFIN and/or B\_RFIN pins.

A S1P file with complex impedance over frequency, required for S11 optimization in a simulator, can be down-loaded from <u>www.nxp.com</u>.

There is a slight difference between both inputs, due to the physical design.

#### 3.2 IF outputs

The four IF outputs have a characteristic impedance of 75  $\Omega$  in the L-band and are DC coupled. A DC blocking capacitor is required. Those outputs are usually combined with the Vif\_X (with 1<X<4) pins to enable V/T detect on each IF output (not required for Quattro mode).

#### 3.3 PHEMT bias control

Maximum four LNA stages, normally two cascaded stages per RF path, can be biased. The first stages are pHEMT types only. The second LNA stages can be pHEMT or RF transistor: set by the pin 2AB\_TYPSEL. Connect this pin to GND for pHEMT bias selection, and leave it floating to bias BFU910 or equivalent.

#### 3.4 LNA bias current setting

Used to program the LNA quiescent current, i.e. 10mA for typical pHEMT's. Pin 1AB\_ISET programs the quiescent current for the first stage LNA's (RFA as well as RFB), the pin 2AB\_ISET has a similar function for the 2<sup>nd</sup> LNA stages. A typical resistor of 22 k $\Omega$  to GND is applied to set 10 mA typical DC bias current. The allowed range for the Rset resistors is 15 k $\Omega$  to 220 k $\Omega$ . Typical values of the quiescent current as function of the Rset resistor value is shown in the table below.

| Rset value                                | 220 kΩ | 33 kΩ | 22 kΩ | 15 kΩ |

|-------------------------------------------|--------|-------|-------|-------|

| Average Id measured at nominal conditions | 1 mA   | 7 mA  | 11 mA | 15 mA |

#### 3.5 Crystal pins (reference oscillator)

These are used to connect the crystal, required for the PLL in the LO generation. Avoid long in-balanced tracks, they could lead to interference.

A typical load capacitance of 16 pF is seen for the TFF1044 including the parasitic capacitance of the PCB pads.

#### 3.6 IF mode control pins (VT-IF X, 1 < X < 4)

These are inputs correlated to the four IF outputs and control the 4 x 4 switch matrix. Switching between RFA and RFB depends on the DC value, LB/HB selection depends on the presence of a 22 kHz pulse superposed on the DC.

#### 3.7 Polarization Swap / Mode Select

With this pin one could set the TFF1044 in different modes, for example toggle the RFA  $\Leftrightarrow$  RFB selection mode (depending on Voltage on pin VT\_IF X). This enables the shortest none-crossing possible routing of the RF tracks in the front-end part of the LNB.

To program the TFF1044 into Quattro mode this pin should be pulled down to GND via a 100 k $\Omega$  resistor. For normal operation (RFA is horizontal) this pin should be grounded, to swap (RFB is horizontal) the pin must be kept floating.

#### 3.8 Gain Select

The TFF1044 conversion gain has three modes, low, medium and high gain (typ. 30, 33 and 36dB). Pin GAIN\_SET must be grounded for low gain, floating for medium gain and connected to GND via 100 k $\Omega$  for high gain mode.

**AN11640**

#### **Typical application Diagrams / Schematics** 4.

© NXP B.V. 2015. All rights reserved.

**Application note**

AN11640

AN11640

Picture of NXP Quad Reference LNB, see also AN11674

### 4.1 Supply topology

LNB's (DVB-S outdoor equipment) are usually supplied by the indoor equipment over the coaxial cable(s). RF is superposed on the DC content, hence in the LNB Bias Tees are required to separate the DC from the AC content.

The DC voltage at the IF is also used to select the required polarization for corresponding IF. Common used values are 18 V (Vertical Polarization) or 13 V (Horizontal Polarization).

In addition a low frequency pulse is used to control the band selecting for corresponding IF. A common frequency for this pulse is 22 kHz, no tone selects LB, with tone present, within specified voltage range, HB is selected.

Requirements for the supply:

- 1) The entire supply current can be sourced from 1 indoor unit (STB) or multiple (maximum 4), DC separation between the IF outputs is required;

- 2) The 22kHz pulse may not be present on each IF hence isolation at 22 kHz is required in order to guarantee proper band selection;

- In case linear regulators are used the worse-case scenario for power dissipation and thermal behavior should be monitored/safeguarded (usually in case the LNB has only one active user at 18 Volts).

In NXP Quad reference LNB design each IF has a linear regulator (each one having Imax >200 mA) connected to generate 6 Volts. By doing this the IF's are separated for DC.

The outputs of the regulators are combined, using 4 diodes (If >200 mA), to prevent current flowing from one regulator to the others in case multiple IF's are activated. Due to these diodes the supply voltage for the TFF1044 will be the regulator voltage minus one forward diode voltage.

#### 4.1.1 Regulator decoupling capacitors

The regulators require a decoupling capacitor to GND at each input to suppress noise on the supply lines and to enable stable operation. Using a large capacitor value will cause a low AC impedance and might impact the 22 kHz pulse amplitude. A too small value might lead to regulator instability. Align with the vendor of applied regulator for the lowest, but still safe, possible capacitor value. The capacitor at the regulator outputs can have each required value.

#### 4.1.2 TFF1044 decoupling capacitor

The TFF1044 has integrated regulators and supply decoupling for high frequencies. For low frequency noise/ripple rejection a decoupling capacitor of 1uF, close to the Vcc pin, is recommended.

#### 4.1.3 The IF output Transmission Lines/ Bias Tees

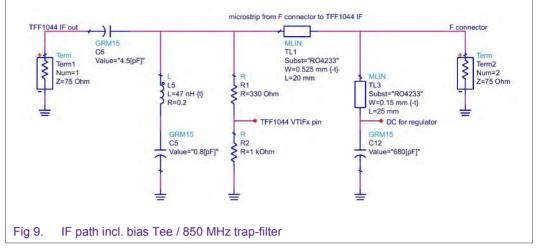

Example for application, configuration for one IF path:

The signal path from TFF1044 IF outputs to the LNB F-connector should contain:

- a 75 Ohms transmission line (TL) to transport RF energy from TFF1044 to F-connector, represented in the schematic above as TL1;

- a way to transport the 22 kHz pulse from the F-connector to the TFF1044 VT-detect pin, by the 330 ohms resistor R1;

- a Bias Tee to separate the DC on the F-connector and feed it into the regulator without effecting the RF signal path, represented in the schematic above as TL3;

- a DC blocking functionality to protect the TFF1044 IF output as C6;

- optionally a trap-filter to suppress the spurious tone generated by the difference of the LO frequencies, created in the schematic above by L5/C5.

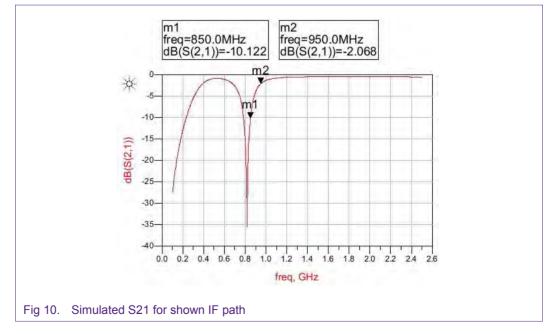

Simulated transfer for given configuration:

Experiments on the TFF1044 evaluation board show that in case a low cost variable wire wound inductor is used (0.4mm wire/2.5mm diameter/4.5 turns), as often applied in tincanned tuners, and alignment is allowed a rejection of the 850 MHz spurious up to 25 dB is possible. The impact on the 950 MHz gain can be less than 1 db.

AN11640

AN11640

### 5. Creating a PCB layout with TFF1044

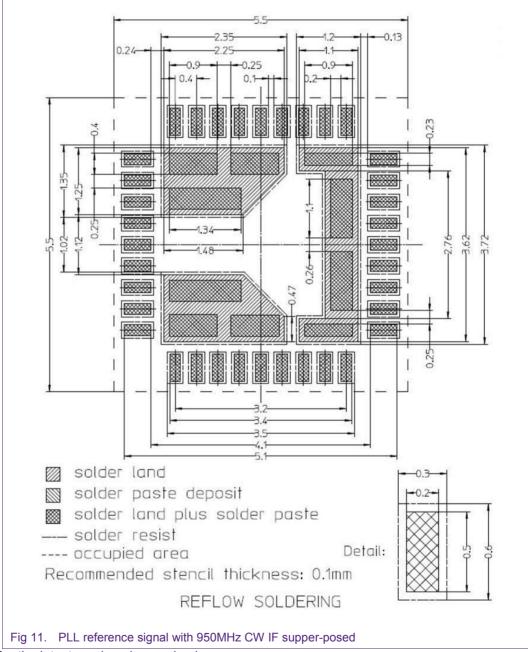

### 5.1 Recommended footprint

For the latest version always check www.nxp.com

We recommend to connect the ground-planes under the device, keeping the free areas under the center. It is also recommended to connect the GND pins 10, 13, 17, 22, 24, 29, 33, 36 towards the inner ground

### 6. Do's and Don'ts

#### 6.1 Measuring the TFF1044

The TFF1044 can be evaluated in an isolated environment on NXP's evaluation board OM7980. If required a control board to generate the 13V/18V and 22 kHz pulse via a bias Tee is available, type number ON7981.

#### 6.1.1 Noise Figure

Most LNB parameters can be measured in conventional way, however because a PLL is applied in the LO generation compared to DRO based LNB's differences might be observed. These are mostly related to the PLL reference frequency (XO). When measuring close to the noise floor in the IF spectrum at a XO harmonic frequency spurious might be observed that are not present in DRO based concepts, however with modulated signals under normal operating conditions the spurious ratios do not degrade the BER or MER.

#### 6.1.1.1 Measuring Noise Figure off XO grid

In case noise figure is measured, applying Y-factor method, with a small resolution bandwidth it is recommended to avoid measuring exactly on the XO grid. In that case the C/(N+I) ratio and not the C/N ratio is measured. Avoid measuring on a grid like 950, 1000, 1050 MHz. Alternatively use a frequency grid like 937.5, 987.5, 1037.5 MHz.

#### 6.1.1.2 Measuring Noise Figure at LO spurious

In case noise figure is measured, applying Y-factor method, with a small resolution bandwidth it is recommended to avoid measuring exactly on the LO beat, which is two times the difference in applied LO  $(2 \times (10.6 - 9.75)) = 1.7$  GHz. In case noise figure is measured at 1700 MHz the C/(N+I) ratio and not the C/N ratio is measured, as explained in the section above.

#### 6.2 Avoid choosing too high resistor value in the VT detect line

As the VT detect pins draw some current the voltage detected at the pin will be lowered by the resistive losses in the cable and mentioned series resistor. Consequently the threshold for the polarization detection will change. A high resistor value (we recommend 330  $\Omega$ ) will have less impact on the connected impedance (Zo and Q-factor for the 850 MHz trap filter in case applied) but induce the risk for the LNB not to be switching to the right polarization. See also section 4.1.2 on this.

#### 6.3 Keep symmetry in XO lines

In the PCB layout of the XO lines it is important to keep as much symmetry in the XO lines as possible, especially in case the reference crystal is placed away from the TFF1044. By doing this eventual disturbing signals that enter the XO lines in common mode will be cancelled.

### 7. Soldering TFF1044 in workshop environment

•

- TFF1044 has a HVLGA36 (or SOT1359-1) package;

- In the application there is usually a large ground-plane, soldering requires to apply heat from the bottom as well as from the top side;

- In this guide-lines we show how the device can be soldered onto a PCB (for low volumes), or for repair purpose;

- In NXP case a Weller rework station is applied with top and bottom heating.

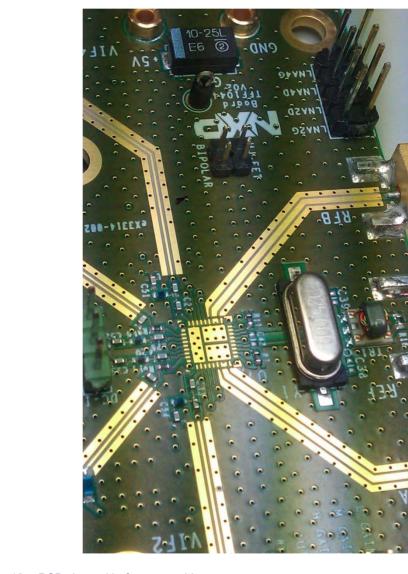

Preparation step 1, Clean the surface for the TFF1044 soldering pads

Fig 12. PCB cleaned before assembly

AN11640

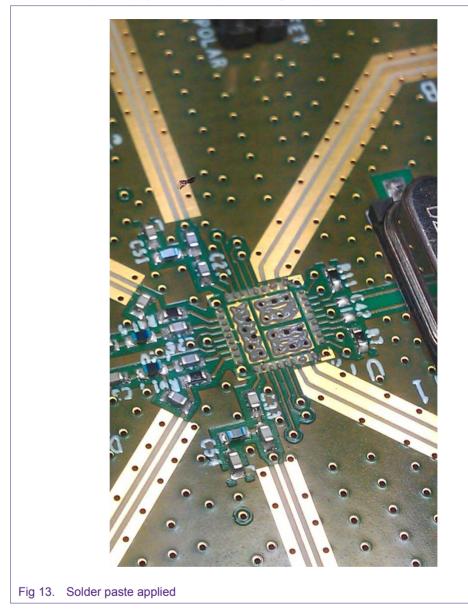

Preparation step 2, Apply the solder paste using a dispenser

AN11640

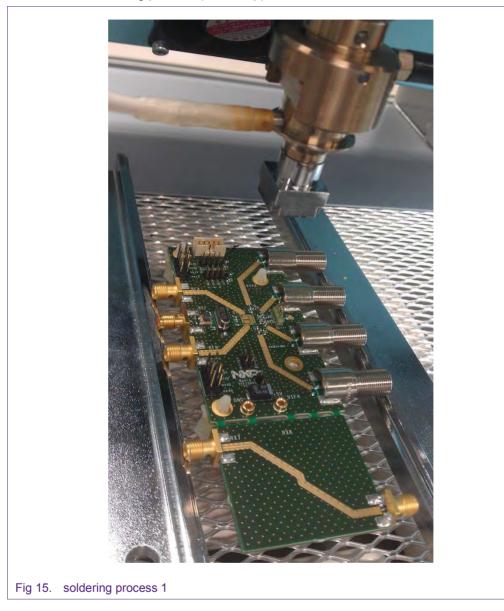

#### The soldering / repair station (Weller)

It is required to apply heat from bottom and top side.

AN11640

#### The soldering process

Just before the soldering process (nozzle up)

**AN11640**

#### The soldering process

During the soldering process (nozzle down). The Weller is pre-heated before the soldering process starts.

Fig 16. soldering process 2

AN11640

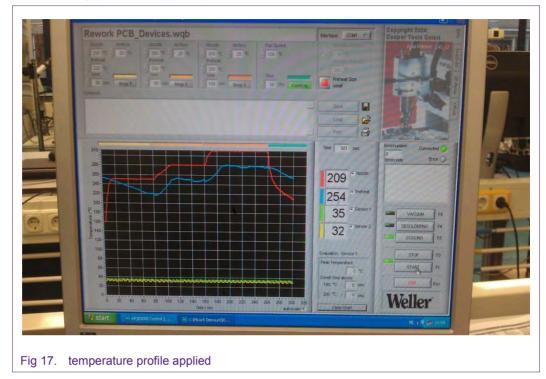

#### The soldering process, applied profile

AN11640

# AN11640

**TFF1044 Application Recommendations**

#### The soldering process, visual inspection

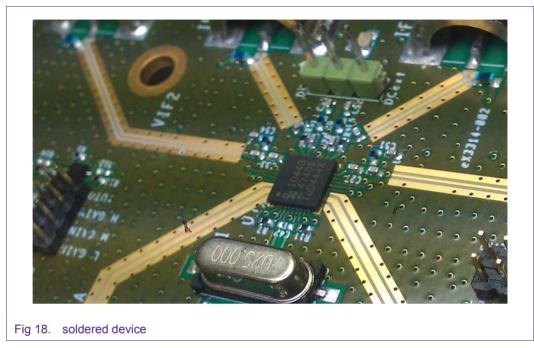

The soldered device

The soldering process, X-ray inspection

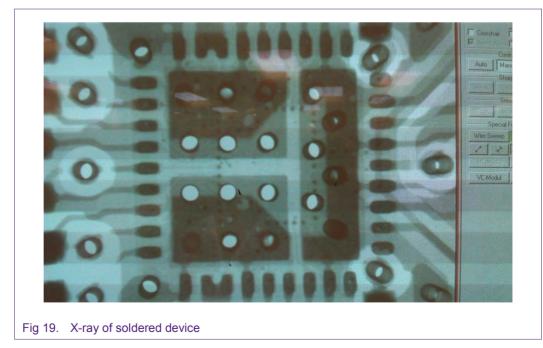

No short circuits or dry-joints observed, 100% ok!

## 8. Typical measurement values

### 8.1 DC voltages at each pin\*3):

| Pin       | Description                                                           | Resistance<br>to GND<br>(Ohm) <sup>[1]</sup> | DC voltage<br>[V] <sup>[2]</sup>         |

|-----------|-----------------------------------------------------------------------|----------------------------------------------|------------------------------------------|

| 1         | 1A_DRAIN, drain voltage 1 <sup>st</sup> LNA stage input<br>A          | 50k                                          | 2.1/0                                    |

| 2         | 1A_GATE, gate voltage 1 <sup>st</sup> LNA stage input A               | 50k                                          | -0.3 <sup>[3]</sup> /-1.2 <sup>[4]</sup> |

| 3         | 1AB_ISET, input to set 1 <sup>st</sup> LNA stage<br>quiescent current | 32k-10M                                      | 2.2 <sup>[3]</sup> /0 <sup>[4]</sup>     |

| 4         | XOP, crystal pin 1                                                    | 33k                                          | 1.7                                      |

| 5         | 2AB_TYPSEL, 2nd stage LNA type selection                              | 4M– 5M                                       | 2.5                                      |

| 6         | XON, crystal pin 2                                                    | 33k                                          | 1.7                                      |

| 7         | 2AB_ISET, input to set 2 <sup>nd</sup> LNA stage quiescent current    | >100M                                        | 2.2                                      |

| 8         | 1B_GATE, gate voltage 1 <sup>st</sup> LNA stage input B               | 50k                                          | -1 <sup>[5]</sup> /-0.4 <sup>[6]</sup>   |

| 9         | 1B_DRAIN, drain voltage 1 <sup>st</sup> LNA stage input<br>B          | 50k                                          | 0 <sup>[5]</sup> /2.1 <sup>[6]</sup>     |

| 10        | B_RF_GND, ground to RF B input                                        | 0                                            | 0                                        |

| 11,<br>12 | B_RFIN                                                                | 2                                            | 0                                        |

| 13        | B_RF_GND, ground to RF B input                                        | 0                                            | 0                                        |

| 14        | 2B_DRAIN, drain voltage 2 <sup>nd</sup> LNA stage input<br>B          | 55k                                          | 0 <sup>[5]</sup> /2.1 <sup>[6]</sup>     |

| 15        | 2B_GATE, gate voltage 2 <sup>nd</sup> LNA stage input B               | 65k                                          | 0.4 <sup>[5]</sup> /0.8 <sup>[6]</sup>   |

| 16        | GAIN_SET, input to set conversion gain                                | 80k                                          | 1.3                                      |

| 17        | GNDIF4                                                                | 0                                            | 0                                        |

| 18        | IFOUT4, IF output nr 4                                                | 1M                                           | 3.2 <sup>[7]</sup> /4.8 <sup>[8]</sup>   |

| 19        | VTIF4, Voltage/tone detect input for IF4                              | 22k                                          | Vin-0.2                                  |

| 20        | VTIF3, Voltage/tone detect input for IF3                              | 22k                                          | Vin-0.2                                  |

| 21    | IFOUT3, IF output nr 3                                       | 1M   | 3.2 <sup>[7]</sup> /4.8 <sup>[8]</sup> |

|-------|--------------------------------------------------------------|------|----------------------------------------|

| 22    | GNDIF3                                                       | 0    | 0                                      |

|       |                                                              |      |                                        |

| 23    | VCC, general device supply voltage                           | 22K  | 5.0                                    |

| 24    | GNDIF2                                                       | 0    | 0                                      |

| 25    | IFOUT2, IF output nr 2                                       | 1M   | 3.2 <sup>[7]</sup> /4.8 <sup>[8]</sup> |

| 26    | VTIF2, Voltage/tone detect input for IF2                     | 22k  | Vin-0.2                                |

| 27    | VTIF1, Voltage/tone detect input for IF1                     | 22k  | Vin-0.2                                |

| 28    | IFOUT2, IF output nr 2                                       | 1M   | 3.2 <sup>[7]</sup> /4.8 <sup>[8]</sup> |

| 29    | GNDIF1                                                       | 0    | 0                                      |

| 30    | POL_SWAP/MODE_SEL                                            | 137k | 2.5                                    |

| 31    | 2A_GATE, gate voltage 2 <sup>nd</sup> LNA stage input A      | 65k  | 0.8 <sup>[3]</sup> /0.4 <sup>[4]</sup> |

| 32    | 2A_DRAIN, drain voltage 2 <sup>nd</sup> LNA stage input<br>A | 55k  | 2.1 <sup>[3]</sup> /0 <sup>[4]</sup>   |

| 33    | A_RFGND, ground to RF A input                                | 0    | 0                                      |

| 34,35 | A_RFIN                                                       | 2    | 0                                      |

| 36    | A_RFGND, ground to RF A input                                | 0    | 0                                      |

AN11640

### 9. Legal information

#### 9.1 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

#### 9.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the

customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

#### 9.3 Licenses

#### Purchase of NXP <xxx> components

<License statement text>

### 9.4 Patents

Notice is herewith given that the subject device uses one or more of the following patents and that each of these patents may have corresponding patents in other jurisdictions.

<Patent ID> -- owned by <Company name>

#### 9.5 Trademarks

Notice: All referenced brands, product names, service names and trademarks are property of their respective owners.

<Name> — is a trademark of NXP B.V.

## 10. List of figures

| Fig 1.  | TFF1044 block diagram                               | 3    |

|---------|-----------------------------------------------------|------|

| Fig 2.  | Typical Quad LNB block diagram                      | 4    |

| Fig 3.  | Typical EU gain AppCAD example                      | 5    |

| Fig 4.  | Typical EU Gain AppCAD example using 2<br>BFU910    | 6    |

| Fig 5.  | Typical high gain AppCAD example using 4<br>BFU910  | 7    |

| Fig 6.  | Typical RFA/RFB input impedance                     | 8    |

| Fig 7.  | Schematic NXP Quad reference LNB                    | .10  |

| Fig 8.  | NXP Quad Reference LNB                              | .11  |

| Fig 9.  | IF path incl. bias Tee / 850 MHz trap-filter        | .13  |

| Fig 10. | Simulated S21 for shown IF path                     | .13  |

| Fig 11. | PLL reference signal with 950MHz CW IF supper-posed | . 15 |

| Fig 12. | PCB cleaned before assembly                         | .17  |

| Fig 13. | Solder paste applied                                | .18  |

| Fig 14. | repair station                                      | .19  |

| Fig 15. | soldering process 1                                 | .20  |

| Fig 16. | soldering process 2                                 | .21  |

| Fig 17. | temperature profile applied                         |      |

| Fig 18. | soldered device                                     | .23  |

| Fig 19. | X-ray of soldered device                            | .23  |

### 11. Contents

| 1.      | Introduction3                                    |

|---------|--------------------------------------------------|

| 2.      | Product Description3                             |

| 2.1     | Design considerations4                           |

| 2.2     | Noise Figure and Gain, system level example 1 5  |

| 2.3     | Noise Figure and Gain, system level example 2 6  |

| 2.4     | Noise Figure and Gain, system level example 3 7  |

| 3.      | I/O's description8                               |

| 3.1     | RF inputs, A_RFIN and B_RFIN8                    |

| 3.2     | IF outputs8                                      |

| 3.3     | PHEMT bias control9                              |

| 3.4     | LNA bias current setting9                        |

| 3.5     | Crystal pins (reference oscillator)9             |

| 3.6     | IF mode control pins (VT-IF X, 1 < X < 4)9       |

| 3.7     | Polarization Swap / Mode Select9                 |

| 3.8     | Gain Select9                                     |

| 4.      | Typical application Diagrams / Schematics 10     |

| 4.1     | Supply topology12                                |

| 4.1.1   | Regulator decoupling capacitors12                |

| 4.1.2   | TFF1044 decoupling capacitor12                   |

| 4.1.3   | The IF output Transmission Lines/ Bias Tees 13   |

| 5.      | Creating a PCB layout with TFF104415             |

| 5.1     | Recommended footprint15                          |

| 6.      | Do's and Don'ts16                                |

| 6.1     | Measuring the TFF104416                          |

| 6.1.1   | Noise Figure16                                   |

| 6.1.1.1 | Measuring Noise Figure off XO grid16             |

| 6.1.1.2 | Measuring Noise Figure at LO spurious            |

| 6.2     | Avoid choosing too high resistor value in the VT |

|         | detect line16                                    |

| 6.3     | Keep symmetry in XO lines16                      |

| 7.      | Soldering TFF1044 in workshop environment 17     |

| 8.      | Typical measurement values24                     |

| 8.1     | DC voltages at each pin*3):24                    |

| 9.      | Legal information26                              |

| 9.1     | Definitions26                                    |

|     | Disclaimers     |    |

|-----|-----------------|----|

| 9.3 | Licenses        | 26 |

| 9.4 | Patents         | 26 |

| 9.5 | Trademarks      | 26 |

| 10. | List of figures | 27 |

| 11. | Contents        | 28 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in the section 'Legal information'.

#### © NXP B.V. 2015.

#### All rights reserved.

For more information, visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 4 June 2015 Document identifier: AN11640