# AN11639 BGU7061 evaluation board application note Rev. 1 — 24 April 2015

Application note

#### **Document information**

| Info                | Content                                                                                                                                                                                                                                                                                 |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Keywords            | BGU7061, LNA-VGA, IP3 <sub>i</sub> , NF, PCB, P <sub>i(1dB)</sub> , dynamic range.                                                                                                                                                                                                      |

| Abstract            | This application note describes the evaluation board (EVB) design and typical performance of the BGU7061. The BGU7061 is a fully integrated analog-controlled variable gain amplifier module. This EVB is supplied with all necessary connectors in order to enable ease of evaluation. |

| Ordering info       | Board number: OM7935, BGU7061<br>12NC: 9340 662 13598                                                                                                                                                                                                                                   |

| Contact information | For more information, please visit: http://www.nxp.com                                                                                                                                                                                                                                  |

#### **BGU7061** evaluation board

#### **Revision history**

| Rev | Date     | Description        |

|-----|----------|--------------------|

| 1   | 20150424 | First publication. |

#### **Contact information**

For more information, please visit: <a href="http://www.nxp.com">http://www.nxp.com</a>

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

**BGU7061** evaluation board

#### 1. Introduction

This application note gives a description of the BGU7061 evaluation board.

This enables ease of evaluation; it provides the EVB circuit schematic, the bill of materials (BOM), PCB material information and artwork. It also provides a list of equipment for a typical evaluation set up, as well as typical test results of the BGU7061.

This fully supplied EVB can be ordered from the NXP website www.nxp.com

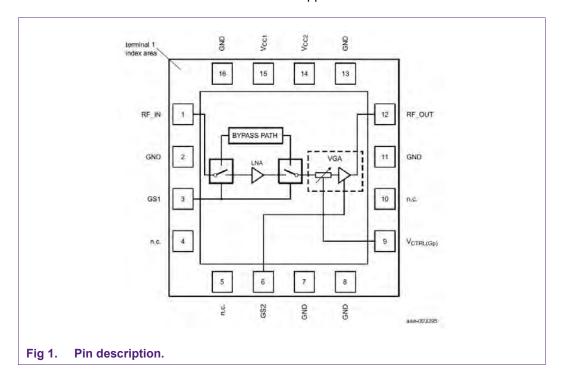

### 2. Product description

NXP semiconductors' BGU7061 is a fully integrated analog-controlled variable gain amplifier module. Its low noise and high linearity performance makes it ideal for sensitive receivers in cellular base station applications. The BGU7061 is operating in the 770 MHz to 915 MHz frequency range (covering FDD LTE bands 8, 13, 18, 19, and 20) and has a gain control range of 35 dB. At maximum gain the noise figure is 0.85 dB. The gain is analog-controlled having maximum gain at 0 V and minimum gain at 3.3 V. The LNA can be bypassed extending the dynamic range. The BGU7061 is internally matched to 50 Ohm, meaning no external matching is required, enabling ease of use. It is housed in a 16 pins 8x8x1.3mm leadless HLQFN16R package SOT1301. The BGU7061 can operate from 4.75V to 5.25 single supply and consumes about 230 mA in high gain mode (LNA active) and about 190mA in the low gain mode (LNA bypassed)

BGU7061 is one of a series of LNA-VGA products for the different frequency bands intended for cellular base stations and its related applications.

**BGU7061** evaluation board

#### 3. BGU7061 Evaluation board

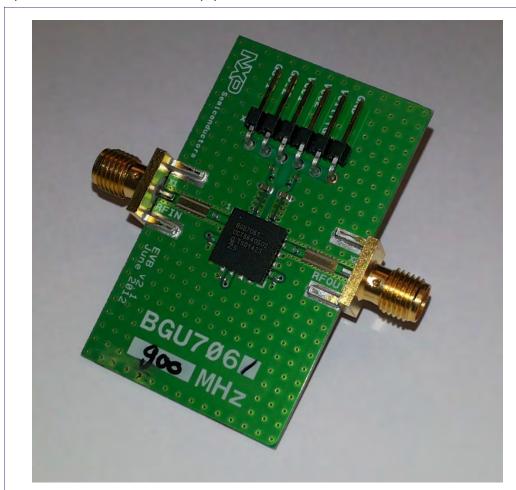

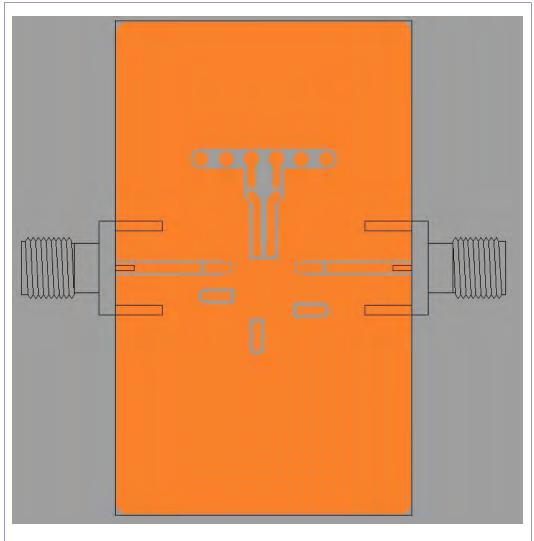

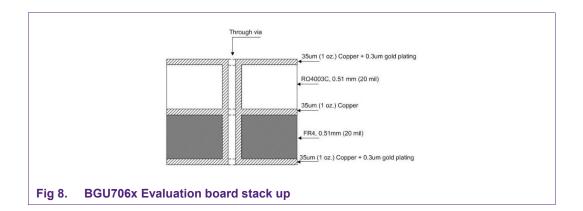

The BGU7061 evaluation board, (see Fig 2) is fabricated on a 1mm thick 3 layer PCB that uses 0.5mm R4003C for the RF performance and 0.5mm Fr4 for the mechanical strength of the PCB. The board is fully assembled with the BGU7061, including the external components. The board is supplied with two SMA connectors for input and output connection to the RF test equipment.

Fig 2. Evaluation Board

#### **BGU7061** evaluation board

#### 3.1 Application circuit

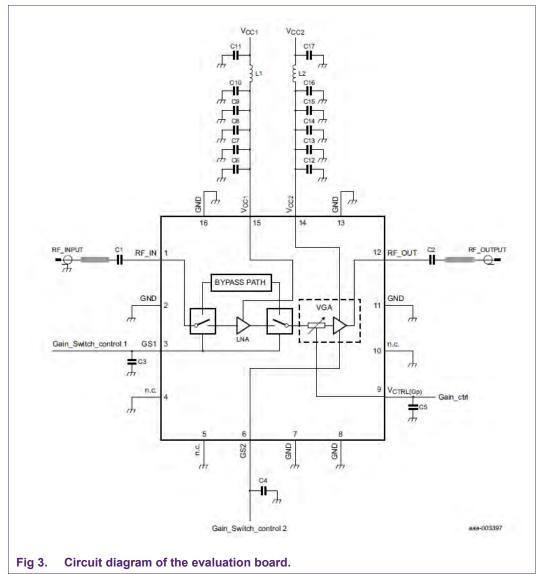

The circuit diagram of the evaluation board is shown in Fig 3

Since the BGU7061 is fully integrated the evaluation board only needs two AC coupling capacitors on the RF input and RF output, as well as bias decoupling circuits on Vcc1 and Vcc2, GS1, GS2,  $V_{CTRL(GP)}$ .

#### 3.2 Decoupling structure.

Applying the BGU7061 in e.g. wireless base station BST, ask for careful Vcc decoupling in order to get the optimal and stable performance of the product especially on NF.

If the LNA\_VGA module is supplied via supply rail that supplies more components, lack of decoupling can degrade the performance.

**BGU7061** evaluation board

## 3.3 PCB Layout information

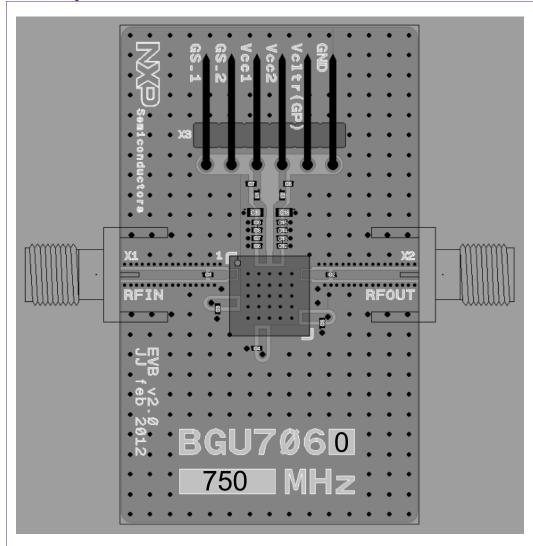

Fig 4. BGU7061 evaluation board component placement

#### **BGU7061** evaluation board

Table 1. BOM of the BGU7061 evaluation board

Table description (optional)

| Designator         | Description         | Footprint            | Value | Supplier Name/type                                           |               |

|--------------------|---------------------|----------------------|-------|--------------------------------------------------------------|---------------|

| U1                 | BGU7061             | 8x8x1.3mm<br>16 pins |       | HLQFN16R                                                     |               |

| PCB                |                     | 20x30mm              |       | BGU706x EVB v2.1<br>June 2012                                |               |

| C1,C2              | Capacitor           | 0402                 | 150pF | Murata GRM1555                                               | AC coupling   |

| C3-C5              | Capacitor           | 0402                 | 100pF | Murata GRM1555                                               | Decoupling    |

| C6,C12             | Capacitor           | 0402                 | 100pF | Murata GRM1555                                               | Decoupling    |

| C11,C17            | Capacitor           | 0402                 | 100nF | Murata GRM1555                                               | Decoupling    |

| C7-C10,<br>C13-C16 | -                   | -                    | -     | -                                                            | Not assembled |

| L1,L2              | Inductor            | 0402                 | 10nH  | Murata LQG15                                                 | Decoupling    |

| X1,X2              | SMA RF<br>connector | -                    | -     | Johnson, End launch<br>SMA 142-0701-841                      |               |

| X3                 | DC header           | -                    | -     | Molex, PCB header,<br>right angle, 1 row 6<br>way 90121-0766 |               |

Fig 5. BGU706x Evaluation board Top layer PCB layout

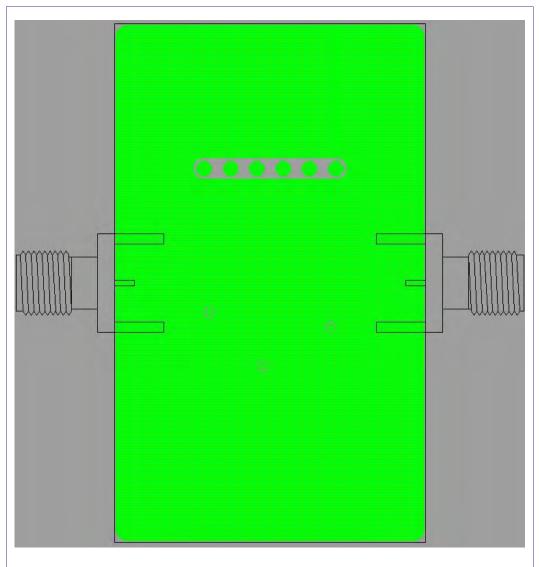

Fig 6. BGU706x Evaluation board inner layer PCB layout

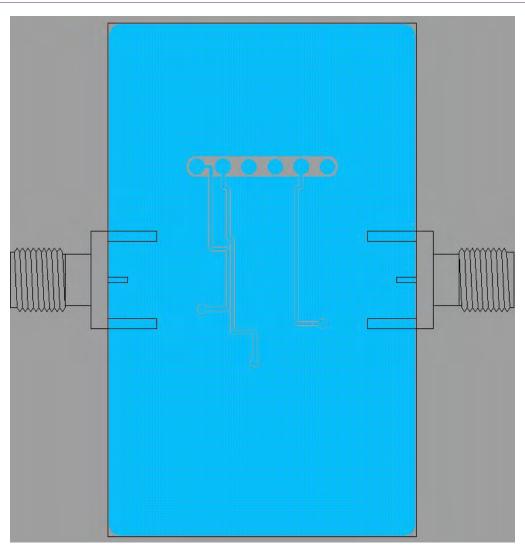

Fig 7. BGU706x Evaluation board bottom layer PCB layout

#### **BGU7061** evaluation board

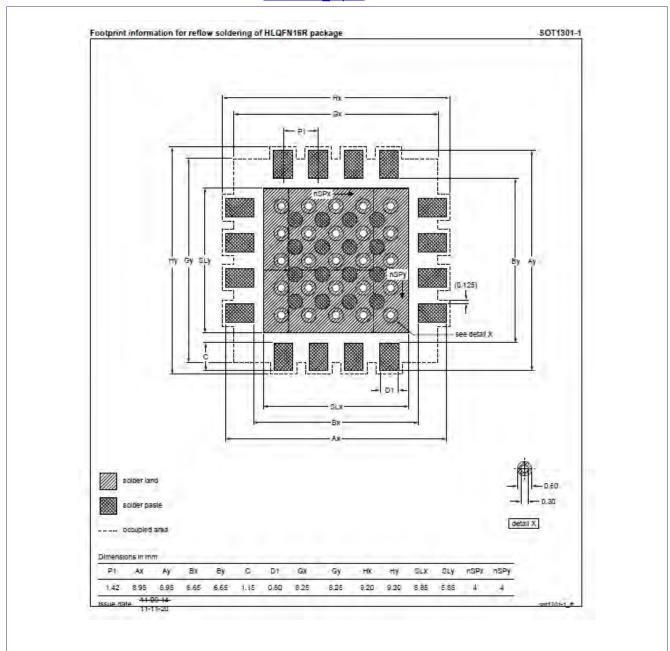

#### 3.4 Recommended footprint

A good PCB layout is an essential part of an RF circuit design. The BGU7061 evaluation board can serve as a guideline for laying out a board using the BGU7061. Both RF input and RF output lines are controlled impedance lines. Vcc1 and Vcc2 are decoupled by a  $\Pi$  filter decoupling. The recommended footprint for reflow soldering can be found in Fig 9 as well as via this link sot1301-1 fr.pdf.

Fig 9. Recommended footprint specification for the HLQFV16R

**BGU7061** evaluation board

#### 4. Test Setup

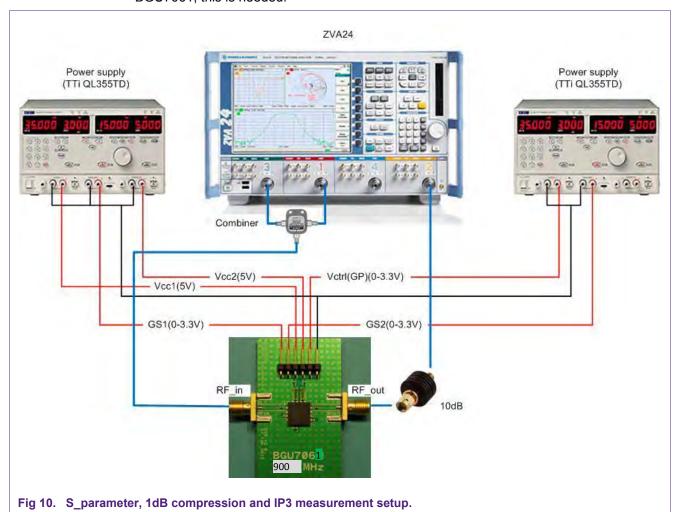

#### 4.1 S\_Parameter,1dB compression, IIP3, measurement setup

The BGU7061 EVB is fully assembled and tested.

Fig 10 Shows the measurements setup that is used to evaluate the BGU7061 EVB for S\_parameters Gain, IRL ORL Reverse Isolation), 1dB gain compression as well as IIP3. It is intended as a guide only, substitutions are possible. The 10dB attenuator in the output path is recommended in order to avoid overdriving the analyzers receiver port when measuring 1 dB gain compression. Especially in the high gain mode of the BGU7061, this is needed.

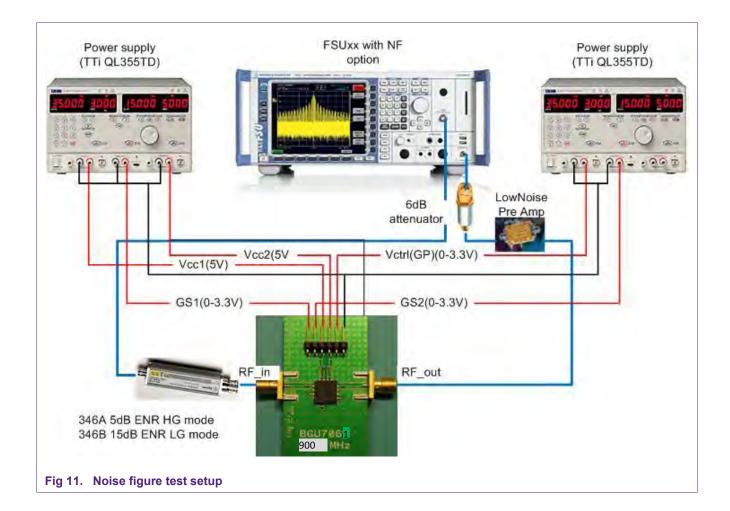

#### 4.2 Noise figure measurement setup

In Fig 11 the noise figure measurement set-up is shown, this is also intended as a guide only, substitutions can be made. For the High gain mode of the BGU7061 it is recommended to use a 5dB ENR noise source, for the Low gain a 15 dB ENR noise source recommended. To achieve to lowest possible setup noise figure an external pre amplifier might be necessary, but since this will make the total gain in the highest gain setting of the BGU7061 to high a 6dB attenuator is needed to avoid overdriving the input of the spectrum analyzer.

**BGU7061** evaluation board

# 5. Typical operating performance.

A detailed overview of the performance of the BGU7061 can be found in de <u>Datasheet</u>. In <u>Table 2</u> and <u>Table 3</u> the typical performance at 900 MHz in High- and Low-gain is given.

Table 2. Typical performance high gain mode

GS1=LOW; GS2=HIGH; Vcc1=5V; Vcc2=5V; f=900MHz; Tamb=25°C; input and output 50Ω; unless otherwise specified.

| Symbol                | Parameter                            | Conditions                                       | Тур   | Unit |

|-----------------------|--------------------------------------|--------------------------------------------------|-------|------|

| ICC(tot)              | total supply current                 |                                                  | 229   | mA   |

| $G_{p(min)}$          | minimum power gain                   | $V_{ctrl(Gp)} = 3.3 \text{ V}$                   | 12.7  | dB   |

| G <sub>p</sub> (max)  | maximum power gain                   | $V_{ctrl(Gp)} = 0 V$                             | 36.7  | dB   |

| G <sub>p</sub> (flat) | power gain flatness                  | 880 MHz≤ f ≤915 MHz                              | 0     | dB   |

|                       |                                      | 18 dB≤ G <sub>p≤</sub> 35 dB                     |       |      |

| NF                    | noise figure                         | V <sub>ctrl(Gp)</sub> = 0 V(maximum power gain)  | 0.74  | dB   |

|                       |                                      | G <sub>p</sub> = 35 dB                           | 0.87  | dB   |

|                       |                                      | G <sub>p</sub> = 18 dB                           | 6.47  | dB   |

| IP3ı                  | input third-order intercept point    | 2-tone; tone-spacing = 1.0 MHz                   |       |      |

|                       |                                      | G <sub>p</sub> = 35 dB                           | 2.0   | dBm  |

|                       |                                      | Gp = 30 dB                                       | 4.8   | dBm  |

|                       |                                      | G <sub>p</sub> = 29 dB                           | 5.0   | dBm  |

|                       |                                      | G <sub>p</sub> = 18 dB                           | 6.3   | dBm  |

| Pi(1dB)               | input power at 1 dB gain compression | Gp = 35 dB                                       | -12.5 | dBm  |

|                       |                                      | G <sub>p</sub> = 30 dB                           | -7.6  | dBm  |

|                       |                                      | G <sub>p</sub> = 29 dB                           | -6.8  | dBm  |

|                       |                                      | G <sub>p</sub> = 18 dB                           | -4.8  | dBm  |

| RLin                  | input return loss                    | V <sub>ctrl(Gp)</sub> = 0 V(maximum power gain)  | 30.5  | dB   |

|                       |                                      | G <sub>p</sub> = 35 dB                           | 28.0  | dB   |

| RLout                 | output return loss                   | V <sub>ctrl(Gp)</sub> = 0 V (maximum power gain) | 17.5  | dB   |

| K                     | Rollett stability factor             | 0 GHz≤ f ≤ 12.75 GHz                             | >1    |      |

|                       |                                      |                                                  |       |      |

#### **BGU7061** evaluation board

Table 3. Typical performance low gain mode

GS1=HIGH; GS2=LOW; Vcc1=5V; Vcc2=5V; f=900MHz; Tamb=25°C; input and output 50Ω; unless otherwise specified.

| Symbol              | Parameter                            | Conditions                                       | Тур  | Unit |

|---------------------|--------------------------------------|--------------------------------------------------|------|------|

| ICC(tot)            | total supply current                 |                                                  | 199  | mA   |

| Gp(min)             | minimum power gain                   | $V_{ctrl(Gp)} = 3.3 \text{ V}$                   | -5.9 | dB   |

| G <sub>p(max)</sub> | maximum power gain                   | $V_{ctrl(Gp)} = 0 V$                             | 18.3 | dB   |

| Gp(flat)            | power gain flatness                  | 698 MHz≤ f ≤748 MHz                              | 0.0  | dB   |

|                     |                                      | 3 dB≤ G <sub>p≤</sub> 17 dB                      |      |      |

| NF                  | noise figure                         | G <sub>p</sub> = 17 dB                           | 11.2 | dB   |

|                     |                                      | Gp = 3 dB                                        | 22.9 | dB   |

| IP3ı                | input third-order intercept point    | 2-tone; tone-spacing = 1.0 MHz                   |      |      |

|                     |                                      | G <sub>p</sub> = 17 dB                           | 21.4 | dBm  |

|                     |                                      | Gp = 12 dB                                       | 26.5 | dBm  |

|                     |                                      | G <sub>p</sub> = 11 dB                           | 27.5 | dBm  |

|                     |                                      | G <sub>p</sub> = 3 dB                            | 31.2 | dBm  |

| Pi(1dB)             | input power at 1 dB gain compression | G <sub>p</sub> = 17 dB                           | 5.6  | dBm  |

|                     |                                      | G <sub>p</sub> = 12 dB                           | 10.4 | dBm  |

|                     |                                      | G <sub>p</sub> = 11 dB                           | 11.1 | dBm  |

|                     |                                      | Gp = 3 dB                                        | 13.2 | dBm  |

| RLin                | input return loss                    | V <sub>ctrl(Gp)</sub> = 0 V(maximum power gain)  | 25.1 | dB   |

|                     |                                      | G <sub>p</sub> = 17 dB                           | 22.7 | dB   |

| RLout               | output return loss                   | V <sub>ctrl(Gp)</sub> = 0 V (maximum power gain) | 18.3 | dB   |

| K                   | Rollett stability factor             | 0 GHz≤ f ≤ 12.75 GHz                             | >1   |      |

|                     |                                      |                                                  |      |      |

#### 6. Customer Evaluation Kit

The Evaluation Kit will come in an ESD shielded bag labeled like below It will include 1 EVB.

Fig 12. BGU7061 Customer evaluation kit.

#### **BGU7061** evaluation board

### 7. Legal information

#### 7.1 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

#### 7.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or

customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

#### 7.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are property of their respective owners.

16 of 19

#### **BGU7061** evaluation board

# 8. List of figures

| Fig 1.  | Pin description.                                        | .3 |

|---------|---------------------------------------------------------|----|

| Fig 2.  | Evaluation Board                                        | .4 |

| Fig 3.  | Circuit diagram of the evaluation board                 | .5 |

| Fig 4.  | BGU7061 evaluation board component placement            | .6 |

| Fig 5.  | BGU706x Evaluation board Top layer PCB layout           | .8 |

| Fig 6.  | BGU706x Evaluation board inner layer PCB layout         | .9 |

| Fig 7.  | BGU706x Evaluation board bottom layer PCB layout        | 10 |

| Fig 8.  | BGU706x Evaluation board stack up                       | 10 |

| Fig 9.  | Recommended footprint specification for the HLQFV16R    | 11 |

| Fig 10. | S_parameter, 1dB compression and IP3 measurement setup. | 12 |

| Fig 11. | Noise figure test setup                                 |    |

| Fig 12. | BGU7061 Customer evaluation kit                         | 15 |

#### **BGU7061** evaluation board

# 9. List of tables

| Table 1. | BOM of the BGU7061 evaluation board7 |

|----------|--------------------------------------|

| Table 2. | Typical performance high gain mode14 |

| Table 3. | Typical performance low gain mode15  |

#### **BGU7061** evaluation board

# 10. Contents

| 1.  | Introduction                       | 3  |

|-----|------------------------------------|----|

| 2.  | Product description                | 3  |

| 3.  | BGU7061 Evaluation board           | 4  |

| 3.1 | Application circuit                | 5  |

| 3.2 | Decoupling structure               | 5  |

| 3.3 | PCB Layout information             | 6  |

| 3.4 | Recommended footprint              | 11 |

| 4.  | Test Setup                         | 12 |

| 4.1 | S_Parameter,1dB compression, IIP3, |    |

|     | measurement setup                  | 12 |

| 4.2 | Noise figure measurement setup     | 12 |

| 5.  | Typical operating performance      | 14 |

| 6.  | Customer Evaluation Kit            | 15 |

| 7.  | Legal information                  | 16 |

| 7.1 | Definitions                        | 16 |

| 7.2 | Disclaimers                        | 16 |

| 7.3 | Trademarks                         | 16 |

| 8.  | List of figures                    | 17 |

| 9.  | List of tables                     | 18 |

| 10  | Contents                           | 19 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in the section 'Legal information'.