# AN11415

PTN3355 PCB Layout Guideline, Reference Schematics and<br/>BOMRev. 1 — 16 December 2014Application no

**Application note**

#### **Document information**

| Info     | Content                                                                                |

|----------|----------------------------------------------------------------------------------------|

| Keywords | DisplayPort, PTN3355                                                                   |

| Abstract | This document provides a practical guideline to PTN3355 application design and layout. |

#### **Revision history**

| Rev | Date     | Description     |

|-----|----------|-----------------|

| 1   | 20141216 | Initial version |

# **Contact information**

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

AN11415

All information provided in this document is subject to legal disclaimers.

# 1. Introduction

This document provides a guideline for PTN3355 application and layout guide line in ULT notebook, docking station and dongle designs.

PTN3355 is low power DisplayPort to VGA bridge IC with integrated 1-2 VGA switch. PTN3355 is in an HVQFN40 package, 6 mm x 6 mm, with 0.5 mm pitch. PTN3355 consumes approximately 200 mW of power for video streaming in WUXGA resolution and 890 uW of power in low-power mode. The VGA output is powered down when there is no valid DisplayPort source data being transmitted. PTN3355 is suitable for Ultra Low Power Notebook and other low power devices. PTN3355 also offers second VGA port for docking design.

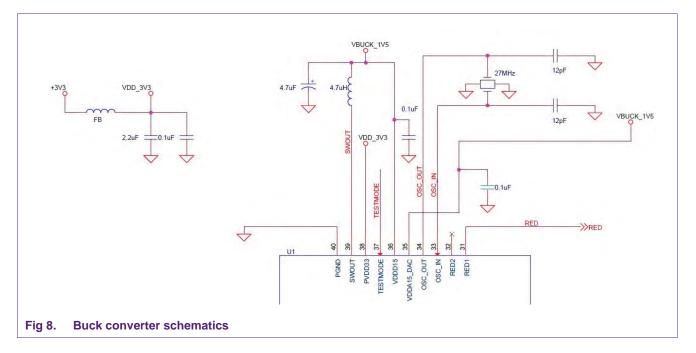

PTN3355 is powered from a 3.3 V power supply, and generated 1.5 V through an internal step-down switch regulator and buck converter for internal core usage and DAC usage.

## 2. Reference designs

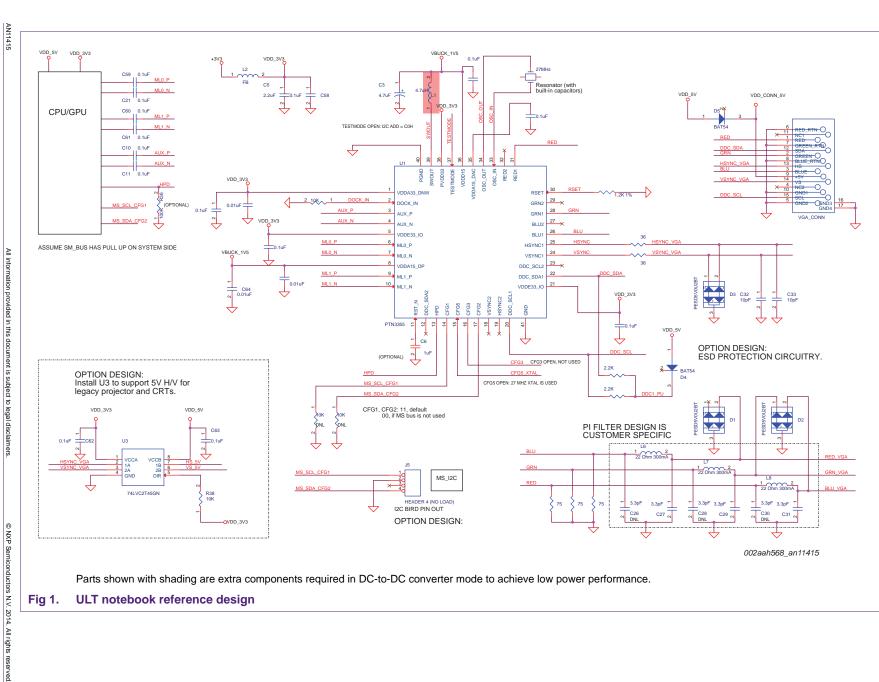

#### 2.1 ULT notebook design

PTN3355 can be connected directly to the DP lanes on mother board, or on docking station.

Connect PTN3355 to one of the DP ports on PCH/GPU with 0.1uF AC caps in series for DP data lanes and AUX lanes. PTN3355 probably will be used as a primary display; make sure the BIOS is set accordingly.

Below is a reference design for one VGA application.

AN11415

Application note

Rev. 1

I

16 December 2014

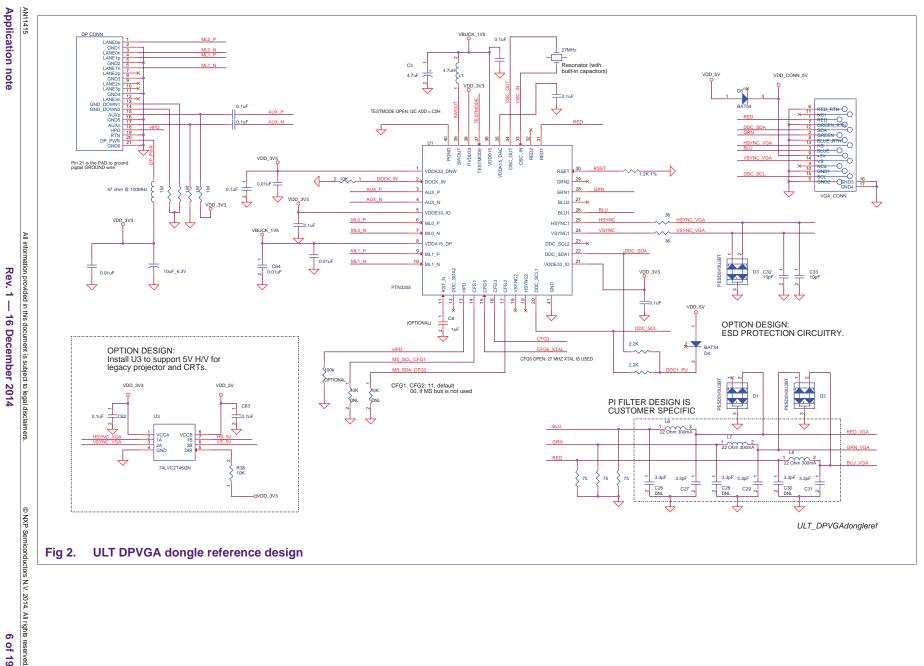

#### 2.2 Dongle design

PTN3355 can also be used on DP-VGA dongles.

Connect PTN3355 DPVGA to one of the DP ports on the system board.

DPVGA dongle gets 3V3 power from DP connector for PTN3355 IC operation, then boost up to 5 V for VGA connector.

**Application note**

NXP Semiconductors

PTN3355 PCB Layout Guideline, Reference Schematics and BOM

AN11415

# Rev. 1 — 16 December 2014

6 of 19

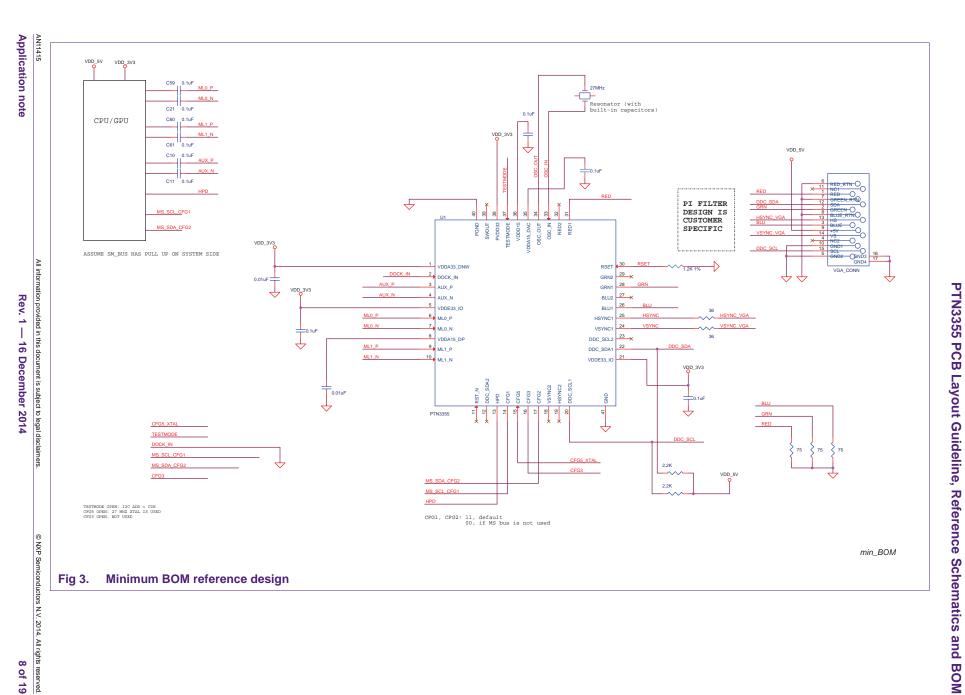

#### 2.3 Minimum BOM design

For cost conscious application, PTN3355 needs only a handful of components to function.

Below is a minimum BOM design for embedded or dongle design.

**Application note**

AN11415

# 3. Buck converter

#### 3.1 Buck converter layout guideline

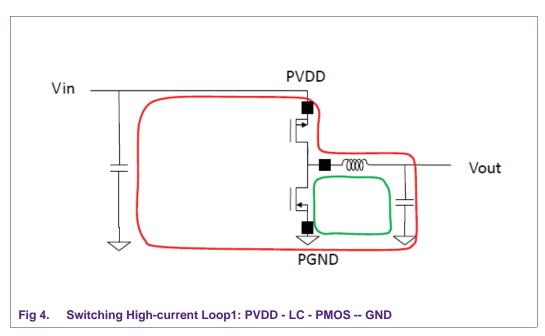

PTN3355 utilizes a switch mode power supply to deliver the power needed with high efficiency. Switch mode power supplies require careful attention to the PC board layout.

PTN3355 PCB Layout Guideline, Reference Schematics and BOM

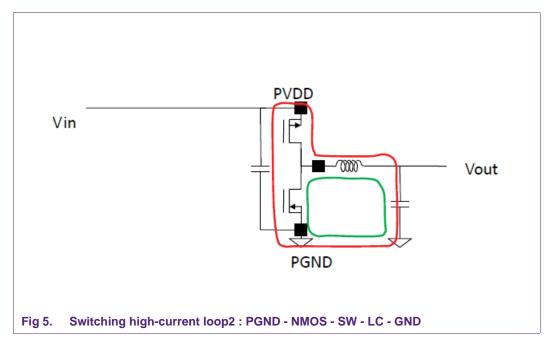

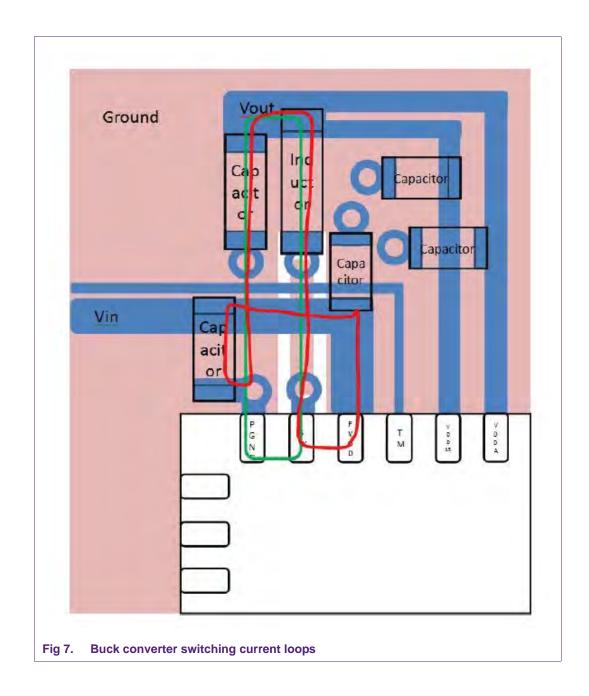

There are two switching high-current loops formed by the switching action of the buck converter. One loop is formed by the current that flows from the input capacitor through the PVDD pin of the part, through the internal PMOS High-side switch, out the SW pin, through the inductor and the load capacitor to the analog ground, and through the ground plane back to the ground connection of the input capacitor. A second switching high current loop is formed when the low-side NMOS switch is on. The current flows from the PGND pin of the part through the internal NMOS switch, out the SW pin, through the inductor and the load capacitor, to the analog ground, and through the ground plane back to the PGND pin of the part.

To minimize electromagnetic interference (EMI), it is essential to minimize the length and area of the switching high current loops. It is also critical that the two switching current paths are matched as closely as possible.

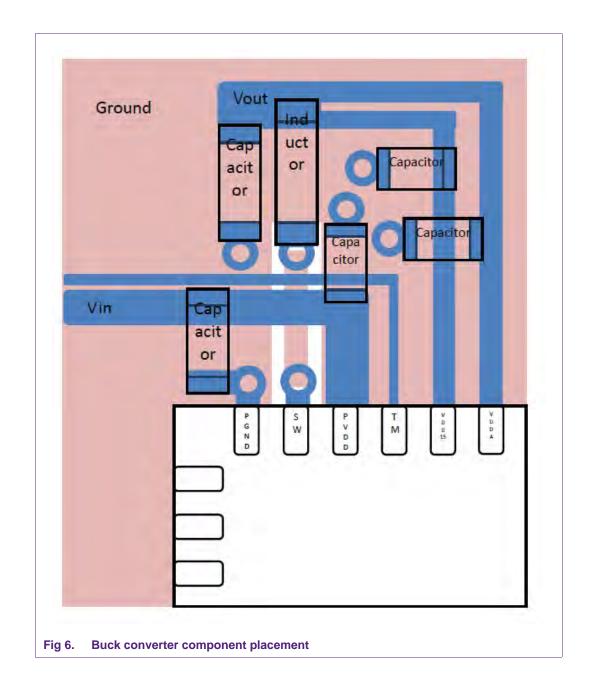

Here are some guidelines for PC board design:

- Connect the exposed paddle of the IC to the PC board ground plane.

- Place the input capacitor as close to the PVDD pin as possible.

- Place the inductor and the load capacitor as close to the SW pin as possible.

- Keep the traces for the input capacitor, inductor and the output capacitor, short, direct and wide.

- Do not connect the PGND pin directly to the ground plane, instead, connect the PGND pin and the input capacitor's ground pin to the ground plane at the same point.

- Minimize the distance between the input capacitor's ground and the ground of the load capacitor.

- Keep the trace for the FB (Vout to VDD1V5) away from the switching high current paths.

The following is a proposed PC board layout scheme for the PTN3355 which minimizes the area of the two switching current loops and matches the current flow paths for the two loops as closely as possible.

Note the smaller capacitors are 0.1 uF caps that must be place as close to the pin as possible.

#### 3.2 Buck converter schematic

# 4. DP receiver interface

Main differential pairs and AUX channel are routed with 100 Ohm impedance. The important parameters to calculate the impedance are:.

- PCB thickness

- Distance to ground plane

- Trace width

- Trace spacing

- PCB permittivity

Guard grounds are used to isolate the pair. This helps to eliminate cross talk between traces. Trace lengths are matched on the same pair to 0.01". Inter pair match to 1".

AC caps for DP lanes and AUX pair should be placed close to the DP interface.

When signals change plane, the ground plane need to move along to keep constant trace impedance. On DPVGA a ground island is inserted on the VCC plane for this purpose.

# 5. VGA interface

| Table 1. Design guid       | delines for VGA connector, PWB to cable junct                                                                                                                                                                            | ion                                   |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Design guideline<br>number | Design guideline description                                                                                                                                                                                             | Approximate impact<br>on EMI decrease |

| 1                          | Define the 2nd PWB layer as ground plane                                                                                                                                                                                 |                                       |

| 2                          | Connect the ground chassis pins of the VGA<br>PWB-connector                                                                                                                                                              | 25 dB                                 |

| 3                          | Use an upper ground plane around VGA<br>connector pins. This design guideline makes no<br>sense when it is not combined with design<br>guideline 4.                                                                      |                                       |

| 4                          | Use enough vias to connect the upper ground<br>plane with main ground plane in 2nd PWB layer.<br>Enough means around every 3 mm (stitching)                                                                              | 20 dB                                 |

| 5                          | Ensure proper connection between<br>PWB-connector chassis and upper ground<br>plane by using contact springs (at least 3<br>contact points).<br>Emission improvement when either 1 or 3<br>contacts were used was 10 dB! | 10 dB                                 |

| 6                          | Apply ferrite bead around VGA cable (is already very common for typical cables available from the market)                                                                                                                | 3 dB                                  |

Following the recommended guidelines, all RGB traces on DPVGA board are routed with 75 Ohm impedance from PTN3355 to VGA connector. Ground fills are used to isolate these traces. Ground fills are connected to ground plane with vias.

# 6. PCB stack up

4-layer FR4 PCB is sufficient for PTN3355 DP-VGA layout. Suggested layers:

- 1. Signal layer 1 for DPs, with ground cover the entire buck converter area plus power islands or thick traces for Vin and Vout for buck converter.

- 2. Ground layer

- 3. Power layer with VDD\_3V3 island to cover entire PTN3355, except pin 39, 36, 35 and pin 8.

- 4. Signal layer 2

#### Table 2. PCB stack up

| PCB stack up<br>Thickness (mil) |            | Impedance                                                     |        |                                        |         |

|---------------------------------|------------|---------------------------------------------------------------|--------|----------------------------------------|---------|

|                                 |            |                                                               |        |                                        |         |

| copper + plating                | 0.70 mils  | $9.45$ mils, $50\Omega\pm10$ % 3.55 mils, $75\Omega\pm10$ %   | 53.09Ω | $5.9/5.5/5.9$ mils, $100\Omega\pm10$ % | 101.26Ω |

| Prepreg                         | 4.70 mils  |                                                               |        |                                        |         |

| copper                          | 1.40 mils  |                                                               |        |                                        |         |

| core                            | 47.20 mils |                                                               |        |                                        |         |

| copper                          | 1.40 mils  |                                                               |        |                                        |         |

| Prepreg                         | 4.70 mils  |                                                               |        |                                        |         |

| copper + plating                | 0.70 mils  | 9.45 mils, 50 $\Omega\pm$ 10 % 3.55 mils, 75 $\Omega\pm$ 10 % | 53.09Ω | $5.9/5.5/5.9$ mils, $100\Omega\pm10$ % | 101.26Ω |

| Solder mask                     | 0.50 mils  |                                                               |        |                                        |         |

| TOTAL                           | 61.80 mils |                                                               |        |                                        |         |

|                                 | 1.57 mm    |                                                               |        |                                        |         |

AN11415

# 7. PTN3355 on notebook BOM

|    | Y Reference                                              | Value       | PCB Footprint | Feature                          | Manufacturer    | Maufacturer Number    | Vendor N.                 | Load Option |

|----|----------------------------------------------------------|-------------|---------------|----------------------------------|-----------------|-----------------------|---------------------------|-------------|

| 1  | 2 C1,C4                                                  | 12pF        | rc0402        | CAP CER 12PF 50V 5% NP0 0402     | Murata          | GRM1555C1H120JZ01D    | Digikey, 490-1279-2-ND    | LOAD        |

| 2  | C2,C8,C10,C11,C13,C19,C20,<br>13 C21,C23,C58,C59,C60,C61 | ),<br>0.1uF | rc0201        | CAP CER 0.1UF 10V 10% X5R 0201   | TDK Corporation | CO603X5R1A104K        | Digikev, 445-7318-2-ND    | LOAD        |

|    | 13                                                       | 4.7uF       | rc1206        | CAP CER 4.7UF 16V 10% X7R 1206   | TDK             | C3216X7R1C475K/1.60   | Digikey, 445-1385-2-ND    | LOAD        |

| 4  | 1 C5                                                     | 2.2uF       | rc0603        | CAP CER 2.2UF 10V 10% X5R 0603   | Taiyo Yuden     | LMK107BJ225KA-T       | Digikey, 587-1253-2-ND    | LOAD        |

| 9  | 2 C14,C24                                                | 0.01uF      | rc0201        | CAP CER 10000PF 10V 10% X5R 0201 | TDK Corporation | C0603X5R1A103K        | Digikey, 445-1793-2-ND    | LOAD        |

| 60 | 3 C27,C29,C31                                            | 3.3pF       | rc0402        | CAP CER 3.3PF 50V NP0 0402       | Murata          | GRM1555C1H3R3C201D    | Digikey, 490-1270-2-ND    | LOAD        |

| 6  | 2 C32,C33                                                | 10pF        | rc0402        | CAP CER 10PF 50V 5% NPO 0402     | Yageo           | CC0402JRNPO9BN100     | Digikey, 311-1014-2-ND    | LOAD        |

| 11 | 3 D1,D2,D3                                               | PESD5V0U2BT | SOT-23        | DIODE ULOW ESD PROTECTION SOT-23 | NXP             | PESD5V0U2BT,215       | Digikey, 568-4296-2-ND    | LOAD        |

| 12 | 1 D4                                                     | BAT54       | S0T23         | DIODE SCHOTTKY 30V 200MA SOT23-3 | Diode           | BAT54TA               | Digikey, BAT54TR-ND       | LOAD        |

| 13 | 1 D5                                                     | BAT54       | SOD80C        | DIODE SS SWITCH 60V 250MA SOD80  | Vishay          | BAV100-GS08           | Digikey, BAV100-GS08TR-ND | LOAD        |

| 14 | 111                                                      | VGA_CONN    | DB-15_HD      | CONN D-SUB RCPT 15POS HD R/A     | EDAC            | 634-015-274-992       | Digikey, 151-1125-ND      | LOAD        |

| 16 | 111                                                      | 4.7uH       | rc1210        | IND 4.7uH, 1210, 20%             | Panasonic       | EU-PA4R7MF2           | Digikey, PCD2336TR-ND     | LOAD        |

| 17 | 112                                                      | 8           | rc1206        | FERRITE 3A 100 OHM 1206 SMD      | Laird-Signal    | HI1206N101R-10        | Digikey, 240-2408-2-ND    | LOAD        |

| 18 | 3 16,17,18                                               | 47nH        | rc0402        | INDUCTOR 47NH 200MA 0402         | Murata          | LQG15HS47NJ02D        | Digikey, 490-2631-2-ND    | LOAD        |

| 19 | 1 R16                                                    | 1.2K 1%     | rc0402        | RES 1.20K OHM 1/10W 1% 0402 SMD  | Pansonic        | ERJ-2RKF1201X         | Digikey, P1.20KLTR-ND     | LOAD        |

| 20 | 2 R29,R30                                                | 36          | rc0402        | RES 36 OHM 1/16W .5% 0402 SMD    | Pansonic        | ERA-2AKD360X          | Digikey, P36DDTR-ND       | LOAD        |

| 21 | 3 R31,R32,R33                                            | 75          | rc0402        | RES 75.0 OHM 1/10W 1% 0402 SMD   | Pansonic        | ERJ-2RKF75R0X         | Digikey, P75.0LTR-ND      | LOAD        |

| 22 | 2 R34,R35                                                | 1.2K        | rc0603        | RES 1.2K OHM 1/10W 5% 0603 SMD   | Yageo           | RC0603JR-071K2L       | Digikey, 311-1.2KGRTR-ND  | LOAD        |

| 25 | 4 R44, R45, R54, R59                                     | 10K         | rc0201        | RES 10K OHM 1/20W 5% 0201 SMD    | Pansonic        | ERI-1GEJ103C          | Digikey, P10KAGTR-ND      | LOAD        |

| 26 | 1 01                                                     | PTN3355     | HVQFN40       | IC PTN3355 HVQFN40               | NXP             | PTN3355BS             | NXP, ptn3355BS            | LOAD        |

| 28 | 1 11                                                     | 27MHz       | 3mm2x2mm5     | CRYSTAL HYBRID 27.000MHZ 3225    | ECS             | ECS-270-20-33-CKM-TR  | Digikey, XC1818TR-ND      | LOAD        |

| 5  | 1 C6                                                     | luF         | rc0603        | CAP CER 1UF 10V 10% X5R 0603     | Murata          | GRM188R61A105KA61D    | Digikey, 490-1543-2-ND    | NO LOAD     |

| 7  | 3 C26,C28,C30                                            | 3.3pF       | rc0402        | CAP CER 3.3PF 50V NP0 0402       | Murata          | GRM1555C1H3R3C201D    | Digikey, 490-1270-2-ND    | NO LOAD     |

| 10 | 2 C62,C63                                                | 0.1uF       | rc0201        | CAP CER 0.1UF 10V 10% X5R 0201   | TDK Corporation | CO603X5R1A104K        | Digikey, 445-7318-2-ND    | NO LOAD     |

| 15 | 1 J5                                                     | HEADER 4    | hdr 4x1       | CONN HEADER . 100 SINGL STR 4POS | Sullins         | PBC04SAAN             | Digikey, S1011E-04-ND     | NO LOAD     |

| 23 | 1 R36                                                    | 100K        | rc0402        | RES 100K OHM 1/10W 5% 0402 SMD   | Pansonic        | ERI-2GEJ104X          | P100KJTR-ND               | NO LOAD     |

|    | R38,R48,R51,R52,R53,R55,R5                               |             |               |                                  |                 | the set of section of |                           |             |

| 24 | 8 8,R60                                                  | 10K         | rc0201        | RES 10K OHM 1/20W 5% 0201 SMD    | Pansonic        | ERI-1GEJ103C          | Digikey, P10KAGTR-ND      | NO LOAD     |

| 27 | 1 U3                                                     | 74LVC2T45GN | sot1116       | Dual Tranceiver                  | NXP             | 74LVC2T45GN           | NXP, 74LVC2T45GN          | NO LOAD     |

Fig 9. Notebook BOM

PTN3355 DPVGA Reference Design Revised: Tuesday, September 24, 2013 # Revision: 0.13

# 8. HVQFN exposed center pad solder lands

PTN3355 uses HVQFN package.

The HVQFN package exposed center pad must be soldered to a corresponding solder land on the board for enhanced thermal, as well as electrical ground, performance.

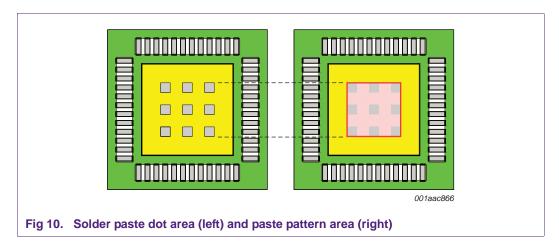

During reflow soldering, solder paste melts and gas or trapped air is released, causing splattering or solder balling. Solder balling and splatter can be minimized if the solder paste is printed as a number of individual dots, instead of one large deposit, and if the solder paste is kept at a sufficient distance from the edge of the solder land.

The solder paste pattern area should cover 35 % of the solder land area. When printing solder paste on the exposed die pad solder land, the solder paste dot area should cover no more than 20 % of this solder land area. Furthermore, the paste should be printed away from the solder land edges. This is illustrated in 01; the solder paste pattern area lies within the boundary indicated by the red line and it is divided by the entire solder land area.

# 9. References

- [1] PTN3355 datasheet, 14 July 2014

- [2] PTN3355 Reference Design Schematics, rev 0.15

- [3] AN10873.pdf, PTN3392 application design reference manual

- [4] AN10798, DisplayPort PCB Layout Guidelines

- [5] Intel Huron River Design Guide, Rev. 0.9, March 2010

# **10. Legal information**

#### 10.1 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

### 10.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

AN11415

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### 10.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

**Application note**

# **11. Contents**

| 1    | Introduction 3                           |

|------|------------------------------------------|

| 2    | Reference designs 3                      |

| 2.1  | ULT notebook design 3                    |

| 2.2  | Dongle design 5                          |

| 2.3  | Minimum BOM design 7                     |

| 3    | Buck converter                           |

| 3.1  | Buck converter layout guideline          |

| 3.2  | Buck converter schematic                 |

| 4    | DP receiver interface                    |

| 5    | VGA interface 14                         |

| 6    | PCB stack up 15                          |

| 7    | PTN3355 on notebook BOM 16               |

| 8    | HVQFN exposed center pad solder lands 17 |

| 9    | References                               |

| 10   | Legal information                        |

| 10.1 | Definitions                              |

| 10.2 | Disclaimers                              |

| 10.3 | Trademarks 18                            |

| 11   | Contents                                 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP Semiconductors N.V. 2014.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com Date of release: 16 December 2014

Document identifier: AN11415