## Quad LIN 2.2 A/SAE J2602 Transceiver

## **TJA1024HG**

Last Updated: Dec 5, 2025

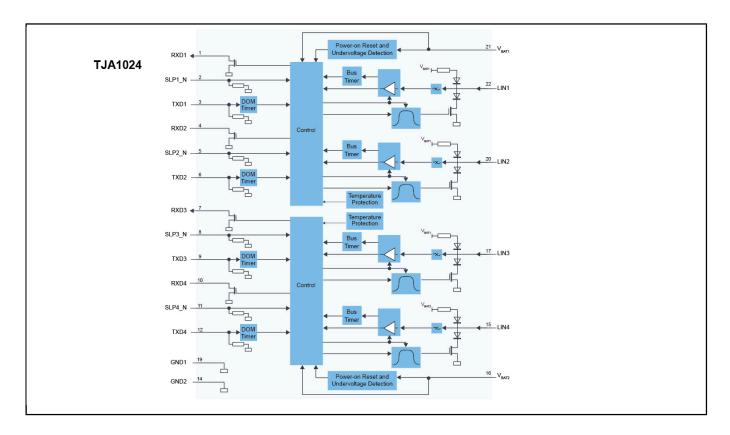

The TJA1024 is a quad LIN transceiver that provides the interface between a Local Interconnect Network (LIN) leader/follower protocol controller and the physical bus in a LIN network. It comprises two independent and separated dual LIN transceiver blocks on a single die (only the ground pins GND1 and GND2 are connected internally) with dedicated supply pins (VBAT1 for LIN 1/LIN2 and VBAT2 for LIN3/LIN4).

The TJA1024 is primarily intended for in-vehicle subnetworks using baud rates up to 20 kBd and is compliant with LIN 2.0, LIN 2.1, LIN 2.2, LIN 2.2A and SAE J2602. The TJA1024 is software compatible with the TJA1022, TJA1027 and TJA1029.

The transmit data streams generated by the protocol controller are converted by the TJA1024 into optimized bus signals shaped to minimize ElectroMagnetic Emissions (EME). The LIN bus output pins are pulled HIGH via internal termination resistors. For a leader application, an external resistor in series with a diode should be connected between pin VBATx and the respective LIN pins. The receivers detect receive data streams on the LIN bus input pins and transfer them via pins RXDx to the microcontroller.

Power consumption is very low when all four transceivers are in Sleep mode. However, the TJA1024 can still be woken up via pins LINx and SLPx\_N.

## **TJA1024 Block Diagram Block Diagram**

View additional information for Quad LIN 2.2 A/SAE J2602 Transceiver.

Note: The information on this document is subject to change without notice.

## www.nxp.com

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2025 NXP B.V.