## **LPC SPIFI Peripheral**

## SPIFI-NXP-MICROCONTROLLERS

Last Updated: Apr 10, 2022

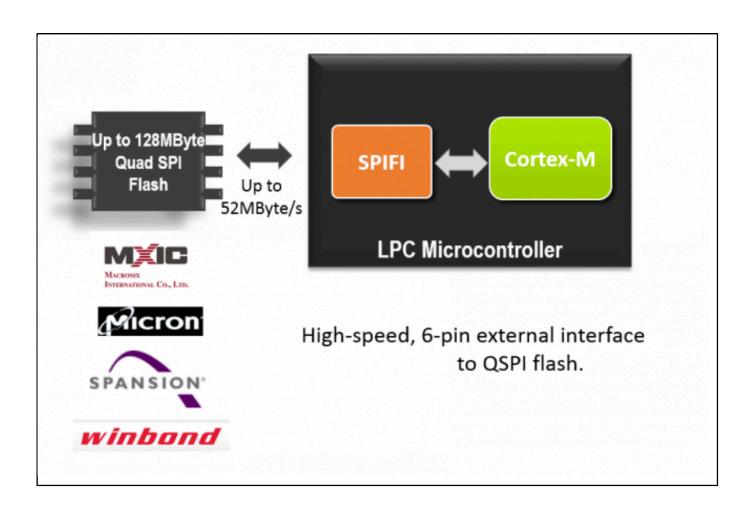

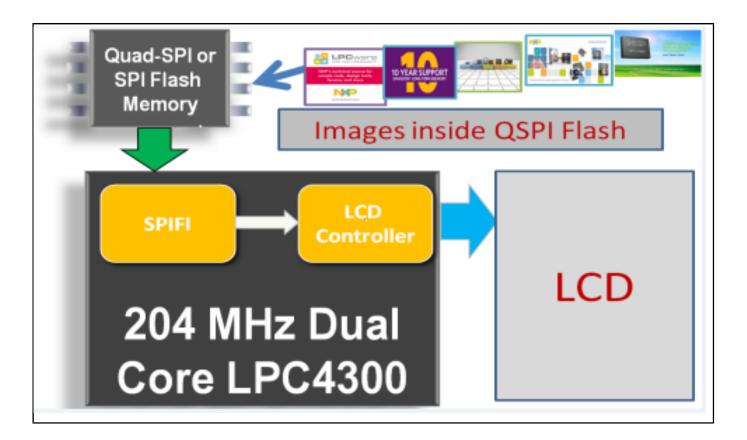

The SPI Flash Interface (SPIFI) allows low pin-count serial flash memories to be connected to an Arm® based LPC Microcontroller with very little performance penalty compared to higher pin-count parallel flash memories. After a few commands configure the interface at startup,the entire flash content is accessible as normal memory using byte, halfword, and word accesses by the processor and/or DMA channels. Erasure and programming are handled by simple sequences of commands.

Many SPI flash devices use serial commands for device setup/initialization, and then move to dual or quad commands for normal operation. Different serial Flash vendors and devices accept or require different commands and command formats. SPIFI includes sufficient flexibility to be compatible with many market-leading devices plus extensions to help insure compatibility with future devices.

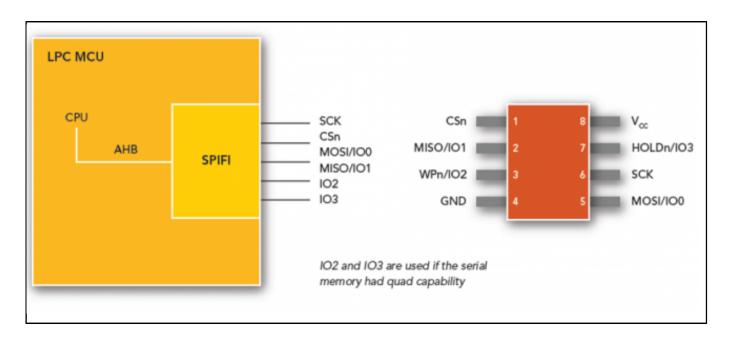

The SPIFI implements basic, dual, and quad SPI in half-duplex mode, in which the SPIFI always sends a command to a serial flash memory at the start of each frame. In write commands, the SPIFI sends all of the data in the frame, while in read commands, the SPIFI sends the command, and then the serial flash sends data to the SPIFI. SPI Flash devices respond to commands sent by software, or automatically sent by the SPIFI when software reads the serial flash region of the memory map. Commands are divided into fields called opcode, address, intermediate data, and data. The address, intermediate data, and data fields are optional depending on the opcode. Some devices include a mode in which the opcode can be implied in Read commands for higher performance. Data fields are further divided into input and output data fields depending on the opcode.

## LPC-SPIFI-PERIPHERAL-BD2 Block Diagram

LPC-SPIFI-PERIPHERAL-BD3 Block Diagram

View additional information for LPC SPIFI Peripheral.

Note: The information on this document is subject to change without notice.

## www.nxp.com

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2025 NXP B.V.