## Quad Universal Asynchronous Receiver/Transmitter (QUART)

## **SC28C94A1A**

アーカイブス

このページには、製造中止(生産終了)となった製品の情報が記載されています。本ページに記載されている仕様および情報は、過去の参考情報です。

Last Updated: Aug 16, 2023

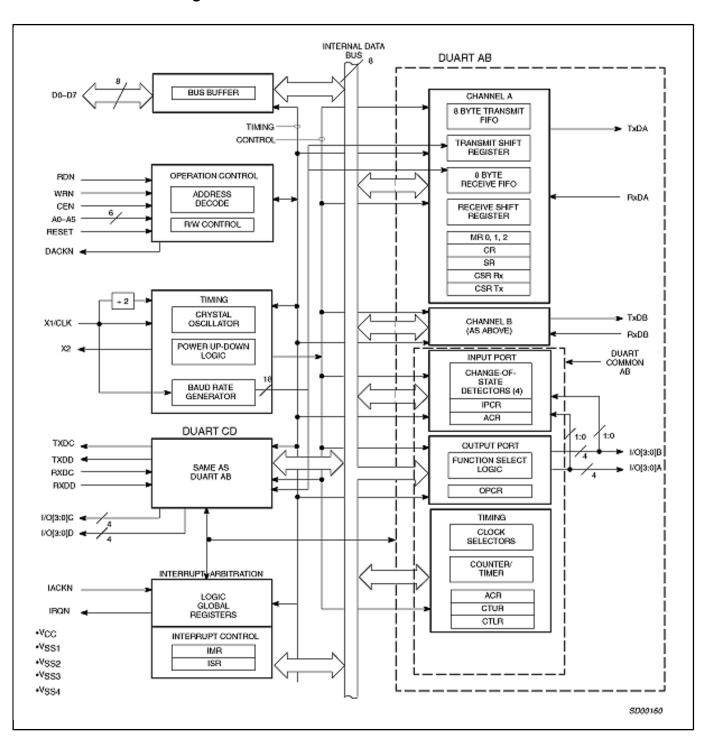

The 28C94 quad universal asynchronous receiver/transmitter (QUART) combines four enhanced Philips Semiconductors industry-standard UARTs with an innovative interrupt scheme that can vastly minimize host processor overhead. It is implemented using Philips Semiconductor's high-speed CMOS process that combines small die size and cost with low power consumption.

The operating speed of each receiver and transmitter can be selected independently at one of eighteen fixed baud rates, a 16X clock derived from a programmable counter/timer, or an external 1X or 16X clock. The baud rate generator and counter/timer can operate directly from a crystal or from external clock inputs. The ability to independently program the operating speed of the receiver and transmitter make the QUART particularly attractive for dual-speed channel applications such as clustered terminal systems.

Each receiver is buffered with eight character FIFOs (first-in-first-out memories) and one shift register to minimize the potential for receiver overrun and to reduce interrupt overhead in interrupt driven systems. In addition, a handshaking capability is provided to disable a remote UART transmitter when the receiver buffer is full (RTS control).

The 28C94 provides a power-down mode in which the oscillator is stopped and the register contents are stored. This results in reduced power consumption on the order of several magnitudes. The QUART is fully TTL compatible and operates from a single +5V power supply.

## SC28C94A1A Block Diagram

View additional information for Quad Universal Asynchronous Receiver/Transmitter (QUART).

Note: The information on this document is subject to change without notice.

**www.nxp.com**NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2024 NXP B.V.