## 1.8 V dual UART, 5 Mbit/s (max.) with 128-byte FIFOs, infrared (IrDA) and 16 mode or 68 mode bus interface

## SC16C852L

アーカイブス

このページには、製造中止(生産終了)となった製品の情報が記載されています。本ページに記載されている仕様および情報は、過去の参考情報です。

Last Updated: Jul 11, 2023

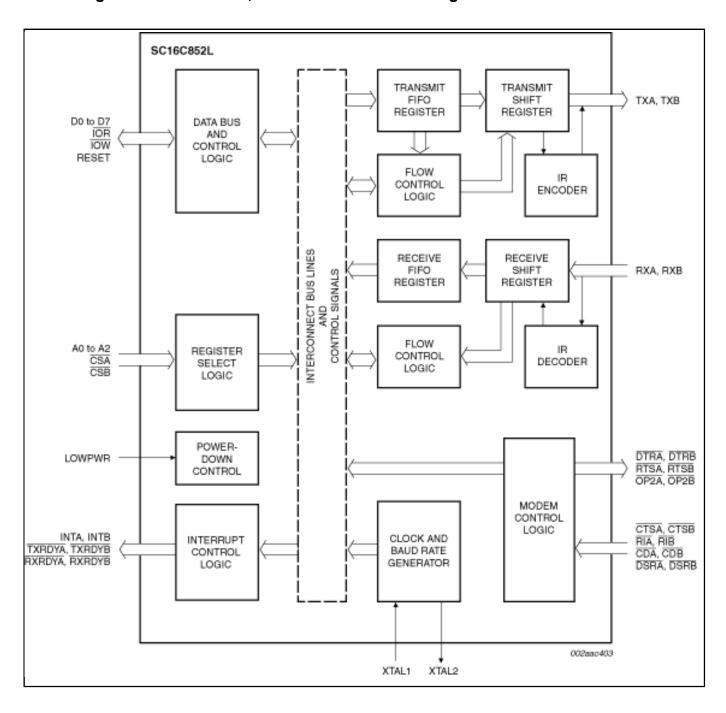

The SC16C852L is a 1.8 V, low power, dual channel Universal Asynchronous Receiver and Transmitter (UART) used for serial data communications. Its principal function is to convert parallel data into serial data and vice versa. The UART can handle serial data rates up to 5 Mbit/s. The SC16C852L is pin compatible with the SC16C652B. SC16C852L can be programmed to operate in extended mode (see Section 6.2) where additional advanced UART features are available. The SC16C852L UART provides enhanced UART functions with 128-byte FIFOs, modem control interface, DMA mode data transfer, and IrDA encoder/decoder. The DMA mode data transfer is controlled by the FIFO trigger levels and the TXRDYx and RXRDYx signals. On-board status registers provide the user with error indications and operational status. System interrupts and modem control features may be tailored by software to meet specific user requirements. An internal loopback capability allows on-board diagnostics. Independent programmable baud rate generators are provided to select transmit and receive baud rates.

The SC16C852L with Intel (16 mode) or Motorola (68 mode) bus host interface operates at 1.8 V and is available in plastic LQFP48, TFBGA36 and very small (Micro-UART) HVQFN32 packages.

## Block diagram: SC16C852LIB, SC16C852LIBS Block Diagram

View additional information for 1.8 V dual UART, 5 Mbit/s (max.) with 128-byte FIFOs, infrared (IrDA) and 16 mode or 68 mode bus interface.

Note: The information on this document is subject to change without notice.

**www.nxp.com**NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2024 NXP B.V.