## **Simple Two-Wire Bus Buffer**

## PCA9525

アーカイブス

このページには、製造中止(生産終了)となった製品の情報が記載されています。本ページに記載されている仕様および情報は、過去の参考情報です。

Last Updated: Jul 12, 2023

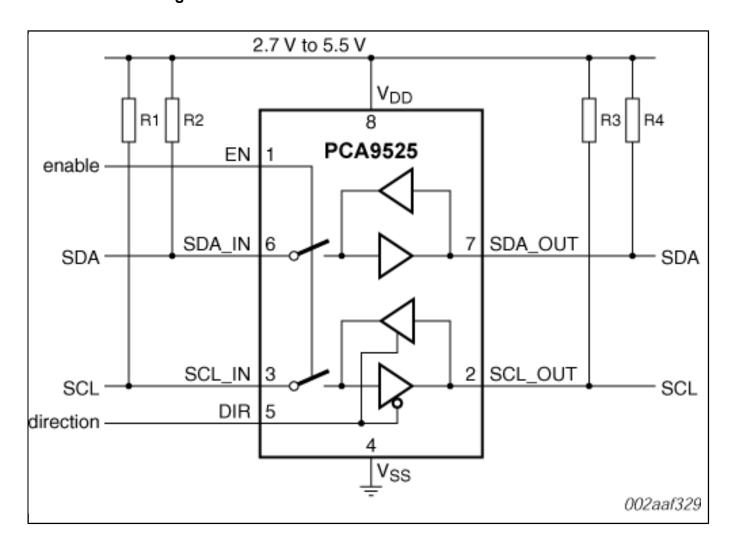

The PCA9525 is a monolithic CMOS integrated circuit for bus buffering in applications including I2>C-bus, SMBus, DDC, PMBus, and other systems based on similar principles.

The buffer extends the bus load limit by buffering both the SCL and SDA lines, allowing the maximum permissible bus capacitance on both sides of the buffer.

The PCA9525 includes a unidirectional buffer for the clock signal, and a bidirectional buffer for the data signal. Target devices which employ clock stretching are therefore not supported.

In its most basic implementation, the buffer will allow an extended number of target devices to be attached to one (or more) controller devices. In this case, all controller devices would be positioned on the Sxx IN side of the PCA9525.

The direction pin (DIR) further enhances this function by allowing the unidirectional clock signal to be reversed, thus allowing controller devices on both sides of the buffer.

The enable (EN) function allows sections of the bus to be isolated. Individual parts of the system can be brought on-line successively. This means a controlled start-up using a diverse range of components, operating speeds and loads is easily achieved.

## PCA9525 Block Diagram

View additional information for Simple Two-Wire Bus Buffer.

Note: The information on this document is subject to change without notice.

## www.nxp.com

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2024 NXP B.V.