# レベル変換I<sup>2</sup>Cバス・リピータ PCA9517

## Not Recommended for New Designs

このページでは、新規設計を推奨しない製品に関する情報を掲載しています。

Last Updated: Dec 16, 2024

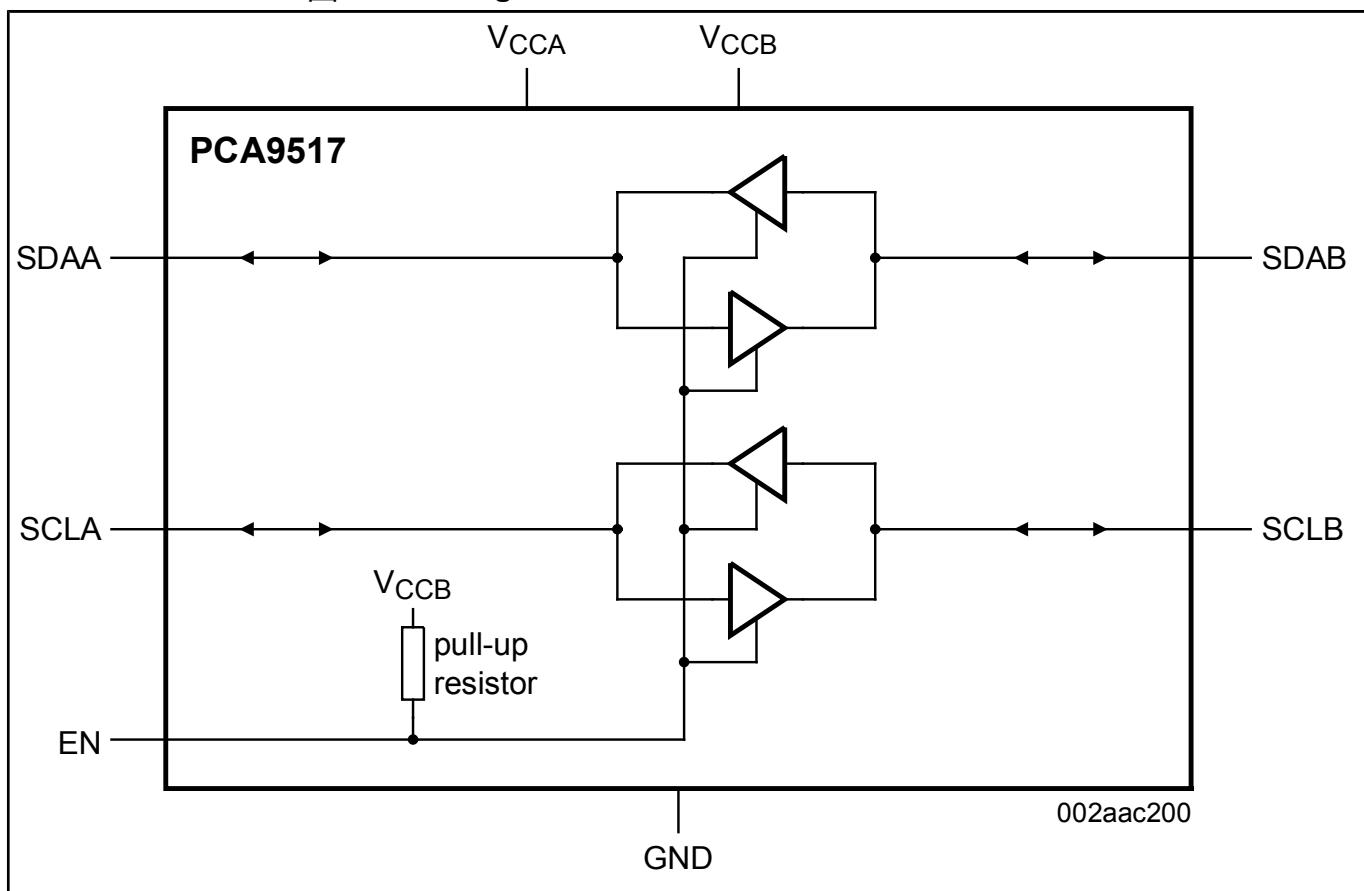

PCA9517は、低電圧（最小0.9 V）と高電圧（2.7 V～5.5 V）のI<sup>2</sup>CバスまたはSMBusアプリケーション間でレベル・シフトを行うCMOS集積回路です。レベル変換時にI<sup>2</sup>Cバス・システムのすべての動作モードと機能を保持するとともに、データ（SDA）ラインとクロック（SCL）ラインの両方を双方向にバッファリングしてI<sup>2</sup>Cバスを拡張することで、400 pFの2つのバスを実現します。PCA9517を使用すると、システム設計者はバスを電圧と静電容量の両方について絶縁された2つのバスに分割できます。SDAピンおよびSCLピンは過電圧への耐性があり、PCA9517の電源がオフのときにはハイインピーダンスとなります。

2.7 V～5.5 Vのバスを駆動するB側ドライバの動作はPCA9515Aデバイスのドライバと類似していますが、可変電圧バスのA側ドライバはより多くの電流を駆動し、静的オフセット電圧が不要です。これにより、B側のLOWはA側でほぼ0 VのLOWに変換され、低電圧ロジックのより小さな電圧スイングに対応できます。

PCA9517のB側I/Oドライバは静的オフセット設計であるため、PCA9510、PCA9511、PCA9512、PCA9513、PCA9514、PCA9515A、PCA9516A、PCA9517（B側）、PCA9518など、立上がり時間アクセラレータを備えた他のデバイスには接続できません。ただし、複数のPCA9517のA側を相互に接続することで、共通バスでA側を使用したスター型トポグラフィが可能になり、A側を静的または動的オフセット電圧を備えた他のバッファに直接接続できます。複数のPCA9517をA側からB側に直列に接続でき、この際にオフセット電圧は蓄積しないため、ToF（Time of Flight）遅延のみを考慮する必要があります。

PCA9517のドライバは、VCCAが0.8 Vを超え、VCCが2.5 Vを超えない限り有効になりません。ENピンは、システムの制御下でドライバをオン/オフするためにも使用できます。イネーブル・ピンの状態の変更はバスがアイドル状態のときのみ行うよう注意が必要です。

B側の内部バッファLOWの出力プルダウンは約0.5 Vに設定されており、内部バッファの入力しきい値はそれよりも約70 mV低く（0.43 Vに）設定されています。B側I/Oが内部でLOWに駆動

された場合、このLOWは入力によるLOWとしては認識されません。これにより、ロックアップ状態の発生が防止されます。A側の出力プルダウンはハードLOWを駆動し、入力レベルは0.3 VCCAに設定されています。これは、低電圧側の電源電圧が最小0.9 Vのシステムで、より低いLOWレベルが必要な場合に対応するためです。

PCA9517のブロック図 Block Diagram

PCA9517D、PCA9517DPのブロック図 Block Diagram

[View additional information for レベル変換I2Cバス・リピータ.](#)

**Note:** The information on this document is subject to change without notice.

---

**www.nxp.com**

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2025 NXP B.V.