## **Dual Bidirectional Bus Buffer**

## P82B96

Last Updated: Jan 31, 2024

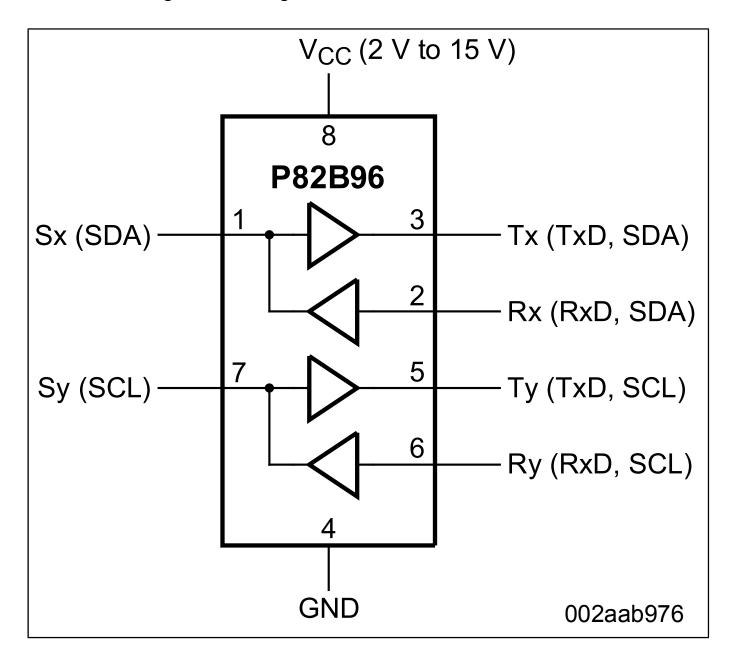

The P82B96 is a bipolar IC that creates a non-latching, bidirectional, logic interface between the normal IC-bus and a range of other bus configurations. It can interface IC-bus logic signals to similar buses having different voltage and current levels.

For example, it can interface to the 350 A SMBus, to 3.3 V logic devices, and to 15 V levels and/ or low-impedance lines to improve noise immunity on longer bus lengths.

It achieves this interface without any restrictions on the normal IC-bus protocols or clock speed. The IC adds minimal loading to the IC-bus node, and loadings of the new bus or remote ICbus nodes are not transmitted or transformed to the local node. Restrictions on the number of IC-bus devices in a system, or the physical separation between them, are virtually eliminated. Transmitting SDA and SCL signals via balanced transmission lines (twisted pairs) or with galvanic isolation (opto-coupling) is simple because separate directional Tx and Rx signals are provided. The Tx and Rx signals may be directly connected, without causing latching, to provide an alternative bidirectional signal line with IC-bus properties. P82B96 Block Diagram Block Diagram

View additional information for Dual Bidirectional Bus Buffer.

Note: The information on this document is subject to change without notice.

## www.nxp.com

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2024 NXP B.V.