# QorlQ® P1021/12 Single- and Dual-Core Multi-Protocol Communications Processors

## P1021

#### **Not Recommended for New Designs**

このページでは、新規設計を推奨しない製品に関する情報を掲載しています。

Last Updated: May 30, 2025

P1021 and P1012 devices are "Not recommended for new designs", please use the replacement families Power Architecture (T1024, T1014), Arm Architecture (LS1012, LS1023).

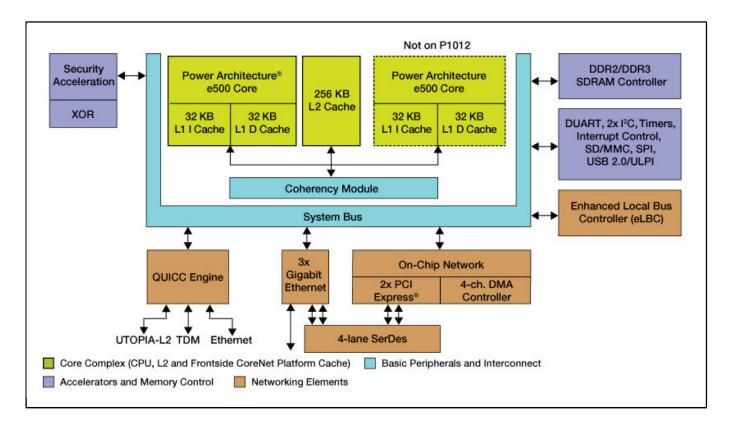

The QorlQ® P1 platform series, which includes the P1021 (dual-core) and P1012 (single-core) communications processors, offers the value of extensive integration and extreme power for a wide variety of applications in the networking, telecom, defense and industrial markets. Based on 45 nm technology for low-power implementation, the P1012 and P1021 processors provide single- and dual-core solutions for the 533 MHz to 800 MHz performance range, along with advanced security and a rich set of interfaces.

The P1012 and P1021 processors incorporate QUICC Engine® technology and are perfectly suited for multi-service gateways, Ethernet switch controllers, wireless LAN access points and high-performance general purpose control processor applications with tight thermal constraints. The QorlQ P1012 and P1021 processors are pin-compatible with the P1011, P1020 and P2 platform products, offering a six-chip range of cost-effective solutions. Scaling from a single core at 533 MHz (P1012) to a dual core at 1.2 GHz per core (P2020), the two QorlQ platforms deliver an impressive 4.5x aggregate frequency range.

### Freescale QorlQ P1021/12 Communication Processor Block Diagram Block Diagram

View additional information for QorlQ® P1021/12 Single- and Dual-Core Multi-Protocol Communications Processors.

Note: The information on this document is subject to change without notice.

#### www.nxp.com

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2025 NXP B.V.