## 12-Bit GTL-to-LVTTL Translator with Power Good Control and High-Impedance LVTTL and GTL Outputs

## GTL2008PW

アーカイブス

このページには、製造中止(生産終了)となった製品の情報が記載されています。本ページに記載されている仕様および情報は、過去の参考情報です。

Last Updated: Jun 14, 2023

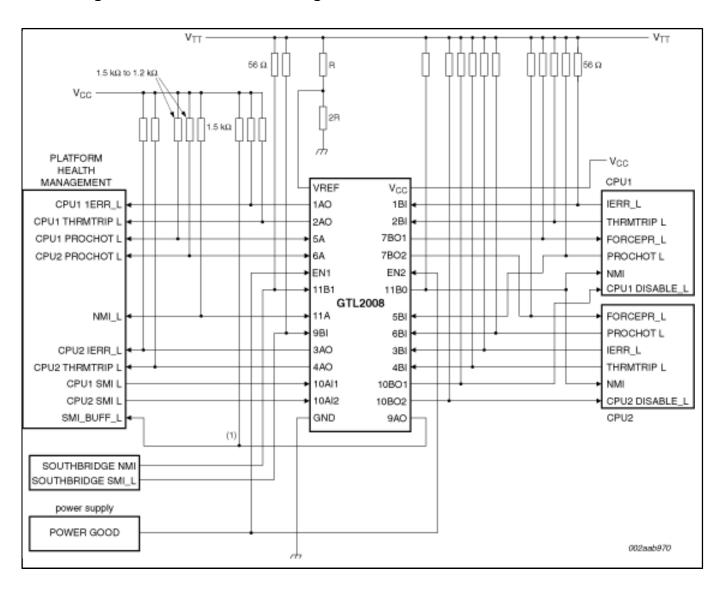

The GTL2008 is a customized translator between dual Xeon processors, Platform Health Management, South Bridge and Power Supply LVTTL and GTL signals.

Functionally and footprint identical to the GTL2007, the GTL2008 LVTTL and GTL outputs were changed to put them into a high-impedance state when EN1 and EN2 are LOW, with the exception of 11BO because its normal state is LOW, so it is forced LOW. EN1 and EN2 will remain LOW until VCC is at normal voltage, the other inputs are in valid states and VREF is at its proper voltage to assure that the outputs will remain high-impedance through power-up.

The GTL2008 has the enable function that disables the error output to the monitoring agent for platforms that monitor the individual error conditions from each processor. This enable function can be used so that false error conditions are not passed to the monitoring agent when the system is unexpectedly powered down. This unexpected power-down could be from a power supply overload, a CPU thermal trip, or some other event of which the monitoring agent is unaware.

A typical implementation would be to connect each enable line to the system power good signal or the individual enables to the VRD power good for each processor.

Typically Xeon processors specify a VTT of 1.1 V to 1.2 V, as well as a nominal Vref of 0.73 V to 0.76 V. To allow for future voltage level changes that may extend Vref to 0.63 of VTT(minimum of 0.693 V with VTT of 1.1 V) the GTL2008 allows a minimum Vref of 0.66 V. Characterization results show that there is little DC or AC performance variation between these Vref levels.

## Block diagram: GTL2008PW Block Diagram

View additional information for 12-Bit GTL-to-LVTTL Translator with Power Good Control and High-Impedance LVTTL and GTL Outputs.

Note: The information on this document is subject to change without notice.

## www.nxp.com

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2024 NXP B.V.