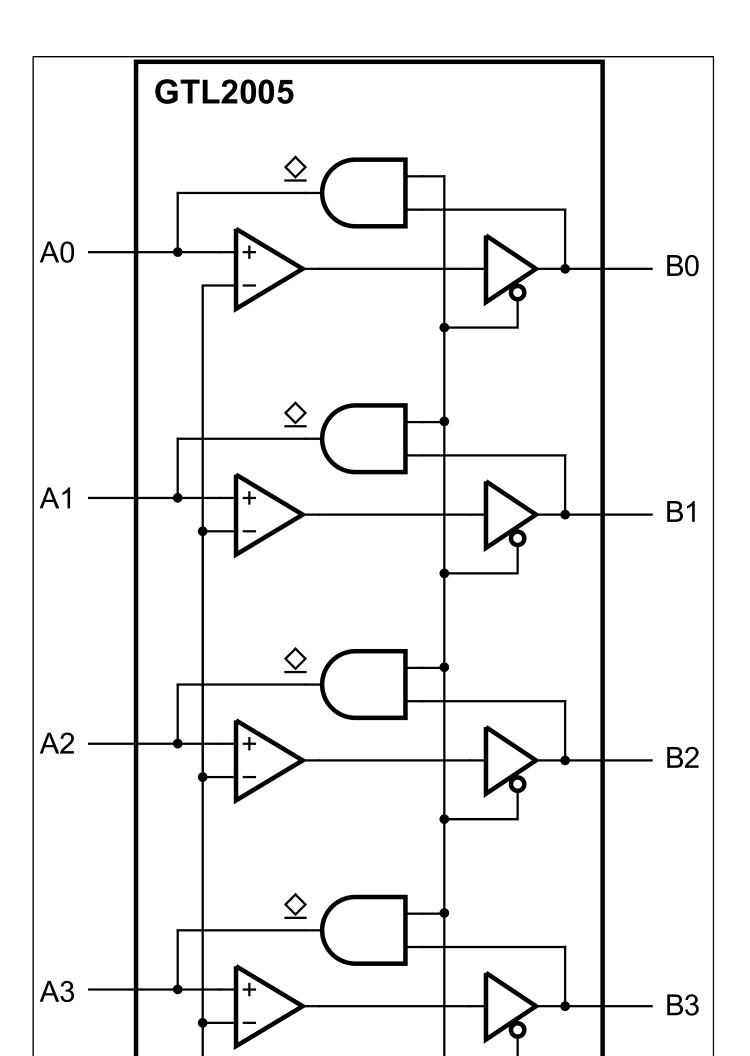

## Quad GTL/GTL+ to LVTTL/TTL Bidirectional Non-Latched Translator

## GTL2005PW

## **Archived**

このページには、製造中止(生産終了)となった製品の情報が記載されています。本ページに記載されている仕様および情報は、過去の参考情報です。

Last Updated: Feb 6, 2025

GTL2005PW device is "End of Life", please use the replacement part GTL2014PW

The GTL2005 is a quad translating transceiver designed for 3.3 V system interface with a GTL/ GTL+ bus.

The direction pin (DIR) allows the part to function as either a GTL-to-TTL sampling receiver or as a TTL-to-GTL interface.

The GTL2005 LVTTL interface is tolerant up to 5.5 V allowing direct access to TTL or 5 V CMOS outputs.

The GTL2005 Vref linearity degrades below 0.8 V (see <u>Section 10.1</u>). If the application allows, use the GTL2014, otherwise more closely review noise margins.

**Quad GTL/GTL+ to LVTTL/TTL Bidirectional Non-Latched Translator Block Diagram**

| : The information on this do | cument is subject to change | without notice. |  |  |

|------------------------------|-----------------------------|-----------------|--|--|

|                              |                             |                 |  |  |

|                              |                             |                 |  |  |

|                              |                             |                 |  |  |

View additional information for Quad GTL/GTL+ to LVTTL/TTL Bidirectional Non-Latched Translator.

NXP and the NXP logo are trademarks of NXP B.V. All other product or service names are the property of their respective owners. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. © 2025 NXP B.V.